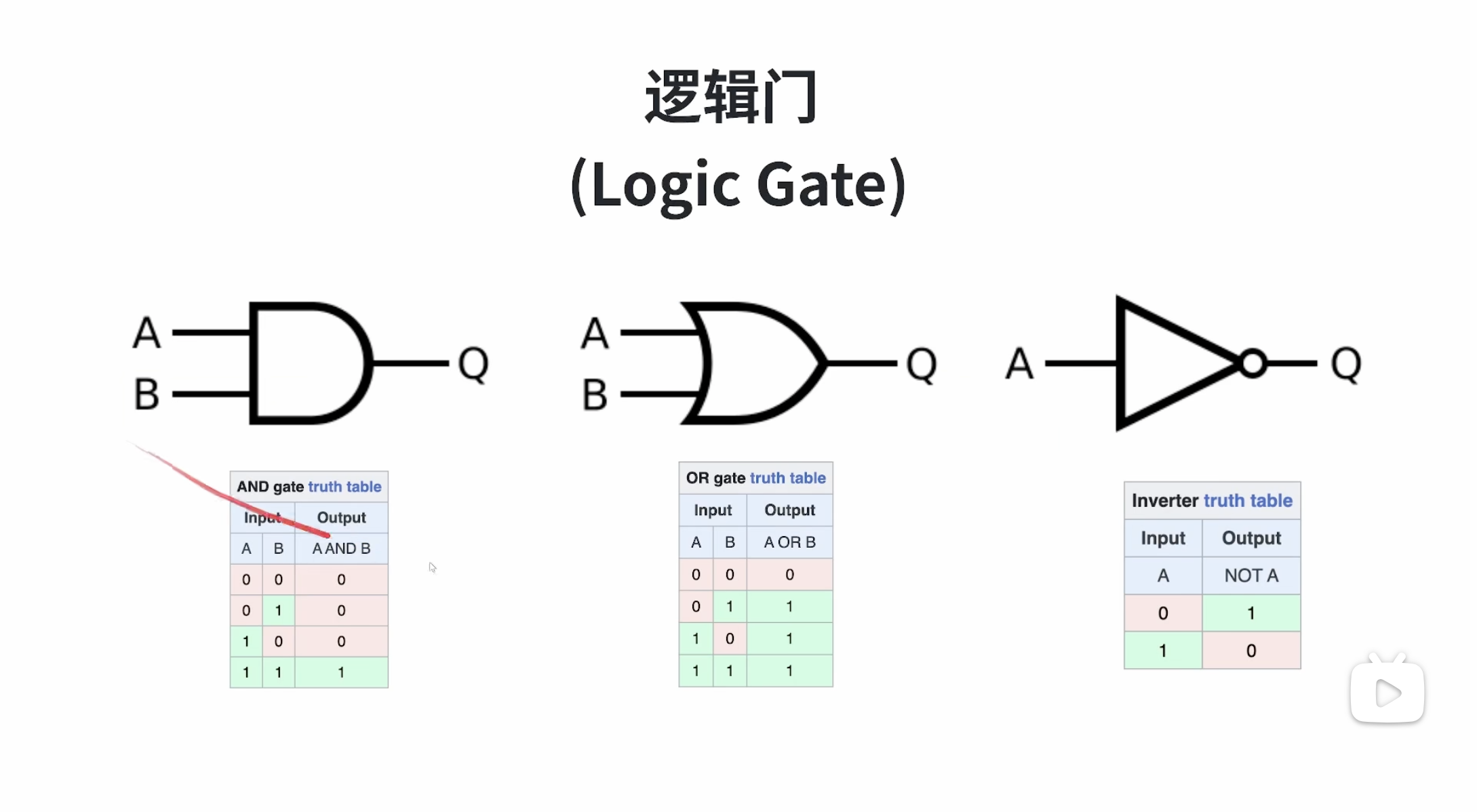

邏輯門

邏輯門簡單地理解即通過特定的條件實現與、或、非、異或等相關邏輯

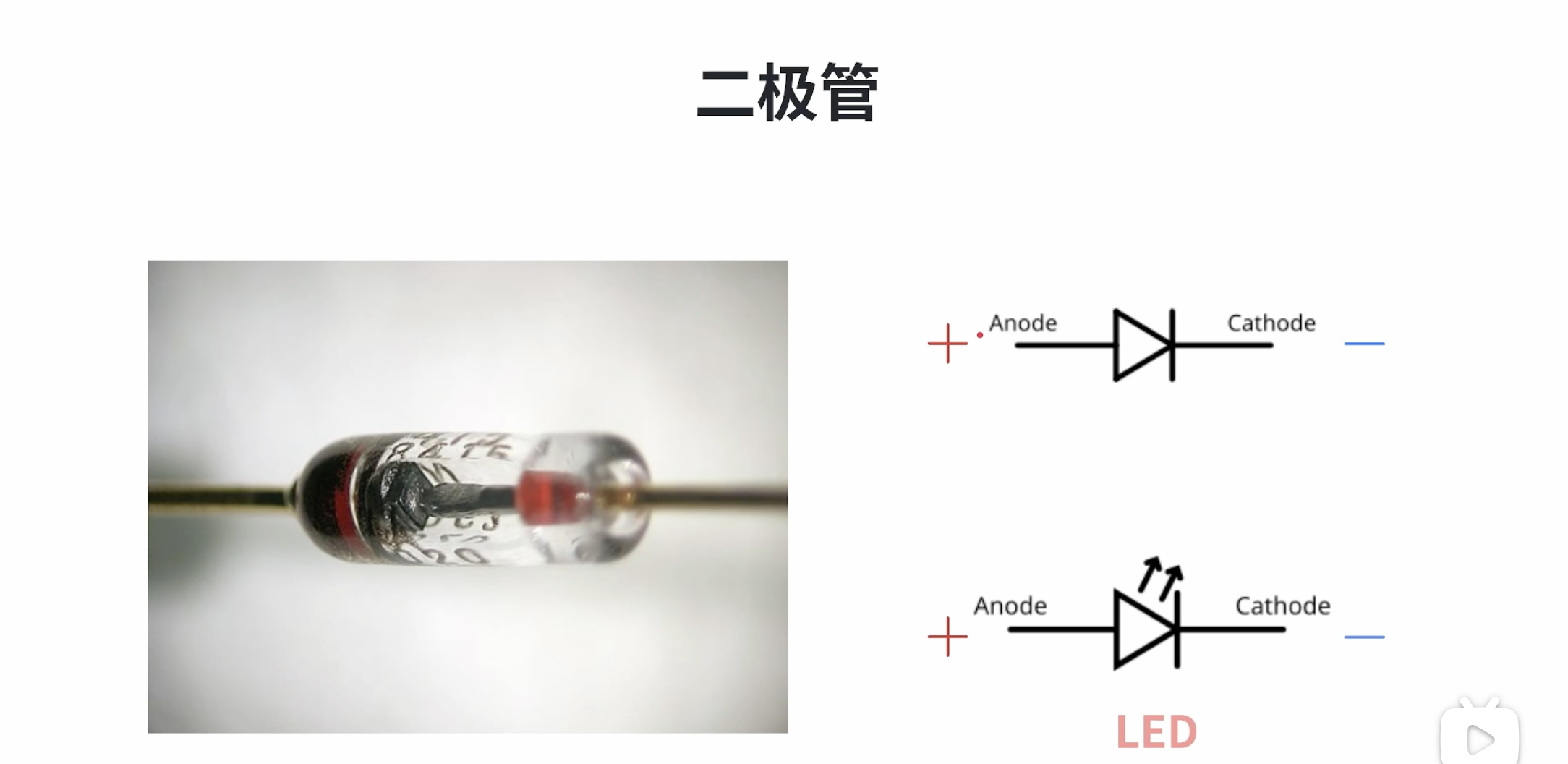

二極管

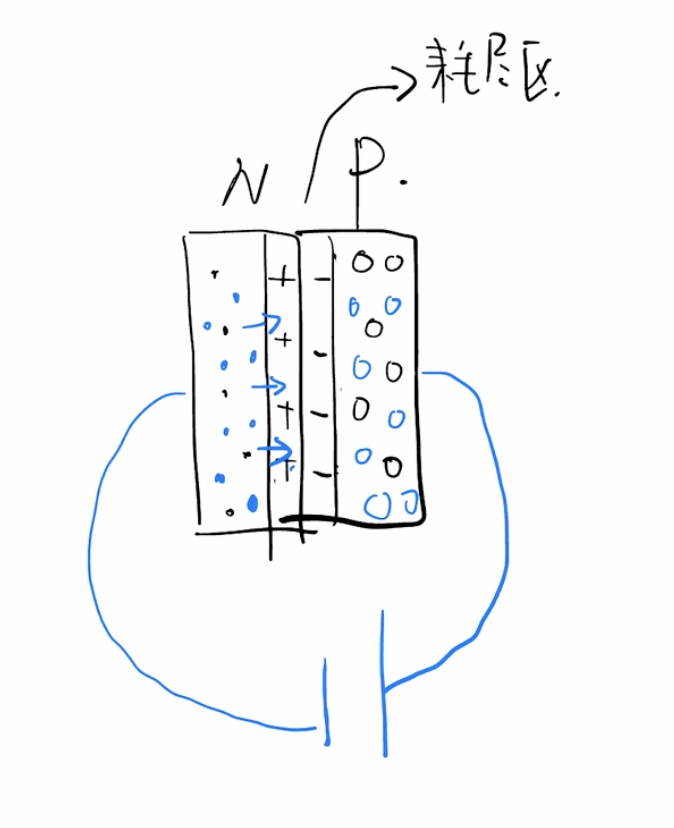

這些最基礎的邏輯門都是通過電路元器件進行搭建的,即半導體材料搭建的二極管

二極管有個特點,一定條件下才可以導通,即得接對正負極,具體的原理可以參考模擬電子技術相關內容

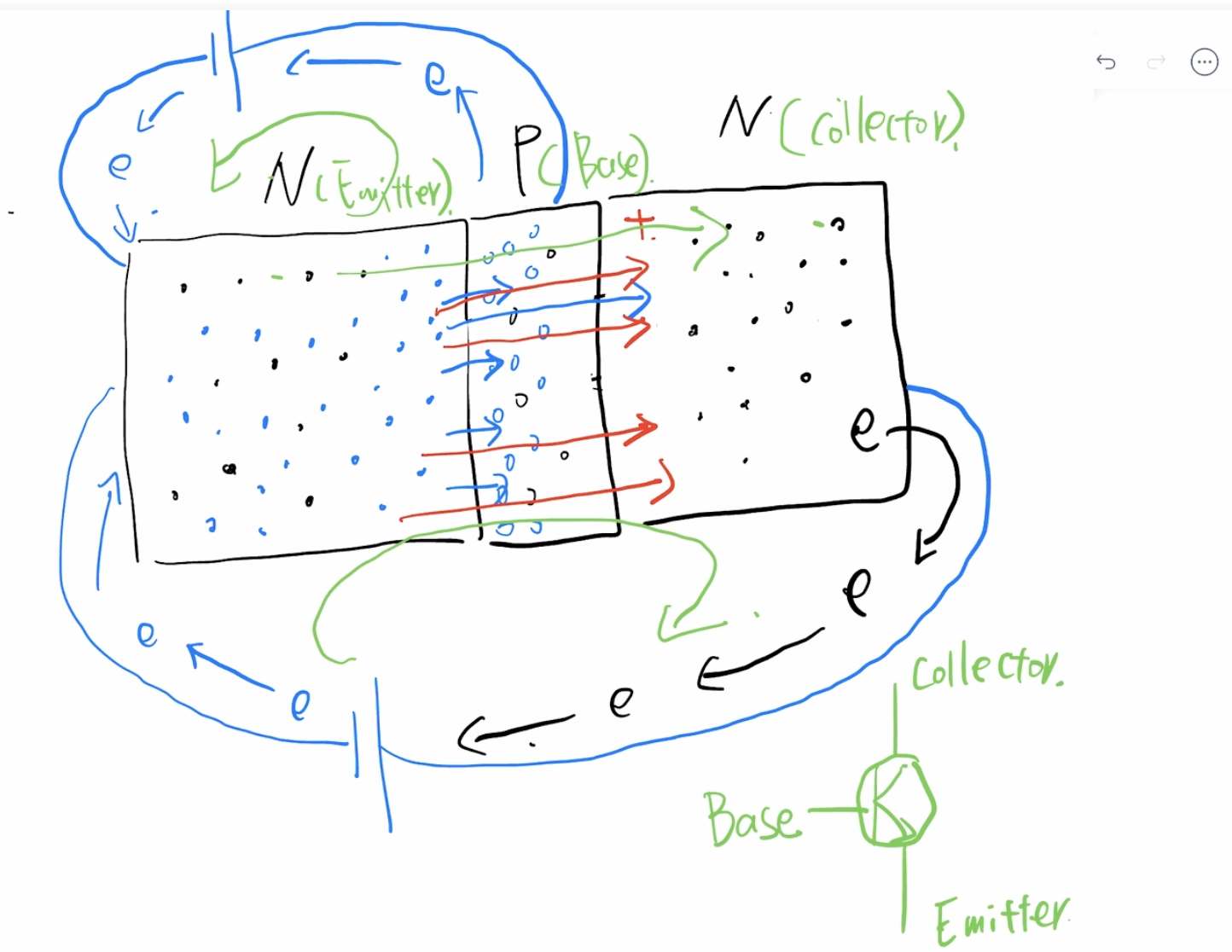

晶體管

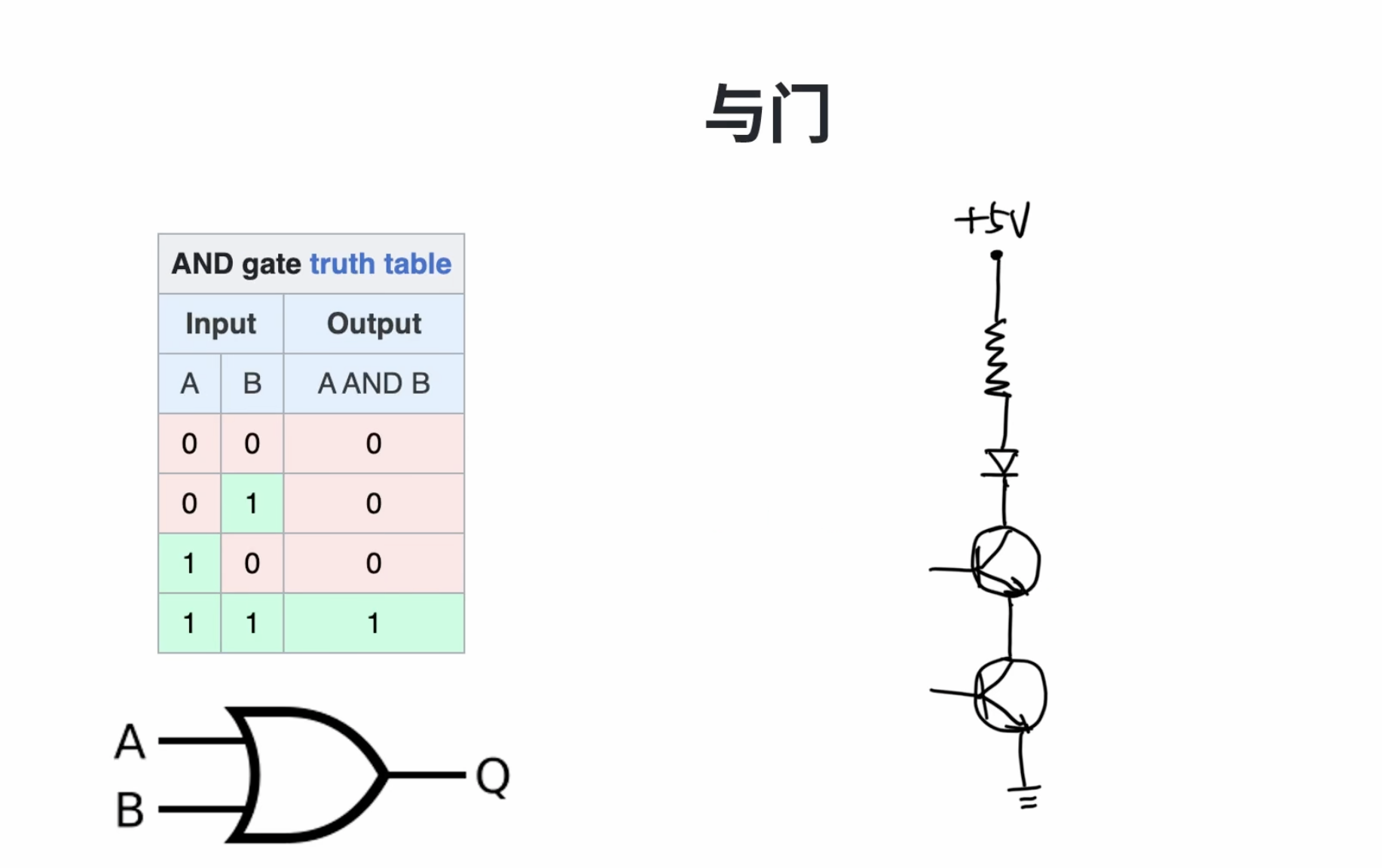

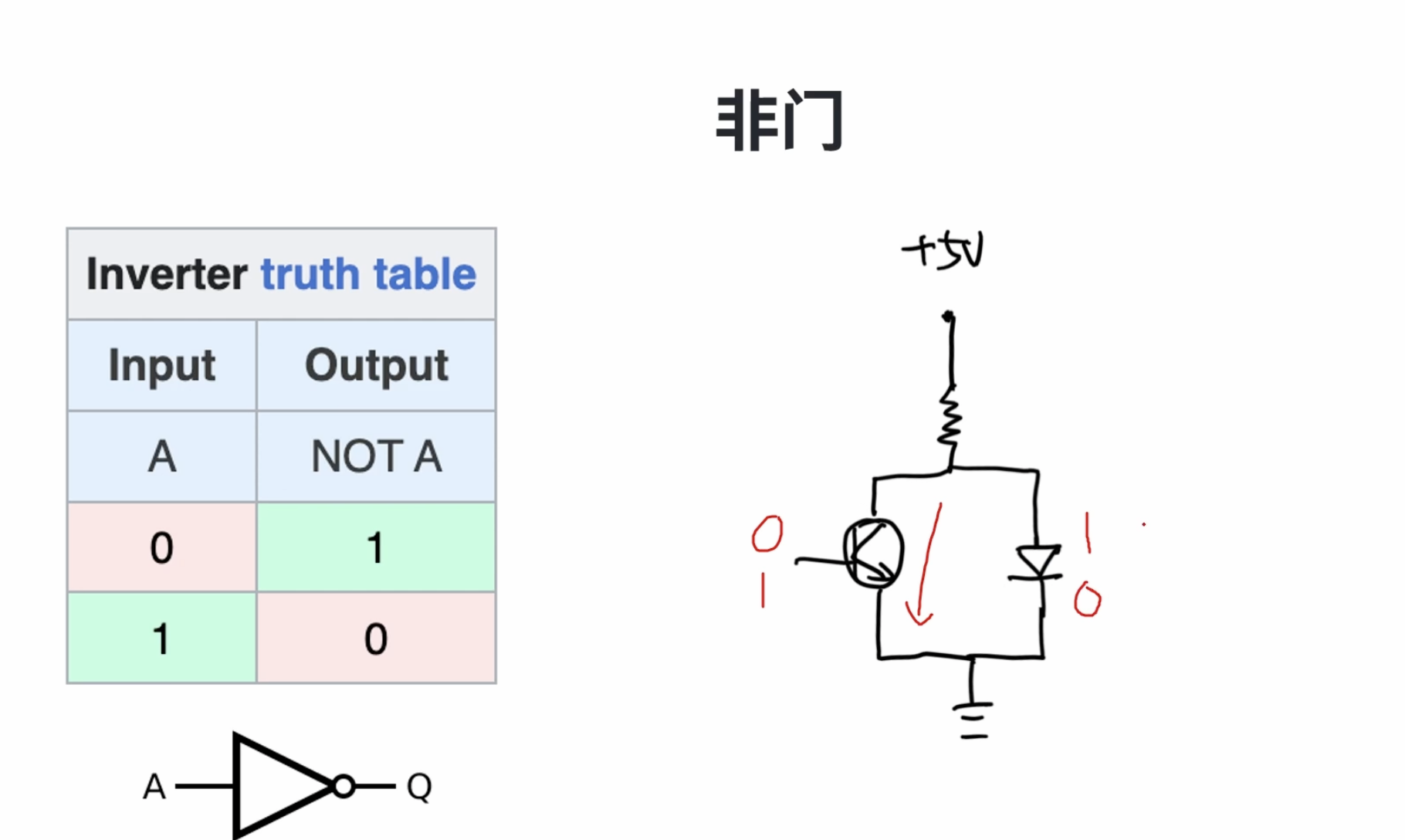

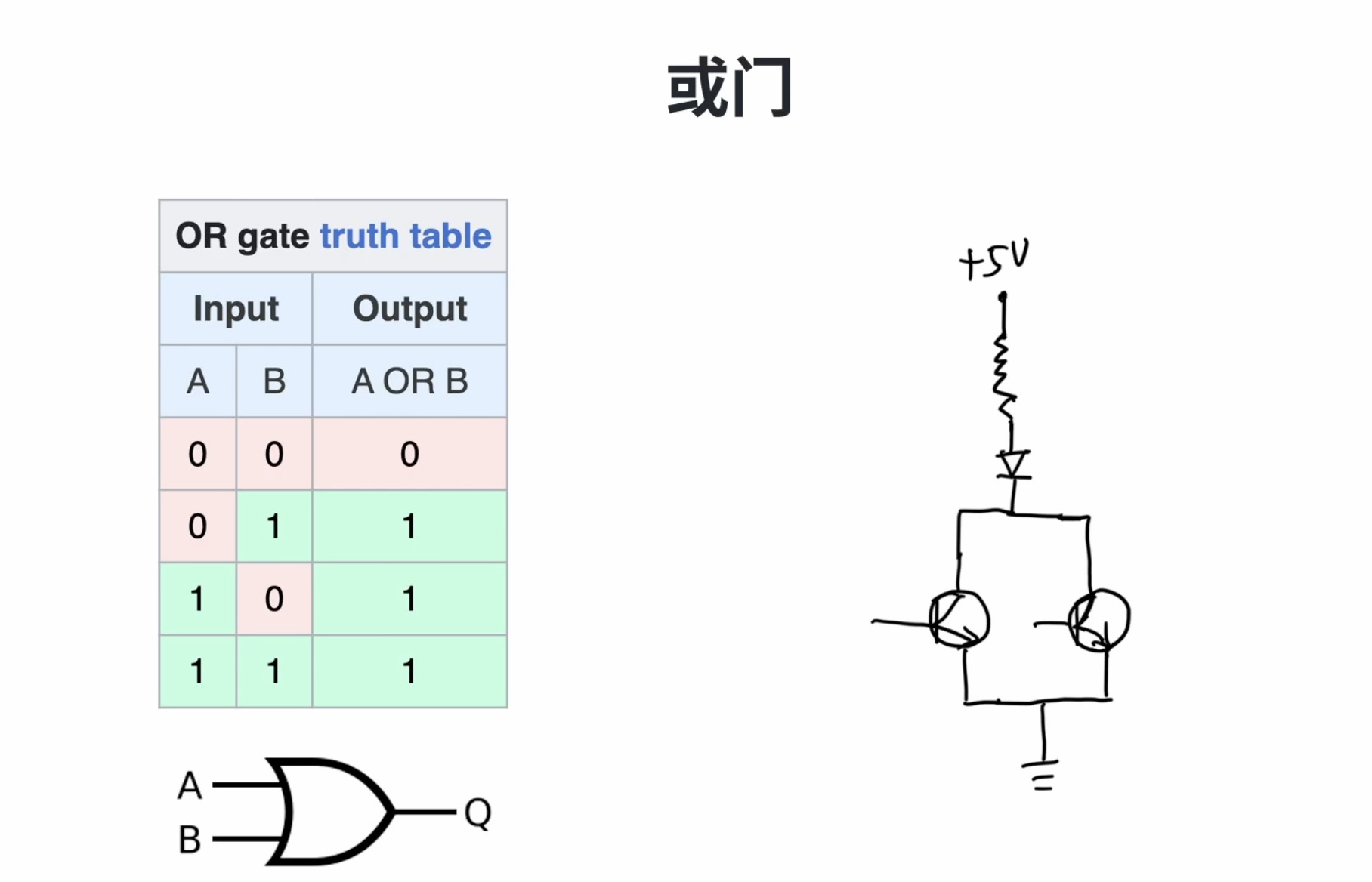

邏輯門搭建

在了解了以上基礎原理之后,搭建邏輯門就很容易了

與門的搭建,即串聯兩個晶體管,控制端來控制是否導通,若兩個晶體管的同時導通則整體電路導通,燈才會亮

非門的搭建,并聯晶體管和燈泡,有兩種情況

1,晶體管的控制端輸入0晶體管這條電路不導通,則燈泡這邊的電路導通,即輸出1

2,晶體管的控制端輸入1晶體管這條電路導通,則燈泡這邊的電路被短路,即輸出0

或門的搭建,通過燈泡串聯兩個并聯的晶體管實現,有如下幾類情況

- 1,左邊晶體管導通(輸入1),右邊晶體管不導通(輸入0),則整體電路導通,燈泡亮(輸出1)

- 2,左邊晶體管不導通(輸入0),右邊晶體管導通(輸入1),則整體電路導通,燈泡亮(輸出1)

- 3,左邊晶體管不導通(輸入0),右邊晶體管不導通(輸入0),則整體電路不導通被斷路,燈泡不亮(輸出0)

- 4,左邊晶體管導通(輸入1),右邊晶體管導通(輸入1),則整體電路導通,燈泡亮(輸出1)

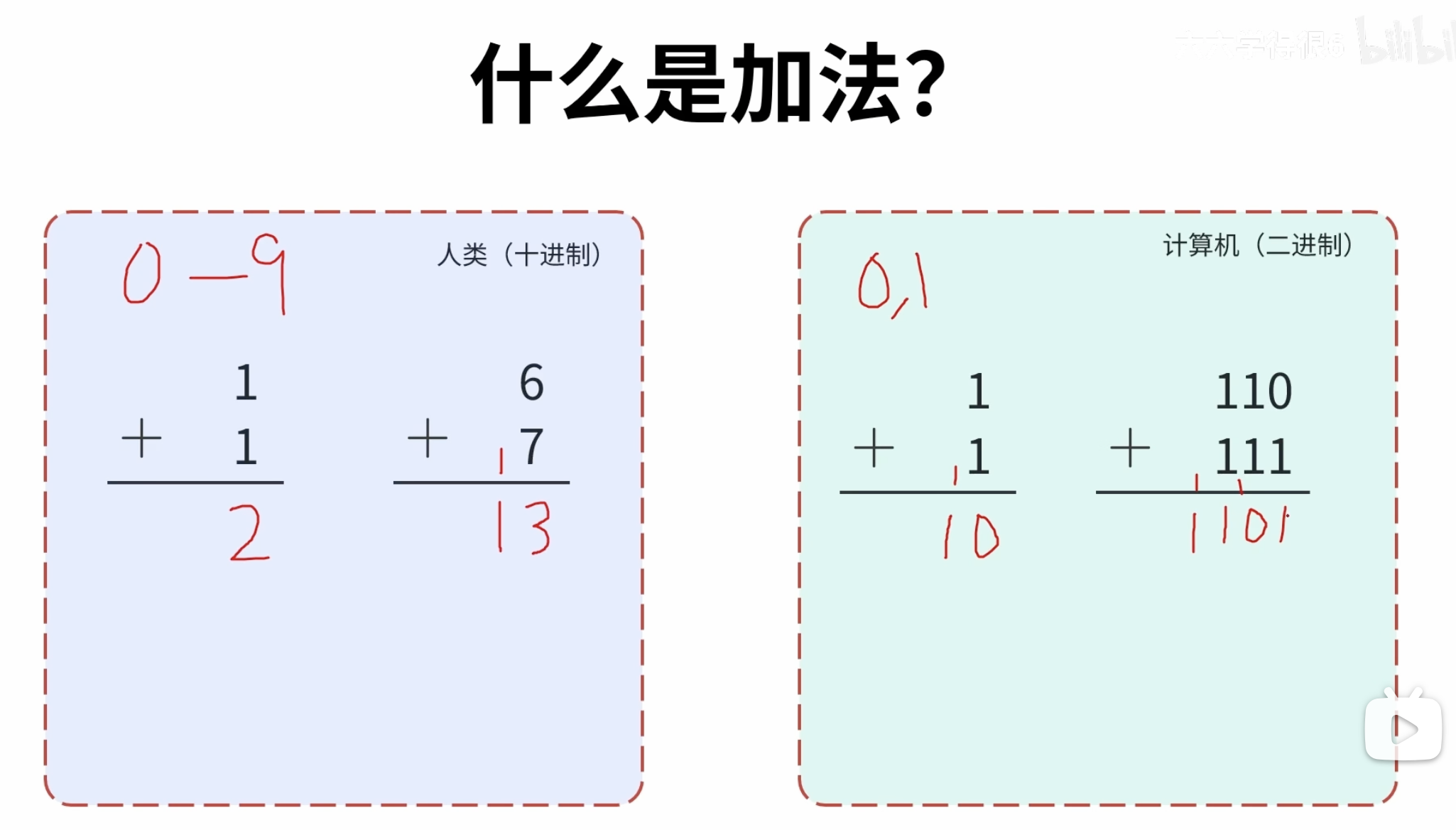

加法器

首先理解下加法原理,人類理解的加法采用的為十進制,比如1+1=2和6+7=13

在6+7這里超過10需進位,因此個位=3,十位=1 因此6+7=13

但是計算機只能給理解二進制,因此1+1,等于需進位因此 1+1=10

同理6+7 轉換成二進制加法=> 110 + 111 = 1101

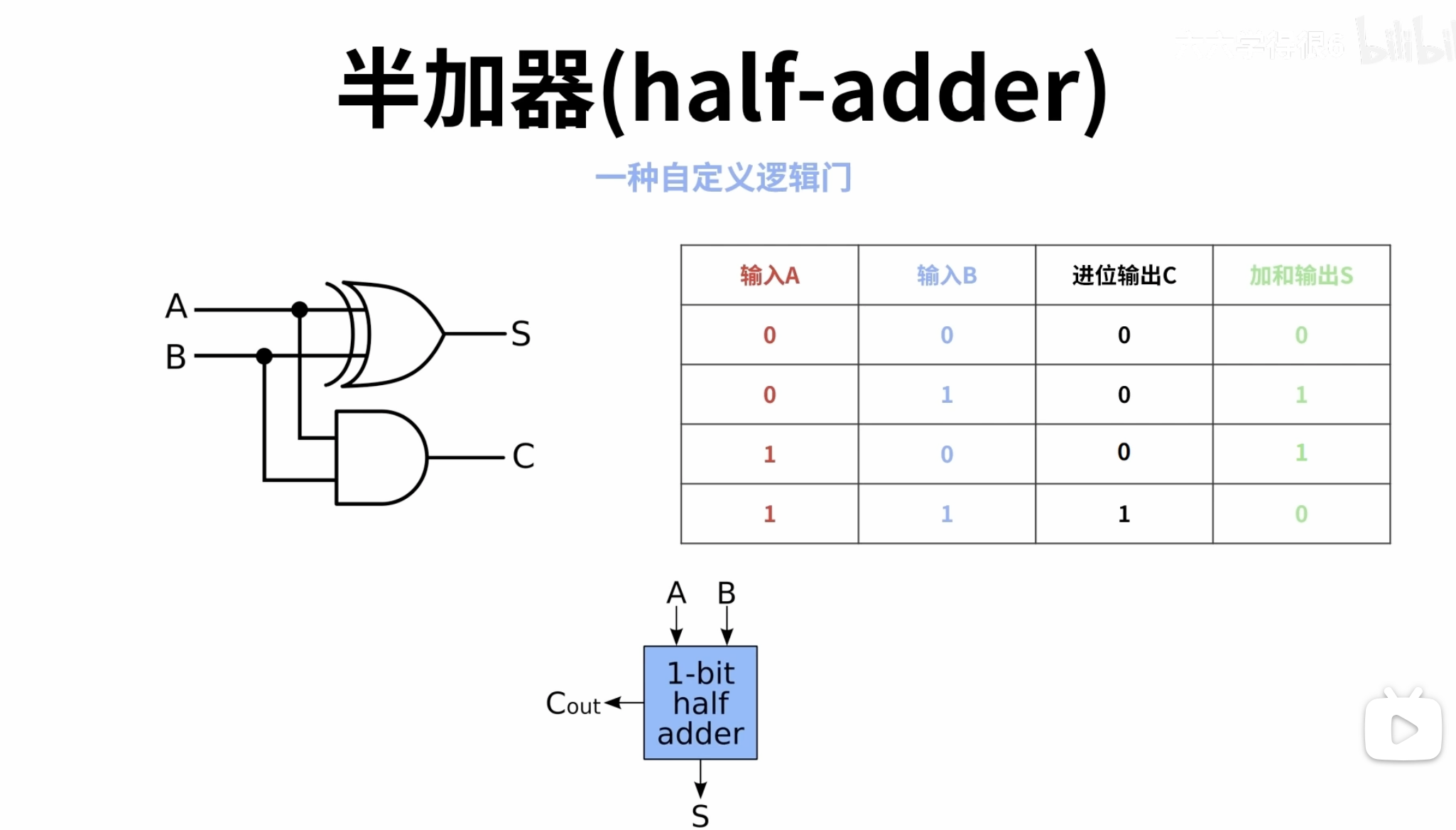

半加器

為啥稱之為半加器呢,當計算1+1=10的時候,半加器可以實現,但計算110+111的時候,輸出位數有4位,但半加器總共只有兩位輸出,因此無法實現多位數字的加法,因此稱之為半加器

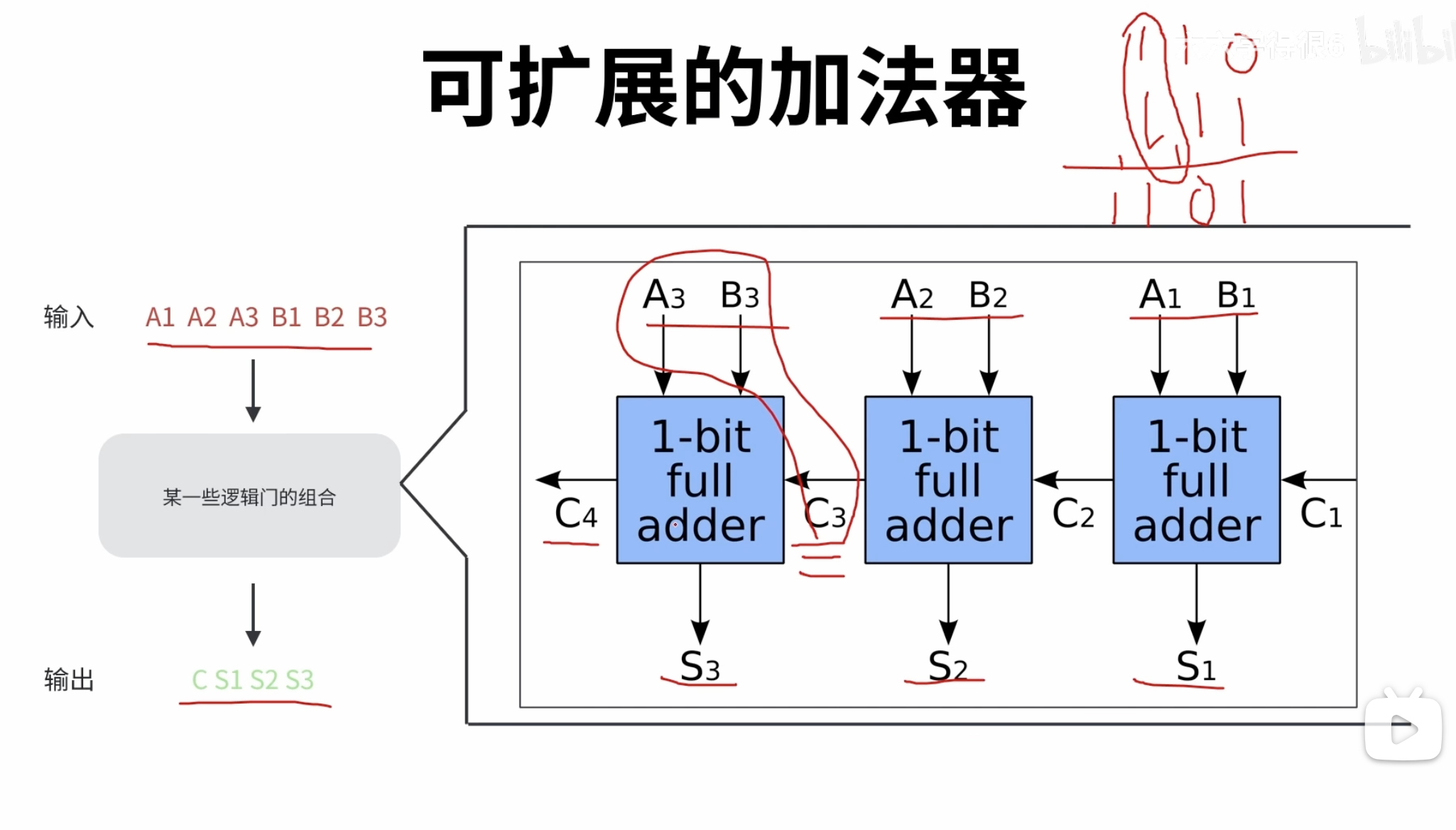

擴展加法器

將多個半加器串聯,即C作為進位輸出作為下一位的輸入,S作為本位的輸出,則實現了多位數字的加法器

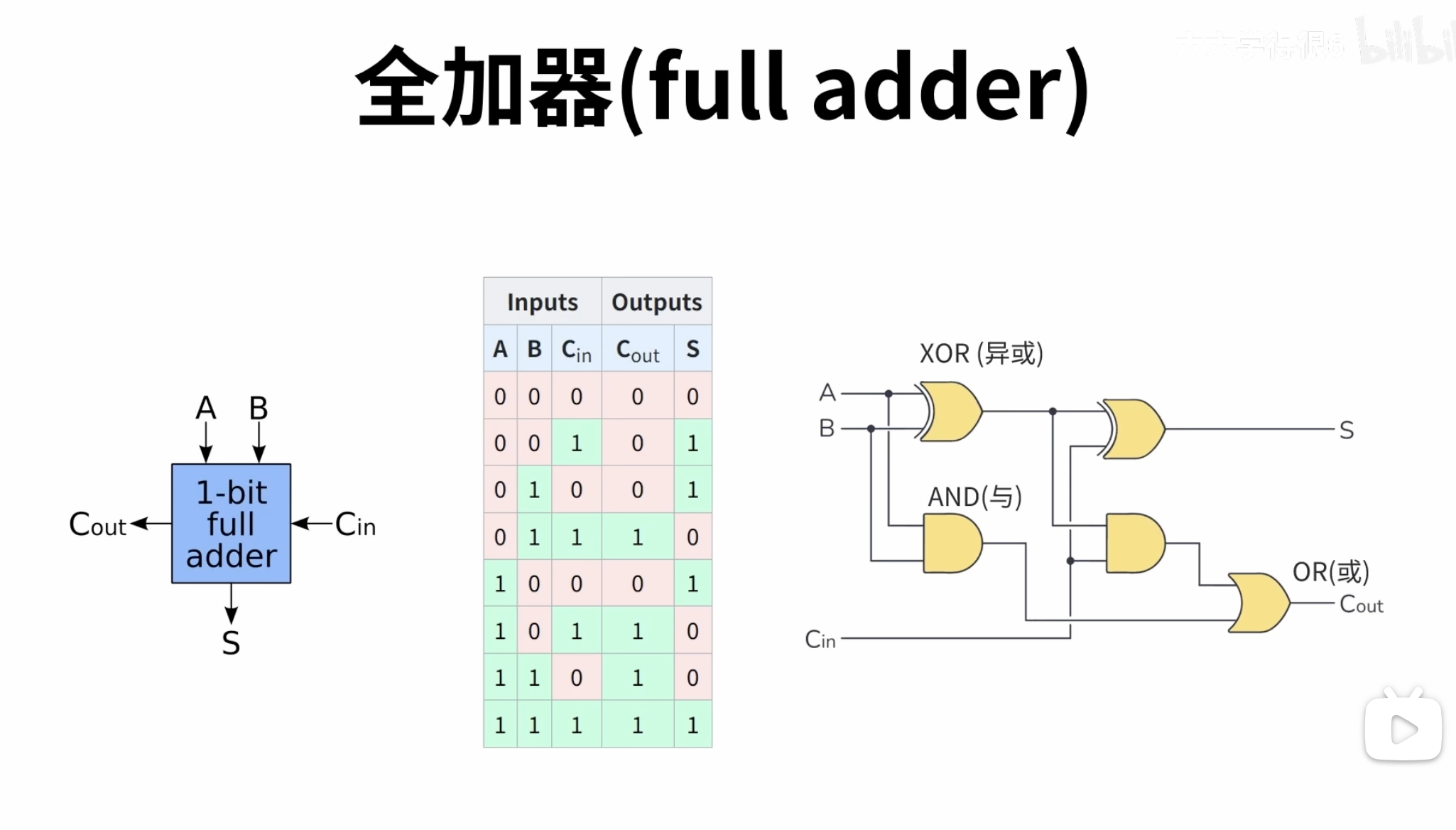

全加器

全加器邏輯門實現

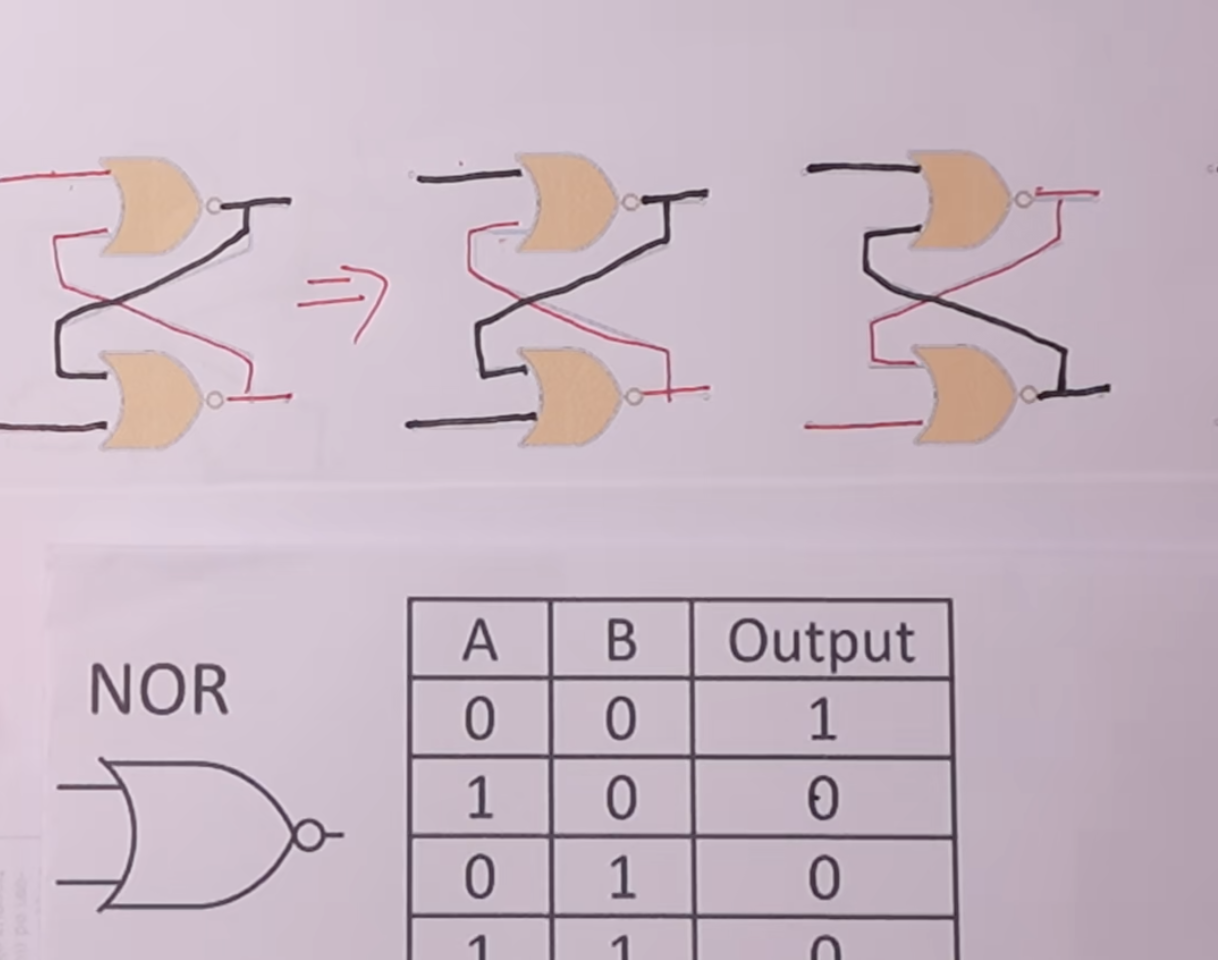

SR鎖存器

為啥還需要鎖存器

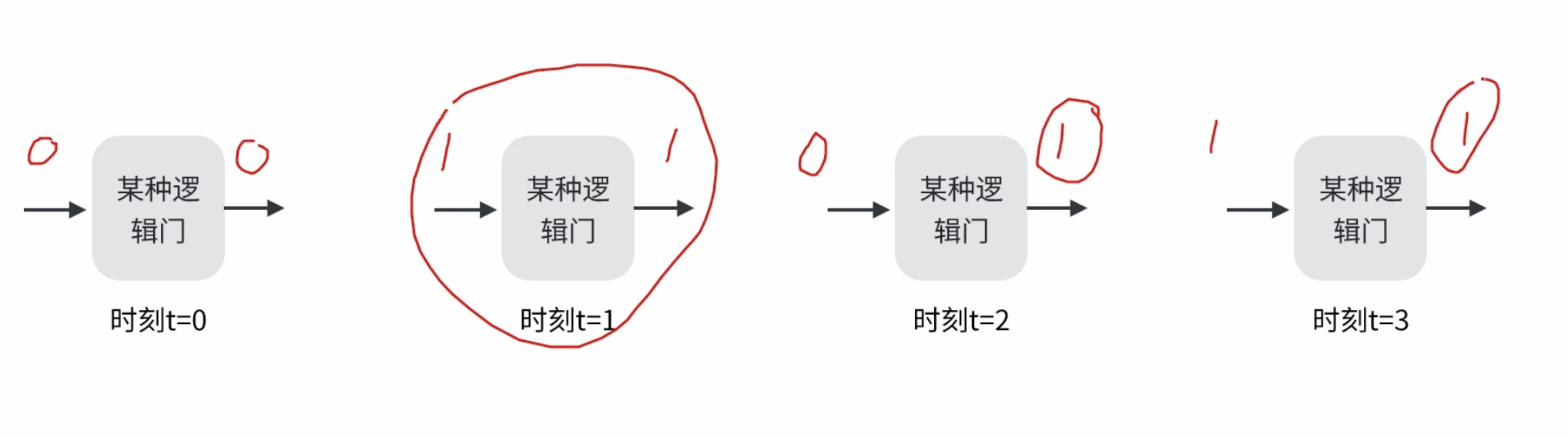

由于組合邏輯門都只有多個輸入,給到多個輸出,但輸出永遠由當前輸入決定,且不會改變,一旦當前輸入改變,則當前輸出會改變,那么它不具有記憶功能,存儲不了之前的輸入

理解記憶

有記憶功能的邏輯門

比如在t=1的時刻,給定輸入1,輸出=1,之后不管任何輸入,輸出恒定不變,則說明它具有記憶功能

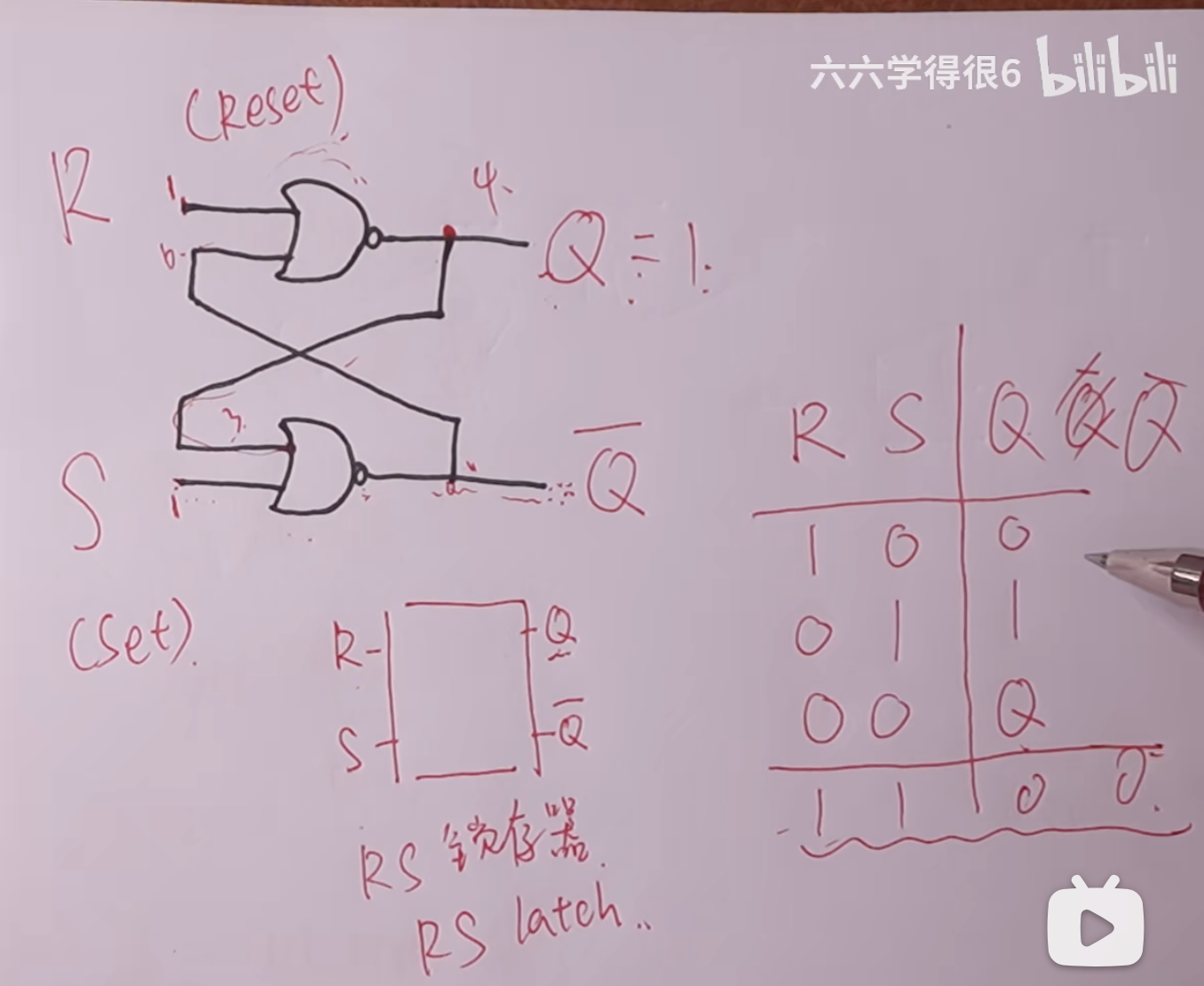

通過是S設置1,Q會輸入1,因此把它稱之為set端,通過Q端設置1, Q會置為0,因此稱之為reset,因此把這個組合邏輯門稱之為SR鎖存器

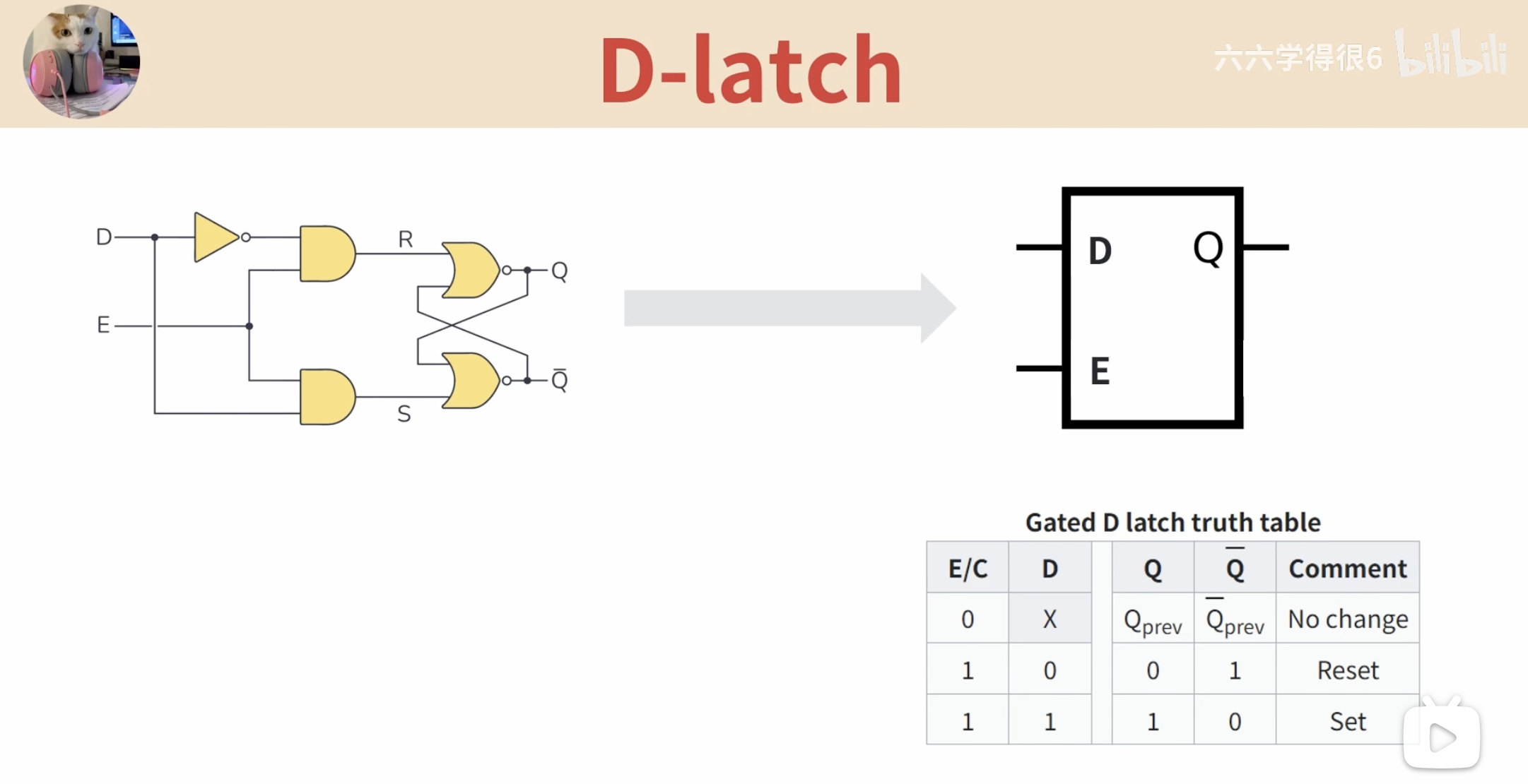

D鎖存器

SR鎖存器的局限

數據設置復雜,可以記憶1,但記憶不了0

沒有總開關設置,無法在想要存儲的時候存儲,關閉存儲的時候不存儲

因此需加上控制位來做總開關,以及加上數據輸入位,輸入1,存儲1,輸入0,存儲0

D鎖存器在SR鎖存器的基礎上做了如下改動

- 1,控制位:加上E使能輸入和與門

- 2,數據輸入D串聯非門

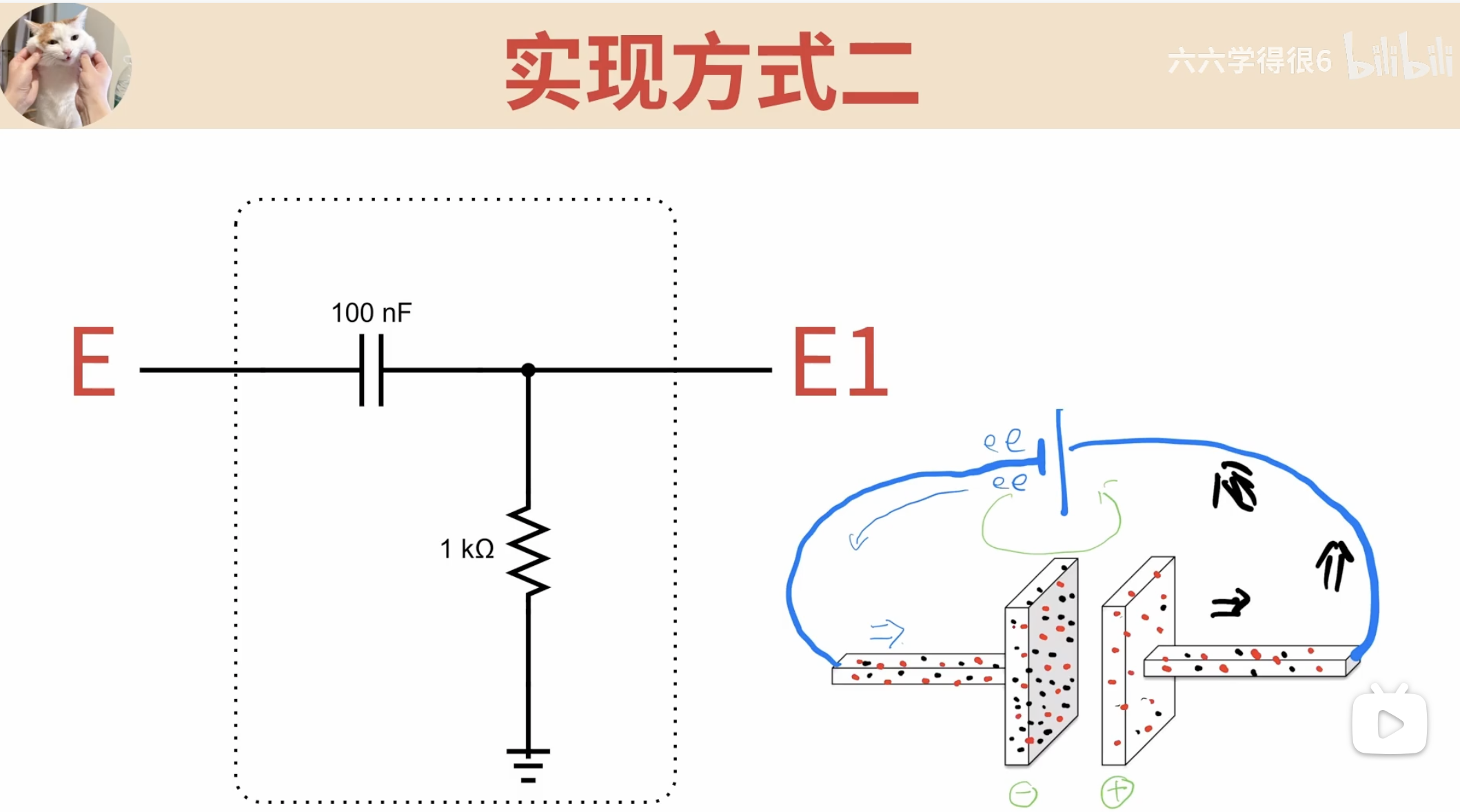

電容器

電容器可以簡單地理解為可以充電和放電的元器件

通常采用電容串聯電路實現RC電路從而準確控制電容充放電的時間

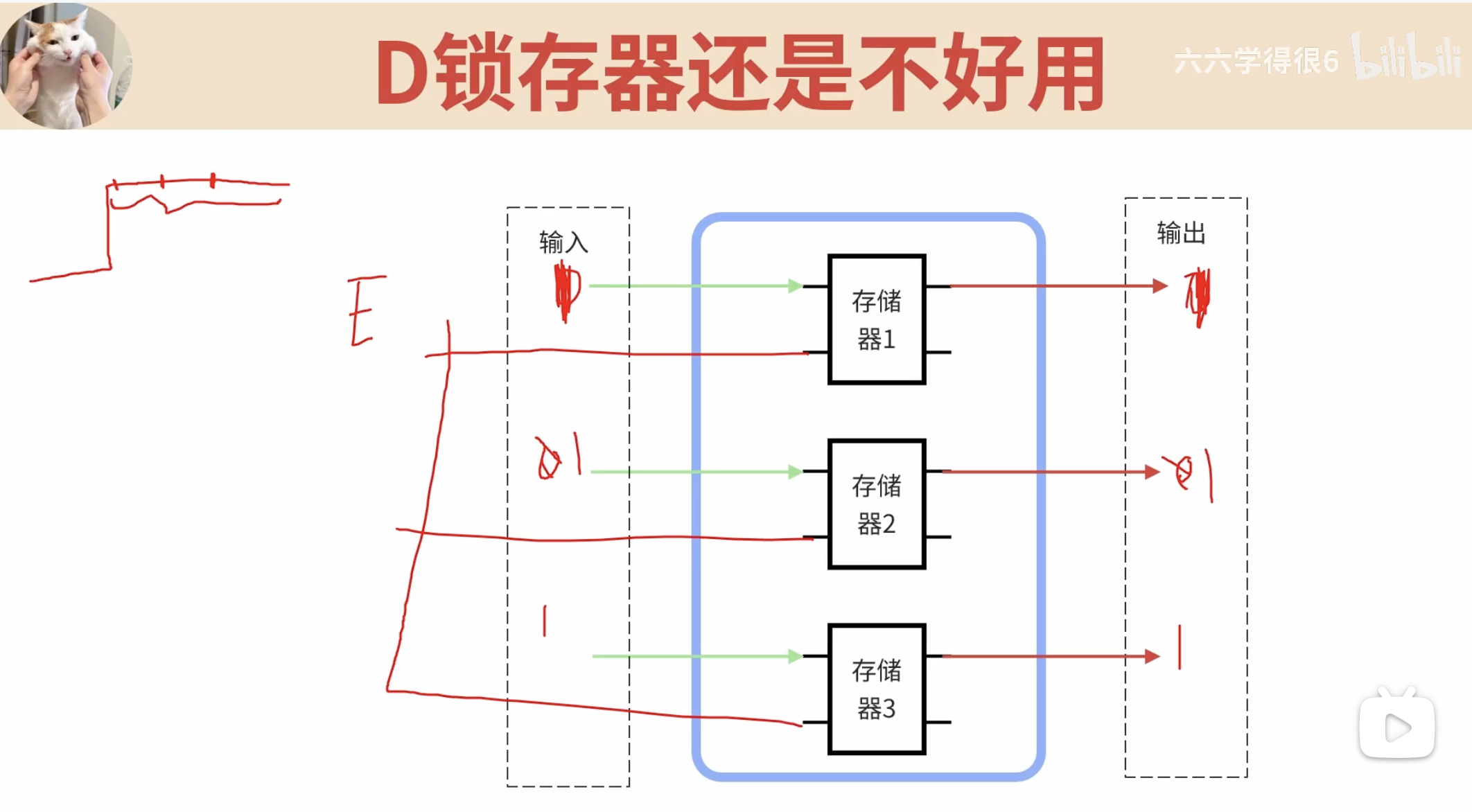

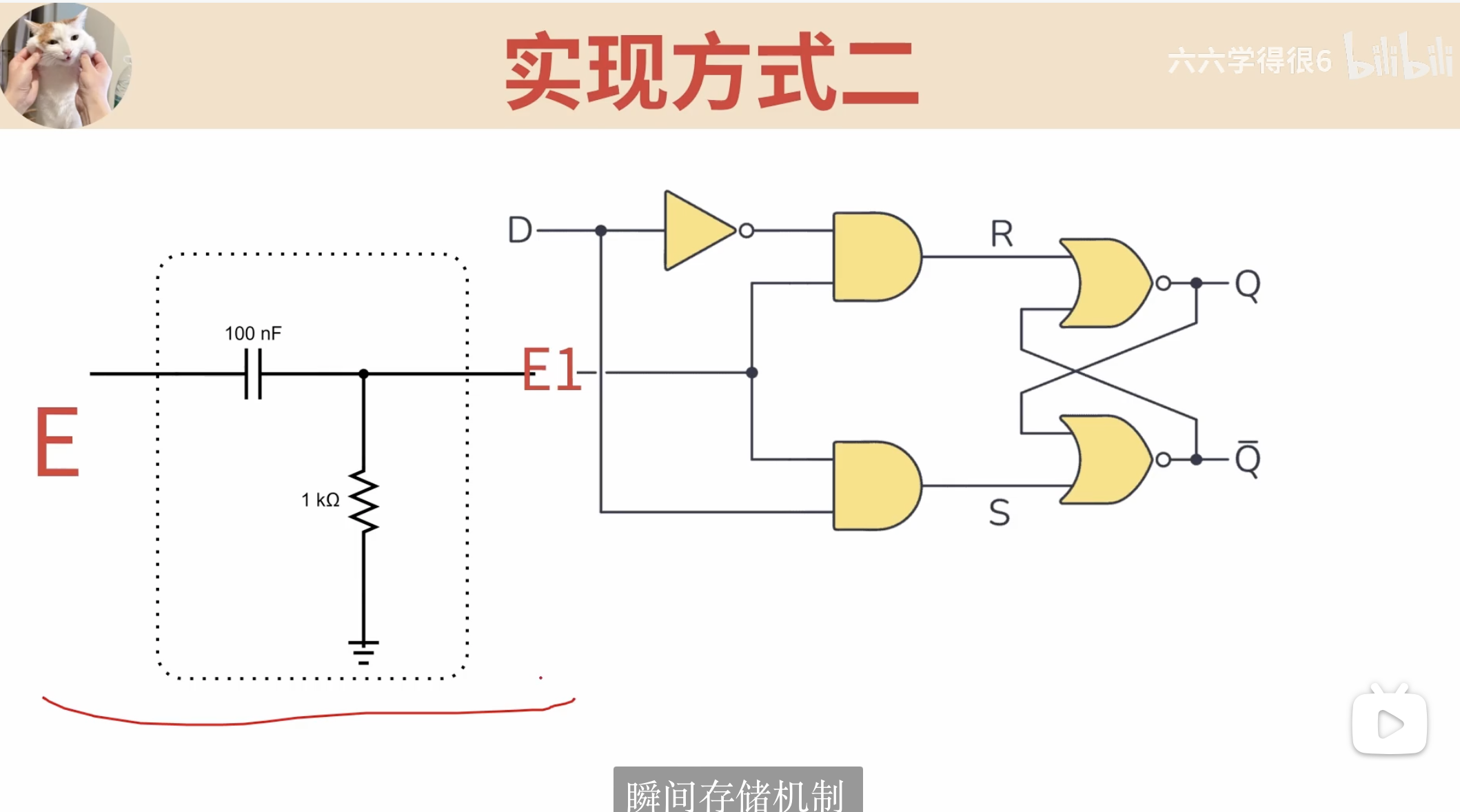

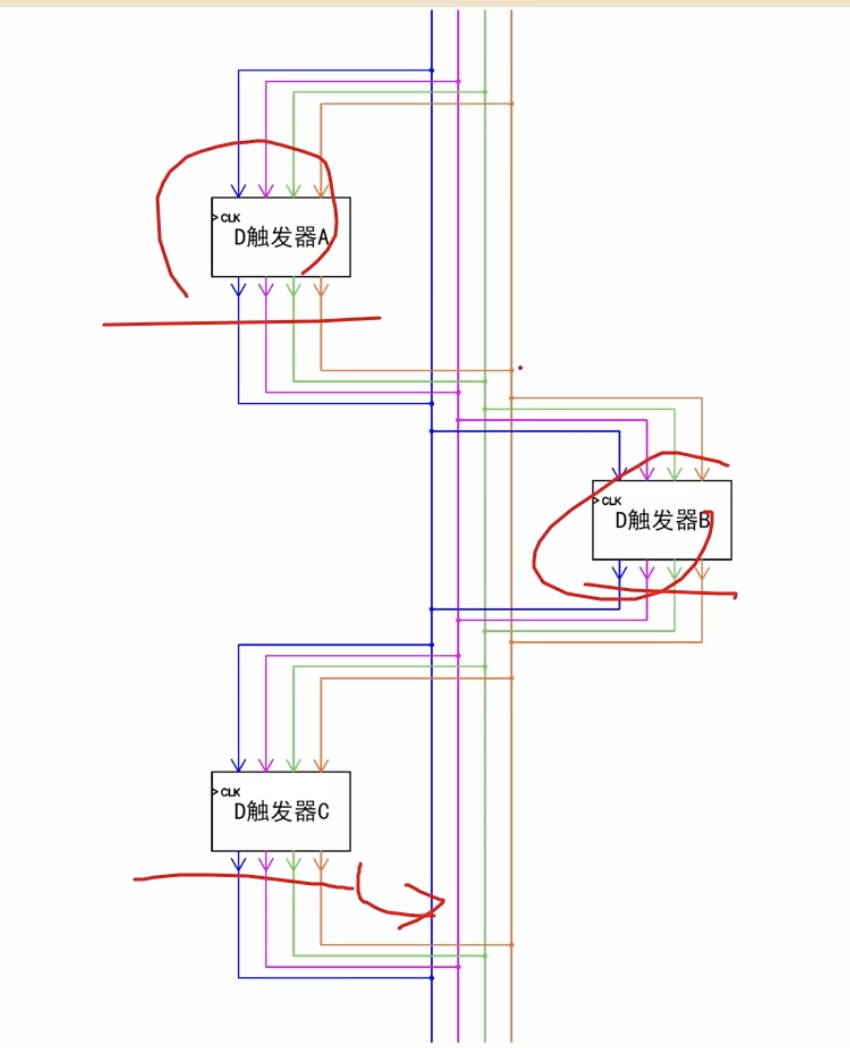

D觸發器

D鎖存器的缺點

由于在E使能端的控制下,由于當前單位時間內輸入時間內很長,很容易收到外界的影響,當某個輸入任意一個改變了,輸入會變得不穩定,因戲需要在一瞬間存儲好時間,不給它誤差的機會

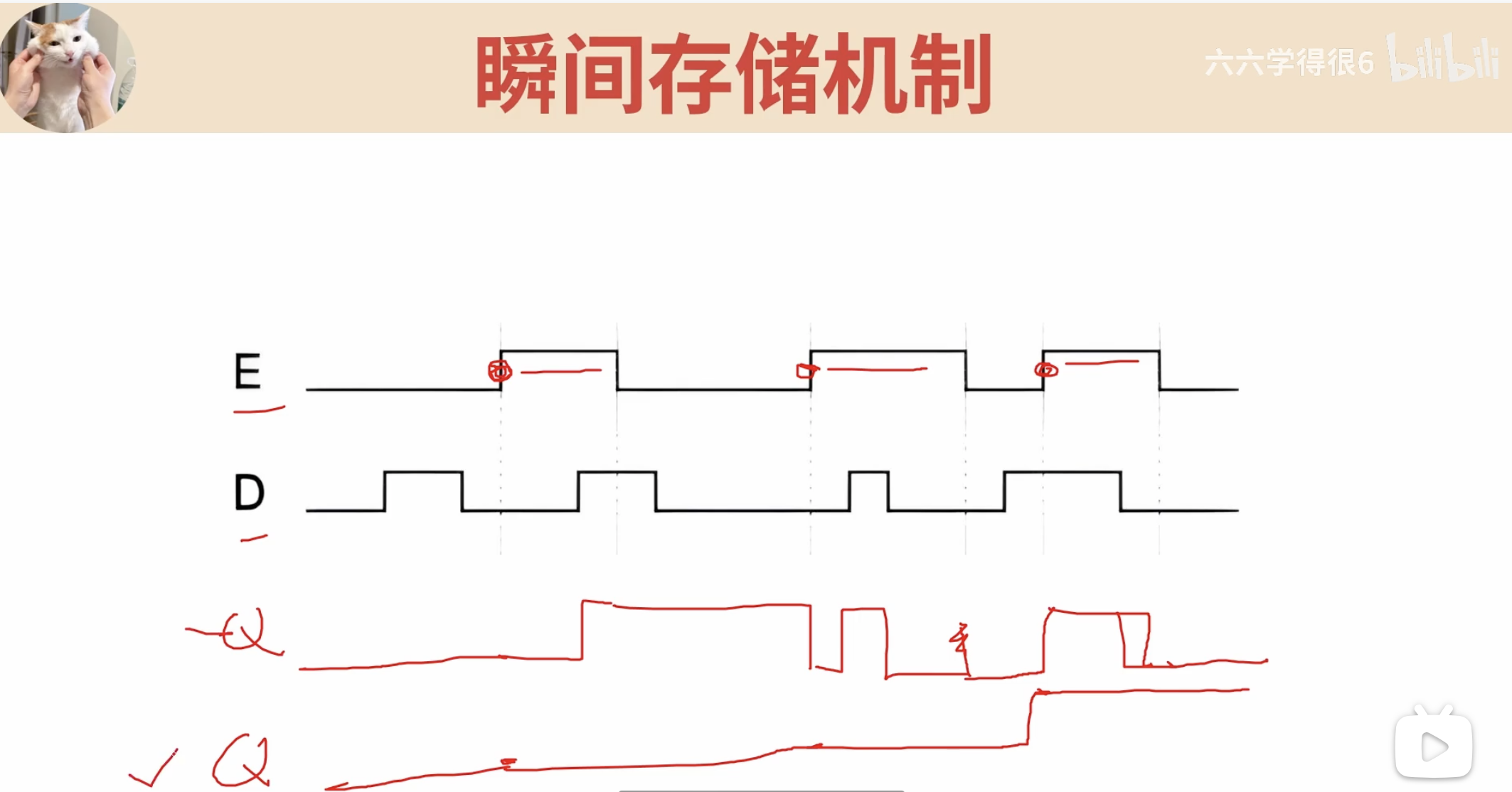

瞬間存儲機制

當E使能端=1的時候,Q會隨著D的輸入而同步輸出

但是現在需要在E=1的瞬間,保持D的輸入,其它的時間不變,因此理想的Q輸出為最后一條Q,而不是倒數第二條Q

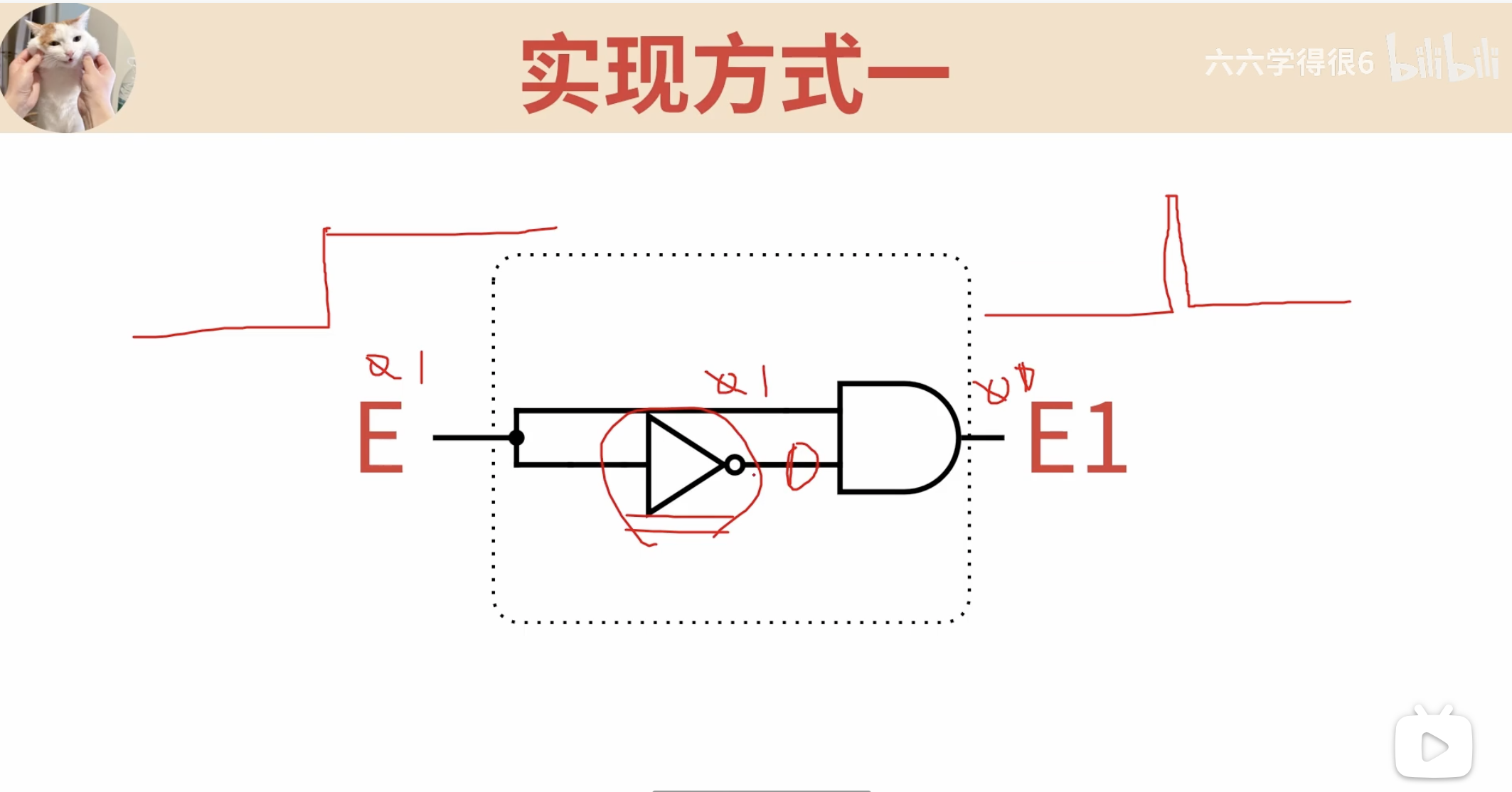

門電路實現

當E=1的時候 通過非門和與門 ,與門上邊輸入=1,下邊輸入由于非門的時間延遲仍然=1,因此E1=1

當時間延遲過了,與門的第二個輸入變成了0,因此E1=0,因此實現了瞬間存儲功能

但這個非門的延遲時間不可控

基于電容實現

利用電容的特點完成瞬間存儲

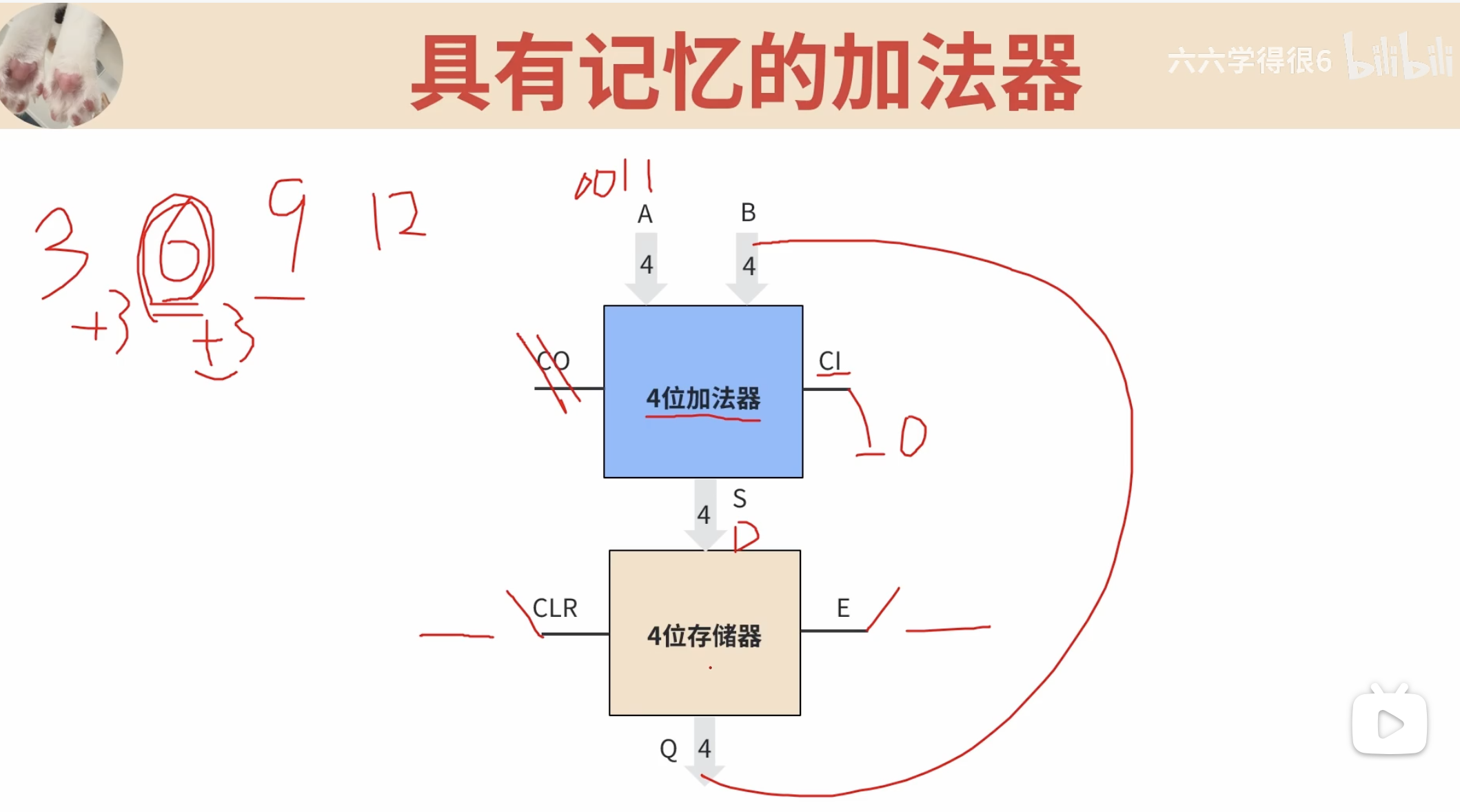

具有記憶的加法器

原理為將具有記憶的存儲器的輸出端再接回道加法器的輸入端

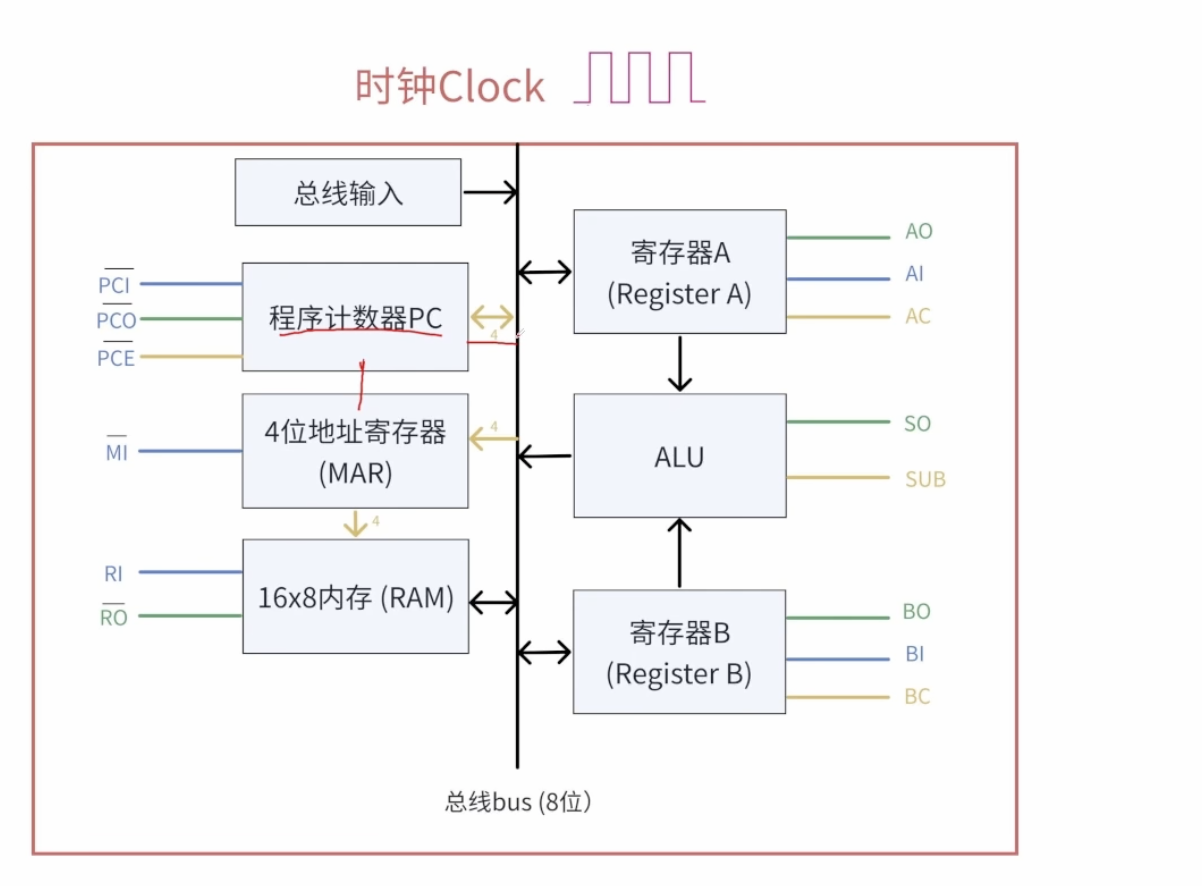

時鐘原理

時鐘主要用來計算機內部的觸發協作,比如計算機在哪個時間節點做哪些操作

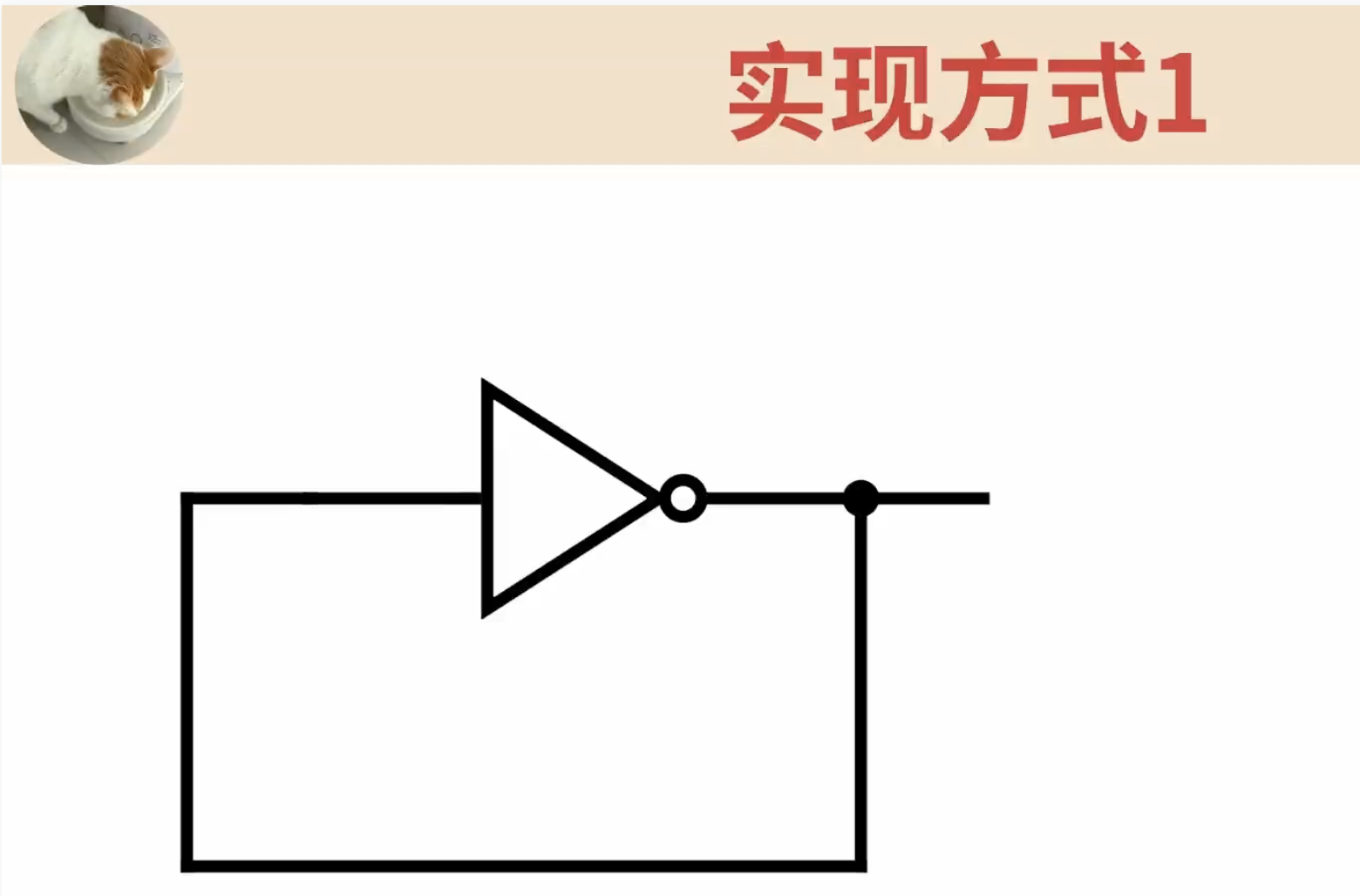

非門實現的時鐘,當一開始輸入=1,輸出=0,輸出0又返回到輸入通過非門,此時輸出就變成了1,循環往復輸出的規律=> 0、1、0

但0和1持續的時間不可控

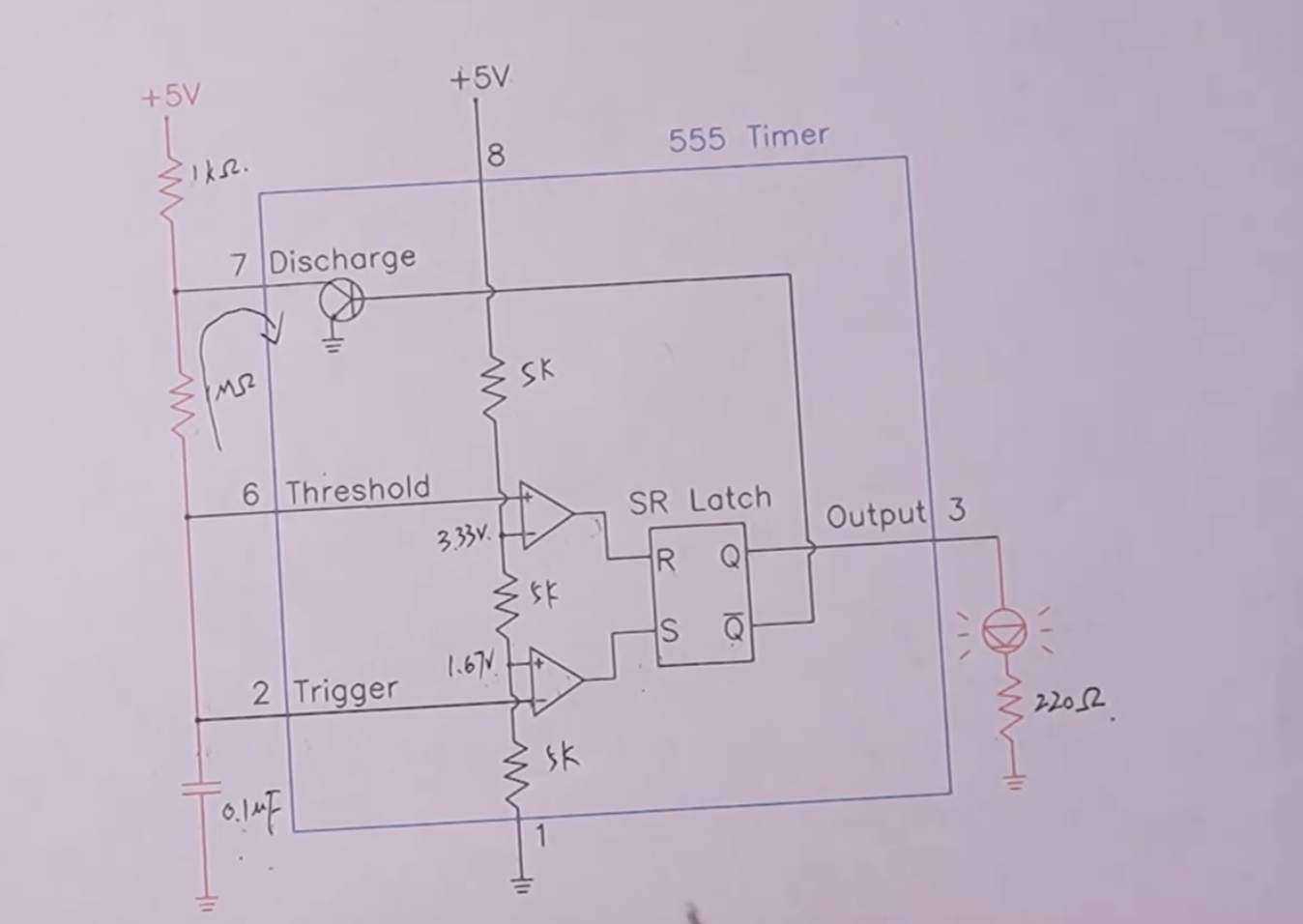

因此還有更好的實現,即通過555觸發器來實現

其中內部用到了很重要的電容RC電路定時充放電,同時利用了比較器,當正極電壓大于負極電壓才會導通,具體的原理可以參考555的原理

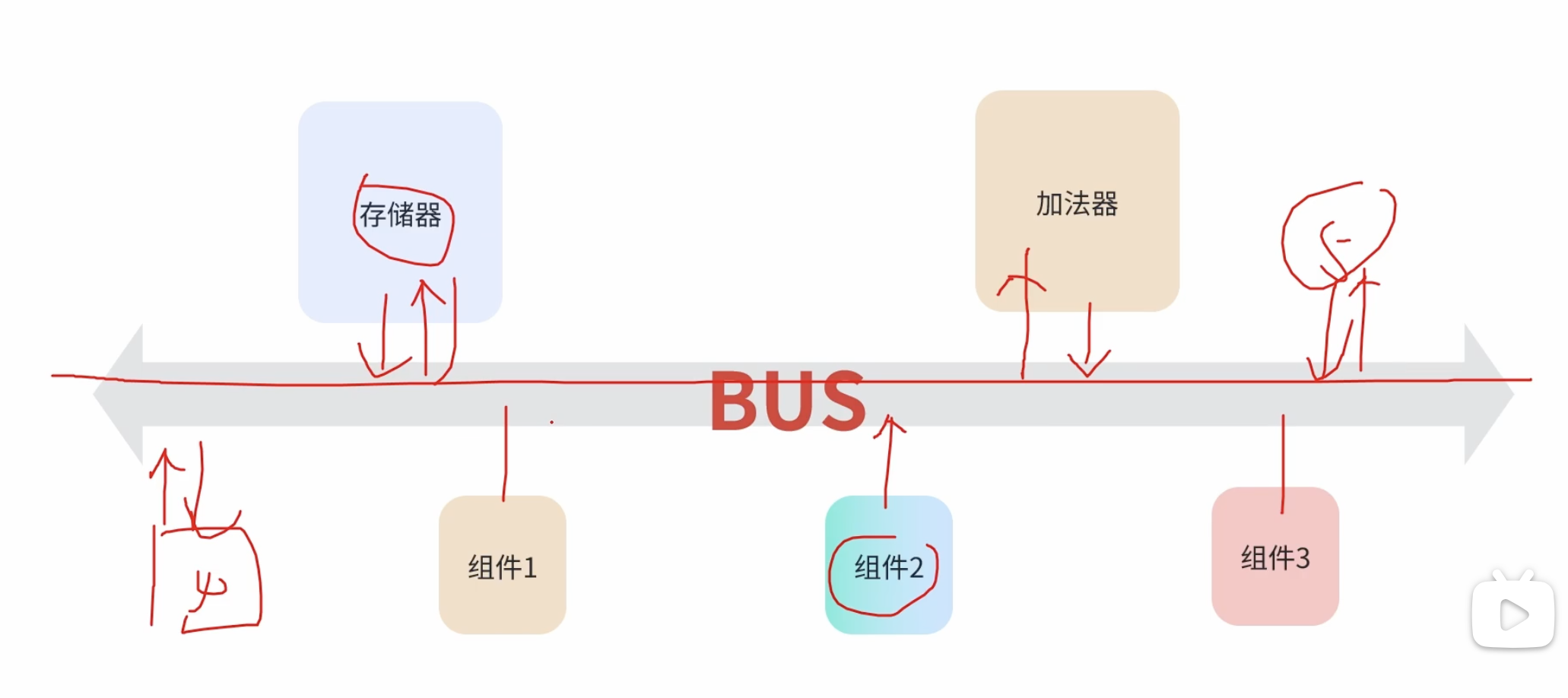

總線原理

簡單地來將,總線即為了統一管理計算機內部所有的元器件,各個存儲器、寄存器、內存等通過總線來傳遞數據,部分元器件輸出數據到總線,部分元器件接受總線數據的輸入

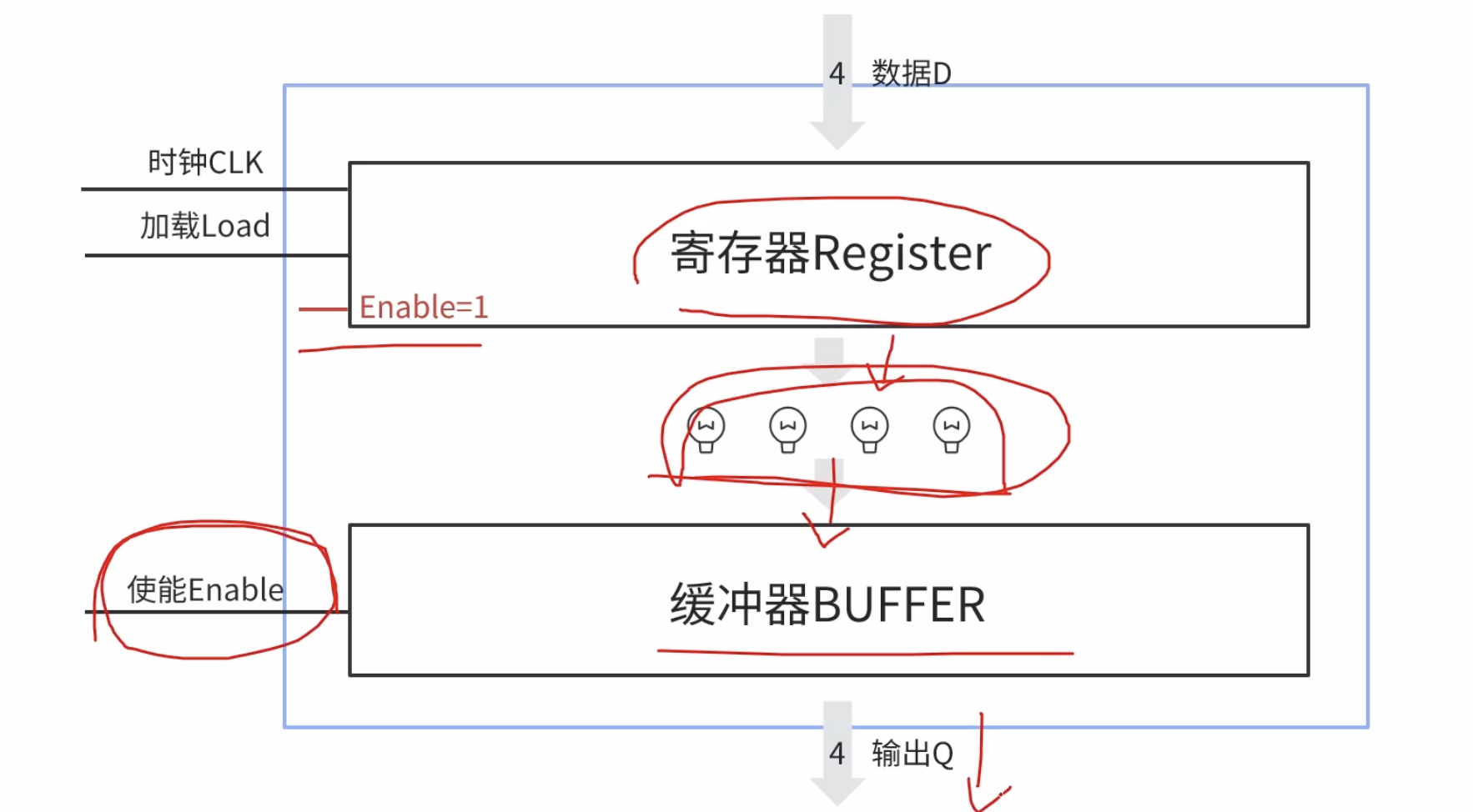

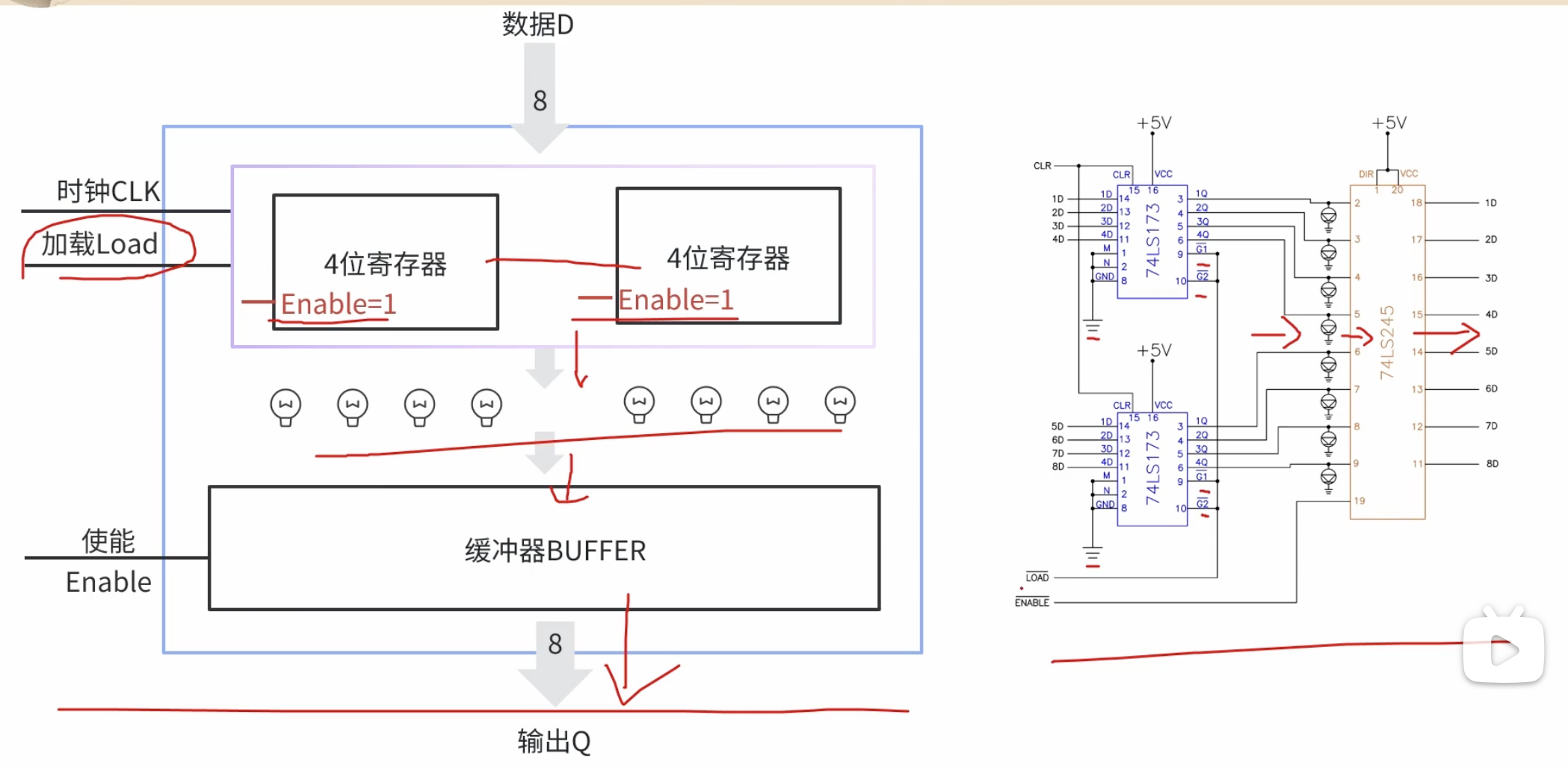

寄存器

D觸發器存在的問題一:眾多觸發器,誰來讀取此時的總線數據呢,之前的D觸發器無法實現控制制定觸發器誰來接受總線數據

解決問題一:因此在原有的觸發器加上load加載端,當load=1,觸發器接受總線數據,load=0,觸發器不接受總線的數據

D觸發器存在的問題二:眾多觸發器都輸出了數據,此時輸出哪個觸發器的數據到總線呢

解決問題二:在觸發器加上enable輸出使能端,當enable=1的時候觸發器才輸出數據到總線

改良的觸發器稱之為寄存器

但此時的寄存器還存在如下問題:

- 無法觀察到每個寄存器的輸入輸出到底是多少

- 有效位數太少了,輸入輸出只有4位

解決怎樣觀察輸入輸出:加上緩沖器,在緩沖期和寄存器之間加上燈泡,用燈泡觀察寄存器的存儲數據

解決有效位數太少:串聯多位寄存器解決

ALU

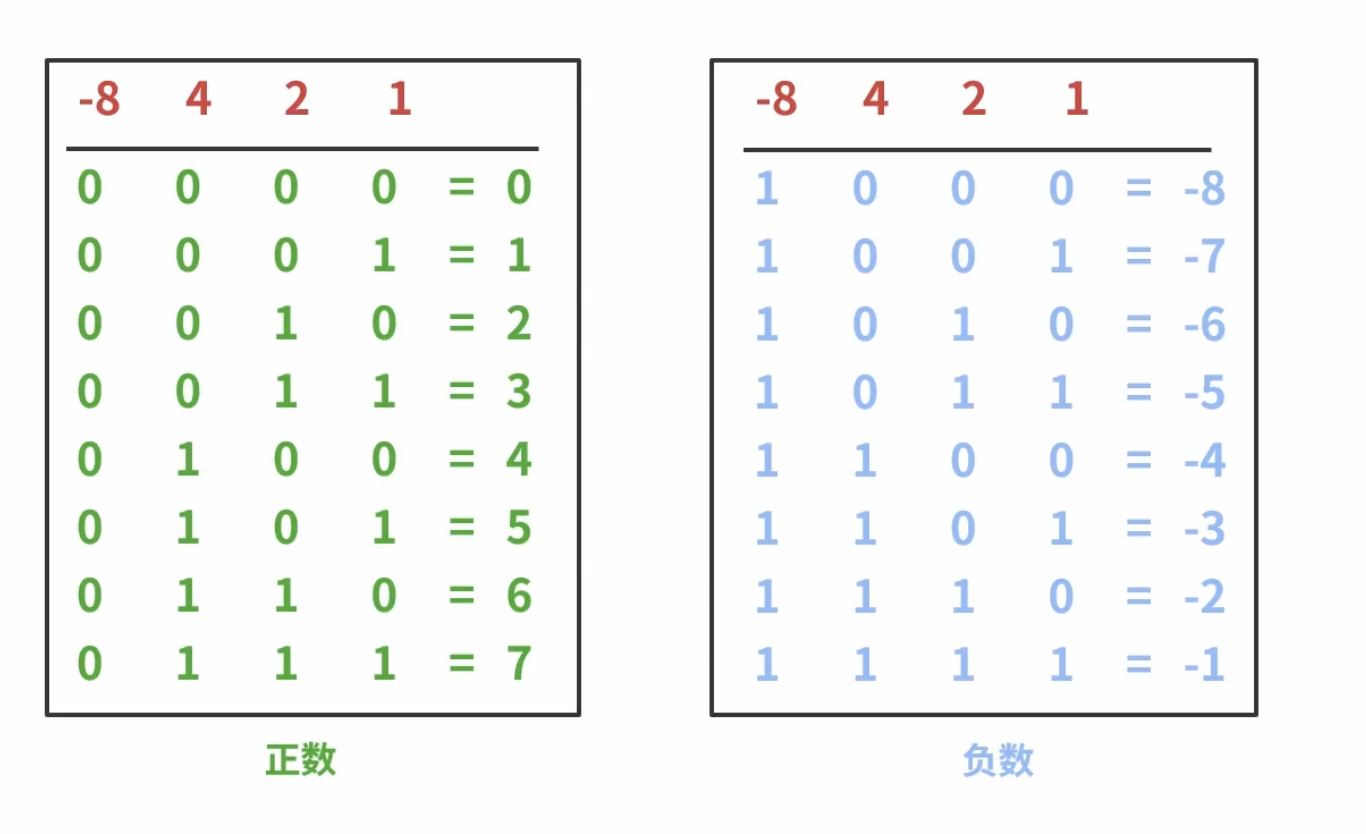

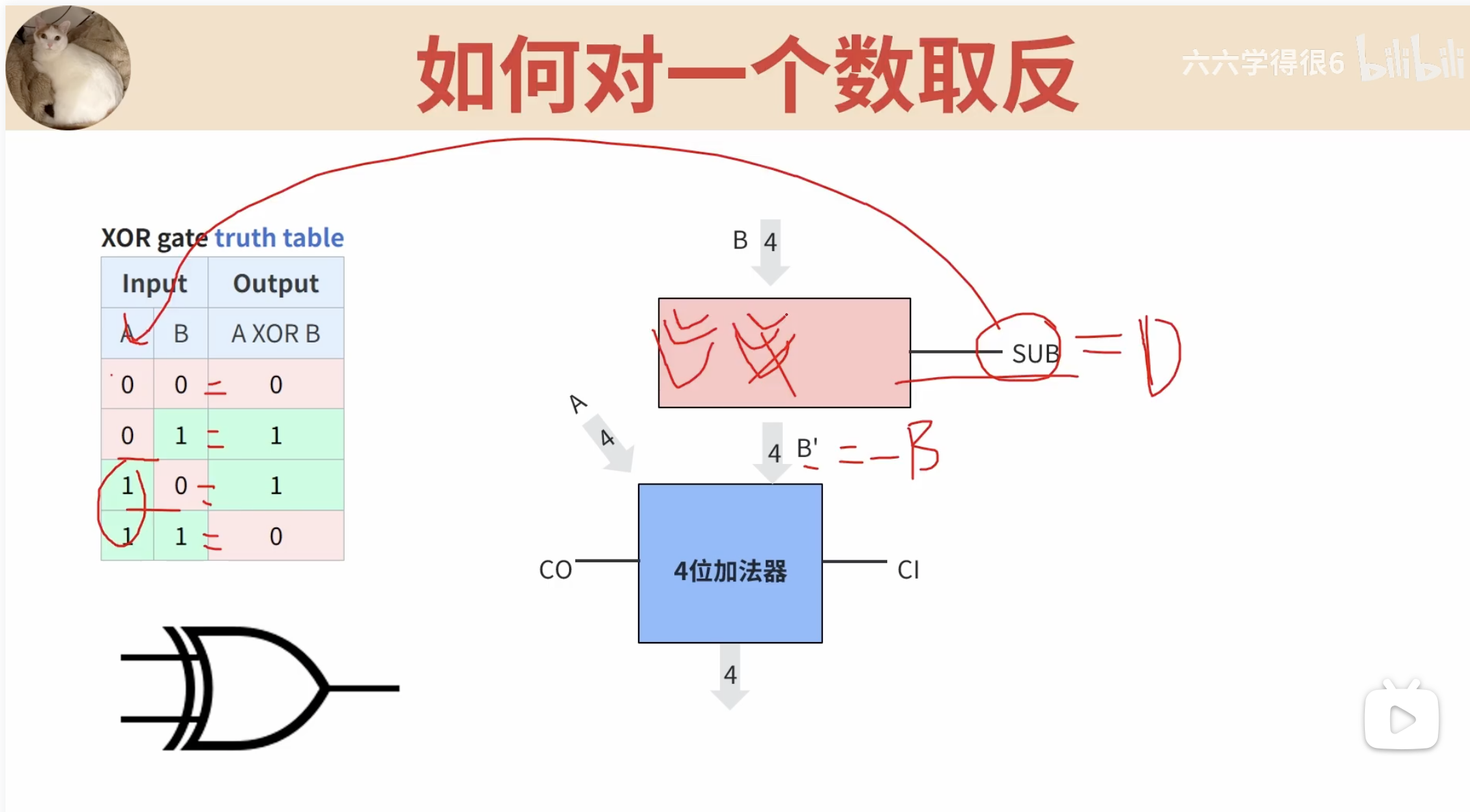

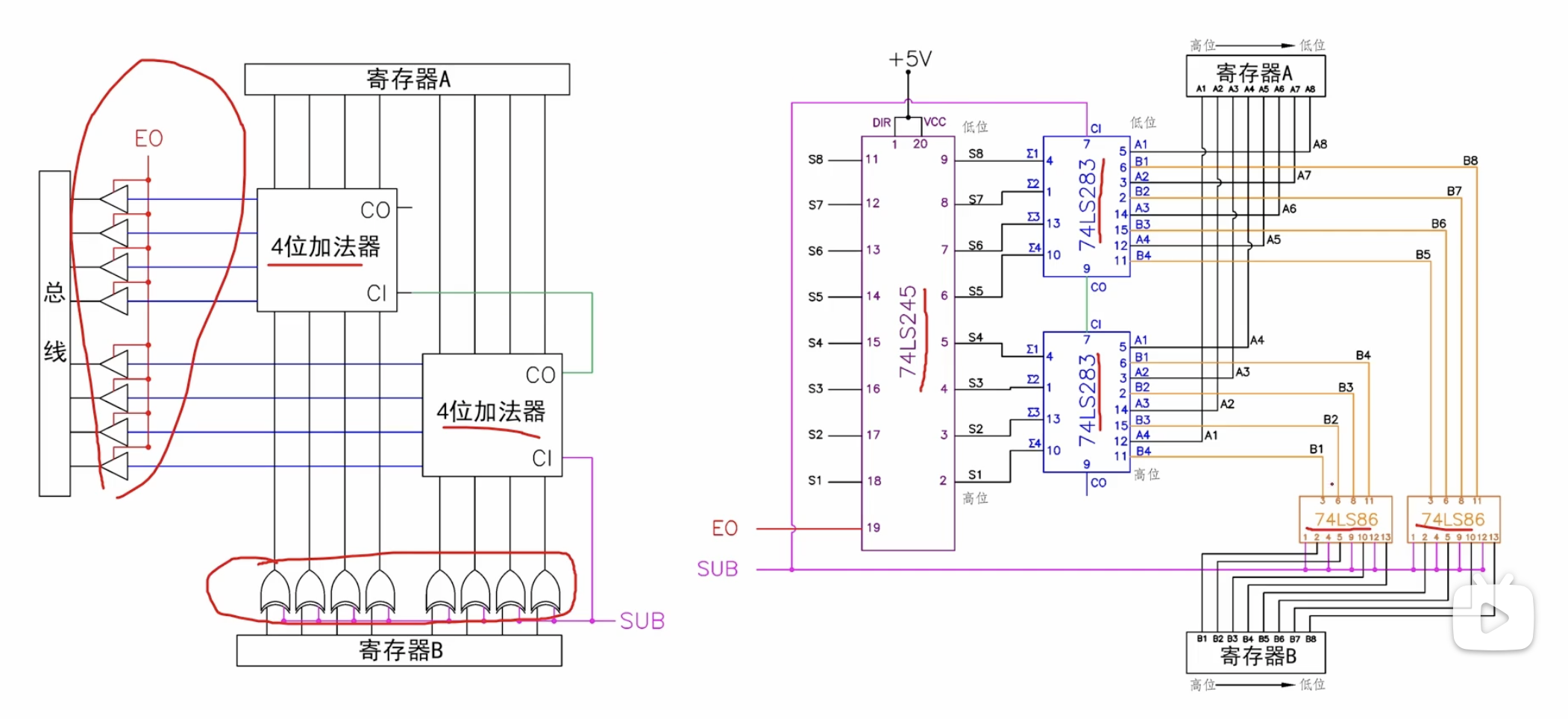

ALU即算數邏輯單元,之前已經實現了加法,ALU包括加減乘除,加法已實現,乘法和加法的本質原理差不多,減法和除法本質原理差不多,則當前只需解決怎樣實現減法功能

例如,6-2 可以換成 6+ (-2) 此時它仍然為加法,重點在于怎樣把2變成-2

規定最高位等于負數,比如4位二進制,最高表達-8,此時的二進制則可以表達負數

舉例:6-2

6=0110 -2=1110

6-2= 0100 此時算出來=4

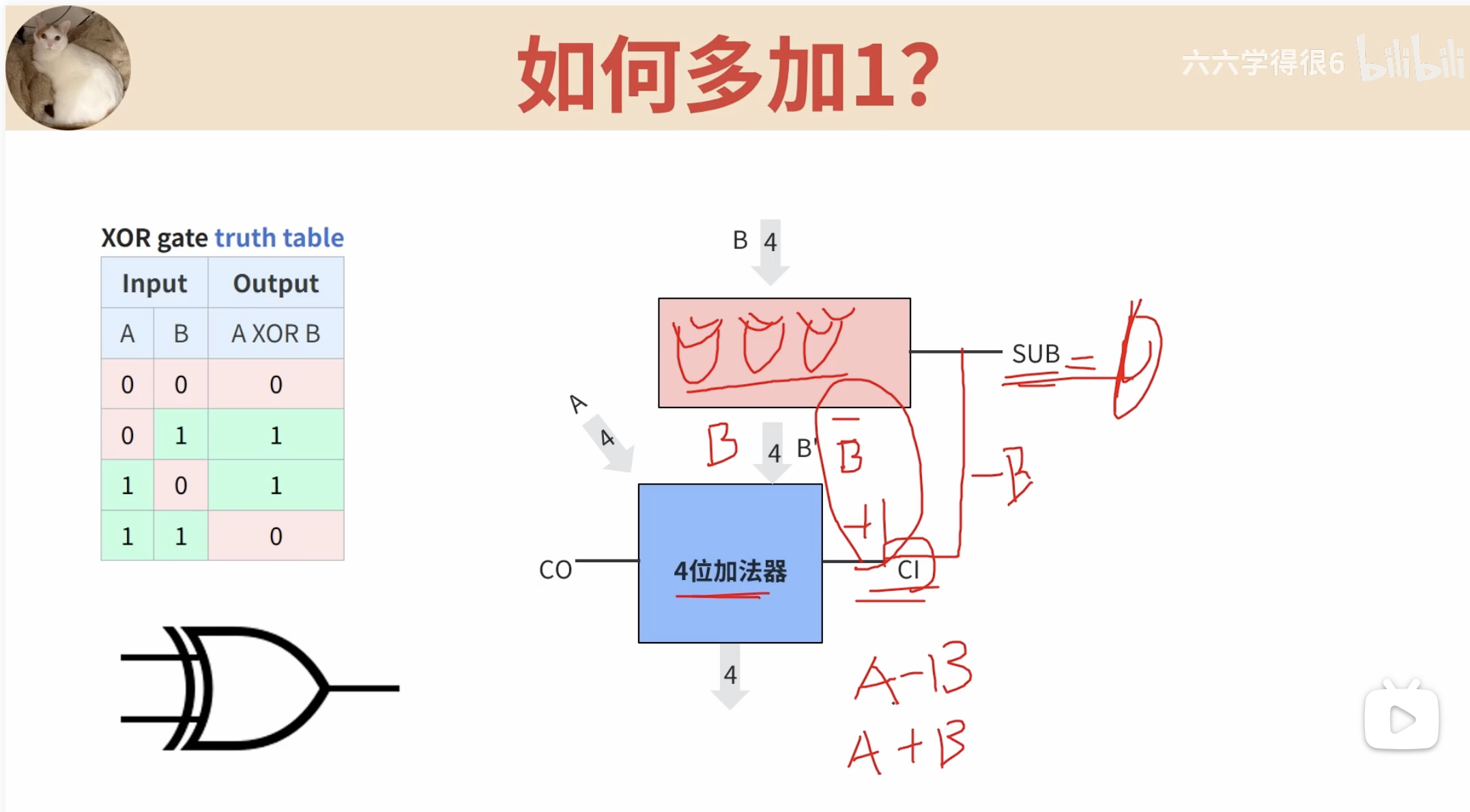

規律:負數二進制=正數取反+1

取反:采用異或門+sub控制端實現

+1操作:sub的輸出直接接到Cl端,sub=1 即計算減法

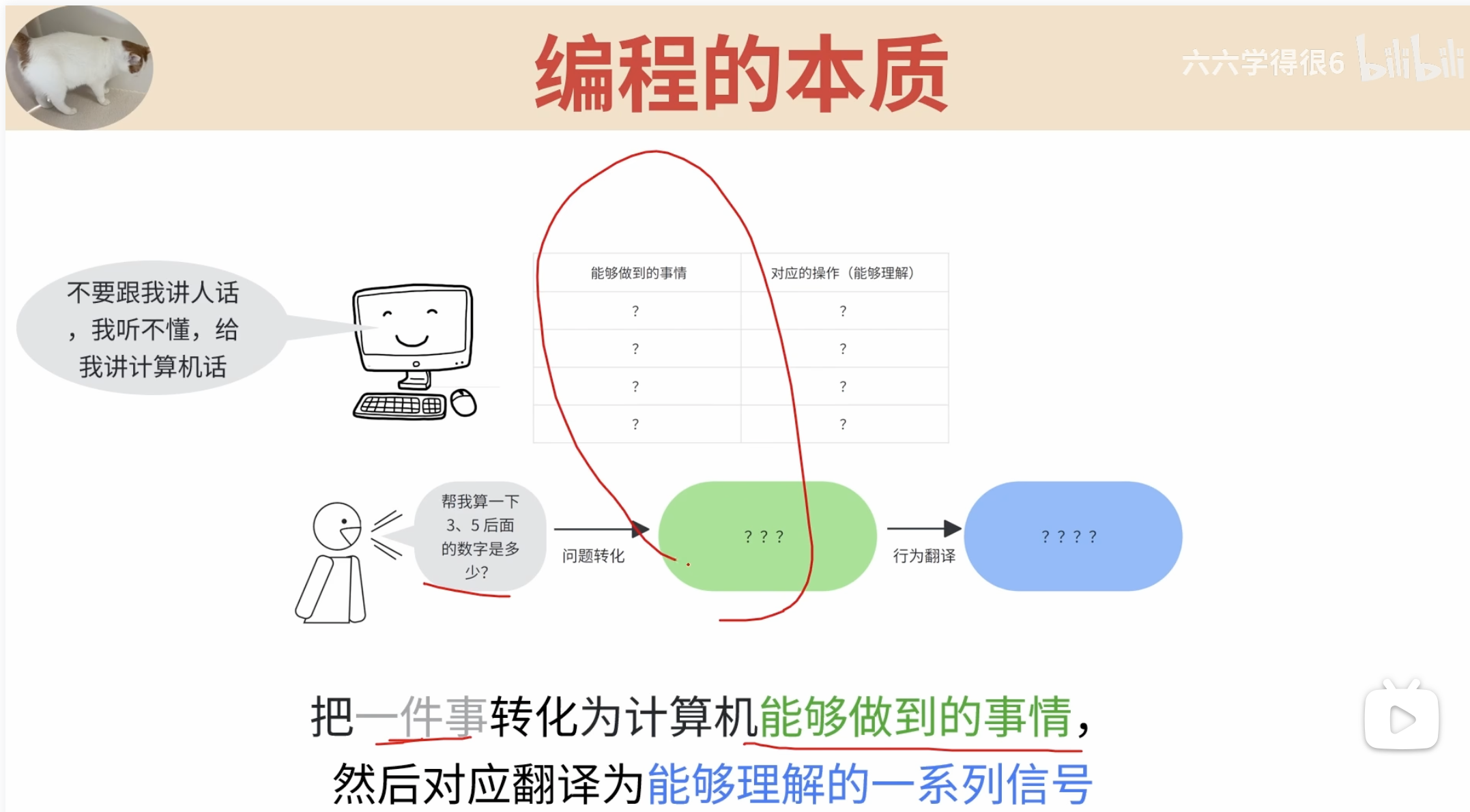

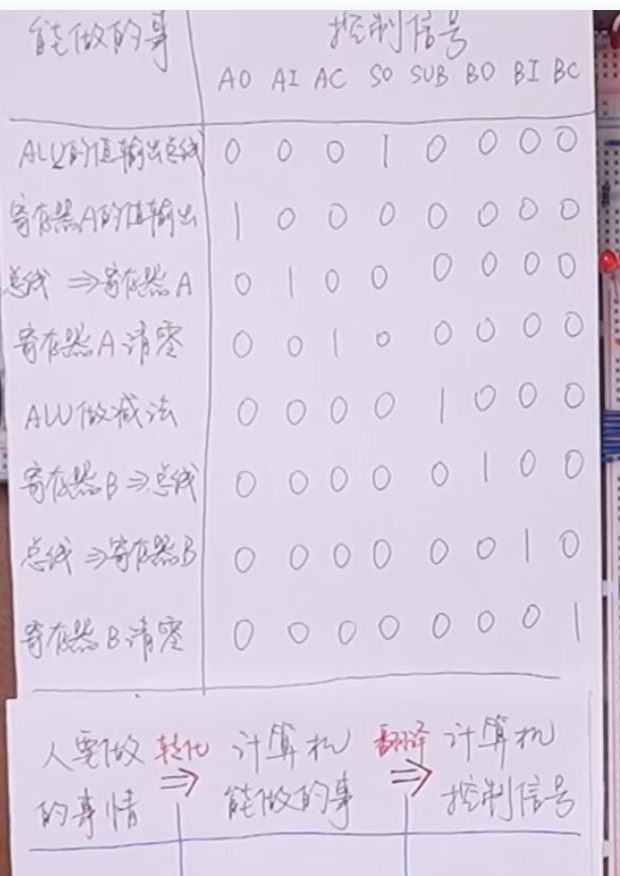

編程的本質

把計算機能夠做的事情翻譯成計算機能夠理解的二進制

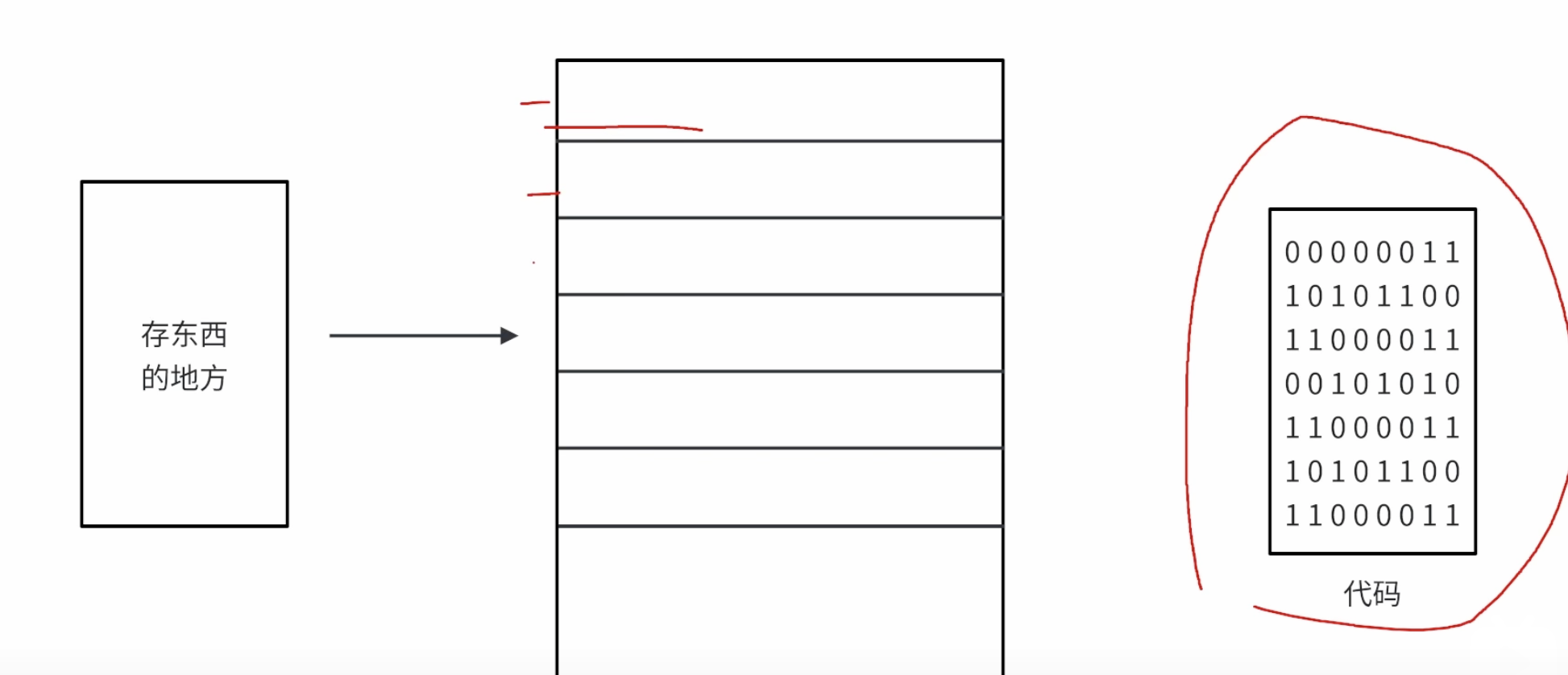

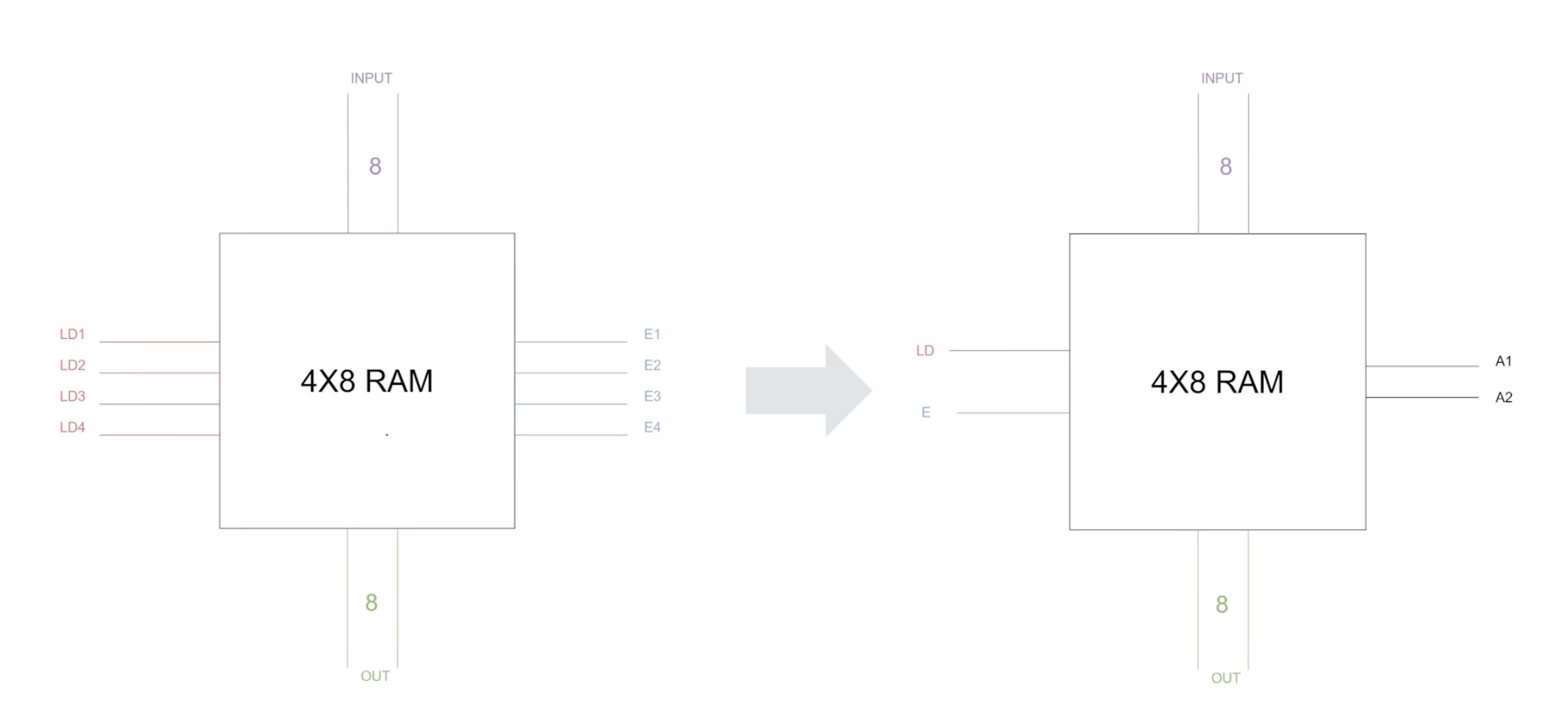

內存

指令得存儲在某個地方,給到后續某個元器件來讀取

但由于需執行的8代碼存在很多行,因此可以把多個寄存器串聯在一起來實現

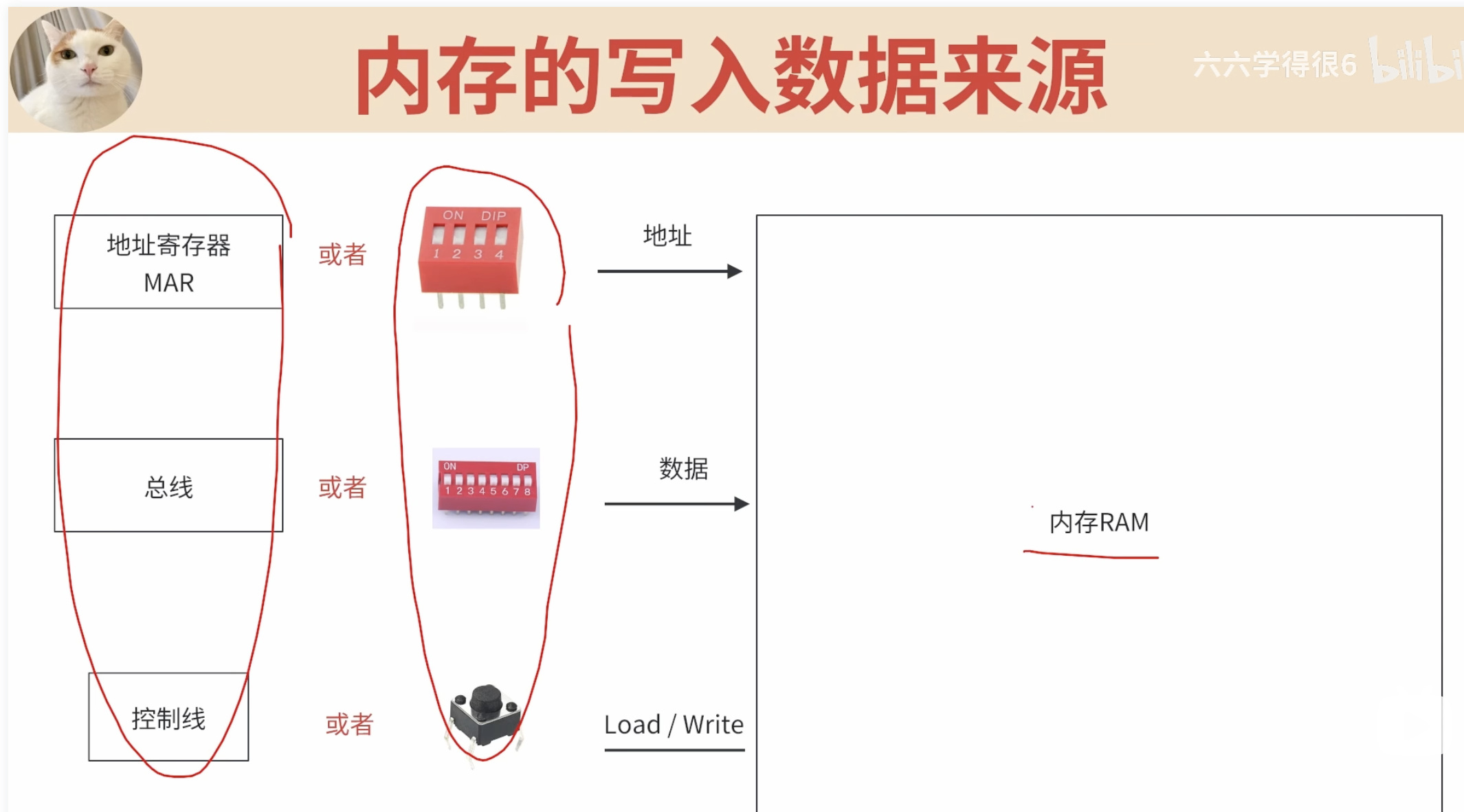

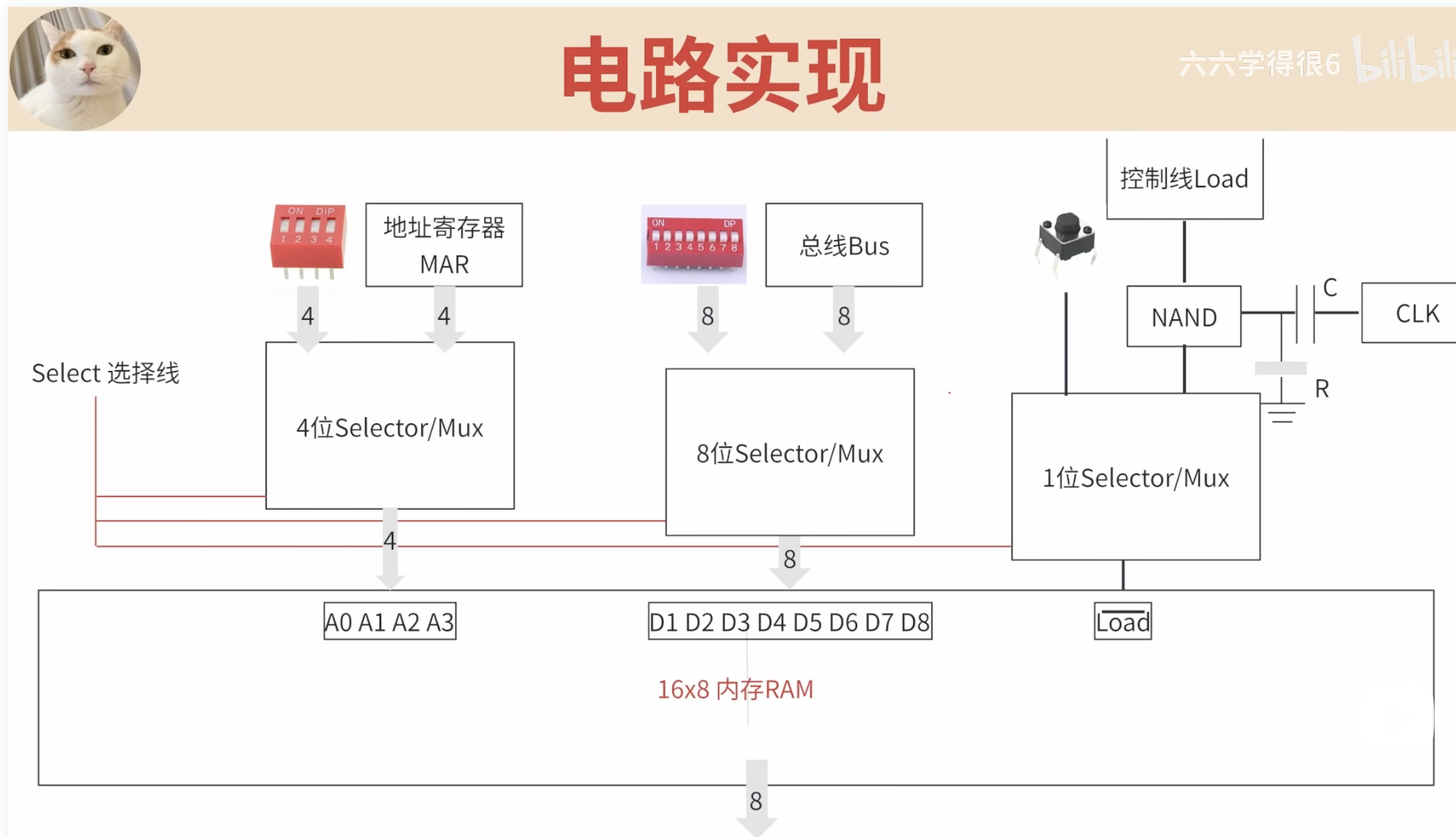

內存的數據來源

數據來源

地址寄存器:存儲來自于哪里的數據地址

總線:從總線獲取數據輸入

控制線:控制加載數據還是寫入數據

但怎樣區分這不同的輸入源呢

可以使用多路選擇器控制采用哪里的輸入數據

最后內存實現電路

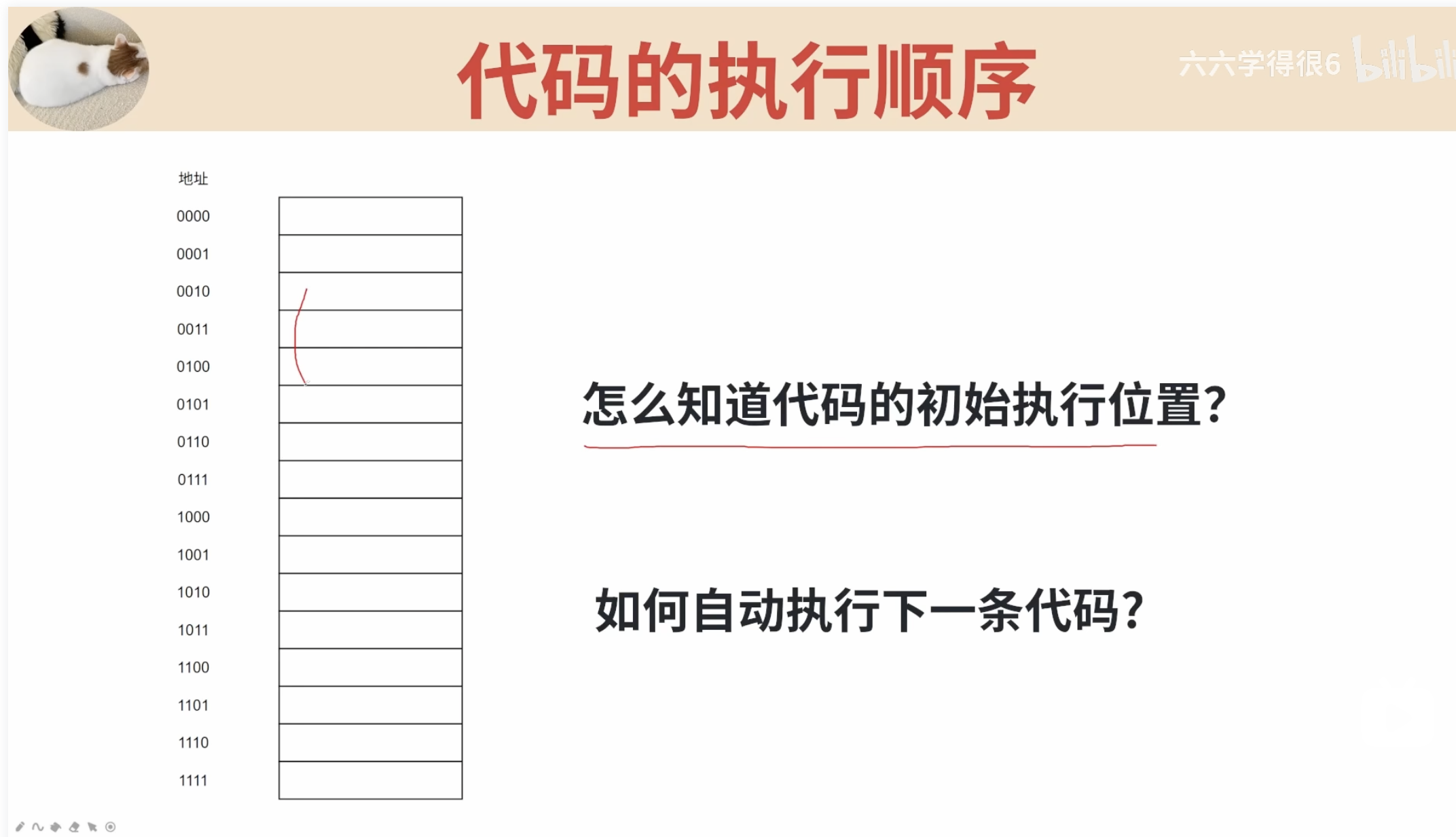

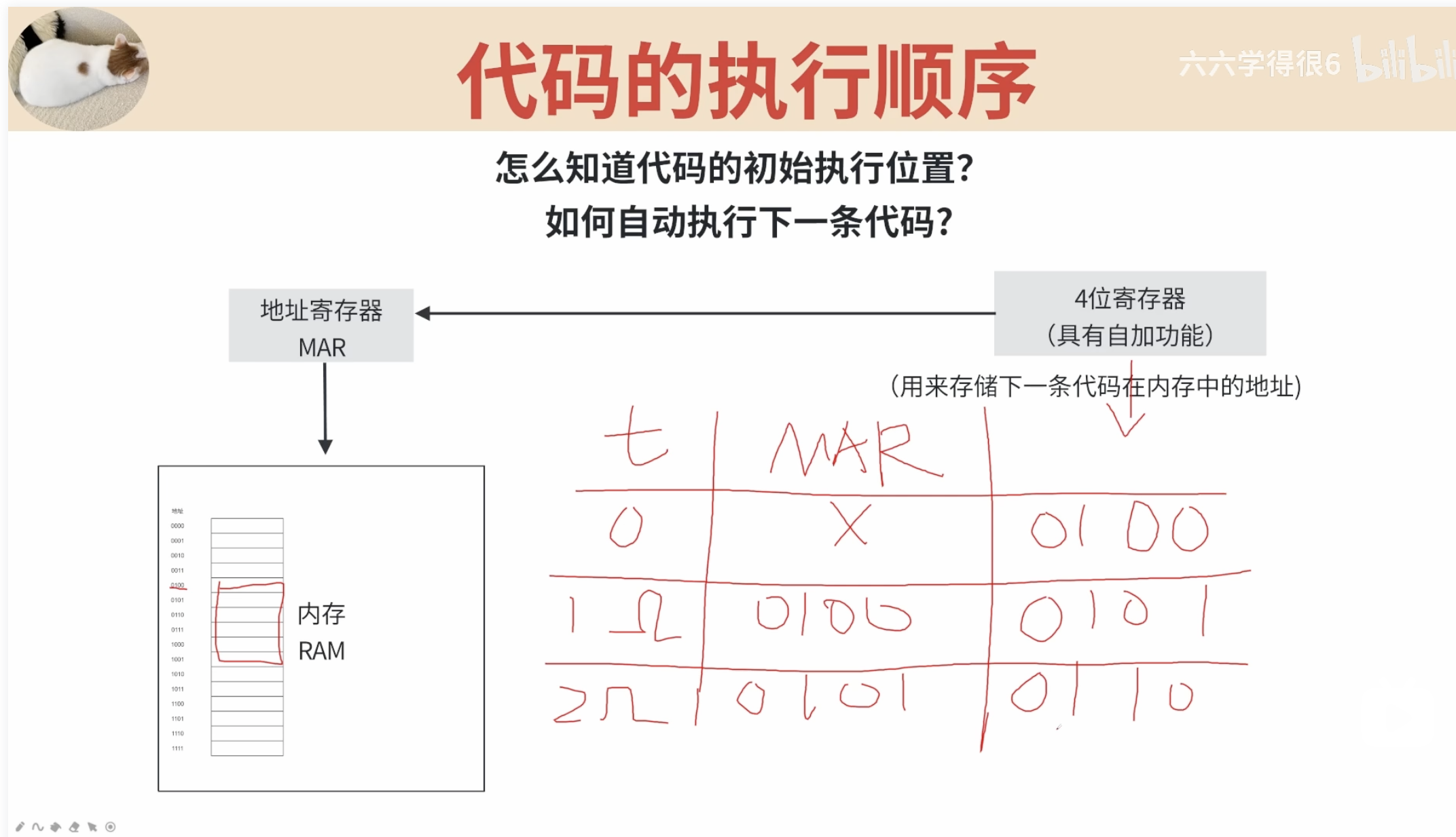

程序計數器 PC

計算機在執行邏輯的時候,執行完的當前數據怎樣知道下一條呢

這個時候需要1個元器件:程序計數器,記錄下一條執行邏輯的地址

可以存儲位置以及能夠自加一操作

完整計算機結構

參考:B站從零搭建計算機教程

---層序遍歷二叉樹)

)

對北半球光伏數據進行時間序列預測)