目錄

一、概覽

二、時序路徑

2.1 數據路徑

2.2 時鐘路徑

2.3 時鐘門控路徑

2.4 異步路徑

2.5 關鍵路徑

2.6 False路徑

2.7?單周期路徑

2.8?多周期路徑

2.9?最長路徑和最短路徑

三、參考資料

一、概覽

??????????靜態時序分析通過模擬最差條件下分析所有的時序路徑,報告出存在違例的路徑,來驗證設計的時序性能是否滿足要求。

??????????相比動態分析的模擬仿真,靜態時序分析因為不需要大量的測試向量,分析更快,再者因為是分析所有的時序路徑,分析結果齊全,單缺點是只能分析時序結果,無法驗證設計功能的正確性。靜態時序分析主要有三個流程:設計連接劃分為一系列的時序路徑,計算每一條路徑的信號傳輸時延,檢查時序約束下違例的路徑。

二、時序路徑

??????????時序路徑可以根據信號的類型分為不同的路徑,如數據路徑,時鐘路徑,時鐘門控路徑,異步路徑等。每一條時序路徑都有一個起點和一個終點,不同時序路徑類型的起點和終點存在些差異,一般起點是設計中由發送時鐘邊沿觸發的位置,終點是設計中數據由起點發出,經過組合邏輯后由捕獲時鐘邊沿觸發接收的位置。

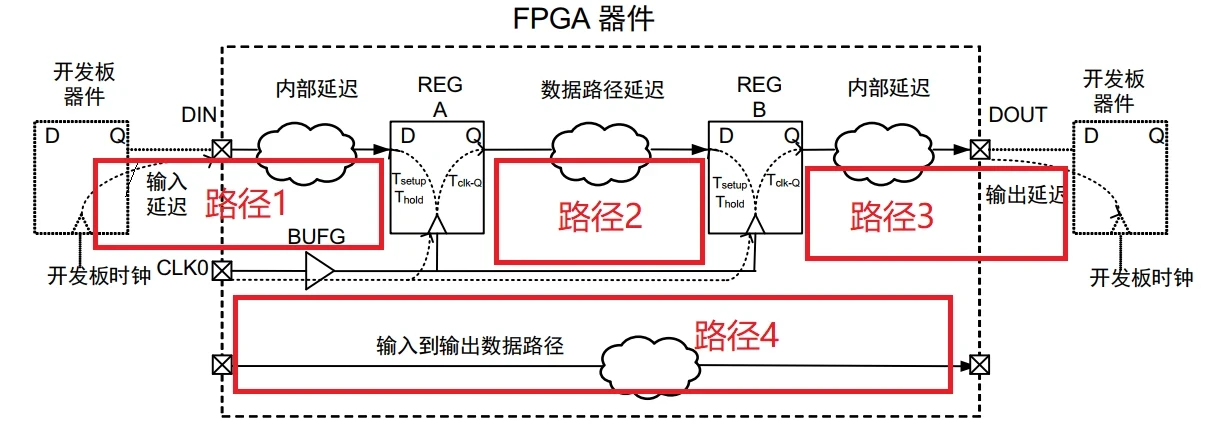

2.1 數據路徑

??????????數據路徑中起點可以是設計的輸入端口(輸入數據可以由芯片外部時鐘發送),或者是時序單元的時鐘引腳,終點可以是時序單元的數據端口或設計的輸出端口(由芯片外部的時鐘捕獲數據)。下圖是根據起點和終點單元類型對時序路徑的分類。

由上圖可知,數據路徑有四種類型

路徑1:外部器件通過輸入端口DIN到FPGA內部的寄存器單元REG?A

路徑2:輸入寄存器REG A到輸出寄存器REG B?

路徑3:FPGA內部寄存器REGB的數據通過輸出端口DOUT輸出到芯片外部

路徑4:芯片輸入端口DIN到輸出端口DOUT間的路徑

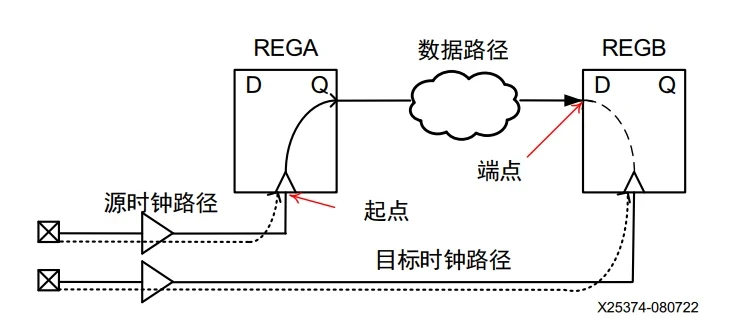

2.2 時鐘路徑

時鐘路徑中起點是時鐘輸入端口,終點是時序單元如觸發器,存儲器的時鐘引腳,以下圖為例,源時鐘路徑和目標時鐘路徑就是兩條時鐘路徑,終點分別是觸發器REGA和REGB的時鐘引腳。

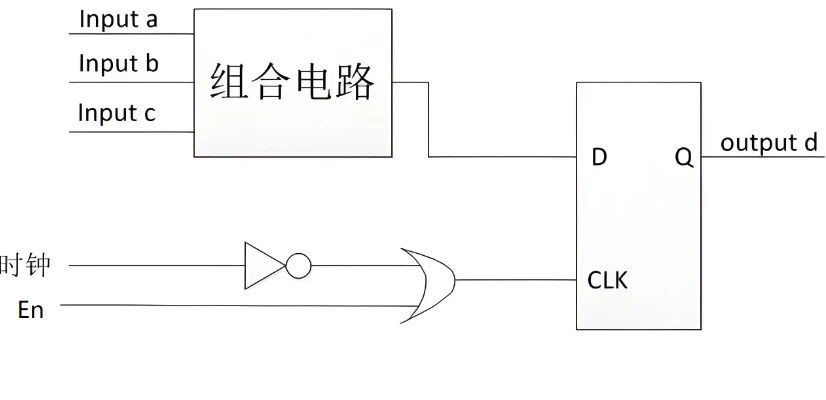

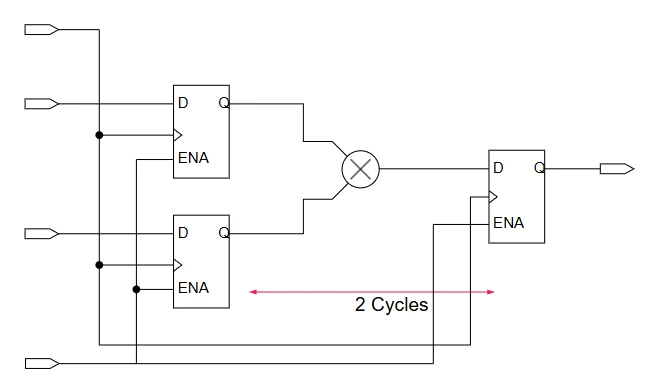

2.3 時鐘門控路徑

時鐘門控路徑中起點是設計的輸入端口,終點是時鐘門控單元的輸入端口,以下圖示例。輸入信號En不屬于時鐘的一部分,但是可以控制輸入時鐘信號是否能有效作用于CLK端口。這種路徑既不屬于時鐘路徑也不屬于數據路徑,成為時鐘門控路徑

2.4 異步路徑

異步路徑中起點是設計的輸入端口,終點是時序單元的異步復位,置位或清零引腳,異步信號不依賴于時鐘信號的有效沿。

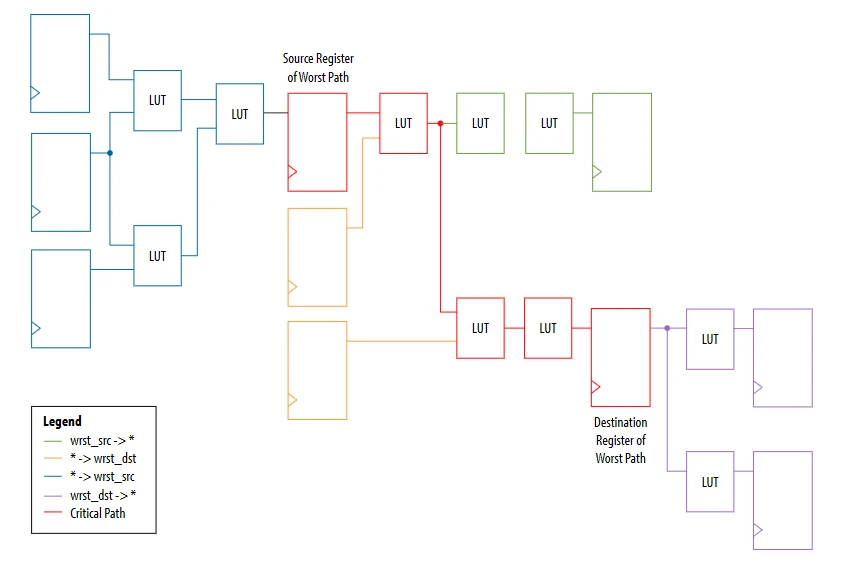

2.5 關鍵路徑

簡單理解,關鍵路徑就是延時最大的組合路徑,決定了設計正常運行時的最大頻率,也是時序敏感的功能路徑。關鍵路徑也是不滿足時序要求的路徑。綜合后時序分析工具就能報告出時序違例的路徑,看到違例路徑后首要做的是確認這些路徑是否屬于不用分析或者多周期的路徑。

在分析設計中的違例路徑時,了解關鍵路徑周圍的相互作用很有幫助。?要了解關鍵路徑上可能存在的拉動因素,可以使用以下 report_timing 命令。 在項目目錄中,運行 report_timing 命令查找關鍵路徑中的節點。?將以下代碼復制到 .tcl 文件中,并將前兩個變量替換為最差路徑的“起始節點”和“終止節點”列中的節點名稱。該腳本將分析最差源寄存器和目標寄存器之間的路徑。以下圖示例,設計的關鍵路徑以紅色顯示。

set wrst_src <insert_source_of_worst_path_here>

set wrst_dst <insert_destination_of_worst_path_here>

report_timing -setup -npaths 50 -detail path_only -from $wrst_src \

-panel_name "Worst Path||wrst_src -> *"

report_timing -setup -npaths 50 -detail path_only -to $wrst_dst \

-panel_name "Worst Path||* -> wrst_dst"

report_timing -setup -npaths 50 -detail path_only -to $wrst_src \

-panel_name "Worst Path||* -> wrst_src"

report_timing -setup -npaths 50 -detail path_only -from $wrst_dst \

-panel_name "Worst Path||wrst_dst -> *".tcl 腳本與圖形之間的關系如下: 前兩行顯示了關鍵路徑兩個端點內部的所有內容,這些路徑將它們拉向不同的方向。 第一個 report_timing 命令分析源驅動的所有路徑,以綠色顯示。 第二個 report_timing 命令分析通往目標的所有路徑,包括關鍵路徑,以橙色顯示。?最后兩個 report_timing 命令顯示了端點外部的所有內容,這些路徑將它們拉向不同的方向。 如果這些相鄰路徑中的任何一條在關鍵路徑附近有松弛,則過濾器會平衡這些路徑與關鍵路徑,以嘗試實現最佳松弛。

2.6 False路徑

對于設計中實際存在,但邏輯功能不正確的路徑,沒有數據從起點到終點,這種沒有時序要求的路徑成為False路徑。因為時序分析工具默認會分析所有的路徑,對于False路徑,需要約束為False path,否則會因優化時序結果而增加運行時間。

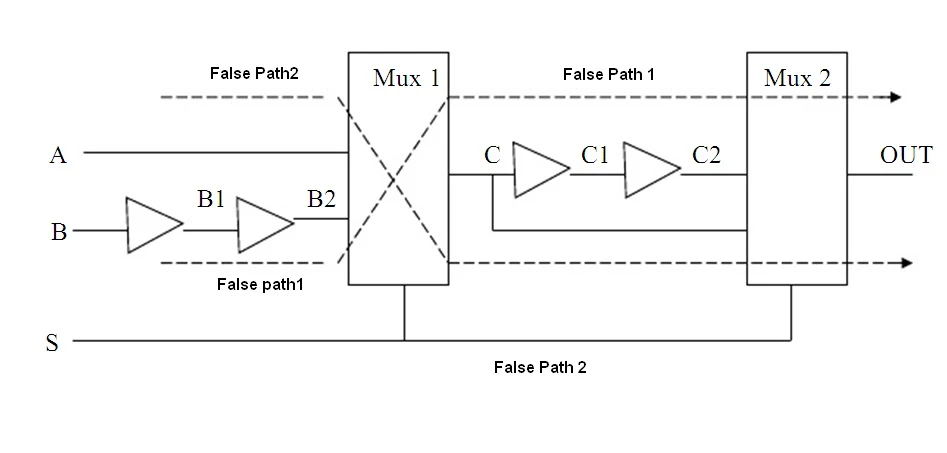

以下圖選擇器設計為例,False path2和False path1不會同時出現,但是時序分析的時候STA工具無法識別這種邏輯,因此必須人為地設置false path約束

常見的False path場景

a)來自配置輸入的場景

b)來自測試的輸入,輸入信號僅用于芯片測試,正常運行模型下不生效

c)來自異步輸入進入到芯片

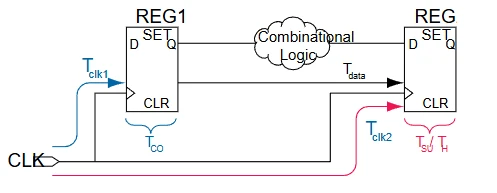

2.7?單周期路徑

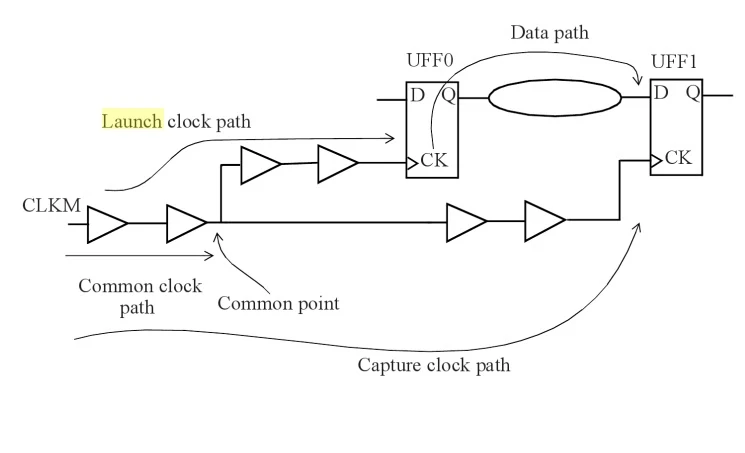

單周期路徑是設計中數據從起點傳輸到終點要求在一個時鐘周期完成,單周期路徑可分為發送路徑和接收路徑。下圖中UFF0是發送觸發器,UFF1是接收觸發器,兩者之前的為數據路徑,數據路徑的起點為UFF0/CK,終點是UFF1/D。

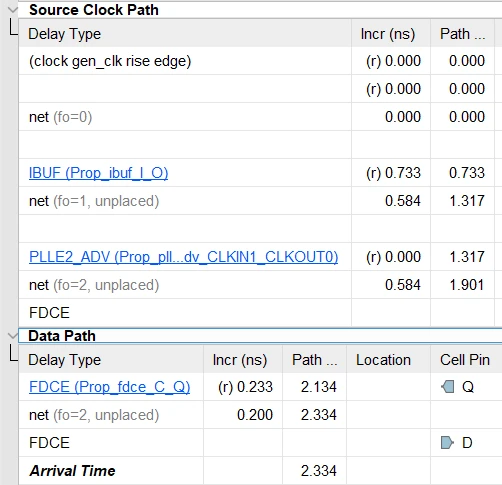

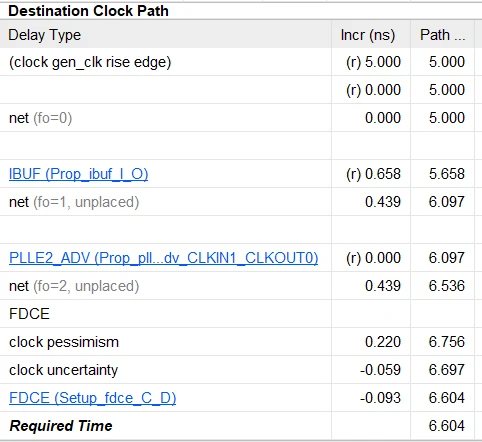

發送時鐘路徑加上數據路徑就是數據到達接收觸發器的到達時間(Arrival Time),接收時鐘的周期加上時鐘延時就是數據到達接收觸發器的要求時間(Required Time)

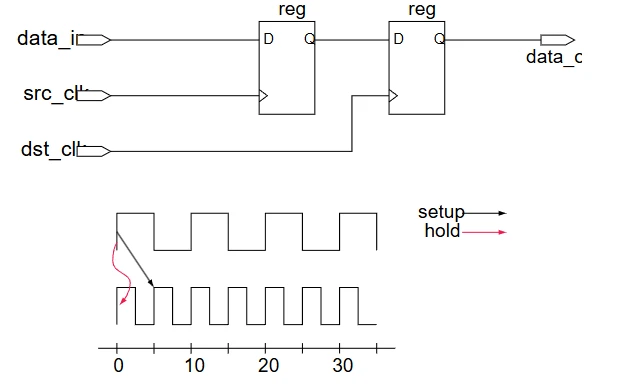

2.8?多周期路徑

多周期路徑是需要非默認設置或保持關系進行正確分析的數據路徑。

例如,一個寄存器可能被需要用于采集每第二個或第三個上升時鐘邊沿上的數據。乘法器的輸入寄存器與輸出寄存器之間的多周期路徑的示例,其中目地寄存器在每隔一個時鐘邊沿上鎖存數據。

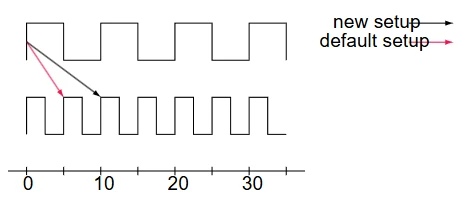

當源時鐘src_clk的周期為10 ns,目的時鐘dst_clk的周期為5 ns時,用于默認設置和保持關系的寄存器到寄存器路徑,源和目的時鐘的相應時序圖,默認設置和保持關系。默認設置關系為5 ns;默認保持關系為0 ns。

為滿足系統要求,您可以通過對寄存器到寄存器路徑指定多周期時序約束來修改默認設置和保持關系。

異常(exception)的multicycle setup assignment值為2,以使用第二個出現的鎖存沿;在此實例中,從默認值5?ns到10?ns。

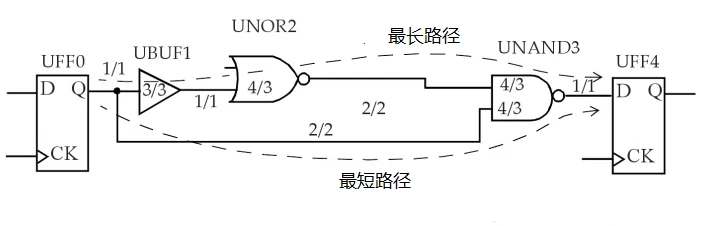

2.9?最長路徑和最短路徑

任何兩個起點和終點間,都可能存在很多路徑,最長的路徑是延時最長的路徑,也成為最差路徑或最遲路徑或Max路徑。最短路徑是延時最小的路徑,也稱為最好路徑或Min路徑。下圖中最長路徑是經過UBUF1,UNOR2,UNAND3單元后的路徑,最短路徑是只經過UNAND3的路徑

三、參考資料

https://www.intel.cn/content/www/cn/zh/docs/programmable/683243/20-1/multicycle-path-analysis.html

)

)

安全保障機制(技術、標準、管理))

(DAY 002))