Chapter 3 Design of Switching Power Regulators

Power Management Techniques for Integrated Circuit Design by Ke-Horng Chen

這本書比較深, 簡單介紹基本概念后, 就直接拋出大段公式和結論, 一章講其他書幾章內容, 適合有一定基礎, 想進一步做電源系統的人查閱. 優點是不廢話, 直面最難問題, 對于實際電路系統設計幫助參考較大.

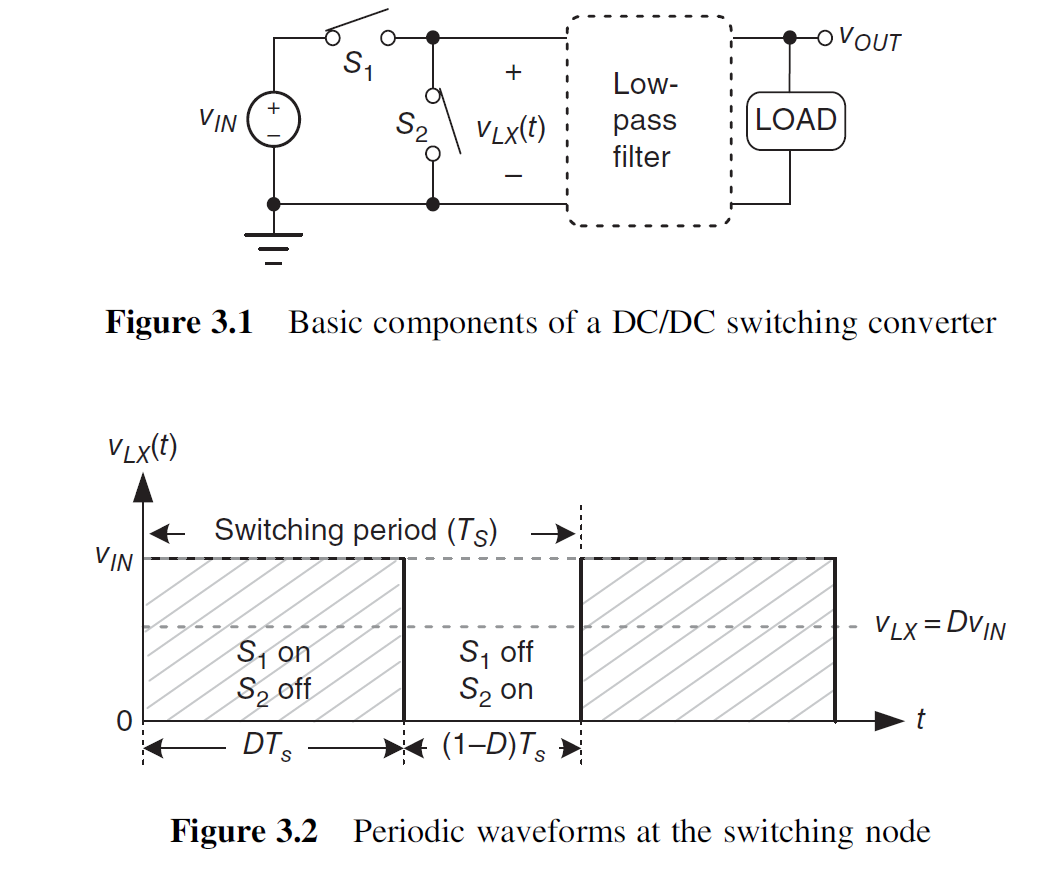

3.1 Basic Concept

DC-DC開關 converter如下圖所示. 由開關S1, S2控制, S1和S2不能同時開啟.

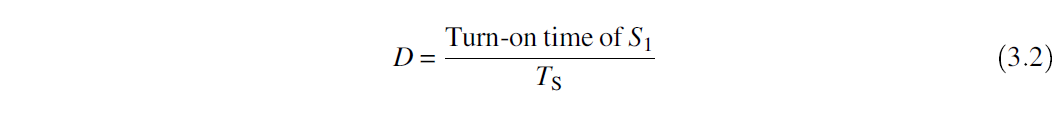

占空比D定義為

通過pulse width modulation (PWM), 輸出電壓為 Vout=D×Vin

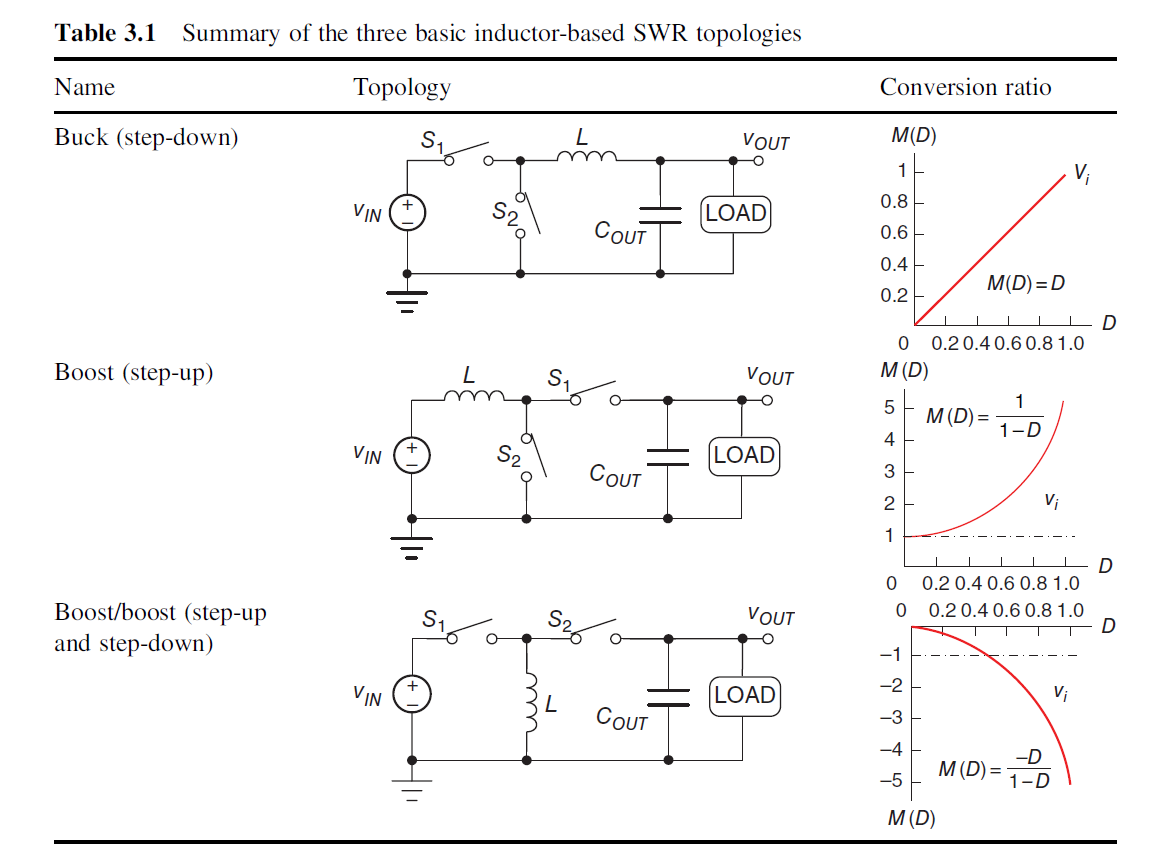

Buck, Boost, Buck/Boost拓撲和電壓轉換M(D)比如下圖所示

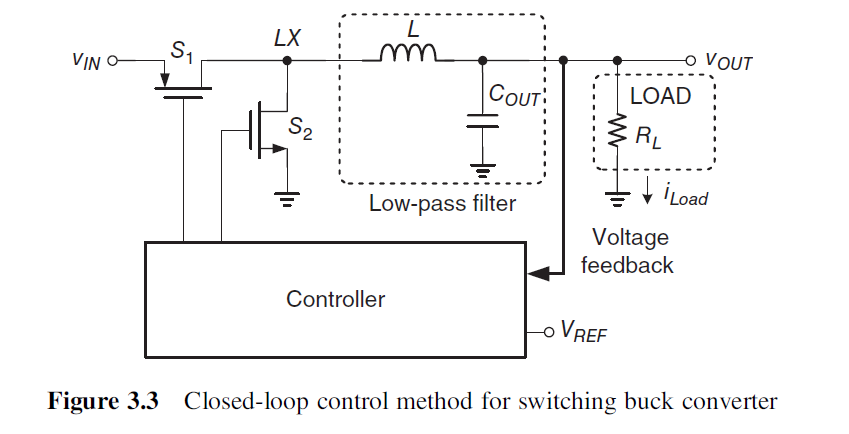

3.2 Overview of the Control Method and Operation Principle

我們可通過檢測Vout, 調節占空比D來穩定輸出電壓Vout, 閉環控制如下圖所示.

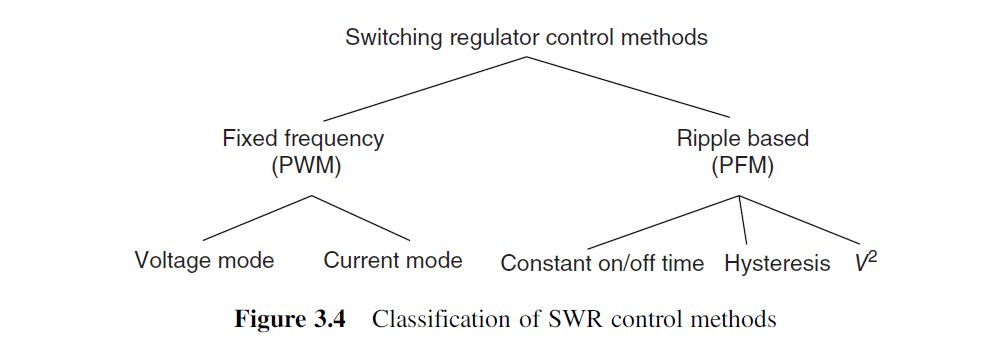

DC-DC控制方法如下圖所示, 分為固定頻率控制和基于紋波控制. 固定頻率也稱為PWM控制, 包括電壓模和電流模. 由CLK上升沿開始每次打拍. 基于紋波控制無需固定時鐘, 包括constant on/off time, hysteresis, V-square (V2)控制.

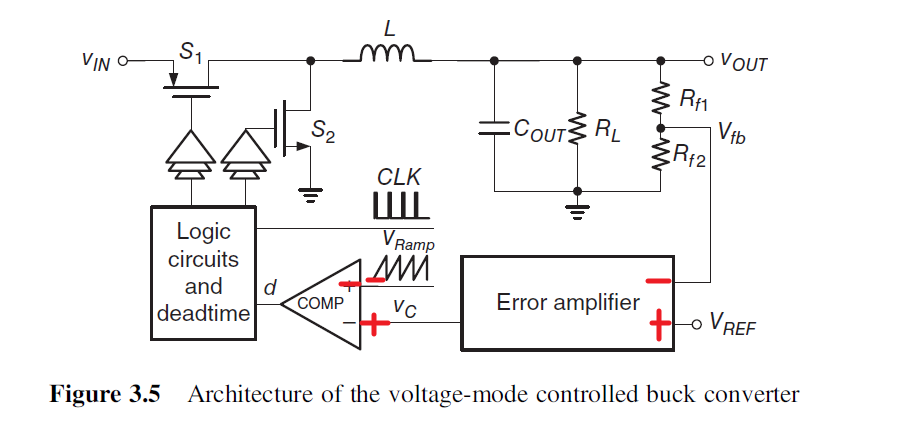

電壓模環路如下圖所示, Error Amplifier放大Vref-Vfb壓差, 產生Vc. 和Vramp三角波進行比較產生占空比D的PWM波形.

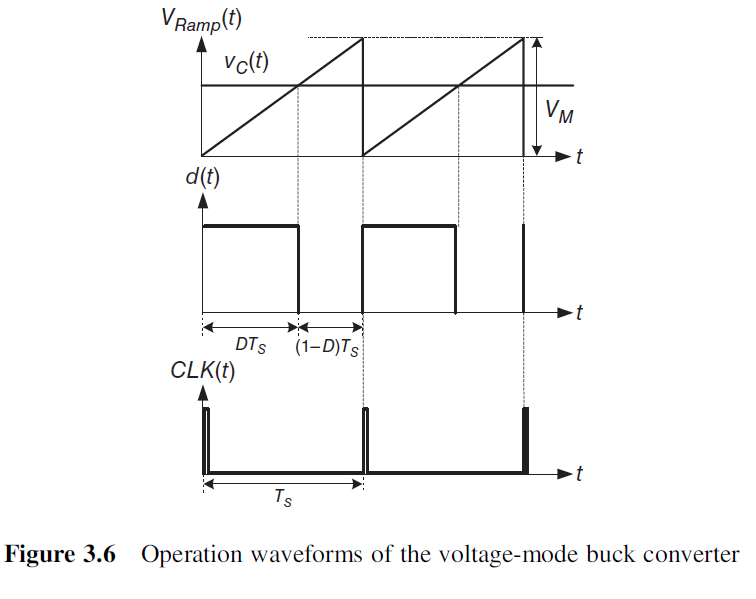

CLK信號定義了固定的開關頻率, 每次打拍由CLK上升沿決定,如下圖所示. Vc決定了占空比. 當Vc>Vramp時, d為1, 當Vc<Vramp時, d為0. 通過負反饋環路, Vfb=Vref. Vfb=Vout Rf1/(Rf1+Rf2).

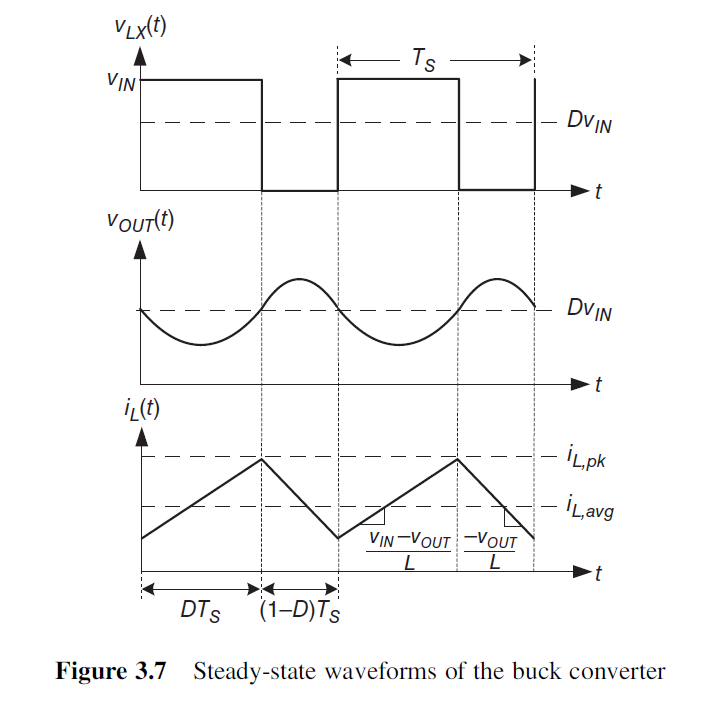

buck converter的穩態波形如下圖所示

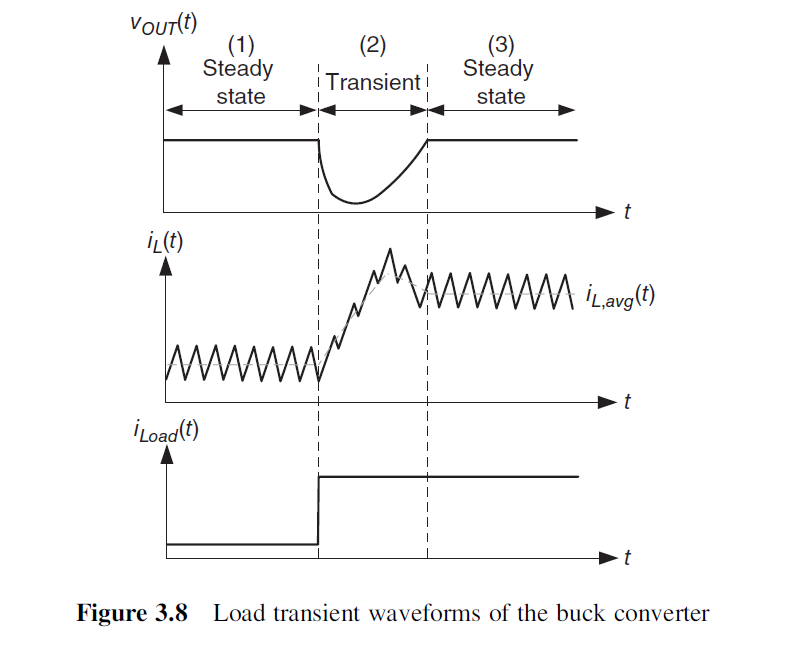

發生負載瞬態跳變 load transient 時, vout, iL的波形如下圖所示. 在(2)階段, buck不能提供變大的iLoad, 因此Vout跌落undershoot. 直到(3)階段回到steady state.

對于電壓模控制, 當vin增加時, 占空比一開始不變, 由于vout增加, 通過負反饋降低vc, 再降低占空比, 從而vout恢復到原先固定值. 前饋技術feedforward technique直接通過vin來控制Vout, 能提高line transient響應.

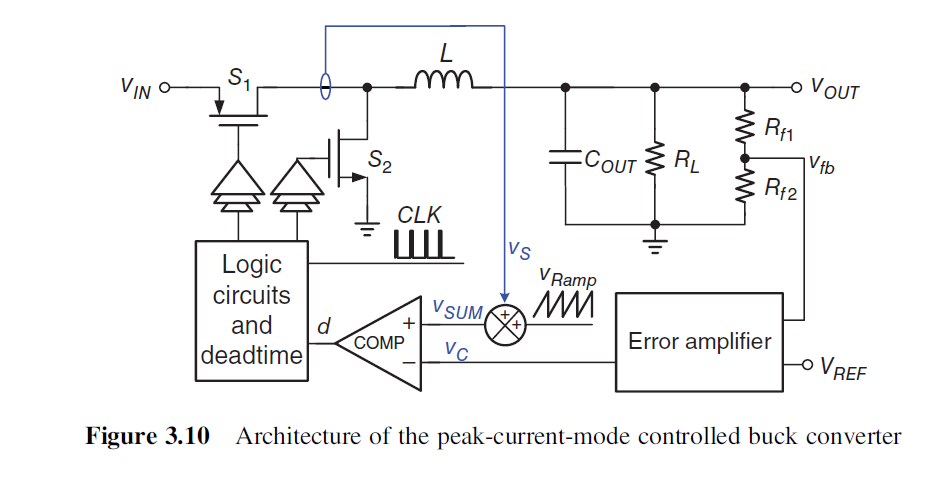

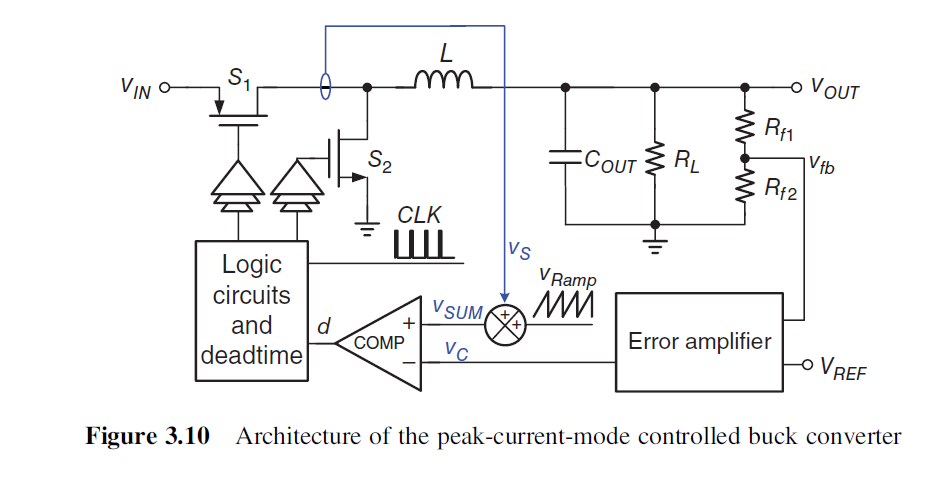

注意, 電感電流不僅包括負載電流信息, 還包括Vin信息. 電流模控制采樣電感電流, 提供Vin信息, 來控制Vout, 即提供feedforward通路來提高line transient. 如下圖Fig 3.10所示. 但仍需要Vout負反饋來進行vout電壓控制, 因為電流模不能直接獲得Vout信息. 峰值電流模環路如圖Fig 3.10所示, 采樣電感電流VS疊加到Vramp上, 和Vc進行比較, 產生占空比D.

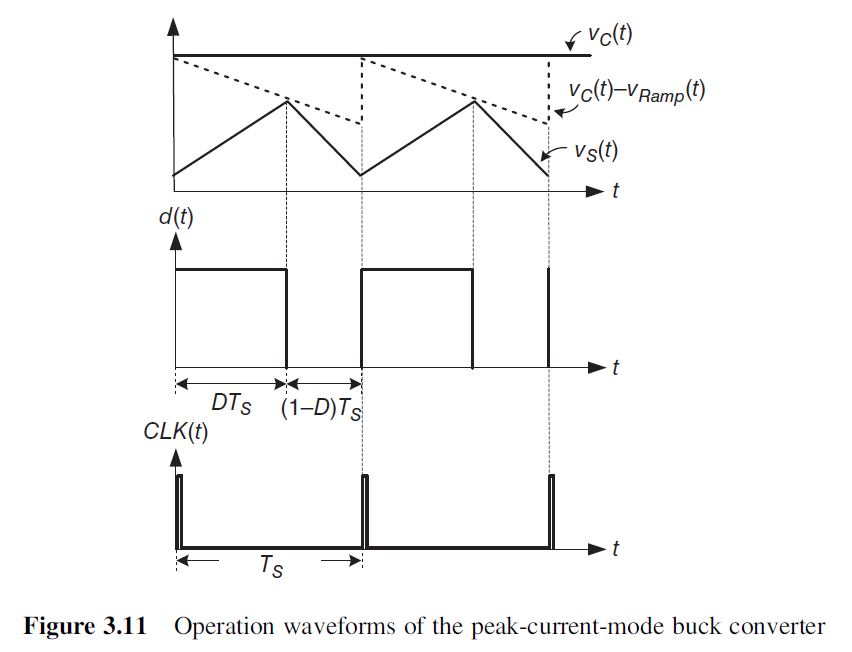

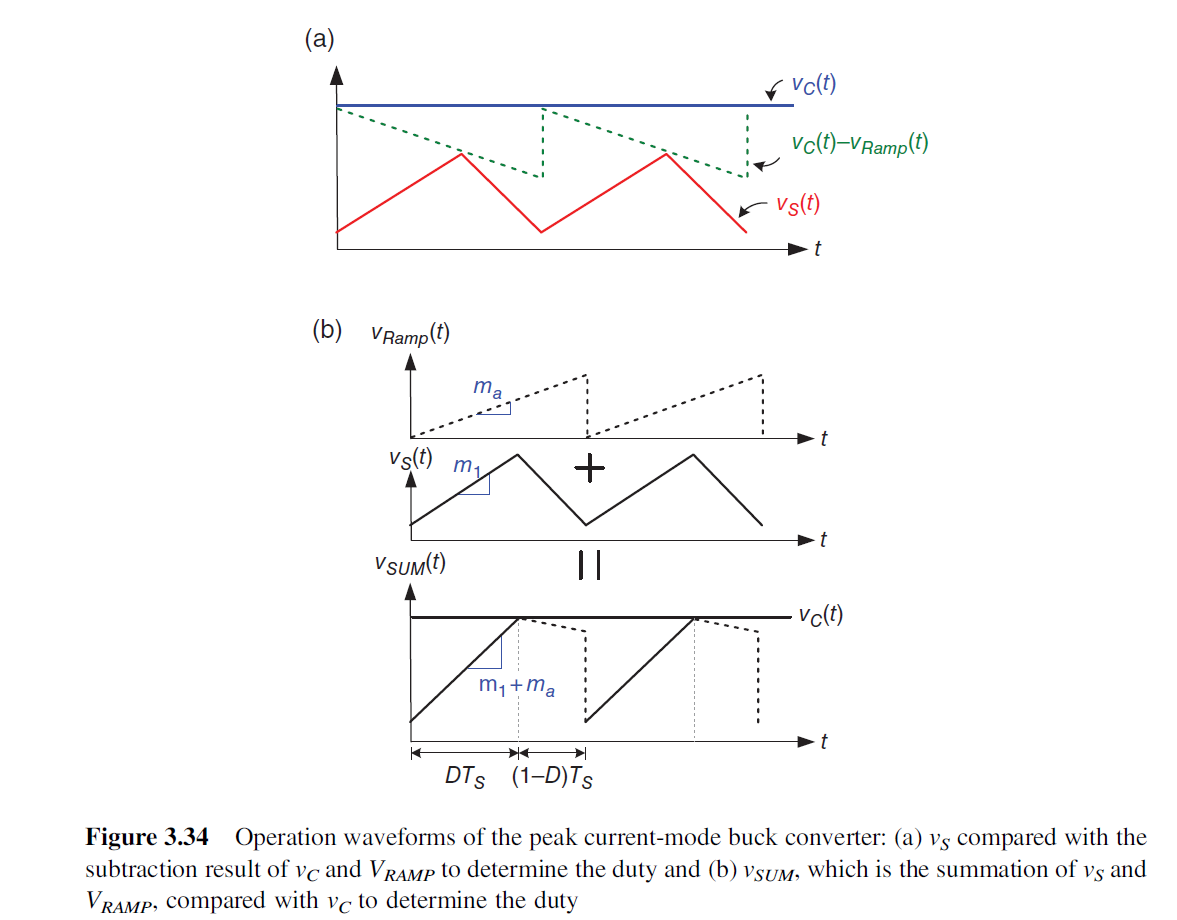

峰值電流模工作模式如Fig 3.11所示, Vc=(Vref-Vfb)*Av. 代表了輸出電壓信息. 在CLK上升沿來臨, 開啟上管, 占空比d=1. Vs隨著電感電流iL增加, 當Vs+Vramp的電壓超過Vc時, d=0, 關閉上管, 開啟下管. 即Vs+Vramp<Vc時, d=1.

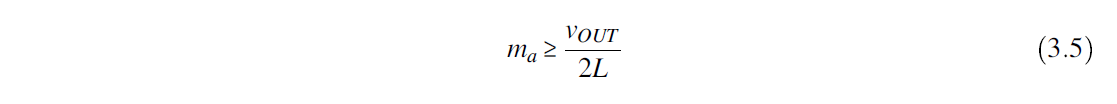

對于電流模, 當d>0.5會出現次諧波震蕩, 因此需要添加斜坡補償vramp. 其斜率ma需要滿足.

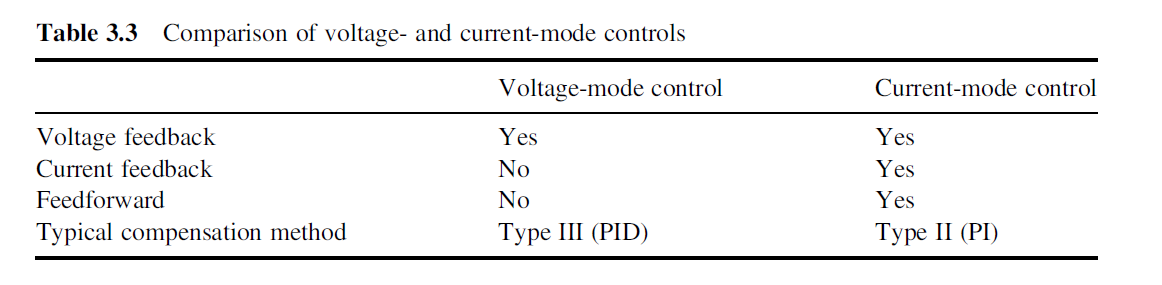

相比電壓模, 電流模既有電壓控制, 也有電流控制, 同時具有feedforward前饋Vin電壓通路, 因此line transient性能好. 而且補償簡單, 單極點系統只需要Type II補償, 無需電壓模Type III補償.

3.3 Small Signal Modeling and Compensation Techniques in SWR

3.3.1 Small Signal Modeling of Voltage-Mode SWR

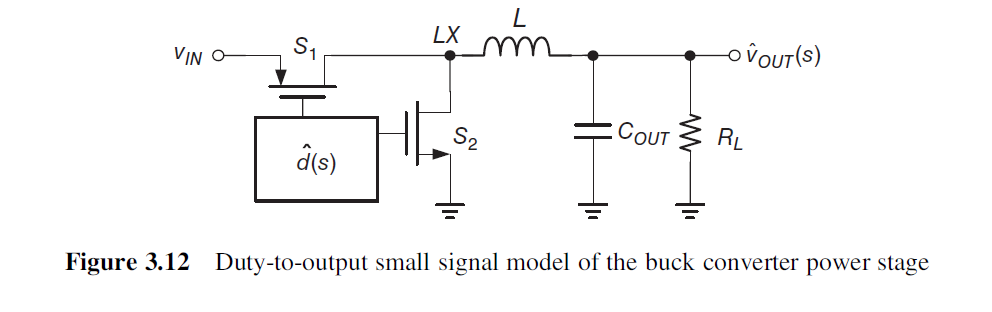

電壓模功率級小信號如下圖所示

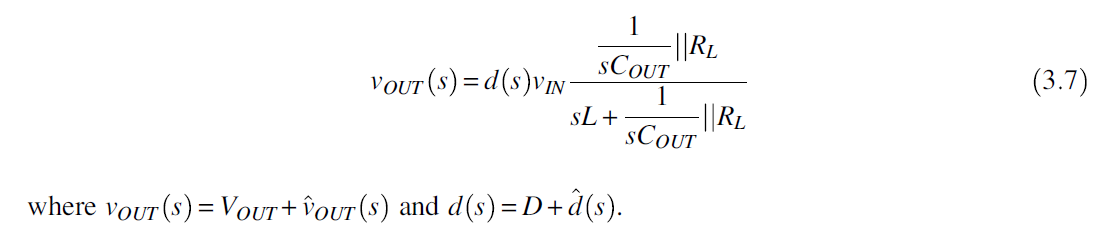

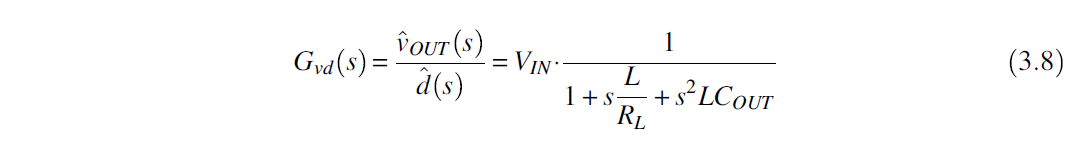

對于電壓模, 輸出Vout=占空比d × Vin (即LX平均電壓)× Cout和R,L的分壓.

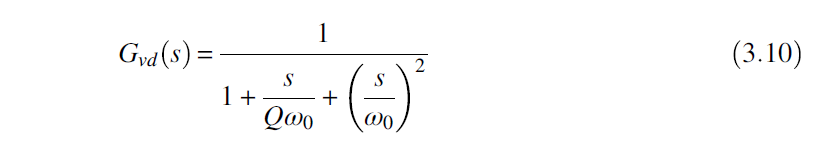

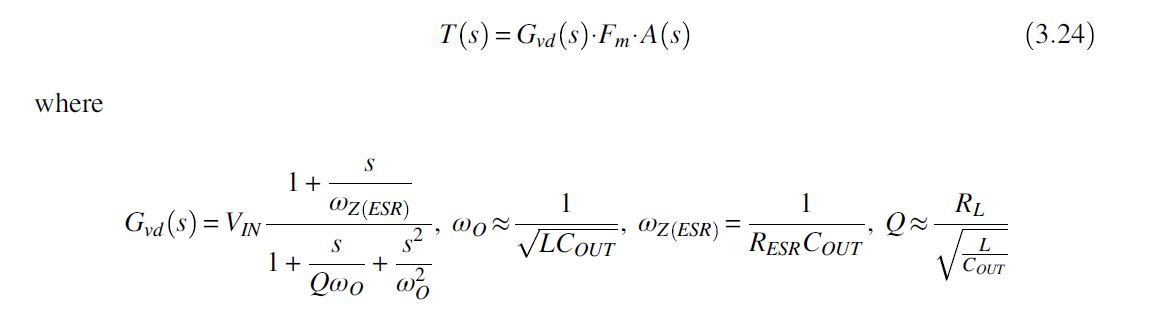

分離DC直流信號和ac小信號. 可得duty-to-output transfer function Gvd(s)

歸一化為

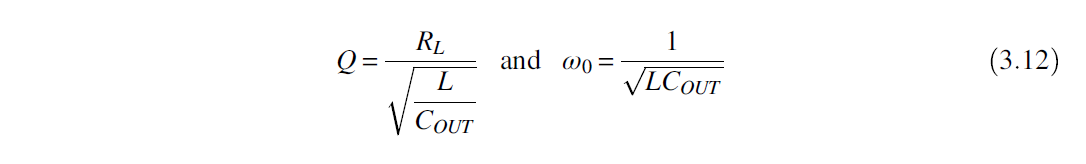

其中Q為品質因數, 代表系統損耗. 共軛極點ω0由LC決定.

共軛極點會導致phase下降180deg, magnitude也下降. low Q下, 兩個極點是分離的. high Q會引入復數共軛極點, 造成magnitude往上翹出現峰值. 峰值Q由負載決定. Q越大, magnitude會往上翹. phase下降越快.

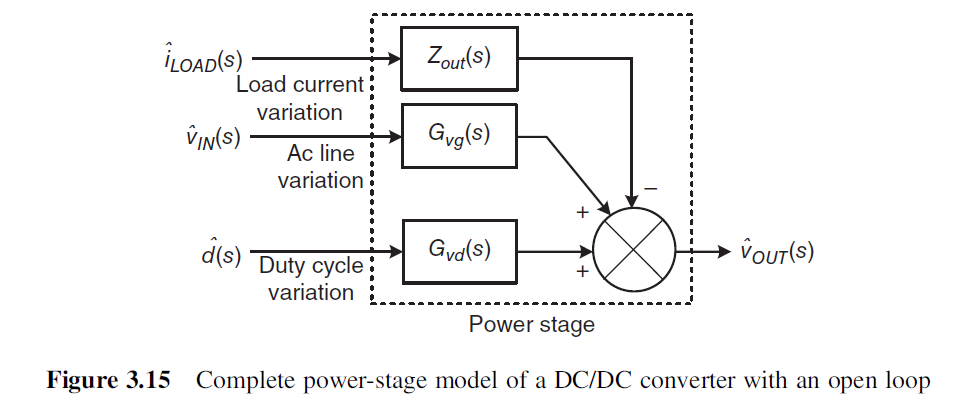

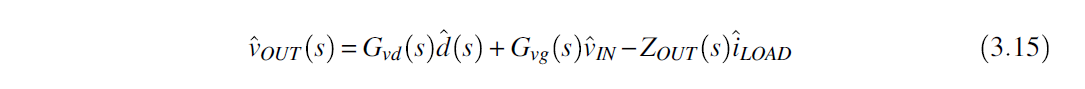

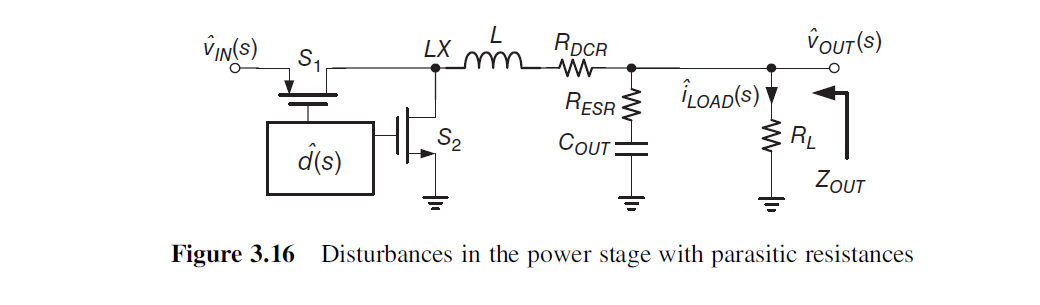

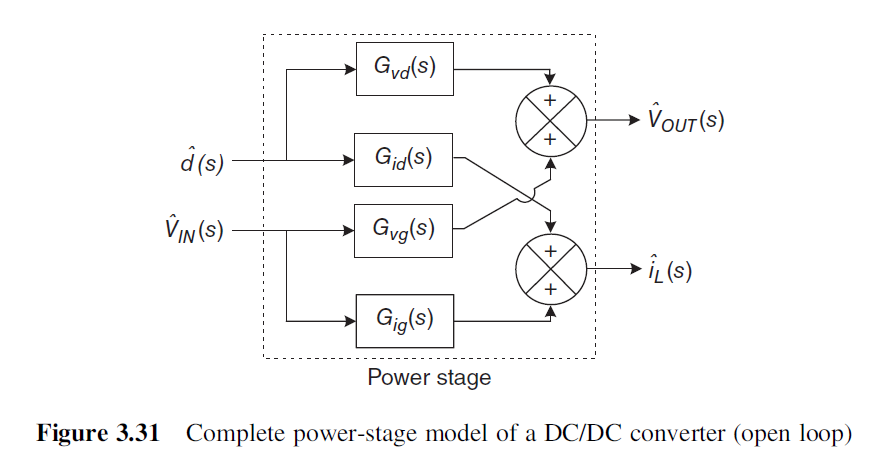

開環下輸出Vout由d, vin和iload決定, 其貢獻如下圖所示

因此輸出Vout可表達為

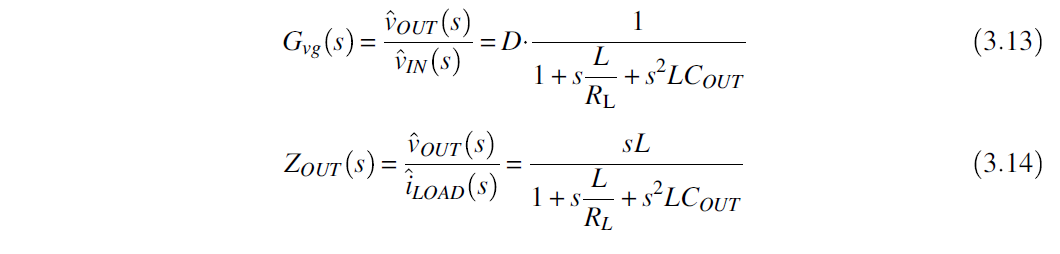

line-to-output 傳輸函數 Gvg和 輸出阻抗傳輸函數 Zout為

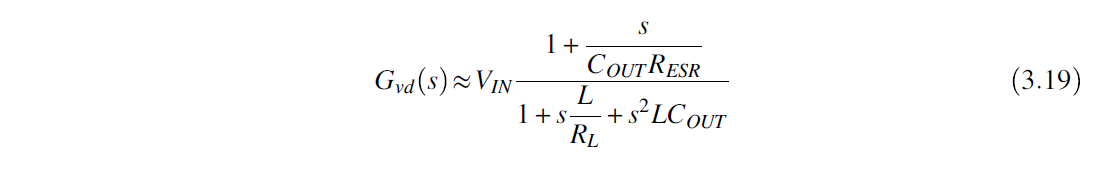

考慮寄生參數, 尤其是輸出電容Cout的Resr

可得duty-to-output transfer function Gvd(s) 增加了一個左零點, 位置為1/(Cout ×Resr)

3.3.2 Small Signal Modeling of the Closed-Loop Voltage-Mode SWR

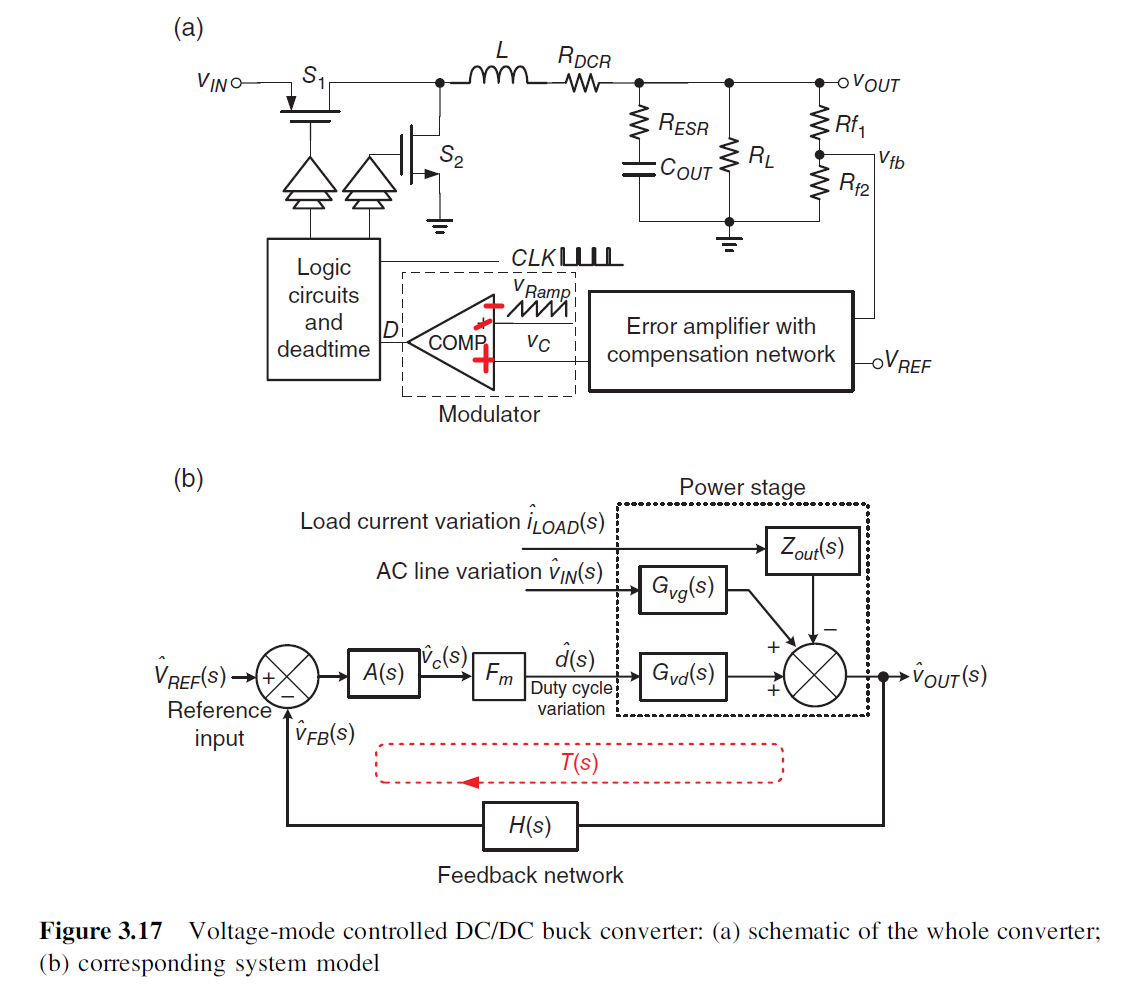

電壓模 buck環路如下圖所示.

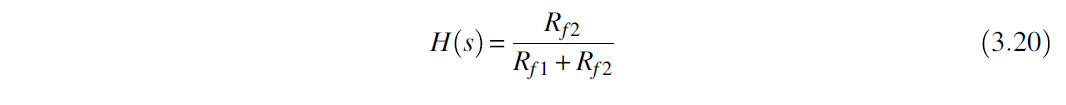

feedback network傳函為分壓電阻:

EA運放補償的傳函為A(s)

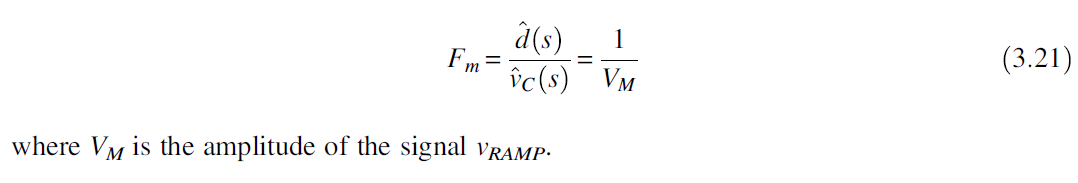

PWM比較器的傳函為 1/Vm, Vm為三角波峰峰值

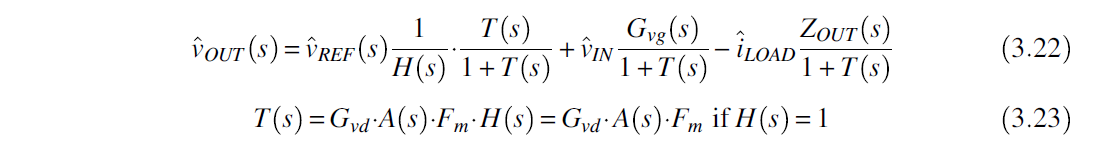

因此閉環輸出Vout的表達式為:

T為Loop Gain環路增益. Loop Gain可用于判斷環路穩定性. 一般要求Loop Gain有高的低頻增益 (提高load和line regulation), 45°的phase margin, 和至少10dB的gain margin. 為了提高瞬態響應, 帶寬即crossover frequency需要做大, 一般crossover frequency定在開關頻率的1/5 or 1/10, 確保開關噪聲能被抑制.

3.3.2.1 Frequency Compensation Design in Voltage-Mode SWR

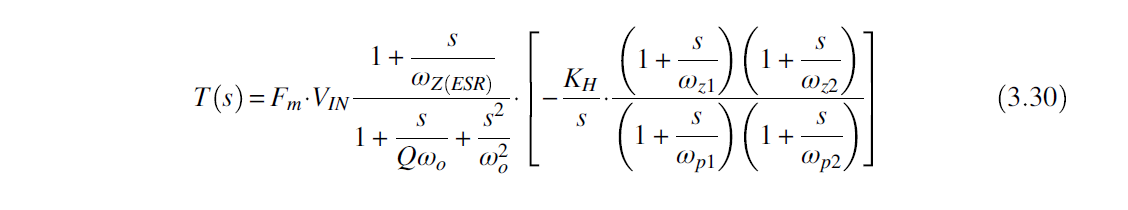

電壓模的Loop Gain為. 其中Gvd有兩個共軛極點, 一個Resr零點. Fm為常數, 要想環路穩定全靠EA補償.

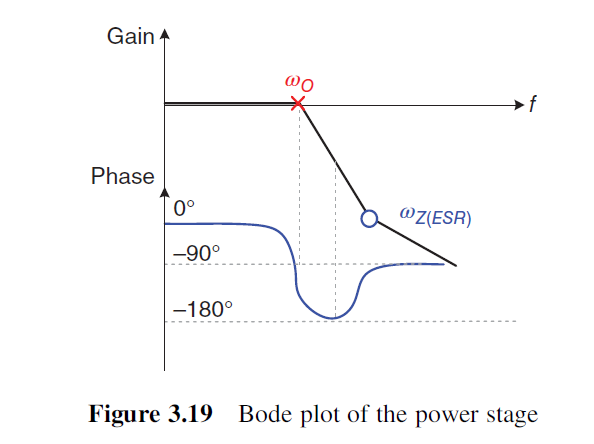

其power stage的bode plot為

A(s)用proportional compensation (P-compensation) 即A為常數會導環路不穩定, 除非Resr很高, 導致ESR零點較低, 但這會造成發生iLoad transient時, Vout的IR紋波很大.

為了提高低頻增益, A(s)用積分器1/s結構, 為了環路穩定性, 只能把帶寬拼命壓低, 讓帶寬在wo以內, 犧牲帶寬, 保證相位裕度. 如下圖所示

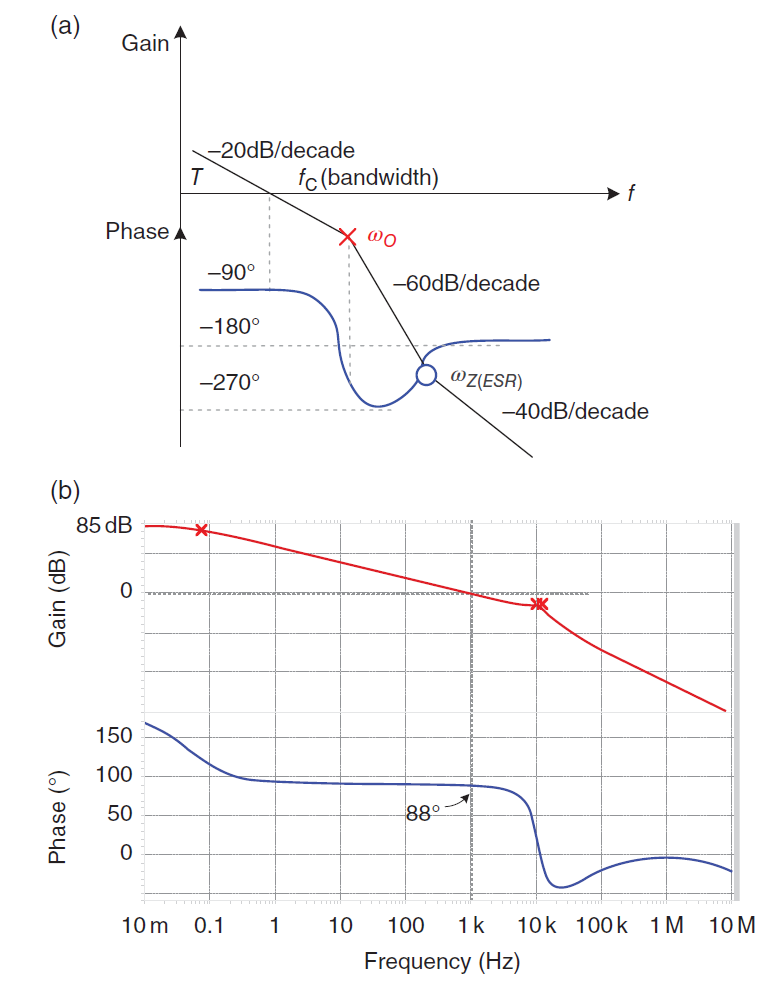

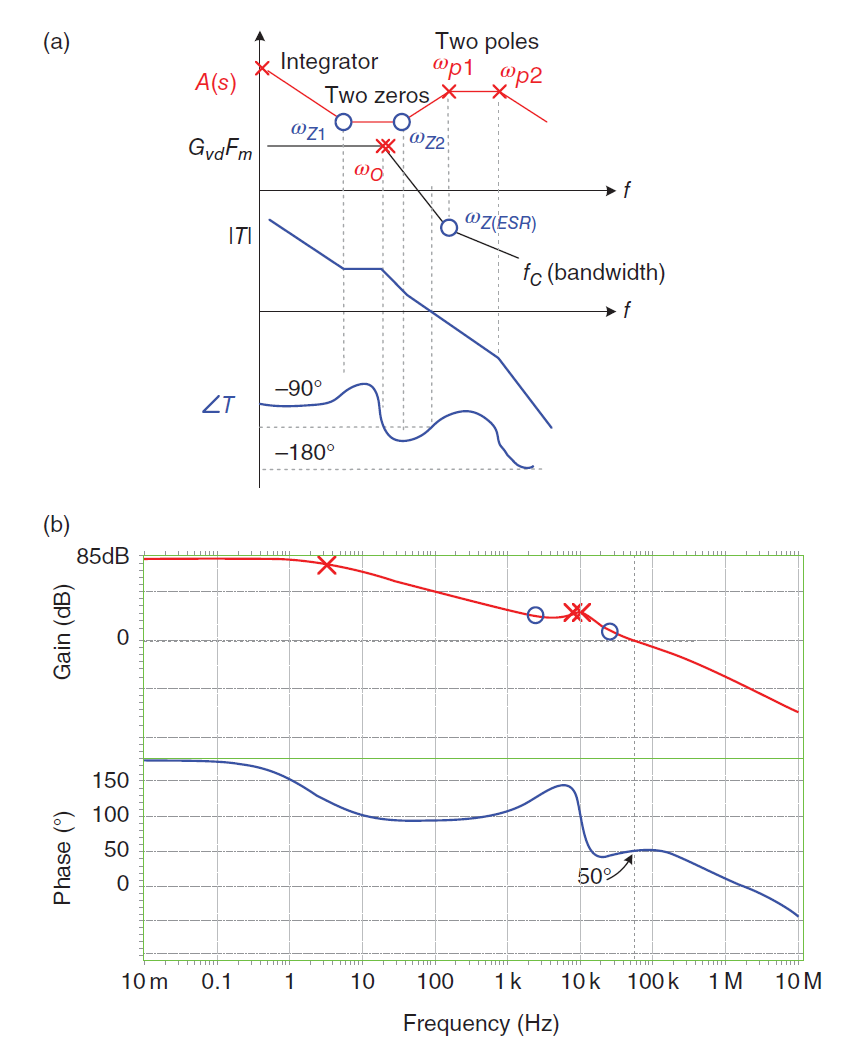

為了獲得高DC增益, 同時提高帶寬, 需要用Type III型補償, 添加一個積分極點, 2個零點提升phase, 和2個高頻極點抑制高頻噪聲增益. 如下圖所示

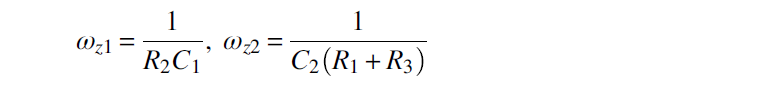

積分極點提供高DC增益, 2個零點進行phase 補償, 可設計1個零點wz1在 ωO之前進行phase lead補償, 另外1個零點wz2在 ωO之后減少phase drop. 為了提高帶寬和phase margin, 一般把crossover frequency放在wz2和wp1之間. 為了進一步提高帶寬, 可把wp1放在wz(esr)處, 通過ESR零點擴展帶寬, 提高瞬態響應速度. Loop Gain T和bode plot如下圖所示. DC gain 85dB, PM=50°, load transient較好.

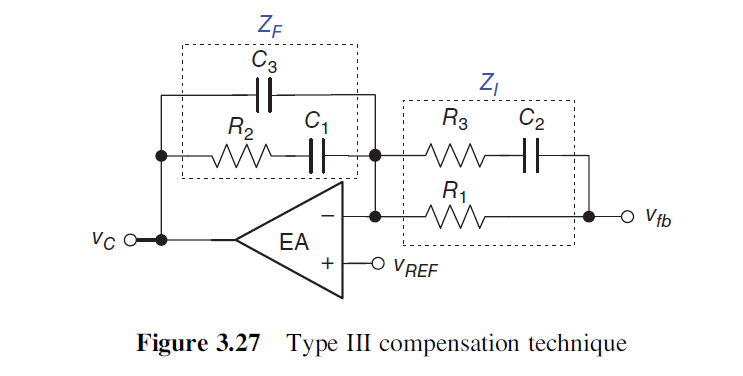

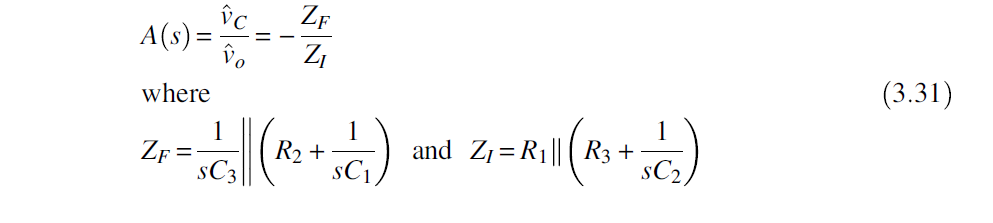

為了實現Type III補償, 可用下面EA補償結構

EA補償Av= -ZF/ZI

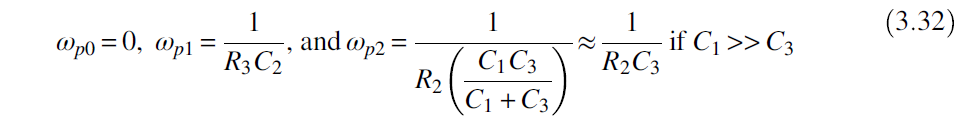

兩個零點

兩個極點

為了產生w0, w1兩個低頻零點 R1, R2, C1和C2不可避免很大. wp1和wp2用來抑制開關噪聲, 但又不能影響穩定性, 因此R3<<R1, C3<<C1.

也可以用高ESR產生零點在crossover frequency之前, 提供phase lead, 然后用Type II補償. 但是發生load transient時, 由于Cout大ESR, Vout ripple更大.

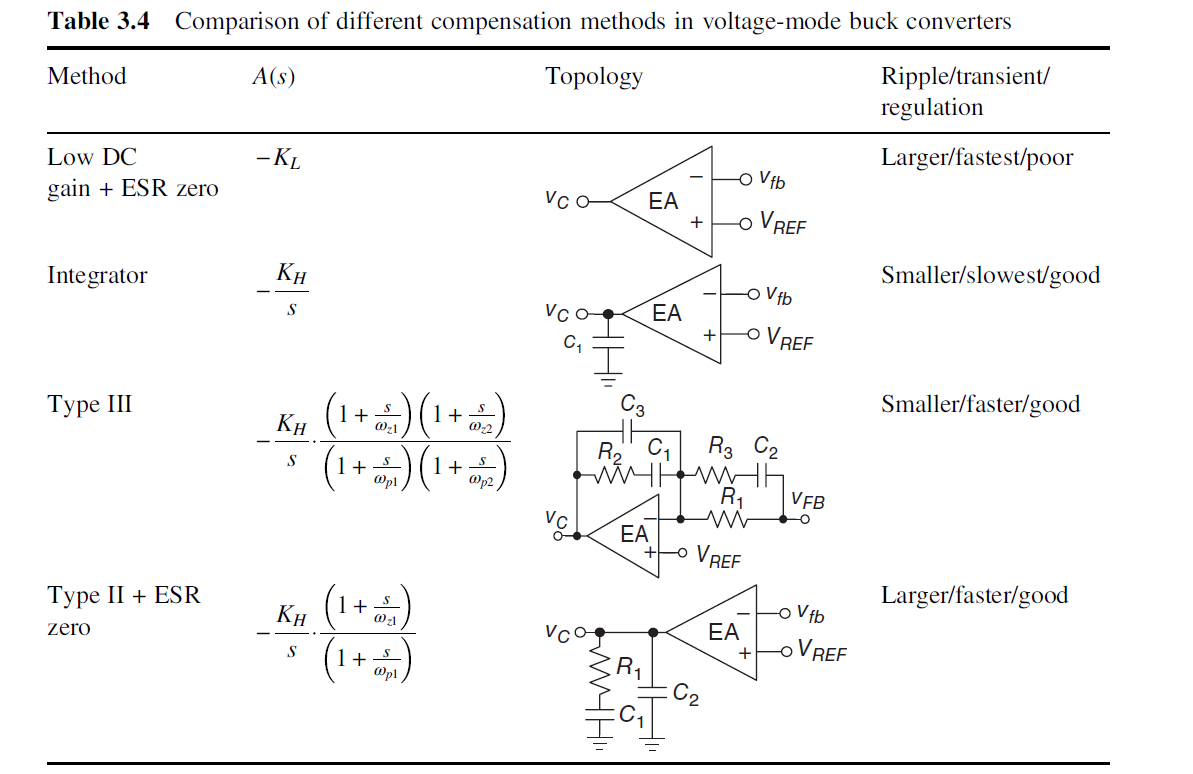

電壓模補償總結如下, 一般電壓模采用Type III補償. 就是補償元器件R,C值較高.

3.3.3 Small Signal Modeling of Current-Mode SWR

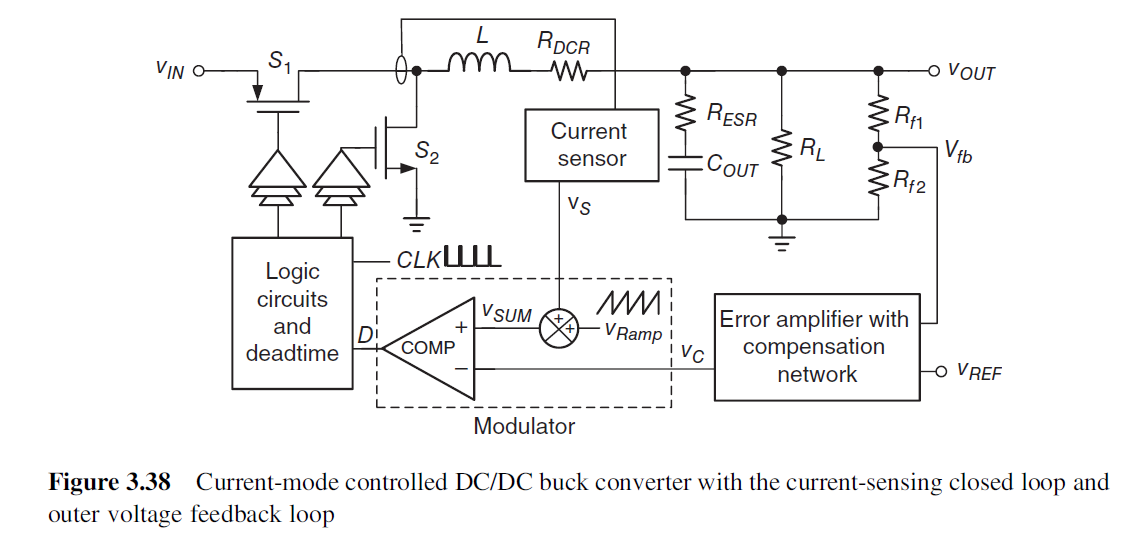

由于功率級的共軛極點, 電壓模buck的補償網路很復雜, 為了提高line transient, 還需要加入Vin前饋通路. 另外功率管需要OCP過流保護. 因此我們可采用電流模控制, 如下圖所示, 圖中 PWM 比較器 ±號反了.

電流模功率級模型如下. d和vin對Vout和iL都有貢獻.

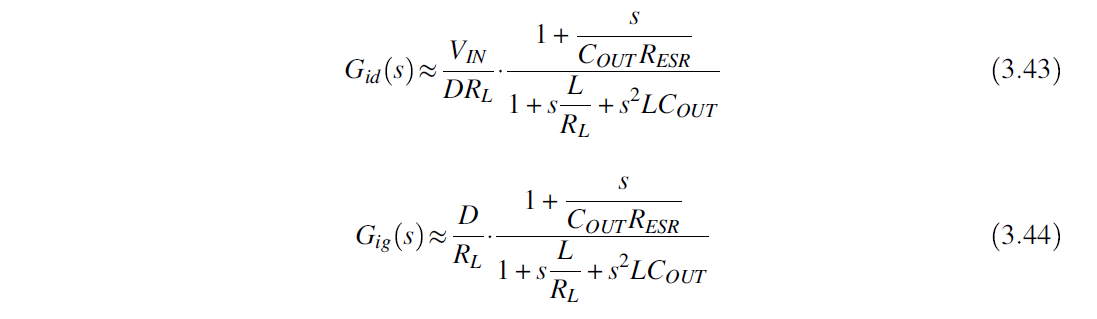

考慮Cout的ESR, Gid和Gig為

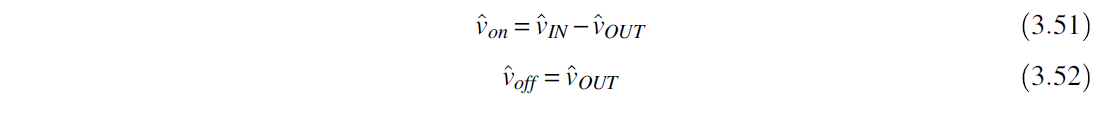

對于電流模, 當d>0.5會出現次諧波震蕩, 因此需要添加斜坡補償vramp. Vsum=Vs+Vramp, 決定了占空比D. Vramp的ma斜率需要>1/2 Vout/L

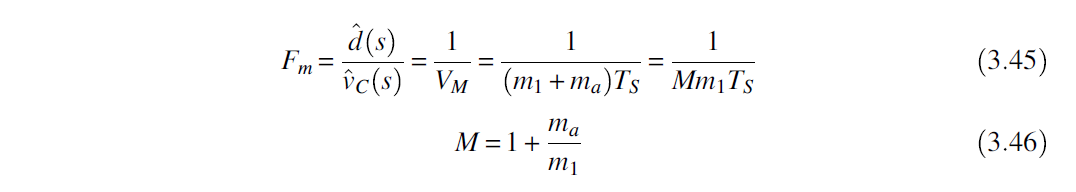

在DTs 引入了斜坡補償ma, 三角波等效峰峰值為(m1+ma)TS. 比較器傳函Fm=1/[(m1+ma)×Ts].

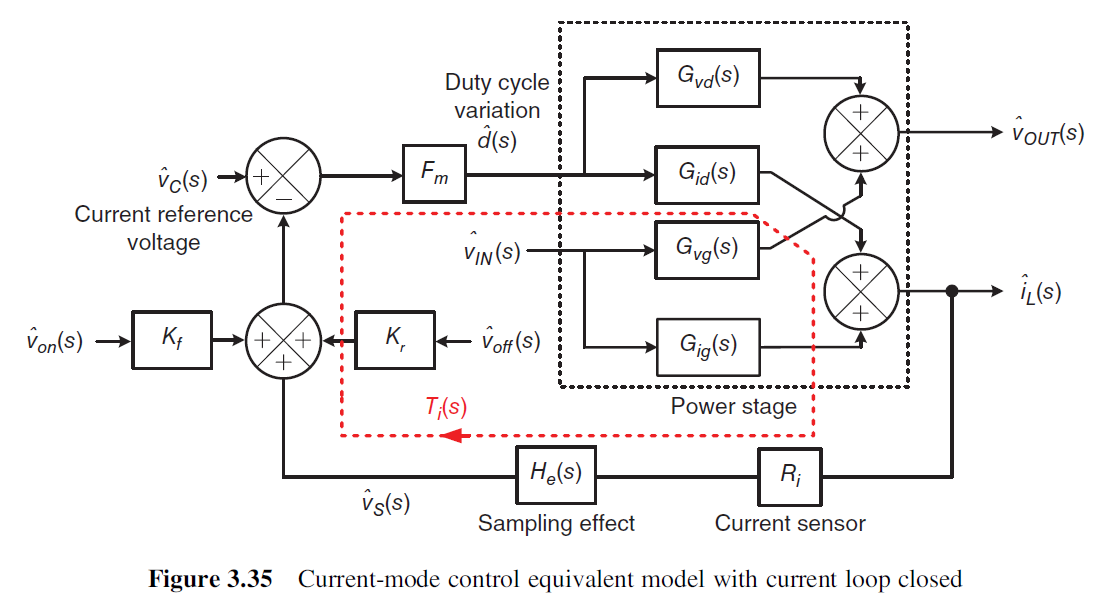

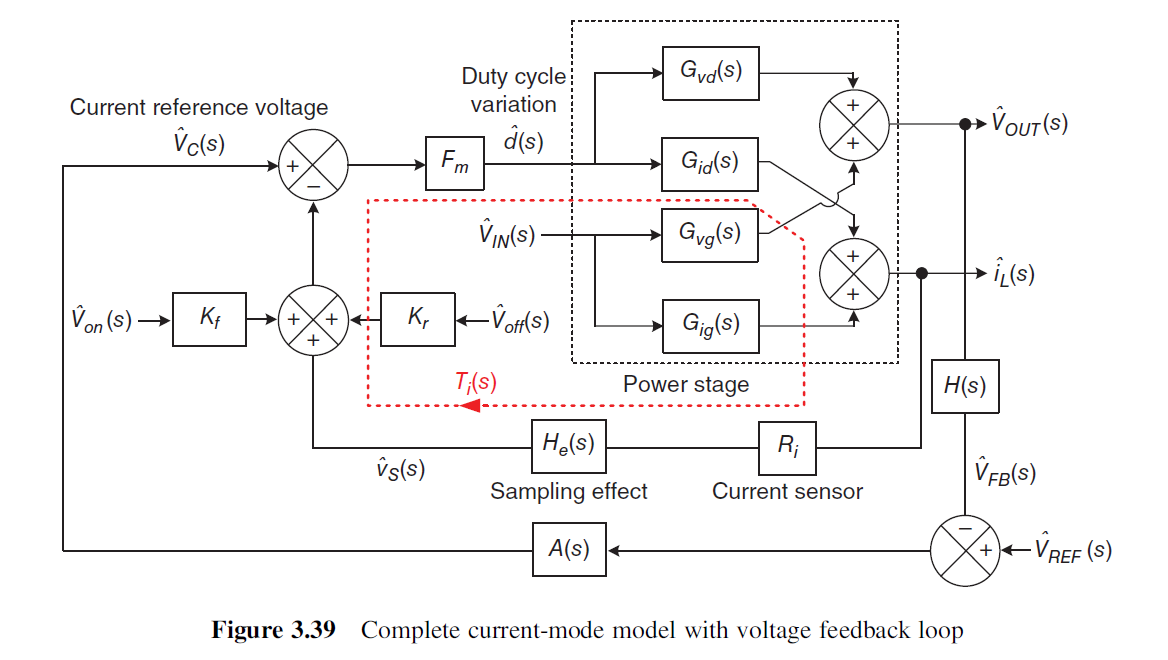

Fig 3.35展示了電流模控制的電流環路.

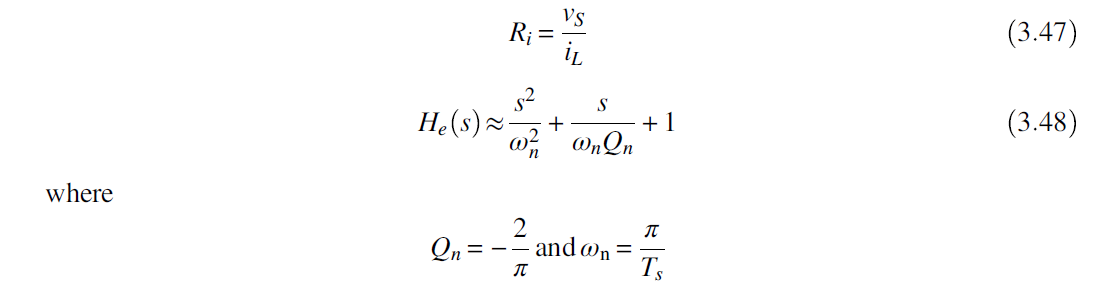

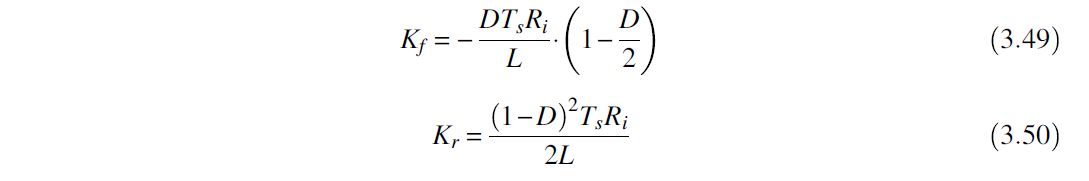

電感電流iL經過Ri轉化成電壓信號Vs: Vs=Ri×iL, 再經過He, 即sample-and-hold效應.

Kr和Kr為在ton-time和toff-time時, 輸入輸出電壓影響電感電流的前饋通路

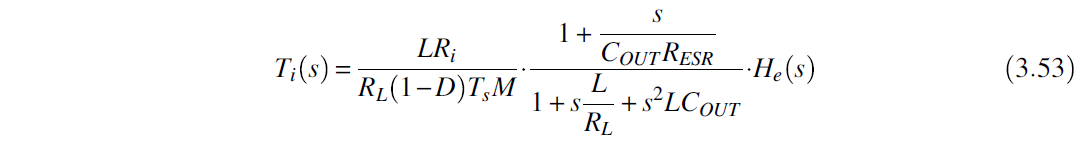

因此可得電流環路增益Ti(s)為

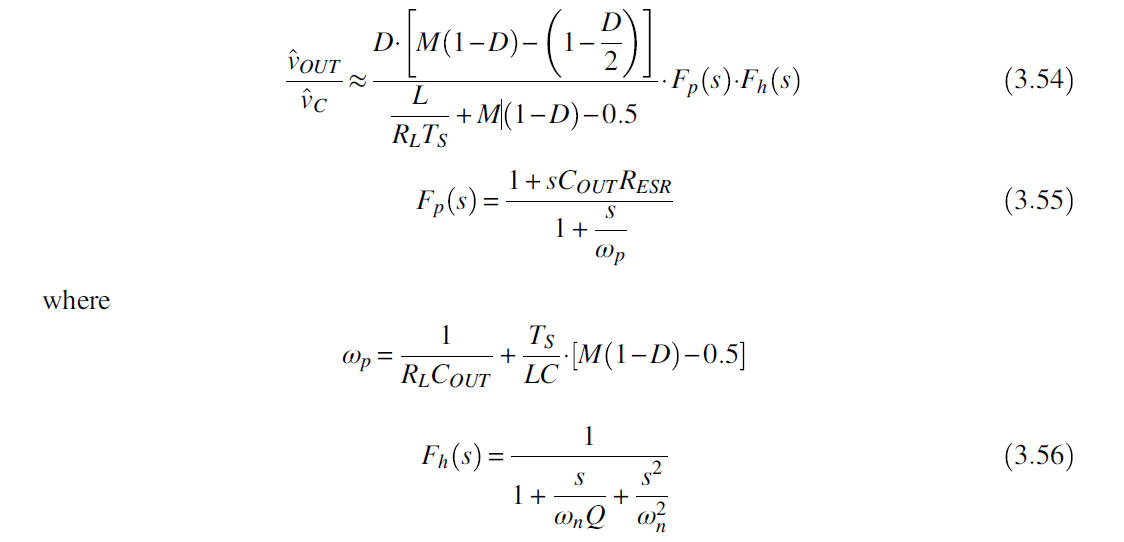

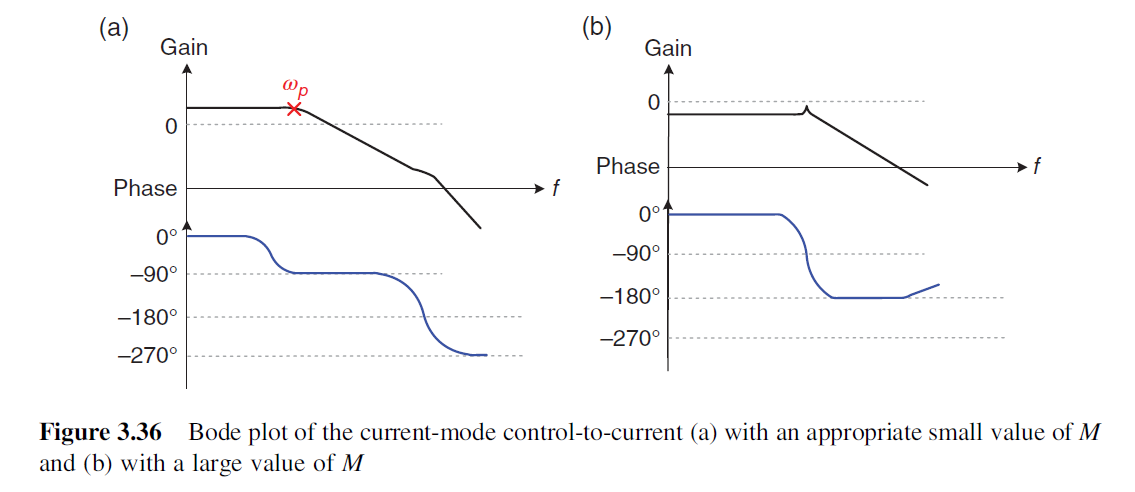

電流模 control-to-output 即vc到vout的傳輸函數為

吧

吧

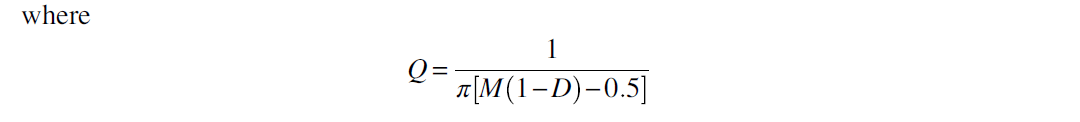

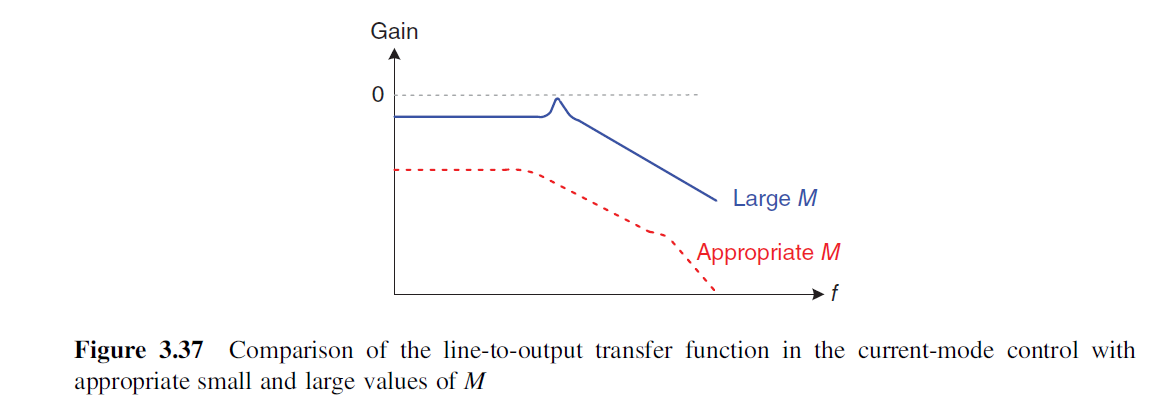

Fig 3.36展示了不同斜坡補償ma, M=1+ma/m1 對于control-to-output即vc到vout 傳輸函數的影響.

(a)為較小, 合適的M值, ma=m2. DC gain大于零, 具有單極點wp, wp約為1/(RL*Cout). 因此電流模可視為單極點系統, 即把電感看成恒流源, 極點由Rout和Cout決定, 比電壓模補償容易多了!

(b)斜坡補償ma越大, M越大, 更容易形成共軛極點. wp往后推, 高頻極點往前推. 當M很大時, 典型的電流模特性控制消失, DC gain低于零, 電感電流信息VS被忽略了. 因此占空比D僅由Vc和Vramp決定, 這就和電壓模控制一樣了, 因此有電壓模的兩個共軛極點. 因此在很大M下, 電流模退化成電壓模控制.

電流模的line-to-output 傳函如下:

當M很大時, dc gain很大, 抑制Vin紋波的作用被大大降低, 類似電壓模, 即輸入Vin不能前饋到環路.

3.3.3.1 Frequency Compensation Design in Current-Mode SWR

電流模中Vc作為電流基準, regulate電感峰值電流. 在實際中電流基準需要在不同負載環境下生成. 為了形成動態電流負載, 把輸出電壓Vout和Vref進行比較, 產生電流基準Vc, 如圖Fig 3.38所示. 當Vout<Vref, Vc增加, 導致電感峰值電流增加, 從而提高輸出Vout, 形成負反饋.

帶電壓反饋的電流模環路如下圖所示

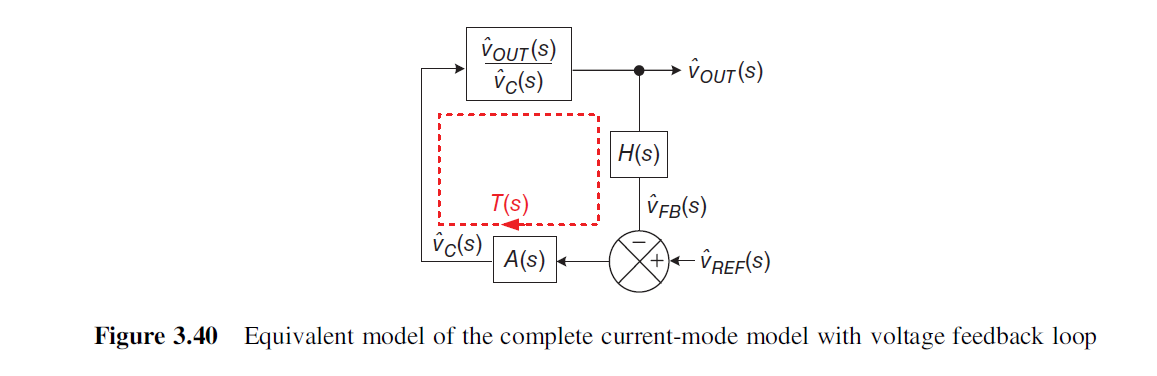

電流模 control-to-output即vc到vout的傳輸函數在上面已經推導, 因此帶電壓反饋的電流模環路可簡化為Fig 3.40

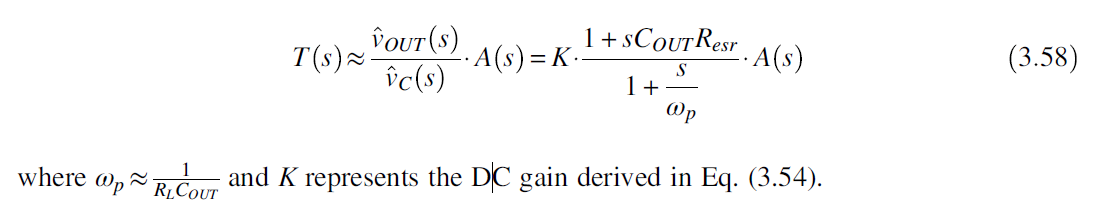

因此loop gain為Eq 3.58. K為電流模DC gain,

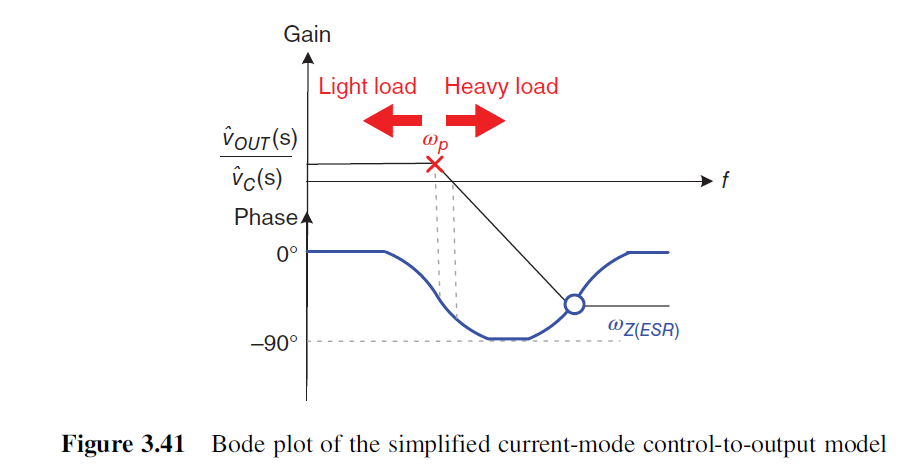

電流模有一個極點和零點. 零點由ESR構成, 極點wp為輸出電容/電阻構成的主極點. 主極點位置隨著負載Rout變換, 輕載wp向內推, 重載wp向外推. 因此電流模控制需要考慮負載Rout和Cout的變化. 一般把crossover frequency定在開關頻率的1/10或者1/5, 抑制開關噪聲.

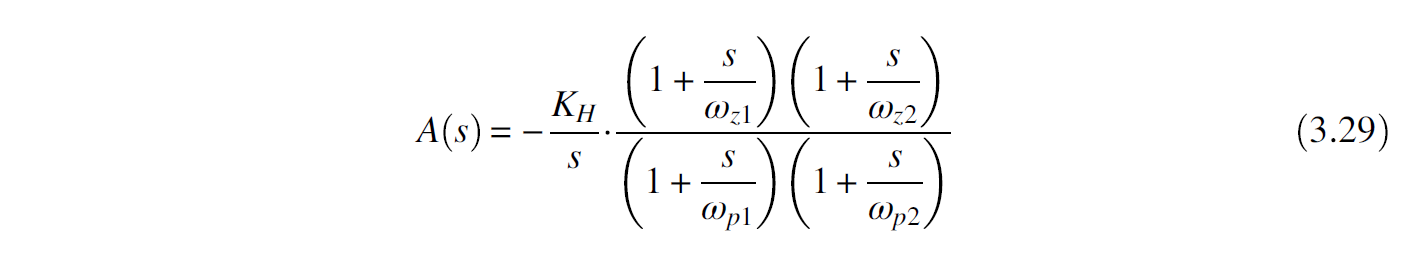

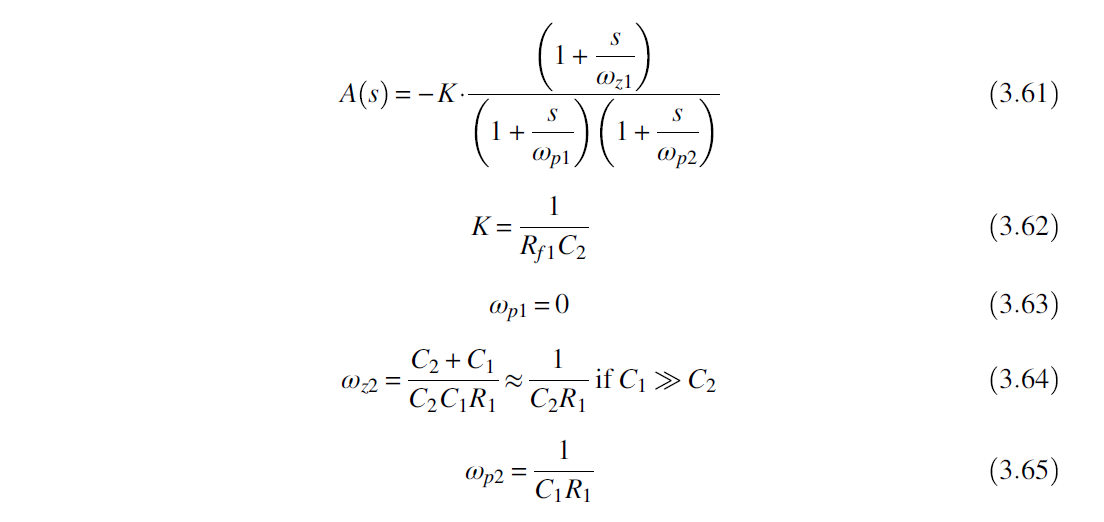

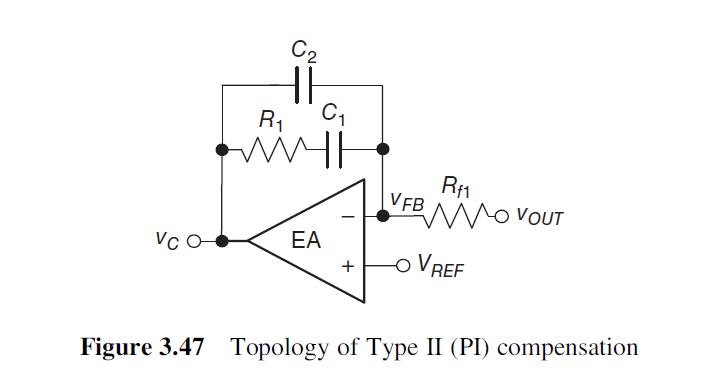

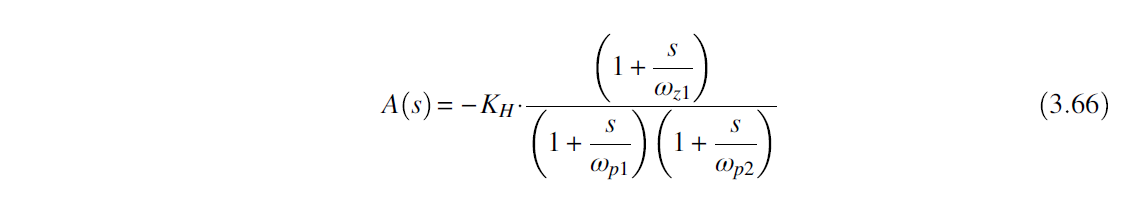

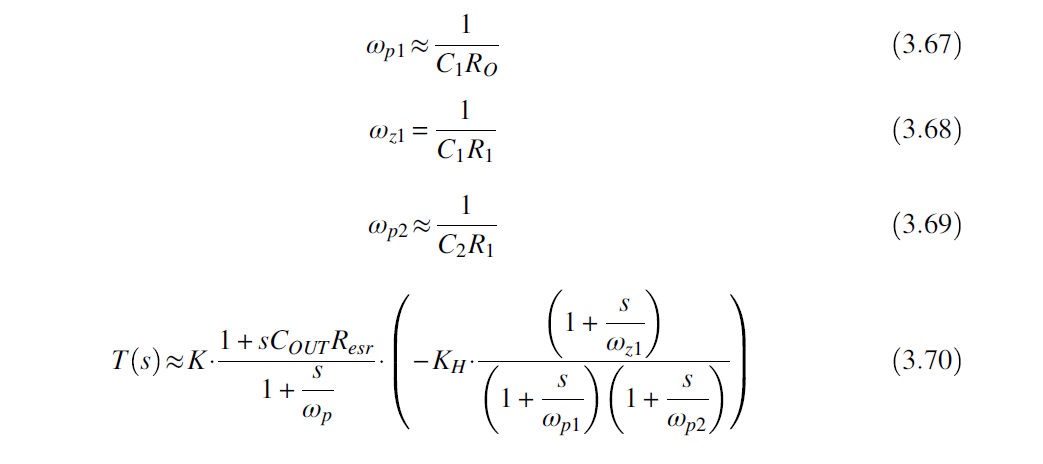

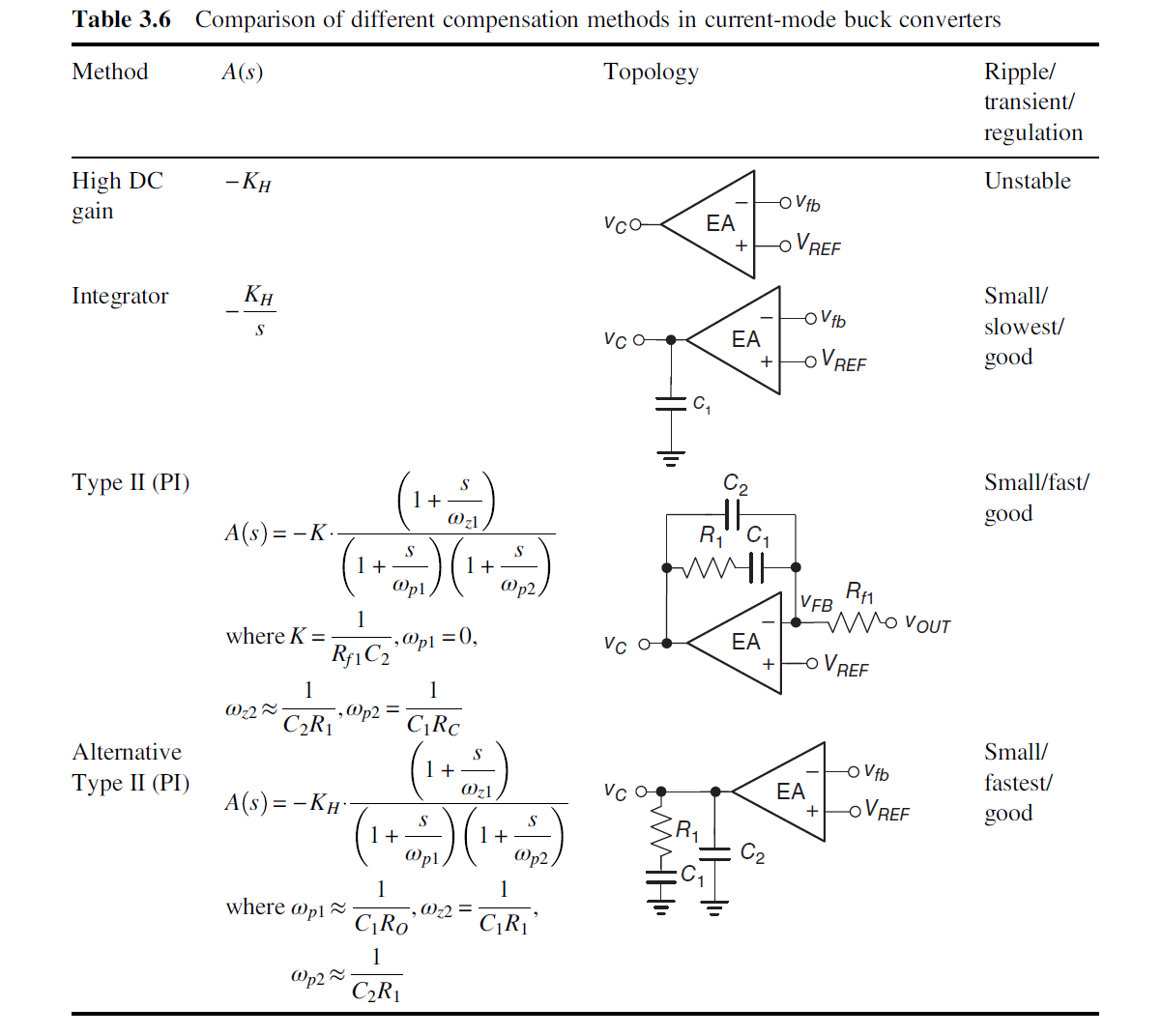

電流模補償采用KH/S積分器或者Type II補償, 即加入原點極點wp1, 低零點wz1和高頻極點wp2, 提高DC gain, 和零點補償phase.

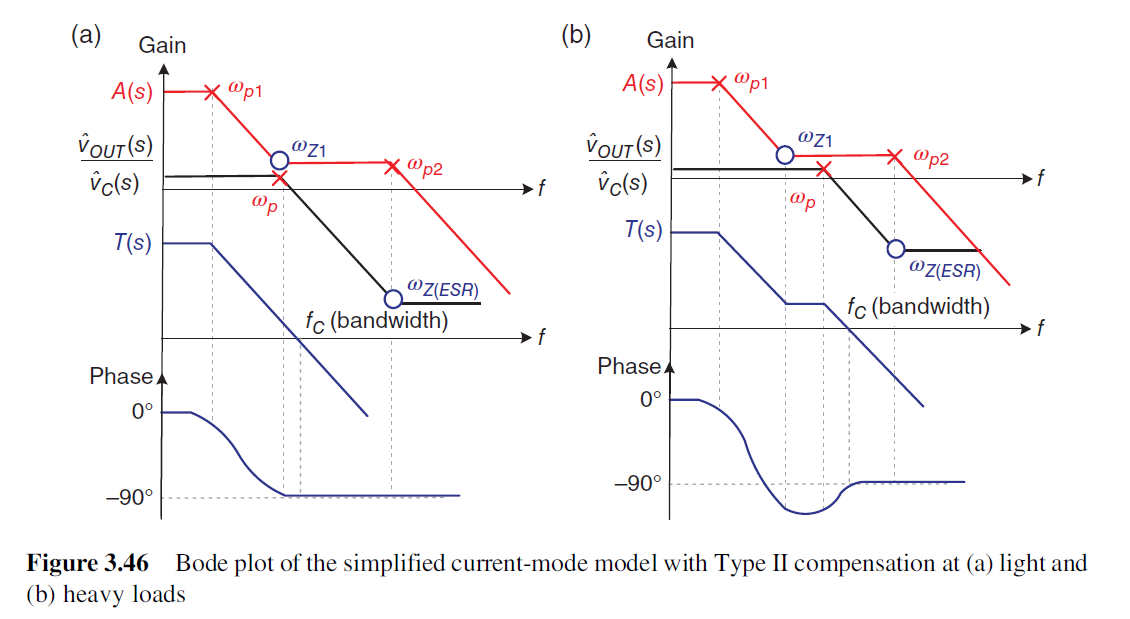

用Type II在輕載和重載下的bode plot如下圖所示

Type II電路實現如下圖所示, 這里EA為OTA, 沒有輸出電流能力.

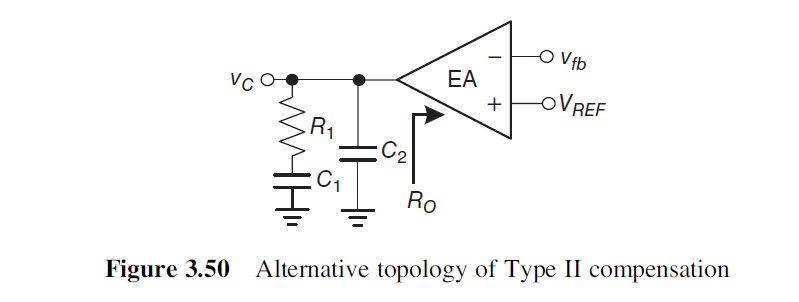

Alternative Type II電路實現如下圖所示, EA為buffer, 輸出電流能力

其主極點由RA輸出阻抗RO和C1決定. C1>>C2, R1和C1構成零點.

Alternative Type II在使用相同電容電阻時, 帶寬更寬30KHz->90KHz, 因此load transient的undershoot和overshoot更小 (263mV->146mV), recover time也更小 (110

us->54us).

電流模補償總結如下所示, 一般采用Type II補償, 加大帶寬, 改善瞬態響應.

:three states)

![[學習] Hilbert變換:從數學原理到物理意義的深度解析與仿真實驗(完整實驗代碼)](http://pic.xiahunao.cn/[學習] Hilbert變換:從數學原理到物理意義的深度解析與仿真實驗(完整實驗代碼))

——CRUD基礎)

)