第四十六問:鎖存器,觸發器,寄存器三者的區別

觸發器:能夠存儲一位二值信號的基本單元電路統稱為 "觸發器"。(單位)

鎖存器:一位觸發器只能傳送或存儲一位數據,而在實際工作中往往希望一次傳送或存儲多位數據。為此可把多個觸發器的時鐘輸入端 CP 連接起來,用一個公共的控制信號來控制,而各個數據端口仍然是各處獨立地接收數據。這樣所構,成的能一次傳送或存儲多位數據的電路就稱為 "鎖存器"。(不同步多位)

寄存器:在實際的數字系統中,通常把能夠用來存儲一組二進制代碼的同步時序邏輯電路稱為寄存器。由于觸發器內有記憶功能,因此利用觸發器可以方便地構成寄存器。由于一個觸發器能夠存儲一位二進制碼,所以把 n 個觸發器的時鐘端口連接起來就能構成一個存儲 n 位二進制碼的寄器。(同步多位)

第四十七問:用觸發器設計分頻器

如16分頻需要多少D觸發器

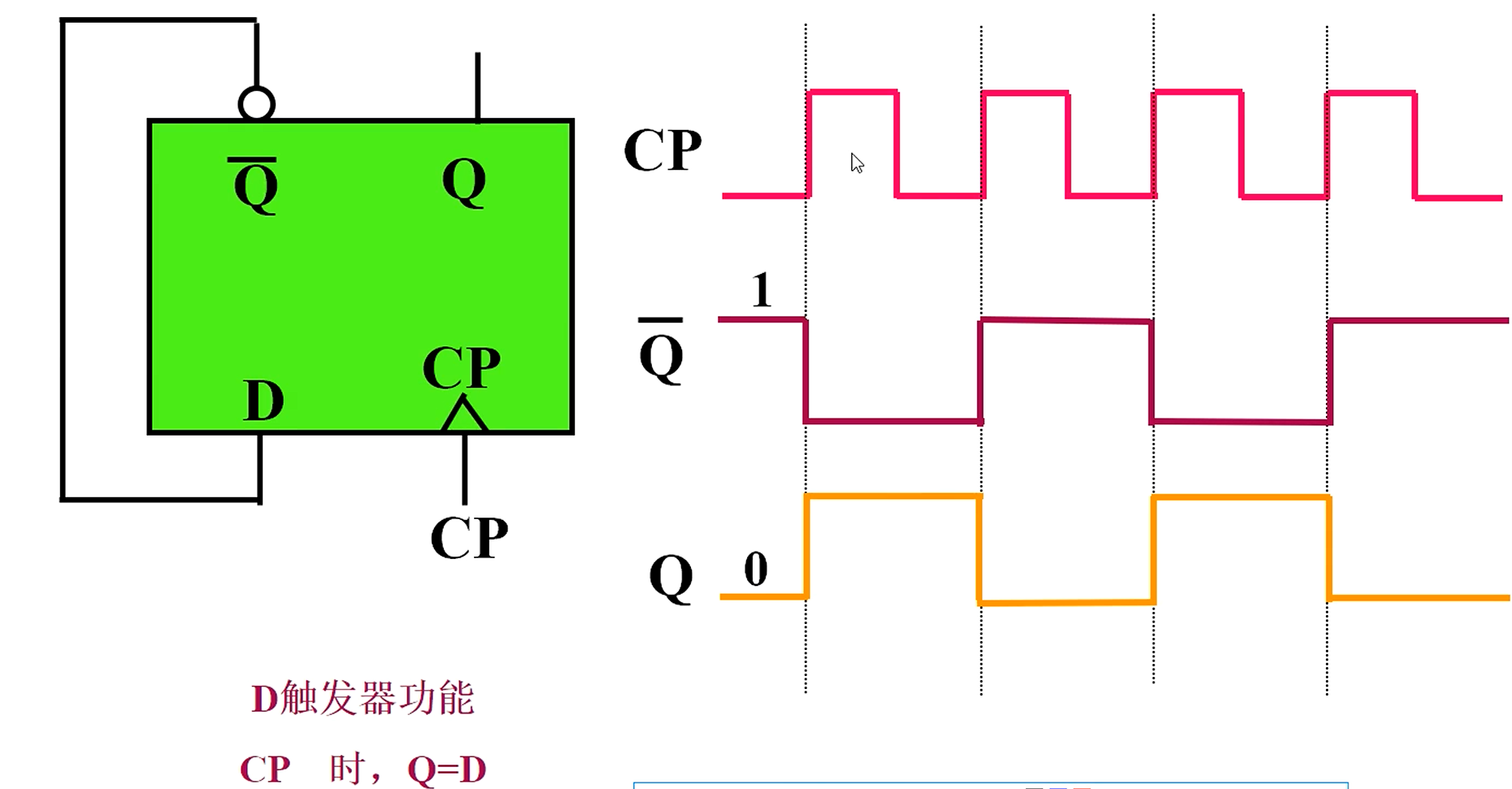

如圖已知D觸發器,位上升沿觸發,觸發時Q= D,Q非連接D;默認Q為低電平,CP時序如上圖。

得到上圖分頻結果;

如果要實現16分頻就把前一個觸發器的輸出連到下一個觸發器的時序輸入。?

注:除了D觸發器,其他觸發器也要了解。

第四十八問:ADC的原理

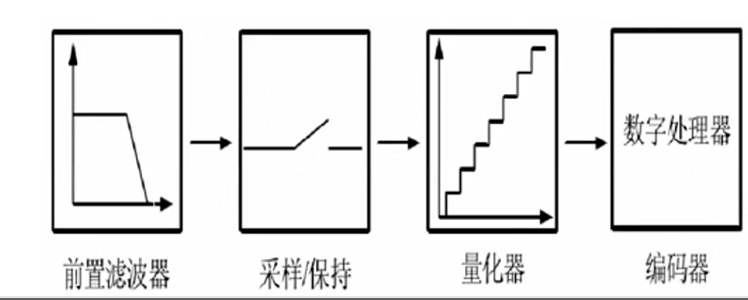

A/D 電路由取樣、量化和編碼三部分組成。

(1)模擬信號在時間上是連續信號而數字信號在時間上是離散信號,因此 A/D 轉換的第一步就是要按照奈奎斯特采樣定律對模擬信號進行采樣。

(2)數字信號在數值上也是不連續的,也就是說數字信號的取值只有有限個數值,因此需要對采樣后的數據盡量量化,使其量化到有效電平上。

(3)編碼就是對量化后的數值進行多進制到二進制的轉換。

?第四十九問:簡述DSP處理器與通用處理器在結構上的區別

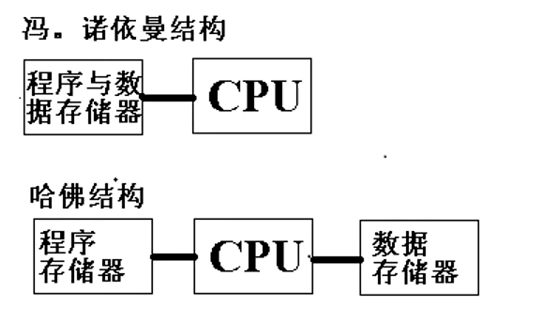

通用處理器采用馮。諾依曼存儲器結構。這種結構中,只有一個個存儲器空間通過一組總線連接到處理器核。通常,做一次乘法會發生 4 次存儲器訪問,用掉至少四個指令周期。

DSP 采用了哈佛結構,將存儲器空間劃分成兩個,分別存儲程序和數據。它們有兩組總線連接到處理器核,允許同時對它們進行訪問。這種安排將處理里器存貯器的帶寬加倍,更重要的是同時為處理器核提供數據與指令。在這種布局下,DSP 得以實現單周期的 MAC 指令。

第五十問:反射系數計算?

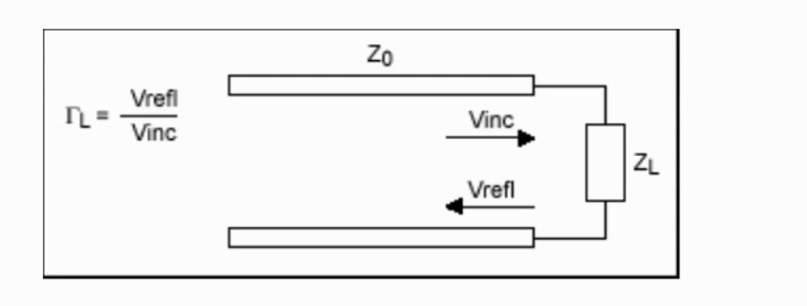

具體問題:假設A傳輸線的特征阻抗是70歐姆,B傳輸線的特征阻抗是:30歐姆,A傳輸線與B傳輸線相連,那么它們之間的反射系數是____

計算公式:

P=反射波振幅/入射波振幅

=(傳輸線特性阻抗-負載阻抗)/(傳輸線特性阻抗+負載阻擋抗)

即P=(Zb-Za)/(Zb+Za)

即(70-30)/(70+30)或者(30-70)/(30+70);

Transformers without Normalization)

)