歡迎關注BUG記錄知乎專欄和BUG記錄公眾號,關注BUG記錄公眾號回復101獲取本文使用的Simulink仿真文件

由于最近研究某個高速接口沒什么實質性的突破,實在寫不出太好的東西,所以就寫點更為基礎的東西分享給大家,順帶著自己也回憶回憶,防止自己西瓜也沒撿到,芝麻也丟了。

這個系列是以前通信原理課程的課設,通過實現BPSK可以學習到Simulink的使用仿真,m序列的verilog實現,Vivado/Xilinx的IP核調用,數據截位,查看數據波形等。

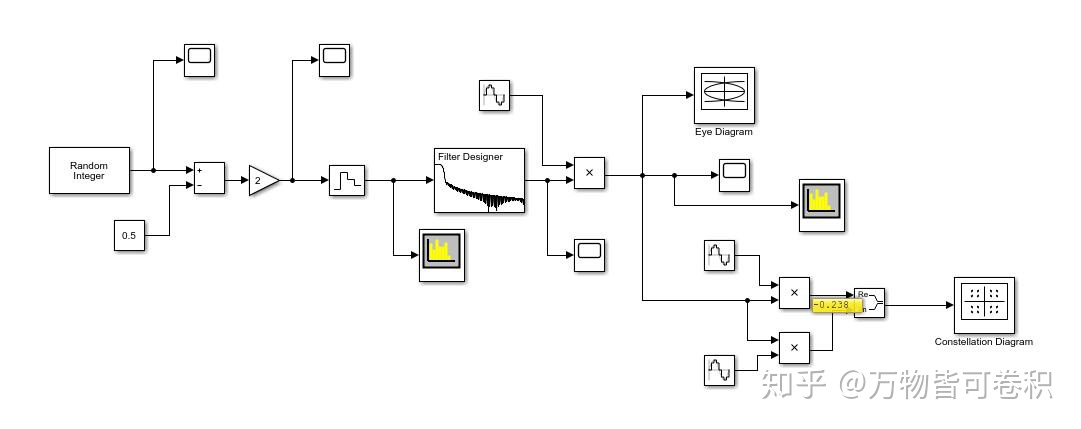

本次文章記錄的是BPSK的Simulink實現,會重點介紹幾個Simulink模塊的作用。

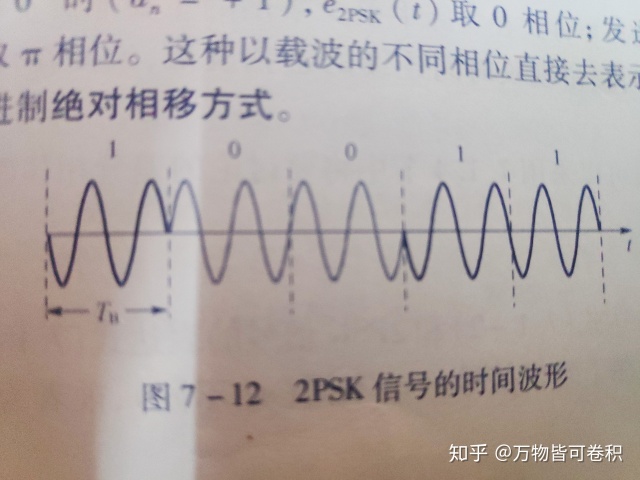

相移鍵控(BPSK)主要是利用載波的相位變化傳遞數字信息,傳遞過程中振幅和頻率保持不變。通常使用初始相位0和pi分別表示二進制的“0”和“1”;

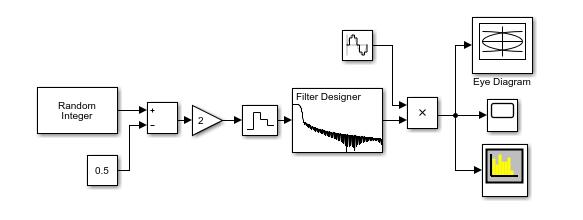

從《通信原理》關于BPSK的講解中可以知道,BPSK的調制方式有模擬調制方法和鍵控法;我們選擇模擬調制,并使用Simulink做仿真,框圖如下:

接下來對各個主要模塊的講解:

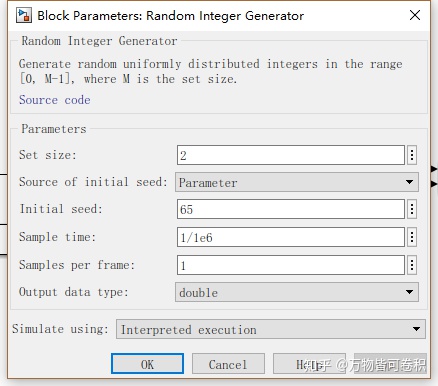

- Random Integer

偽隨機數發生器,可以通過Set size限定隨機數的上限,下限為0;偽隨機數不是真的隨機數,具有很長的周期,它的周期跟Initial seed有關;Sample time控制輸出數據的周期;

這個模塊作用是產生一個隨機序列,在FPGA中將使用m序列模塊實現其功能;

2. 符號映射模塊

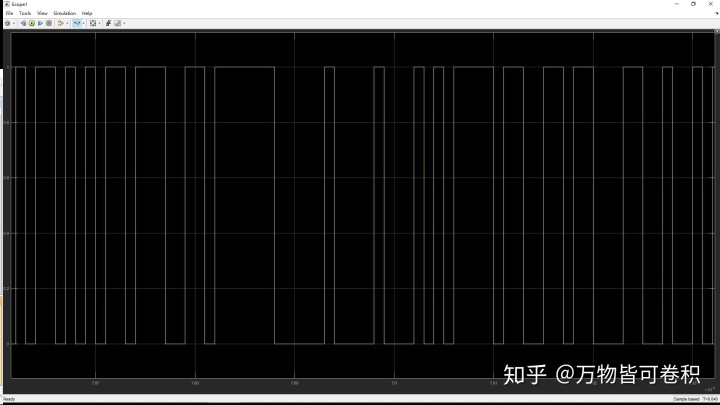

這個模塊在Random Integer后3個小模塊,偽隨機數發生器輸出的0,1經過減0.5后成為-0.5,0.5,乘2之后為-1,1;

也就是0 映射到-1,1映射到1;

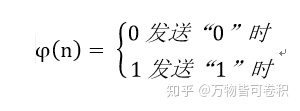

這么做的原因是為了簡化BPSK的過程,

由上面這個公式可以知道,當需要發送初始相位π時,只需要將cos(wt)乘以-1;這里我們假設的是發送“0”時初始相位為π,發送1時初始相位為0,如果想要保持與上圖1一樣的初始相位,可以使用乘以-2代替乘以2,實現0 映射到1,1映射到-1;

注意當產生QPSK等信號時,就不能采用這種方法,需要使用到IQ兩路信號產生基帶信號。

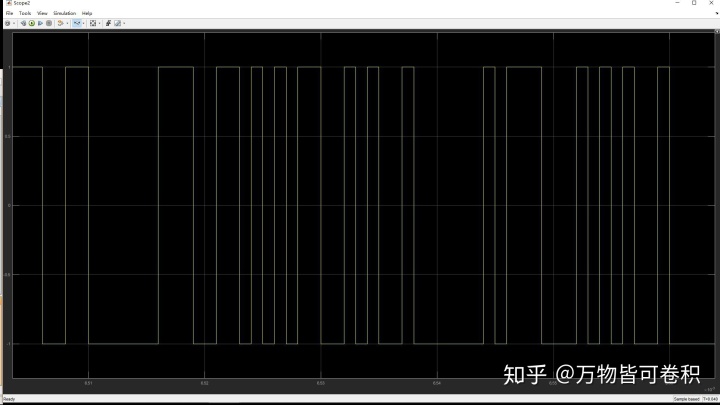

3. 升采樣及基帶濾波模塊

Simulink的例子中,偽隨機信號發生器的符號速率為1Mbps,經過Zero-Order Hold模塊將前面模塊產生的模擬信號轉換為數字信號,采樣率為50MHz;

由于偽隨機信號發生器及符號映射模塊產生的信號為-1和1,產生信號是矩形信號,而根據傅里葉變換的知識可以知道,矩形信號的頻譜是基波加上一系列奇次諧波,為了減小基帶信號的信號帶寬,我們需要使用低通濾波器盡量濾去諧波分量,保留矩形信號的基波;

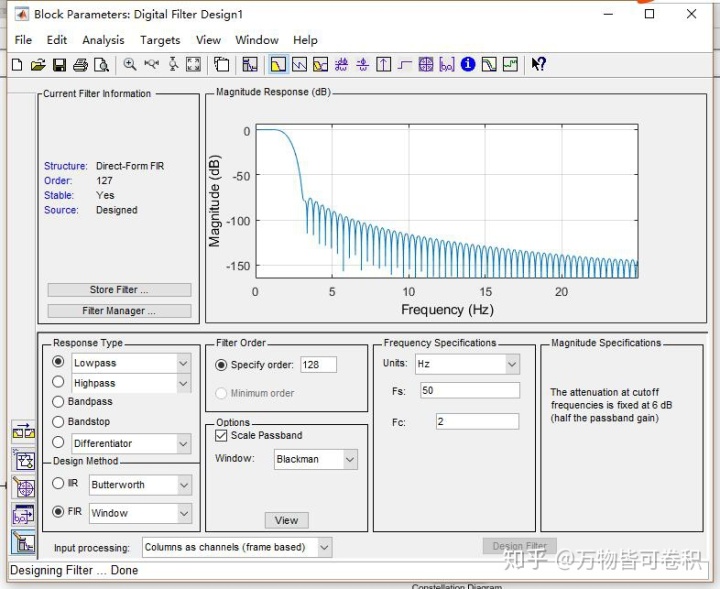

Digital Filter Design設置界面很簡單,勾選Lowpass,選擇FIR,選擇階數128,窗函數選擇Blackman,截止頻率與采樣率之比為2:50;數字濾波器采樣率和截止頻率的單位不重要,兩者之間的比率較為重要;而例子中此時信號為50MHz,所以截止頻率為2MHz;

這個模塊在FPGA中將使用相應的IP核實現功能;

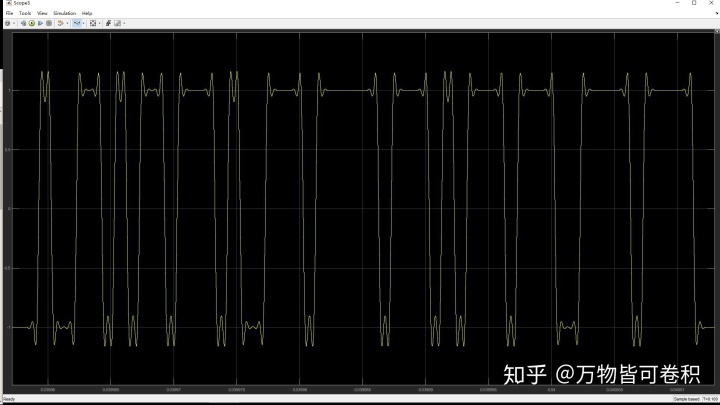

4.上變頻模塊

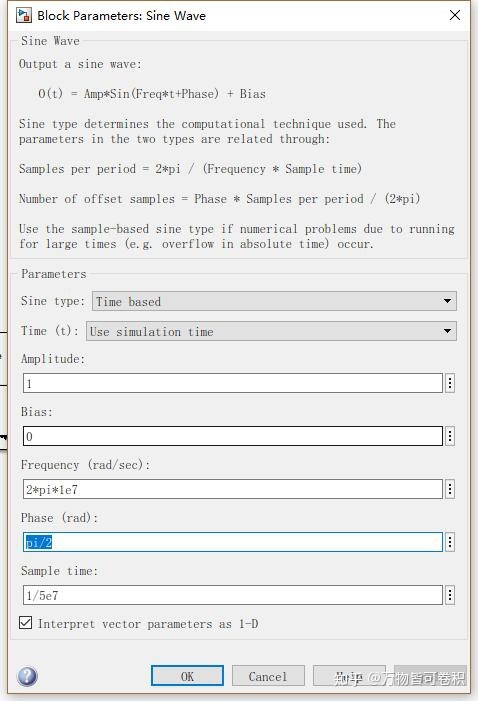

因為基帶信號的頻率較低,實際應用中考慮到天線長度,信號頻譜利用等原因,需要使用上變頻將信號搬移到較高頻率,我們在仿真過程中將基帶信號搬移到10MHz,這就需要將基帶信號與10MHz的正弦波相乘;

Sine Wave模塊的設置較為簡單,設置好幅度Amplitude,頻率Frequency,初始相位Phase和采樣率Sample time后;通過Product模塊將其與基帶信號相乘,輸出就是BPSK的仿真信號;

這個模塊在FPGA中將使用相應的IP核實現功能;

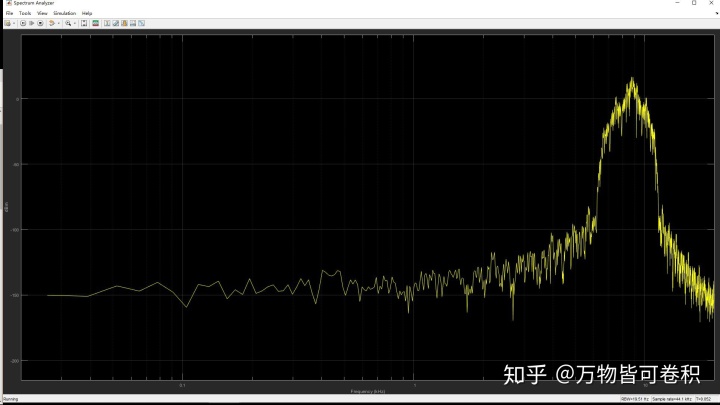

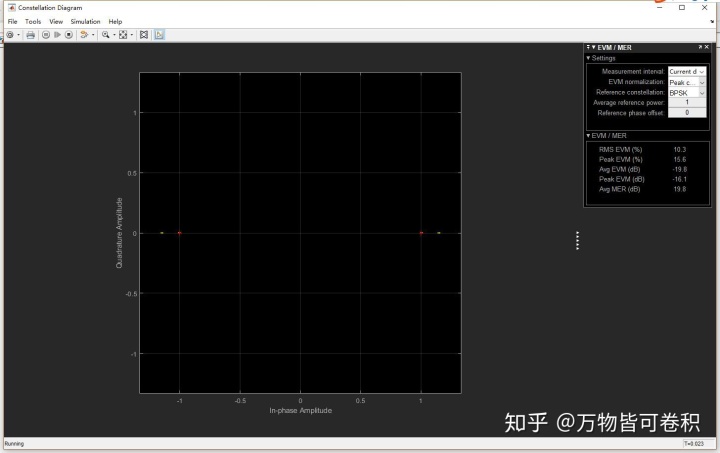

5. 輸出結果

通過偽隨機信號發生器,符號映射,FIR濾波,上變頻模塊后,一個完整的BPSK信號產生了;

雖然這整個仿真過程可能不夠嚴謹,但我們的重心在于verilog實現,接下來會依次講到相應模塊的verilog實現,在這個過程中我回憶和鞏固自己所學的知識,歡迎大家關注。

如果對這個Simulink有更好的改進方法方案可以留言一起談論,歡迎大家點贊收藏留言討論交流。

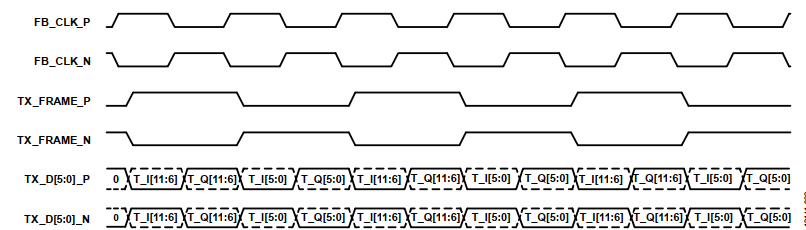

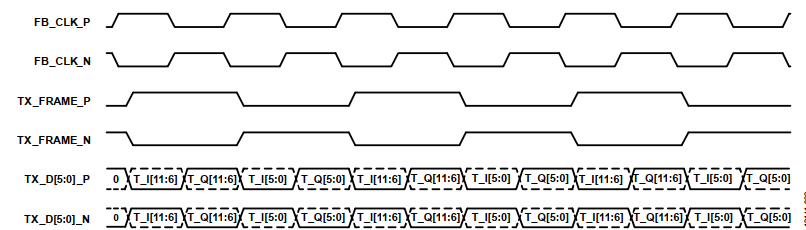

萬物皆可卷積:(LVDS差分信號簡單處理)5. 使用OSERDES發送高速串行數據?zhuanlan.zhihu.com

![arima模型_[不說人話系列]-ARIMA模型](http://pic.xiahunao.cn/arima模型_[不說人話系列]-ARIMA模型)

模擬卷客觀題...)

圖像可視化)

HashMap 源碼原理詳解)

![python計算執行時間的函數_[python] 統計函數運行時間](http://pic.xiahunao.cn/python計算執行時間的函數_[python] 統計函數運行時間)