2 Verilog HDL的設計方法學——層次建模

- 重要的思想:

在語文教學中,應該先掌握核心方法論,再用正確的方法論去做題目,這樣能夠逐漸加深對于方法論的理解,做題的速度和準確率也會越來越高。 - 在Verilog HDL中,該思想同樣適用,在編程,軟件開發也一樣如此

2.1 設計方法學——層次建模

2.1.1 方法理論

- 自上而下設計方法

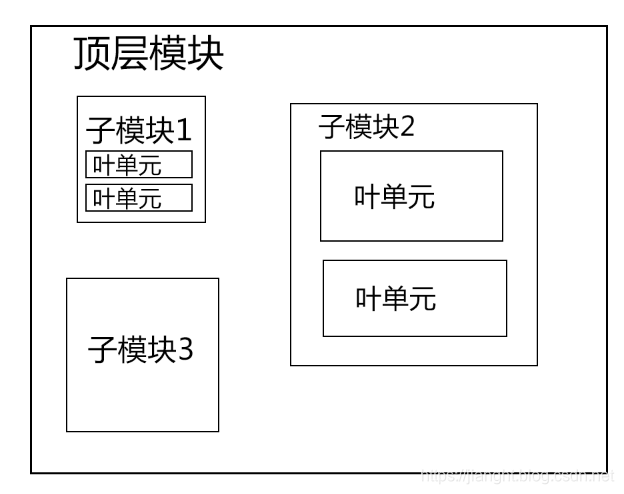

設計者先設計出頂層模塊,然后將其拆解,分析出其內部模塊,再進一步為更小的、已知的功能單元。用流程圖可以進行如下表示

圖示:

- 自下而上的設計方法

設計者使用功能確定是小的功能單元,組合成大的功能單元,然后逐漸增大,流程圖即上面的箭頭反向

2.1.2 實際應用

在實際使用設計方法學的過程中,往往采用二者結合的方式,程序員一邊設計頂層的架構,一邊將小模塊組合成大模塊,上下同時進行,然后進行對接。

實際的流程往往是這個樣子的

這個過程中,對于小單元的實現,是自下而上的,對于整體架構的實現,是自上而下的。

當然,其實這樣的流程過于抽象,并且也不是唯一的,我們看后面的實例部分來深入理解思想即可,大可不必生搬硬套。

2.2 應用層次建模思想設計Verilog HDL程序

具體內容請參考書籍《Verilog HDL:A Guide to Design and Synthesis》(Second Edition)

先來闡述核心概念:

- 模塊與模塊實例

- 設計塊與激勵塊

2.2.1 模塊與模塊實例

對于模塊與模塊實例的關系,和C++中模板與模板實例的關系是類似的

在Verilog HDL中,模塊是基本功能單元,它可以是

- 葉單元

- 子模塊

- 頂層模塊

在更高級的模塊中,可以調用低級模塊實例來構建,也有了一條重要的原則:

- 下級模塊實例,被調用,來構建上級模塊

總而言之,Verilog的核心設計,是由模塊構成的,不同等級的模塊通過模塊實例進行相互調用來建立聯系

每一個模塊,都是一個有接口,有功能,但是內部細節不可見的科技黑箱

每一個模塊實例,都是模塊的副本,可以被它的上級模塊調用

2.2.2 設計塊與激勵塊

- 設計塊就是2.2.1中構建的最上級的模塊,即頂層模塊

- 激勵塊就是用來驗證設計塊的正確性

問題:什么是“激勵”?

先來舉一個類似的例子,在物理電路實驗中,我們連接好電路,然后給他加上電源通電,驗證電路是否連接正確。

在Verilog設計中,我們的“設計塊”就是電路,“激勵塊”就是電源,“仿真測試”就是通電。這樣的類比應該非常清晰明確了,再畫個表格對比。

| Verilog HDL | 電路實驗 |

|---|---|

| 設計塊 | 電路 |

| 激勵塊 | 電源 |

| 仿真測試 | 電路通電 |

激勵塊的作用:

給設計塊加上具備指定特征的信號,來測試設計塊的正確性和效率

激勵塊的兩種設計模式:

- 激勵塊中調用設計塊實例,直接接入信號驅動設計塊

- 生成一個新的“虛擬的”頂層模塊,調用激勵塊實例和設計塊實例,讓二者接口進行交互,通過信號傳遞間接驅動設計塊

舉個例子你就明白了

- 方式一:手動點火來引爆炸藥

- 方式二:使用引爆器引爆炸藥

2.2.3 使用規則

- 模塊、模塊實例和激勵塊的命名,必須是唯一的,不能重名

- 模塊不能嵌套定義,但是模塊內部可以進行其他模塊的聲明或調用其他模塊實例

- 模塊由module開始,endmodule結束

2.2.4 示例

2.3 思考:層次建模在Verilog與C/C++應用的區別

層次建模的思想,一直都應該存在,但是在具體實現中,Verilog設計使用自上而下的設計是可能的,因為模塊相對簡單,接口相對確定,只需要設置好接口,知道需要的模塊和功能即可。

但是對于高級語言來說,自上而下的在紙上設計框架是可以的,具體實現并不能這樣的做,因為它的低層框架同樣是非常復雜的,并不能直接提前設計好,尤其是對于大框架嵌套小框架的情況,一定要先設計好小框架,再完成大框架,也就是自上而下地設計,自下而上地實現。

對于并行的中層框架來說,實現順序也需要按照執行順序來編寫。

2.4 疑問解答

對于第一章提到的問題,現在可以解答了。【Verilog HDL學習之路】第一章 Verilog HDL 數字設計總論

問題1:對于過程“RTL級描述描述–>門級網表”,門級網表等同于門級描述嗎?

問題2:行為級綜合工具的出現允許Verilog HDL進行行為級描述,那么它是可以將行為級描述轉換為RTL級描述嗎?

回答以上兩個問題,Verilog HDL的設計者可以使用四種抽象層次對模塊進行描述,最終通過綜合工具后,一般生成的是門級結構的描述

另外補充一點,RTL級描述,通常指的是能夠被邏輯綜合工具接受的行為級描述和數據流級描述的混合描述

)

)