1. 實踐得到的啟發

先從一個簡單的現象得出結論,Verilog語句是并發執行的!

同時,這也是**$monitor系統任務為全局有效**的一個重要支持因素,如果沒有并發,它是完不成這項功能的實現的。

眾所周知,高級語言通常都是自上而下編譯和執行的,但是Verilog硬件描述語言不一樣,它更喜歡并發執行。

這是一門直接觸及底層硬件編程的語言,效率非常高,并發執行是為了適應它所處的環境。

先來看看一下激勵塊代碼:

module stimulus;// 設置激勵信號reg I0 = 1,I1 = 0,I2 = 1,I3 = 0,I4 = 1,I5 = 0,I6 = 1,I7 = 0; // 輸入數據信息reg S2,S1,S0; // 地址輸入端信息,注意使用“小端序”wire OUT; // 輸出數據mux8_to_1 M8T (I0,I1,I2,I3,I4,I5,I6,I7,S2,S1,S0,OUT);// 設置信號監視器initialbegin$monitor ($time," S2 = %b, S1 = %b, S0 = %b, OUT = %b\n",S2,S1,S0,OUT); // 注意【\n】end// 設置激勵信號initialbegin// $display ("I0 = %b, I1 = %b, I2 = %b, I3 = %b, I4 = %b, I5 = %b, I6 = %b, I7 = %b\n"// ,I0,I1,I2,I3,I4,I5,I6,I7);#1 S2 = 0; S1 = 0; S0 = 0;#1 S2 = 0; S1 = 0; S0 = 1;#1 S2 = 0; S1 = 1; S0 = 0;#1 S2 = 0; S1 = 1; S0 = 1;#1 S2 = 1; S1 = 0; S0 = 0;#1 S2 = 1; S1 = 0; S0 = 1;#1 S2 = 1; S1 = 1; S0 = 0;#1 S2 = 1; S1 = 1; S0 = 1;endendmodule

輸出結果為:

0 S2 = x, S1 = x, S0 = x, OUT = x1 S2 = 0, S1 = 0, S0 = 0, OUT = 1

2 S2 = 0, S1 = 0, S0 = 1, OUT = 0

3 S2 = 0, S1 = 1, S0 = 0, OUT = 1

4 S2 = 0, S1 = 1, S0 = 1, OUT = 05 S2 = 1, S1 = 0, S0 = 0, OUT = 1

6 S2 = 1, S1 = 0, S0 = 1, OUT = 0

7 S2 = 1, S1 = 1, S0 = 0, OUT = 1

8 S2 = 1, S1 = 1, S0 = 1, OUT = 0

觀察可得,不僅僅兩個initial塊是并發執行的,并且他們還是從仿真時刻為0的時候就開始并發執行了。

【疑問】(未解決)

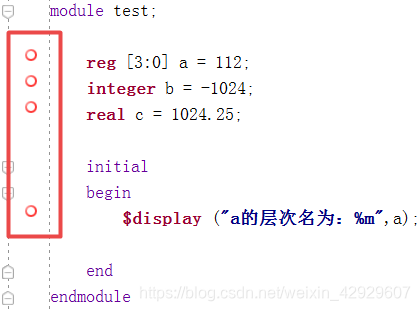

Vivado 2017.4中

紅圈圈是意味著并發執行嗎?暫時不知道,后續再研究。

——————————

后續深入內容以后再說

)

)

, ntohl() , htons(), htonl(), inet_ntoa(), inet_pton(), atoi()匯總)

)