0 確定問題的討論層級與范圍

本文討論的層次是

- 數字邏輯與Verilog HDL語言

討論的范圍是:

- 數據存儲而不是討論邏輯

1 線網類型

1.1 wire類型

這個暫時沒什么好說的,一般常用的就是wire類型,需要注意的是:

- 默認是標量,相當于一個二進制位

- 不能隨意存儲數據,只能流通數據

- 可以使用向量和數組修飾進行拓展

2 寄存器類型

2.1 reg類型

2.1.1 關于無符號數的問題

先接受一個事實,聲明為reg類型的寄存器為無符號數,integer和real類型為有符號數,請先接受這個事實,不要懷疑它,接下來我將通過實驗為你驗證它的確如此!

reg a = -4‘d9;

reg b = -4'sd9;

輸出均為 7 也就是負數的補碼對應的十進制數字

2.1.2 關于越界的問題——數據存儲的通用法則

這與邏輯運算不同,不是非0即為1,遵循的規則是:

越界丟失

事實上,這條規則對于所有的需要使用數值的數據類型都適用,對于reg和net一類類型都一樣的

簡而言之,不能吃太飽,要是撐破了,多出來的部分就會歸零。

例如:

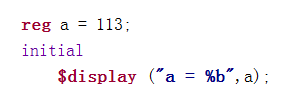

reg a = 112;

$display ("a = %b\n",a);

輸出為:

a = 0;

因為a是一位,112的二進制為111 0000,故前幾位丟失,只保留最后一位0

因此,如果a = 113那么將會被儲存為1

得到輸出結果:

擴展:多角度分析數值越界問題

2.1.3 關于補碼的問題

計算機只要知道這是個補碼,肯定會正確翻譯出來一個負數,但是,得用正確的數據類型才行,否則依然不能正確翻譯出來,比如對于負數,不能使用reg類型, 只能用integer或者real這種支持有符號數的數據類型!

2.2 integer類型

用來表示整數,可以有正負號

最小32位,輕易不用管它,不用指定位寬,按照默認就好,說了最小32位就是32位,指定31位也會變成32位,這種規則不要挑戰,沒有用的。

2.3 real類型

用來表示實數,即可以表述帶小數點的數,可以有正負號

2.4 time類型

最小64位,與具體實現有關,用來表示時間,通常與$time配合使用

time sim_time = $time; // 存儲當前仿真時間

2.5 小結

| 類型 | 使用 | 位寬 | 備注 | 字符串格式 |

|---|---|---|---|---|

| reg | 一般通用 | 默認為1 | 無符號數 | %b %B |

| integer | 整數 | 最小32位 | 有符號數 | %d %D |

| real | 實數 | 最小32位 | 有符號數 | %f %F |

| time | 仿真時間 | 最小64位 | 表示仿真時間 | %t %T |

注意:

- 以上4個類型中,只有reg類型能加向量修飾,以便于進行位寬的拓展integer和real類型與主機字的位數一致,與具體實現有關

- time位數與具體實現有關

- 字符串的顯示看具體需求,無強制要求,上述只是列舉了針對性對應的字符串

補充概念:計算機的字的位數

計算機位,字,字節,字長詳解

)

)

, ntohl() , htons(), htonl(), inet_ntoa(), inet_pton(), atoi()匯總)

)

:RadASM的安裝和使用說明)

)