1. 端口設計的方法

1.1 數據選擇器

以四選一數據選擇器為例,需要的不同接口類型為

- 輸入端口

- 數據輸入端口

- 地址輸入端口

- 使能端(控制與拓展)

- 輸出端口

- 數據輸出端口

2. 端口拓展的方法——層次建模思想

2.0 兩個拓展方向

2.0.1 “數組型”拓展——分治思想與屏蔽理論

這種拓展形式與數組類似,數組可以是由一根線拓展為多根線

舉個例子:四選一數據選擇器拓展為八選一數據選擇器就是**“數組型拓展”**

增加使能端,使四選一數據選擇器能夠實現拓展,拓展為八選一。

分治思想

兩個四選一數據選擇器,各管一頭,分別掌管8個數據輸入端的4個,通過使能端來控制哪個選擇器起作用。

屏蔽理論

對于兩個四選一數據選擇器來說,其中一個起作用,另外一個就不能起作用,想當于被屏蔽了,這個時候,使能端就發揮了作用,將兩個數據選擇器的使能端接在一起,使其變成地址輸入端的最高位,第三位,并且其中一個在連接的時候加上非門,實現同一時間下,只能有一個數據選擇器起作用

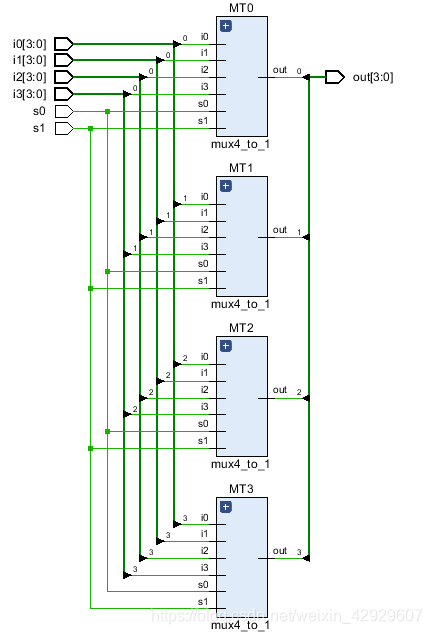

2.0.2 “向量型”拓展——類比思想(高速通道)

這種拓展形式與向量類似,向量可以由一根位寬為1的線拓展為一根位寬為n的線

舉個例子:四選一數據選擇器一般都是一位的,只能輸入0和1,將其拓展為位寬為n的總線,例如實現輸入/輸出數據可以是10,1092等更大的數字,這就是向量型拓展

核心實例說明:依次為起點進行類比,完成一系列的類似事情

從

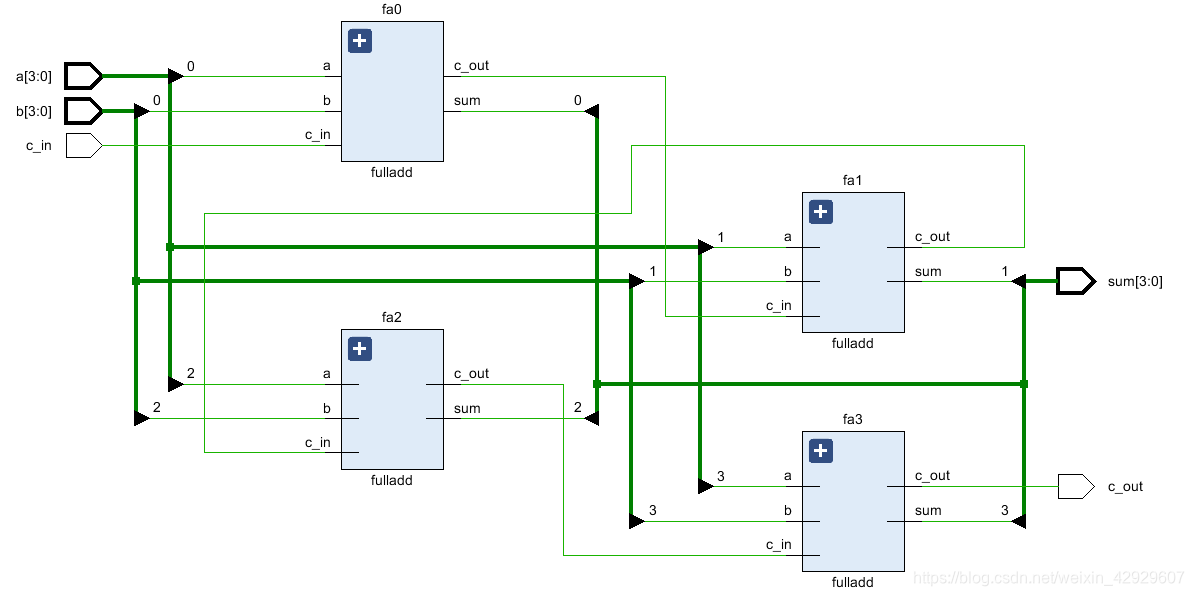

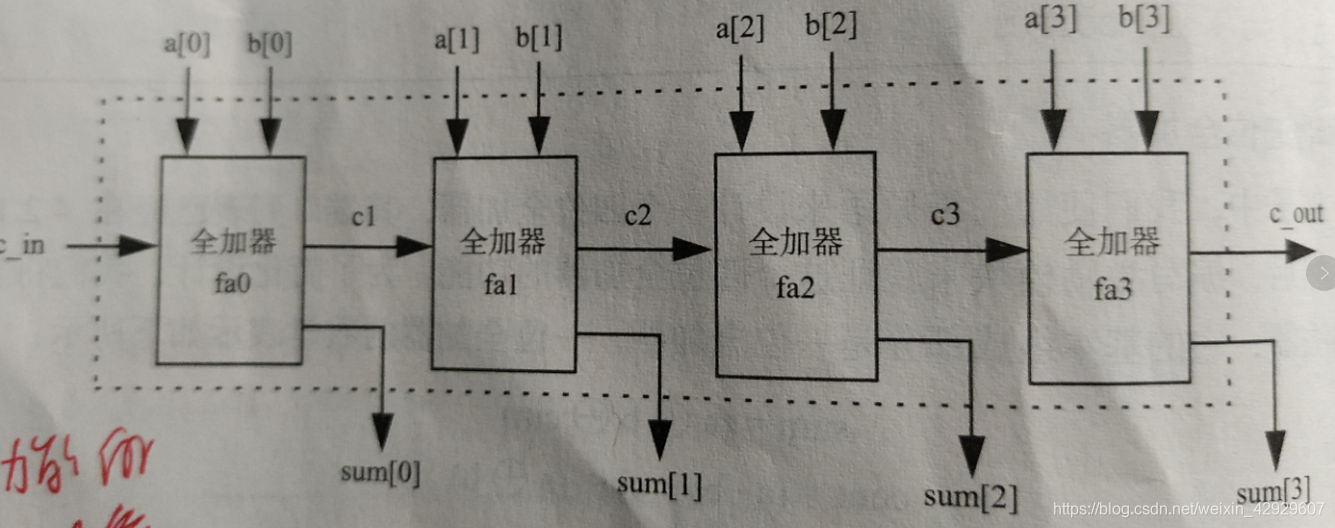

一位全加器到多位全加器的設計

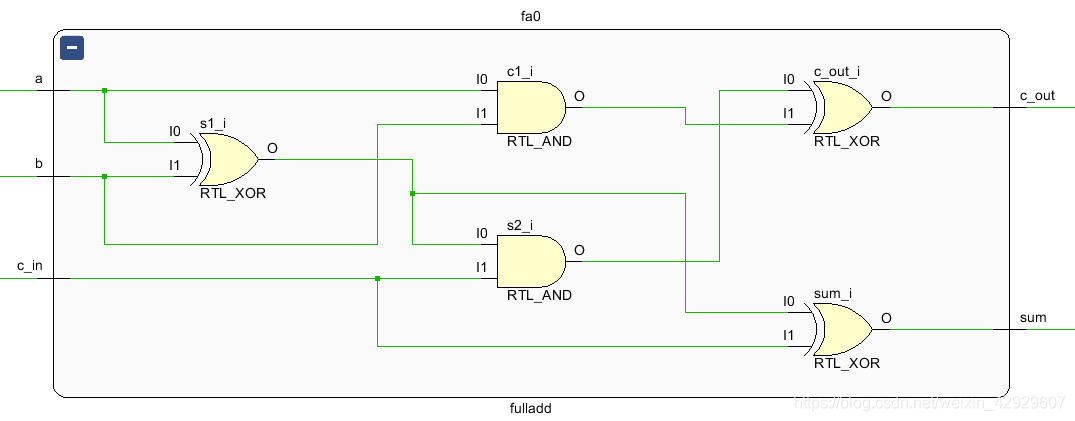

- 一位全加器

- 四位全加器

以下為簡化模型,更便于理解

類比得出

一位四選一數據選擇器到多位四選一數據選擇器

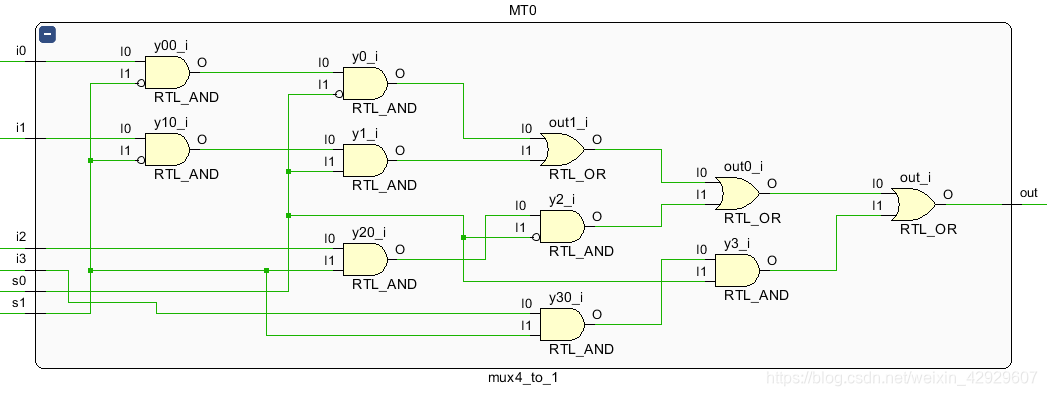

- 一位四選一數據選擇器

- 多位四選一數據選擇器

2.0.3 組合式拓展——類比存儲器的字位拓展

即需要數組型拓展也需要向量型拓展的目標,這個時候,類比存儲器的字位拓展方式,需要合理安排順序,確定是先進行什么拓展,再進行什么拓展,還是綜合考慮。

2.1 數據選擇器

2.1.1 數組型拓展

將2個四選一數據選擇器組合為八選一數據選擇器

2.1.2 向量型拓展

將一位四選一數據選擇器拓展為多位四選一數據選擇器

2.1.3 組合式拓展

將2個一位四選一數據選擇器拓展為1個多位八選一數據選擇器

————————

后續內容將以后更新

)

)

, ntohl() , htons(), htonl(), inet_ntoa(), inet_pton(), atoi()匯總)

)

:RadASM的安裝和使用說明)

)