本原創文章由深圳市小眼睛科技有限公司創作,版權歸本公司所有,如需轉載,需授權并注明出處(www.meyesemi.com)

1. 實驗簡介

實驗目的:

? ? ? 完成 PCIE 通信測試。

實驗環境:

? ? ? Window11

? ? ? PDS2022.2-SP6.4

硬件環境:

? ? ??MES2L676-100HP

2.實驗原理

? ? ? PG2L100H 集成內置了線速率高達 6.6Gbps 高速串行接口模塊,即 HSSTLP。PG2L100H 開發板 提供一個 PCIe x4 接口,PCIE 卡的外形尺寸符合標準 PCIe 卡電氣規范要求,可直接在普通 PC 的 x4 PCIe 插槽上使用。

2.1. PCIE 簡介

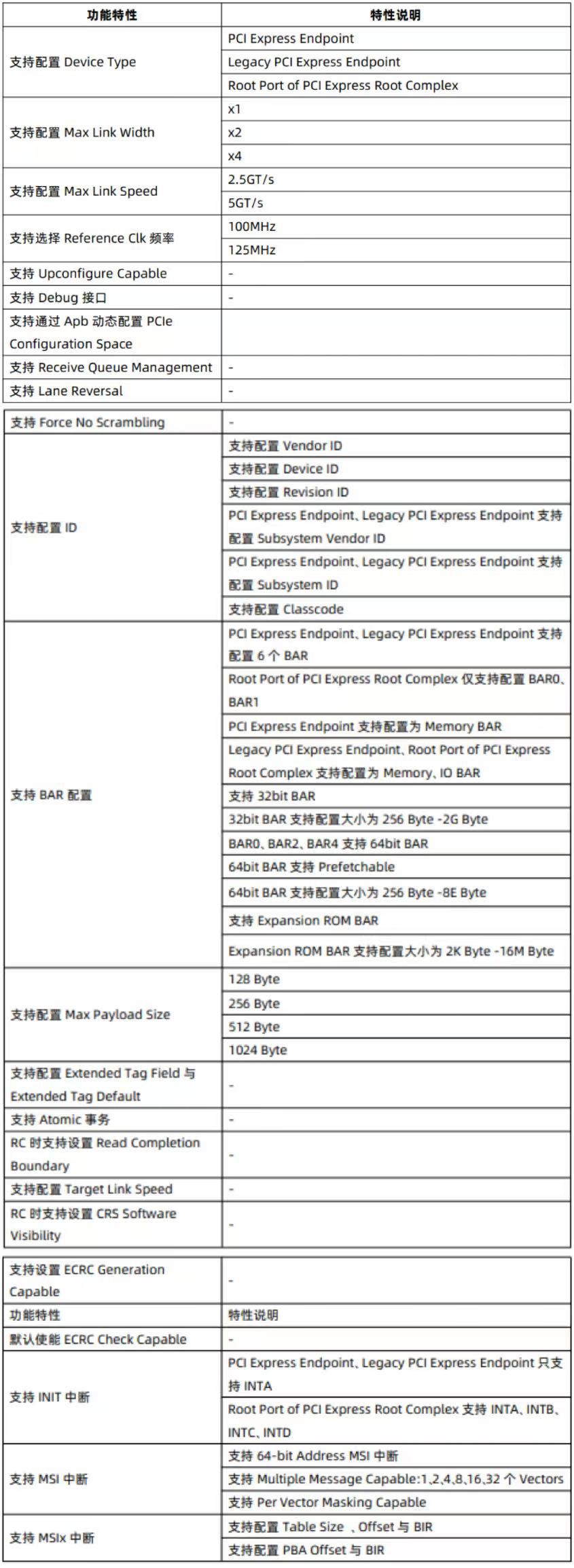

? ? ? PCIE IP 符合 PCI Express? Base Specification Revision 2.1[8]協議和 PHY Interface for the PCI ExpressTM Architecture Version 2.00[12](數據通路擴展為 32 bits)協議。

3. 工程說明

3.1. 安裝 PCIE IP 核

PDS 安裝后,需手動添加 PCIE IP,請按以下步驟完成:

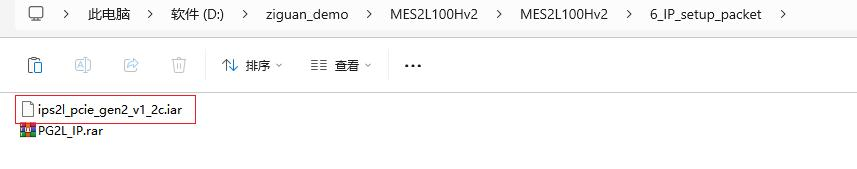

PCIE IP 文件:6_IP_setup_packet\ips2l_pcie_gen2_v1_2c.iar

3.2. PCIE 參考設計例程

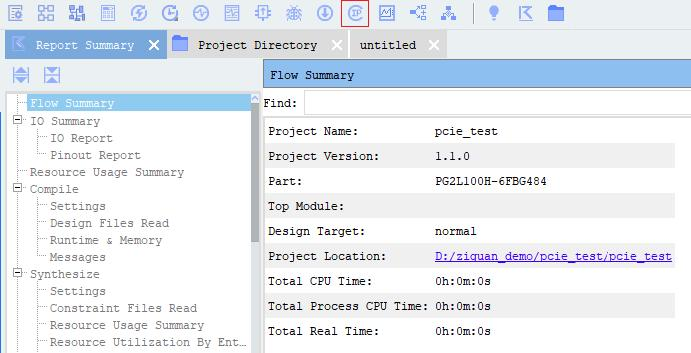

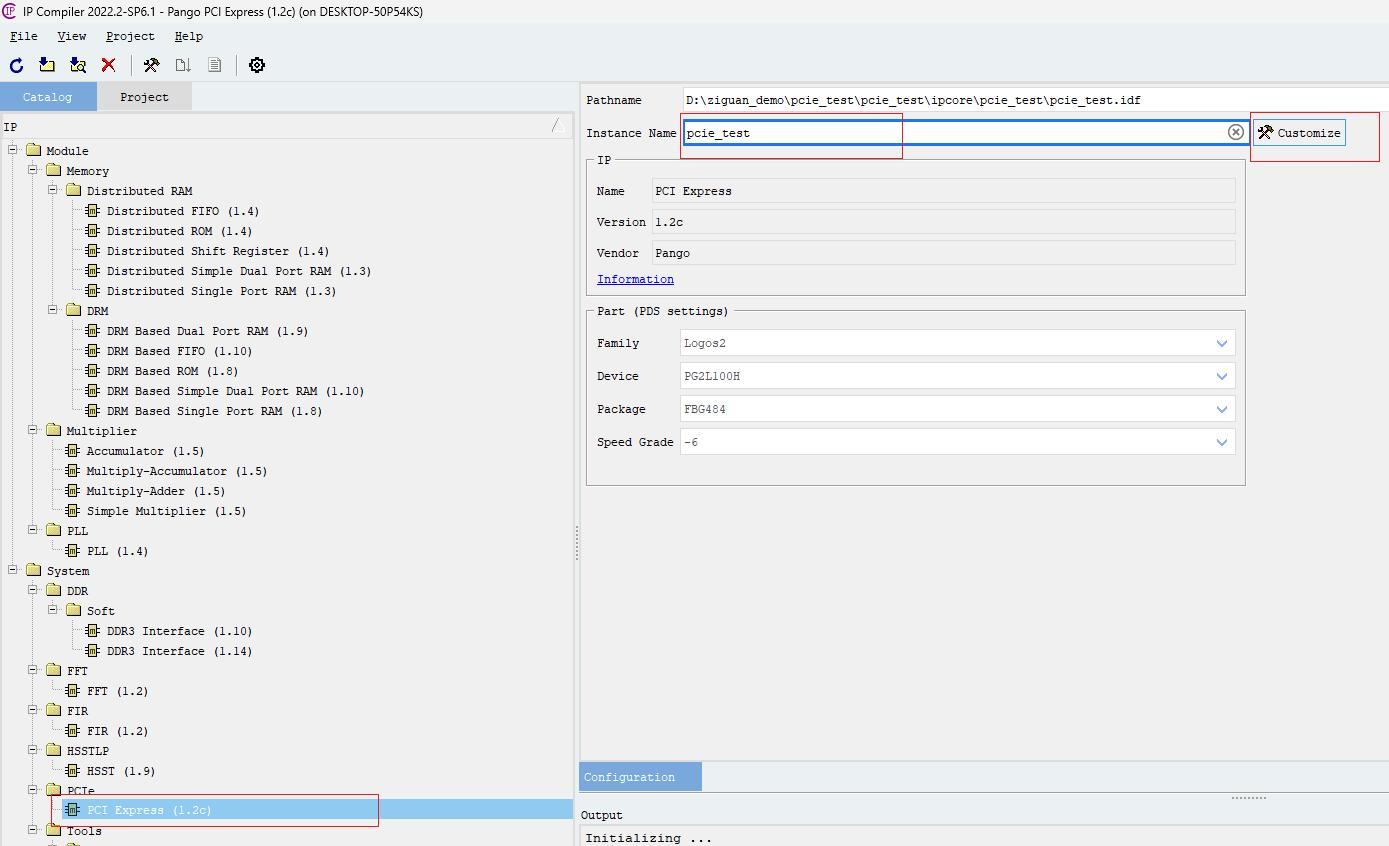

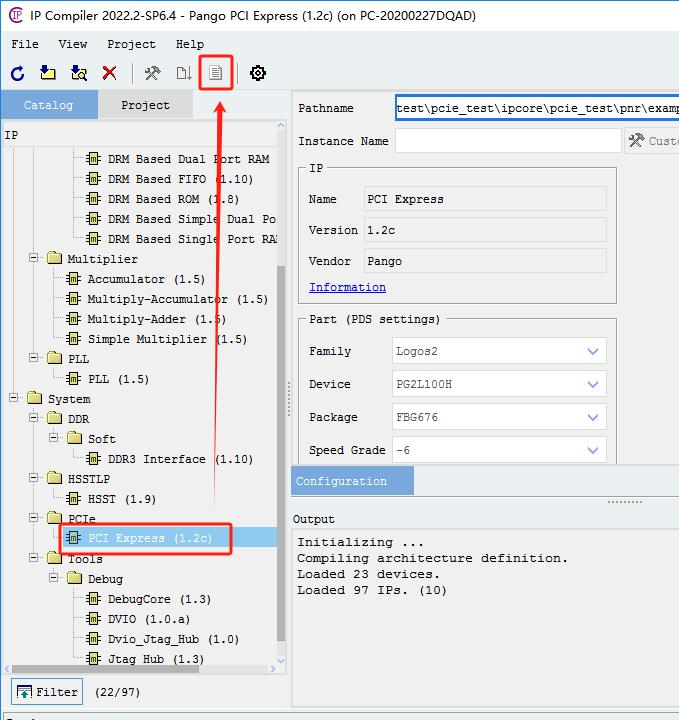

打開 PDS 軟件,新建工程 pcie_test,點開如下圖標,打開 IP Compiler;

選擇 PCIE IP,取名,然后點擊 Customize;

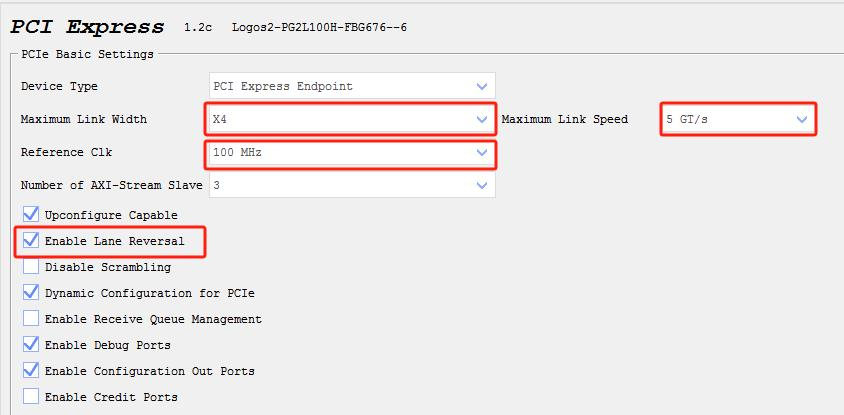

在 PCIE 設置界面中:根據開發板配置 lane 數,可選擇 X4,配置參考時鐘,可參考下圖:

需要注意的是,需要勾選上 Enable Lane Reversal,否則會導致 PCIE 實驗失敗。

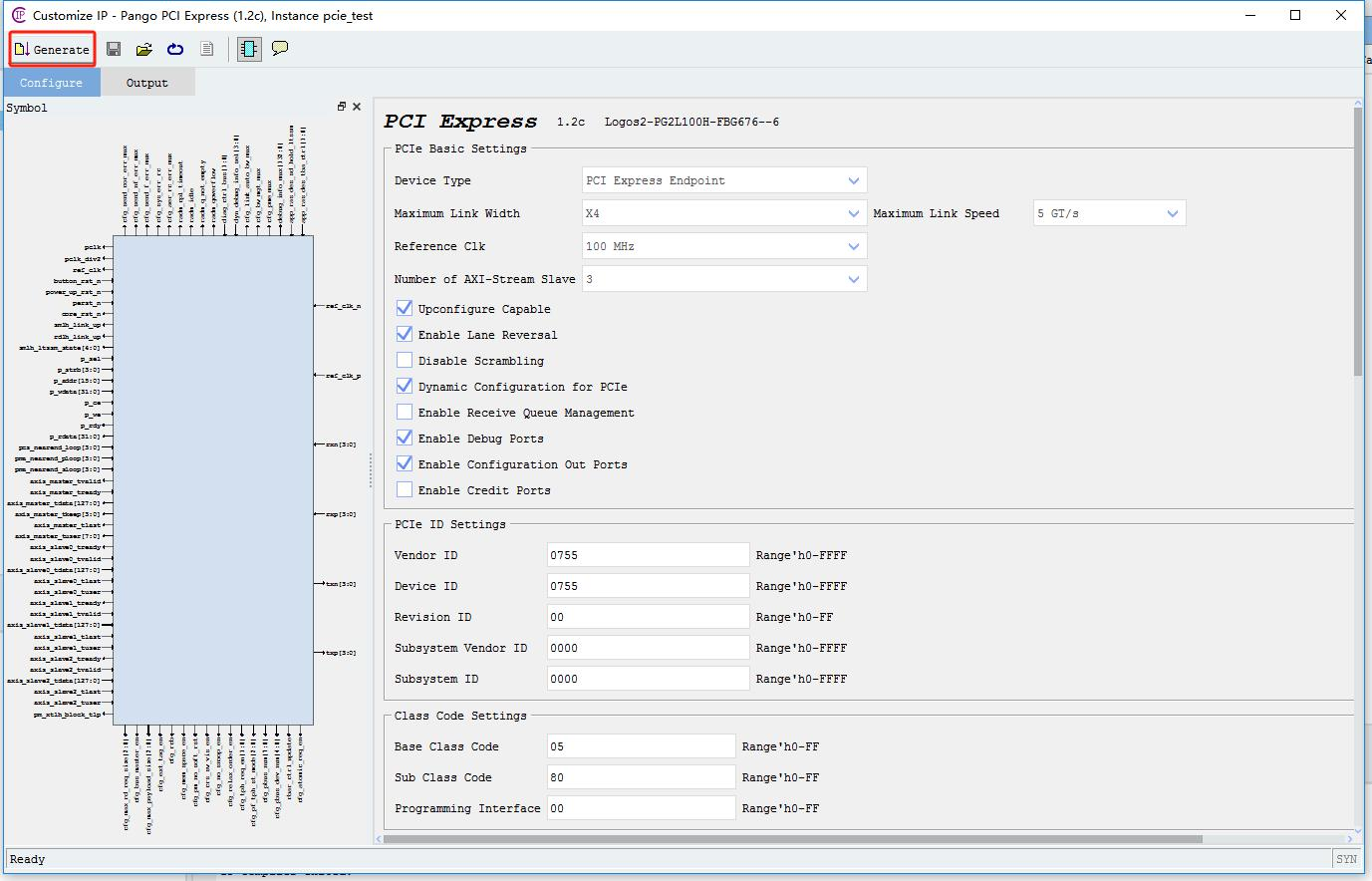

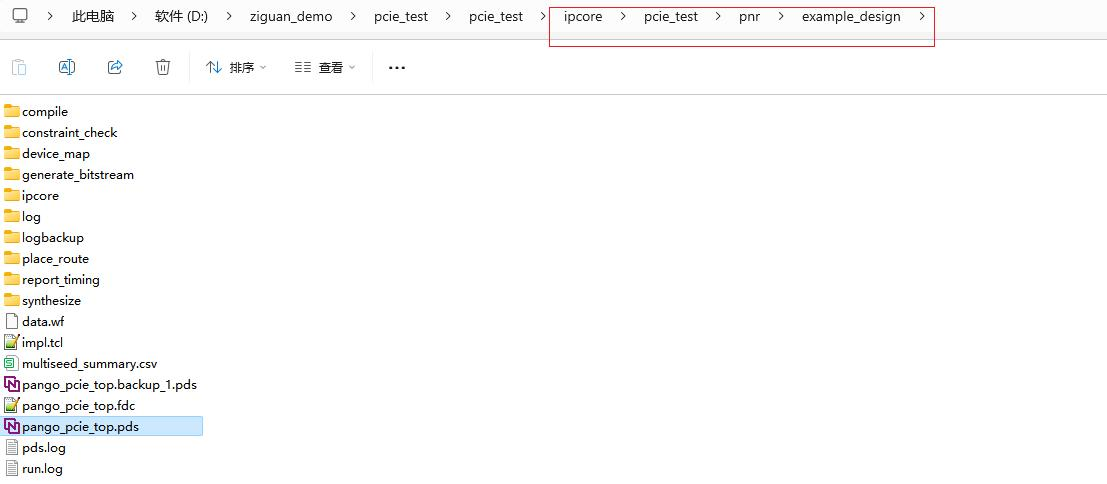

其他設置可保持默認,點擊 Generate 生成 PCIE IP。

關閉本工程,按此路徑打開 Example 工程: Xxxxx\pcie_test\ipcore\pcie_test\pnr\example_design

注意:xxxx 是自己電腦的路徑,后面的 pcie_test 及其后面的路徑是固定的。

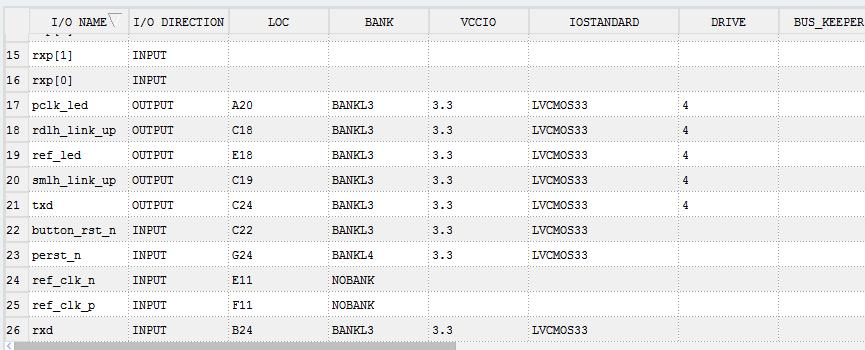

按照開發板管腳,修改相關管腳約束:

注意,像 txp[0],txp[1],rxp[0],rxp[1]等差分信號都不需要約束。其中 txd 和 rxd 是串口。

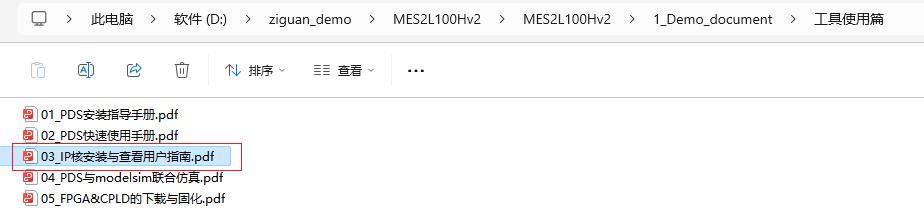

可按以下方式查看 IP 核的用戶指南,了解 Example 模塊組成;

4. 實驗現象

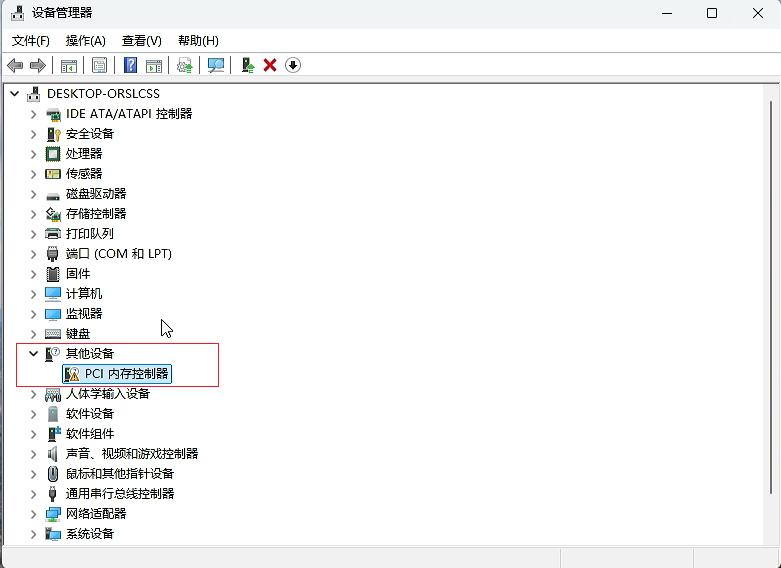

? ? ? 將程序固化到 flash 內,把開發板插入電腦 PCIE 卡槽,開機。打開設備管理器,可識別到 PCIE 設備。

Win 下能彈出該設備即可。

—Dubbo Provider處理服務調用請求源碼)

![6-Django項目實戰-[dtoken]-用戶登錄模塊](http://pic.xiahunao.cn/6-Django項目實戰-[dtoken]-用戶登錄模塊)

![視覺圖像處理中級篇 [2]—— 外觀檢查 / 傷痕模式的原理與優化設置方法](http://pic.xiahunao.cn/視覺圖像處理中級篇 [2]—— 外觀檢查 / 傷痕模式的原理與優化設置方法)

戰士:序)

】KNN算法與模型評估調優)