通過VHDL語言編寫程序用于設計電阻、電容和電感測量儀,通過使用試驗箱進行驗證是否設計正確,資料獲取到咸🐟:xy591215295250 \\\或者聯系wechat 號:comprehensivable

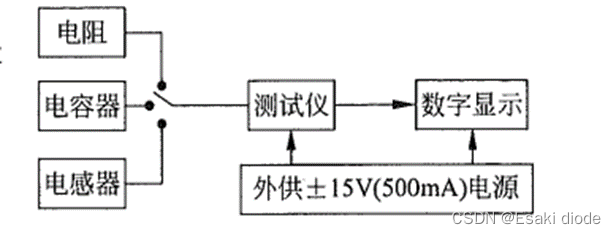

設計并制作--臺數字顯示的電阻、電容和電感參數測試儀,框圖如圖1所示。

1.基本要求

(1)測量范圍:電阻值為100~1MQ;電容值為100~ 10000pF;電感值為100μH~ 10mH。.

(2)測量精度:土5%。

(3)制作4位數碼管顯示器,顯示測量數值,并用發光二極管分別指示所測元件的類型和單位。

?

?

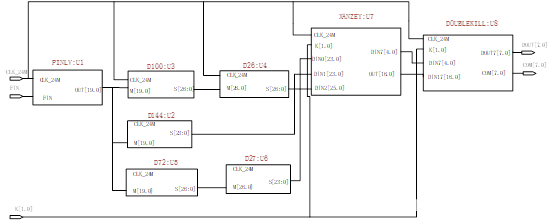

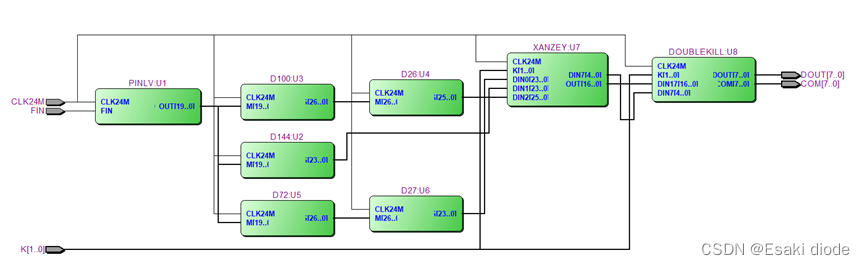

本實驗為了測試電阻、電容、電感的大小,將利用f與之關系做一個轉換,由于缺少硬件電路,于是將利用開發箱的頻率代替測量測量頻率。利用軟件設計代替硬件電路實現所需功能,本次實驗主要由三個模塊組成:測評模塊,選擇模塊,數據轉換譯碼模塊。其中每個模塊又由眾多小模塊組成,其中最主要的為頻率轉換為電阻、電容、電感的計算模塊和將五位十進制數值分離后用5位二進制數表示每位十進制數值。具體設計見圖2:

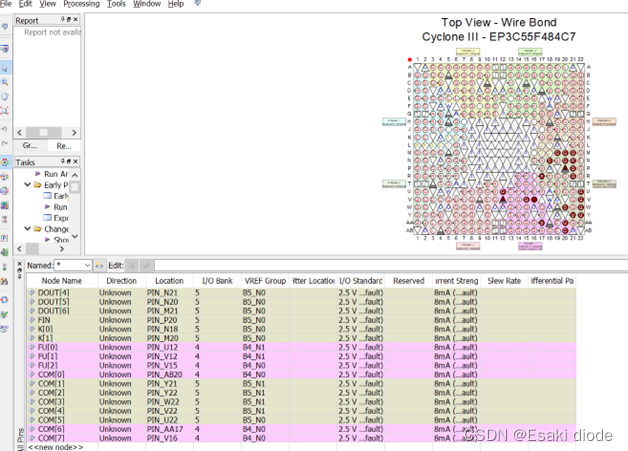

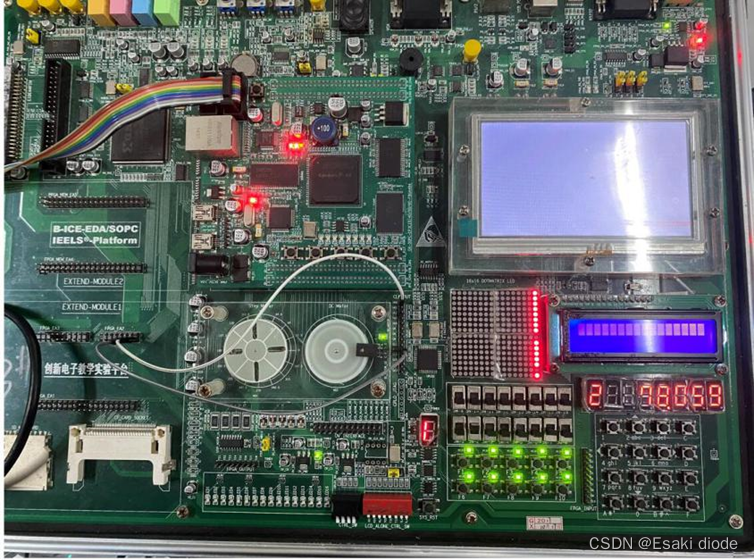

本設計完成后顯示的RTL圖: ?通過管腳鎖定后接入實驗箱進行驗證:

?通過管腳鎖定后接入實驗箱進行驗證:

??電阻顯示

電容硬件實驗現象?:

電感硬件現象顯示?:

總結:本次實驗是較難,核心為除法器的設計較為復雜,其中頻率和電阻、電容和電感存在一定的轉換關系,可以利用測得的頻率來獲得需測量的器件的參數大小,這次實驗讓我明白了除法器的應用。?

)

WIFI模塊RTL8821驅動調試)

GPS/指南針(二))

![YOLOv8數據集可視化[目標檢測實踐篇]](http://pic.xiahunao.cn/YOLOv8數據集可視化[目標檢測實踐篇])

九、視圖庫對接系列(本級)機動車數據推送)

)