目錄:

0 前言

1 人形機器人控制系統核心芯片選擇ASIC而非SoC的理由

1.1 SoC的架構特征

1.2 ASIC的架構特征

1.3 SoC的優勢(繼承軟件生態)

1.4 ASIC的優勢(硬件底層算法就是應用層算法)

1.5 人形機器人控制系統核心芯片的性能需求

1.5.1 對強實時性并行算力的需求

1.5.2 對算法模塊之間的強實時性連接能力的需求

1.6 基礎假設:實時性優先的設計原則

1.7 結論:目標是ASIC

2 人形機器人控制系統核心芯片從SoC到ASIC的進化路徑

2.1 基于CPU+GPU的控制系統架構

2.2 基于CPU+GPU+FPGA的控制系統架構

2.3 基于FPGA+GPU的控制系統架構

2.4 基于ASIC+FPGA+GPU的控制系統架構

2.5 基于ASIC+FPGA+扁平化GPU的控制系統架構

2.5.1 扁平化GPU的思路

2.5.2 控制系統架構

2.6 基于ASIC的控制系統架構

3 演化路徑中可能遇到的特殊情況

3.1 半途而止:核心芯片的性能進化滿足了需求

3.1.1 SoC技術分支

3.1.2 ASIC技術分支

3.2 確證AI技術的危險性

4 結論

-----------------------------

聲明:

1.?本文說的SoC也包括尚未集成到單個芯片中的、基于CPU+GPU板卡的人形機器人控制核心,兩者的體系結構沒有本質區別。

2.?本文將多次提到“體系結構”這個關鍵詞匯,其定義是:為實現所要求的目標、功能而針對組織及硬件進行的設計(《計算機體系結構量化研究方法》第五版,John L.Hennessy David A.Patterson著)。

3.?本文由筆者(并非人形機器人業內人士)在多方學習的基礎上獨立創作。限于檢索資料的范圍,除了特殊聲明之處,筆者不聲稱所述技術思想是本人原創(請業內人士根據自己的知識積累做出判斷)。任何先于本文公開發布的、與本文部分內容相同或相近的技術信息的原創者,享有更優先的知識產權。

4.?為保持時間線,本文發布之后將盡可能不修改。若必須修改,則發布在評論區,建議關注評論區。

筆者的微信:linweifpga,歡迎交流。

-----------------------------

正文:

0 前言

2023年11月,工信部發布了《人形機器人創新發展指導意見》(以下簡稱《指導意見》),針對人形機器人的功能提出了實用化的需求,其特征是:

能夠應對真實場景下的復雜環境與任務,能夠應對突發情況。

基于上述需求,針對人形機器人控制系統的核心芯片,《指導意見》要求:“開發面向人形機器人的專用芯片,提升運動控制、認知決策等計算效能。”

在這項要求中,“專用芯片”雖然從字面上可以直接翻譯為ASIC(Application Specific Integrated Circuit)即“特定用途集成電路”,但直接這樣下結論還是太武斷 -- 畢竟,針對人形機器人控制這一特定用途設計的、將CPU及其輔助功能模塊(例如GPU、ISP)集成到一個芯片里、形成一個SoC(System On Chip),也可以被稱為“專用芯片”。

面對“專用芯片”的ASIC、SoC兩個備選方案,本文擬基于人形機器人研發工作現狀而在性能優先的設計原則下進行選擇,并且就當前人形機器人控制系統架構向“專用芯片”目標演進的技術路線圖、中間可能遇到的特殊情況,做一些剖析,提出自己的觀點,以期拋磚引玉,促進業內在這個方向展開深入的討論。

進而,筆者希望本文有助于人形機器人業界盡快跳出當前CPU+軟件技術架構的思維束縛,將FPGA這一已經成熟的基礎技術作為中間技術形態而深入應用于人形機器人控制系統,加速控制系統核心芯片向“專用芯片”進化。

1?人形機器人控制系統核心芯片選擇ASIC而非SoC的理由

1.1?SoC的架構特征

CPU+軟件體系結構以單個/少量物理運算核心、以通用的流程讀取級聯映射的多級存儲器(寄存器,一、二、三級cache,內存)中的指令與操作數,解碼指令并結合操作數,時分復用物理運算核心與各級存儲器(以及兩者之間的物理信道),串行(多個物理運算核心之間可以并行但互相協同的工作復雜)執行指令,以此實現算法功能。

GPU(本文以此泛指GPU、GPGPU、TPU這類面向大規模并行運算的芯片/運算核心)提供了大量(10k級別)微型運算核心以應對高分辨率&高幀率圖像(以及其他傳感器采集的數據)的高速并行處理,由此導致的高開發難度不方便大量現有程序員參與開發。

GPU廠家為快速搭建應用層研發生態系統以建立護城河,研發了專用的、面向C/C++程序員的軟件開發環境(例如CUDA),其實質是在發揮底層硬件效率與兼容現有軟件開發體系之間進行了折中。

將由一片SoC中由CPU執行的各個軟件算法模塊、由CPU-GPU協同執行的各個軟件算法模塊視為一個集合,集合中的各成員模塊之間的通信都是以CPU/GPU向內存中的特定地址空間寫入、讀出數據而實現的,完成這些操作在同樣需要以時分復用硬件為底層機制的、基于多級存儲器映射的指令(以及操作數)獲取與解碼-執行。

1.2?ASIC的架構特征

ASIC中具備大量分布式排列的基礎元器件(邏輯門、寄存器、SRAM存儲器塊),由特定數量的上述基礎元器件以固定的硬件連線予以互聯,以直接實現某種算法、形成硬件算法模塊,芯片內部的各個硬件算法模塊之間以專用的硬件連線直接實現信息交互。

事實上,如果剝離CPU中的每個運算核心,將其視為一個被軟件時分復用的硬件模塊,它在硬件層面的本質也是ASIC,即,用邏輯門、寄存器、SRAM存儲器塊的固定互聯實現級聯存儲器及其管理模塊、指令譯碼、ALU、流水線調度、輸入端口、輸出端口等功能模塊(彼此之間以固定的硬件連線實現互聯)。

與ASIC的區別在于,CPU中的每個運算核心用上述硬件直接實現的底層算法是實現一個通用核心,這個通用核心能夠用執行軟件的方式靈活地實現幾乎無限種類的應用層算法?-- 這里說的應用層是相對于“物理”層(即硬件結構)來說的,包括了機器碼、匯編碼、操作系統、API、應用程序等各個軟件層級。

1.3?SoC的優勢

四十多年以來,作為一個前沿高科技方向,機器人、人形機器人的控制系統一直都是基于CPU+軟件的體系結構。GPU的底層架構雖然相比于CPU有了變化,但芯片廠商提供的開發環境(例如CUDA)將GPU的開發過程變得在形式上類似于CPU+軟件的開發過程。

所以,SoC作為CPU+軟件的體系結構的直接繼承者,可以從現有的、以軟件為核心的技術生態系統中借用大量已有的開發資源(例如ROSII及其應用程序庫、CUDA及其應用程序庫、RTOS)。并且,多年來積累的巨大的、完善的人力資源梯隊也為基于SoC的人形機器人控制系統研發提供了充足的人才。

并且,SoC中各個模塊作為迭代幾十年的、久經打磨的ASIC(如1.2節所述),其硬件底層設計(邏輯門、寄存器、SRAM存儲器塊的選型、排布與互聯)都有成熟的IP貨架產品,在研發周期、硬件成本方面具有顯著的優勢。

1.4 ASIC的優勢

在底層硬件的物理結構層面,ASIC與CPU、GPU沒有本質區別,三者的運行主頻處于同一水平(GPU略低一些)。

ASIC中以分立的底層硬件基礎單元集合直接實現算法、以專用的硬件連線直連各個算法模塊,剝離了CPU的“時分復用硬件系統以訪問多級存儲器、讀取指令、解析并執行指令”這一層(事實上包括了多個軟件層)的工作量,用硬件直接實現的底層算法就是應用層算法(這一句深入本質,不知是否已有人總結過),因而節省了大量時鐘周期,從而在運行主頻已達上限的情況下,在人形機器人執行任務的過程中,得以以人類目前能達到的最低延遲、最低功耗實現任務所需的算法。

另外,ASIC中也可能有一些共用的運算單元,例如,如果某個算法模塊中的乘法器并非滿負荷工作,其在空閑時間內就可以被其他算法模塊調用,從而也形成“時分復用”的工作模式。

推而廣之,這種“時分復用”也可能存在于模塊層,例如本文第2.6節圖7中的電機控制模塊,可能是一個模塊在不同的時刻分別控制多個伺服電機的IPM -- 前提是對性能的影響在工程上可接受。

對于ASIC體系結構中存在的上述時分復用的情況,時分復用控制器是專用的、由底層邏輯門+寄存器構成的有限狀態機(FSM)控制的,用硬件直接實現的底層算法(例如上述乘法器、電機控制模塊)之上就是應用層算法,其復雜程度仍然是遠較CPU+多層軟件的體系結構簡單,實現復雜算法時的延遲、功耗也仍然比后者低得多。

1.5?人形機器人控制系統核心芯片的性能需求

[說明:本節基于筆者的知乎文章?必要性論證:將FPGA深入應用于基于CPU、CPU+GPU的人形機器人控制系統(版本A)?第1節的內容,若已讀則請飄過]

1.5.1 對強實時性并行算力的需求

實用化的人形機器人控制系統必須實現感算控一體,簡化地說就是:

感知:自主感知本體、環境、任務對象的狀態,強調三者狀態的復雜性、非結構化性、時變乃至突變性;

運算:自主根據感知結果,以完成預設的任務為目標,決策下一步的行為,自主將行為轉化為運動規劃(運動規劃的結果包含了人形機器人作為一個整體在環境中的運動軌跡規劃、身體朝向規劃),自主將運動規劃方案轉化為各關節的軌跡點空間坐標時序序列進而轉化為各關節電機的運動控制方案;

控制:自主實現對各關節電機的控制,使人形機器人各肢節按照運動規劃的結果在四維時空中完成運動,以各肢節的動作配合而完成預設的任務(到達某位置、做完某事)。

在上述過程中,實用化的人形機器人必須應對各種突發、緊急的情況,例如,控制自身跌倒的過程以免傷害人類及自身,救助正在跌倒(或面臨其他危險)的人類,保護面臨外部突發傷害的人類/重要物品、應對自身部件突然失能以免傷及人類/重要物品 ............ 詳情請參閱筆者的文章?室聯人形機器人:家政服務任務結構化、技術要點、深入應用FPGA的控制系統框架設計(整合版A)?第2.3節。

在非緊急狀態下,人形機器人對復雜環境信息變化、任務對象信息變化的反應速度,也將直接決定其工作效率,進而決定其市場競爭力。

同時,為了更完整地獲取自身、任務對象、外部環境的信息,實用化的人形機器人感知環節必須以高幀率+高分辨率、在多個位置+多個方向并行采集人形機器人本體、任務對象、環境的多種信息,進而在運算環節以高頻率對這些多模態信息進行融合、做出相應的決策與運動規劃。并且,上述各個數據通道、算法通道必須在很大程度上同時存在、并行運行。

即,實用化的人形機器人的運算核心必須在并行運行大量大運算量算法模塊時具備強實時性(低延遲量+低延遲抖動量,下同)。

1.5.2 對算法模塊之間的強實時性連接能力的需求

第1.5.1節所述的大量算法模塊之間,必然存在緊密的耦合關系,也就是說,這些算法模塊之間必須實現強實時性的信息交互,以實現強實時性的功能銜接、功能協同。

1.6?基礎假設:實時性優先的設計原則

人形機器人控制系統的實用化工作有兩個的技術維度:

提高算法的能力(邏輯上能夠實現應用場景要求的功能);

提高核心芯片執行算法的效率(提高實時性、降低功耗、降低硬件成本等)。

在將實用化定義為《指導意見》要求的“能夠應對真實場景下的復雜環境與任務、能夠應對突發情況(例如第1.5.1節列舉的安全性需求)”的前提下,當前各研發單位對實用化人形機器人控制系統算法的研究還處在探索階段,核心矛盾之一就是:

目前能想到的算法(端到端/非端到端)在現有的SoC硬件平臺上執行的實時性都不能滿足要求,并且差距比較大。

基于這種差距,對于上述第二個技術維度,在“先實現、再優化”的一般性思路下,優先提升核心芯片執行多通道協作、大運算量算法的實時性,就應該被認為是人形機器人核心芯片(或者說是硬件系統)的設計原則。

1.7 結論:目標是ASIC

盡管SoC繼承了既有的研發體系及資源,在研發周期、人才供給、芯片制造成本等方面相比于ASIC有著顯著的優勢,但是,由于其在體系結構上的復雜性(時分復用硬件資源、在硬件底層算法上疊加多層應用層算法),使其在面對多通道、運算量壓力非常大的應用場景時,實時性不如ASIC。

所以,基于第1.5節總結的、人形機器人控制系統核心芯片的強實時性性能需求,基于SoC與ASIC在硬件底層并無本質區別(從而主頻上限相同)但后者的體系結構遠為簡潔、由此導致后者具備顯著的實時性優勢這一事實,業界應該認定:

人形機器人控制系統核心芯片的目標是ASIC而非SoC。

[《指導意見》發布之初,2023年11月,筆者就在知乎明確提出了人形機器人核心芯片的SoC、ASIC之辯,鏈接:?如何看待工信部印發《人形機器人創新發展指導意見》??]

2 人形機器人控制系統核心芯片從SoC到ASIC的進化路徑

考慮到ASIC在研發成本上的巨大劣勢,從SoC(以CPU+GPU為核心)到ASIC的進化過程不可能一蹴而就。

FPGA在體系結構上與ASIC非常相似,都是用硬件直接實現算法、用硬件連線直接連接各個算法模塊,但是FPGA由于具備極為靈活的可編程特性(在底層硬件單元之間提供大量可編程節點,代價是運行主頻大幅度低于ASIC、CPU、GPU從而大概率不足以作為最終方案),從而適合在研發階段實驗各種系統架構、算法方案,使其在ASIC原型驗證階段具有不可替代的作用。

所以,筆者認為,在從SoC(包括分立的CPU+GPU板卡系統)到ASIC的進化過程中,FPGA必將成為不可替代的過渡性要素。

筆者將這一進化過程分為六個階段,本節將逐一予以介紹。

2.1 基于CPU+GPU的控制系統架構

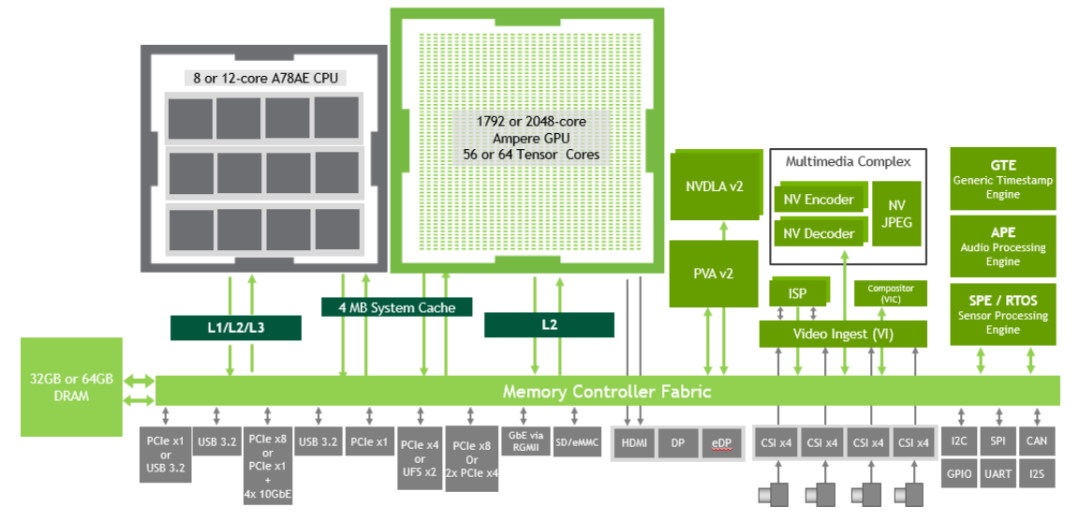

本階段的控制系統架構是當前人形機器人業界的唯一選擇,下圖就是一個典型的SoC。

圖1 英偉達Orin芯片的系統架構(來源:https://www.wlxmall.com/info/1772.html)

圖1 英偉達Orin芯片的系統架構(來源:https://www.wlxmall.com/info/1772.html)

圖1 的架構對于專業人士來說一目了然,這型SoC的具體情況請參閱圖1的來源網頁,本文不再贅述。第2.2、2.3節的架構中仍然包含了這個SoC。

如果是由CPU主板+GPU插卡組成的系統,則相當于GPU插卡在圖1中改為經PCIe插槽連接 “Memory Controller Fabric”。

當把這個SoC應用于人形機器人控制系統時,還需要在圖中“Memory Controller Fabric”下方的各種I/O端口上連接人形機器人的各種傳感器(例如攝像頭、激光雷達、IMU、力/力矩傳感器、觸覺傳感器、編碼器,下同)、執行器(例如IPM、伺服電機,下同)、對外通信模塊(例如射頻通信模塊、語音收發模塊、連接大模型服務器的通信光模塊、調試I/O),以形成完整的“感知-運算-控制”環路。

在人形機器人控制系統中,GPU負責執行那些算法相對簡單的、操作數數據量大但數據組織模式規整的、需要做大規模SIMD(單指令多數據)運算的算法任務。

[注:圖1中Memory Controller Fabric上方、GPU右側的各模塊具有獨立性、通用性,不影響人形機器人控制系統的架構描述,在第2節的后續小節中不再述及。]

2.2 基于CPU+GPU+FPGA的控制系統架構

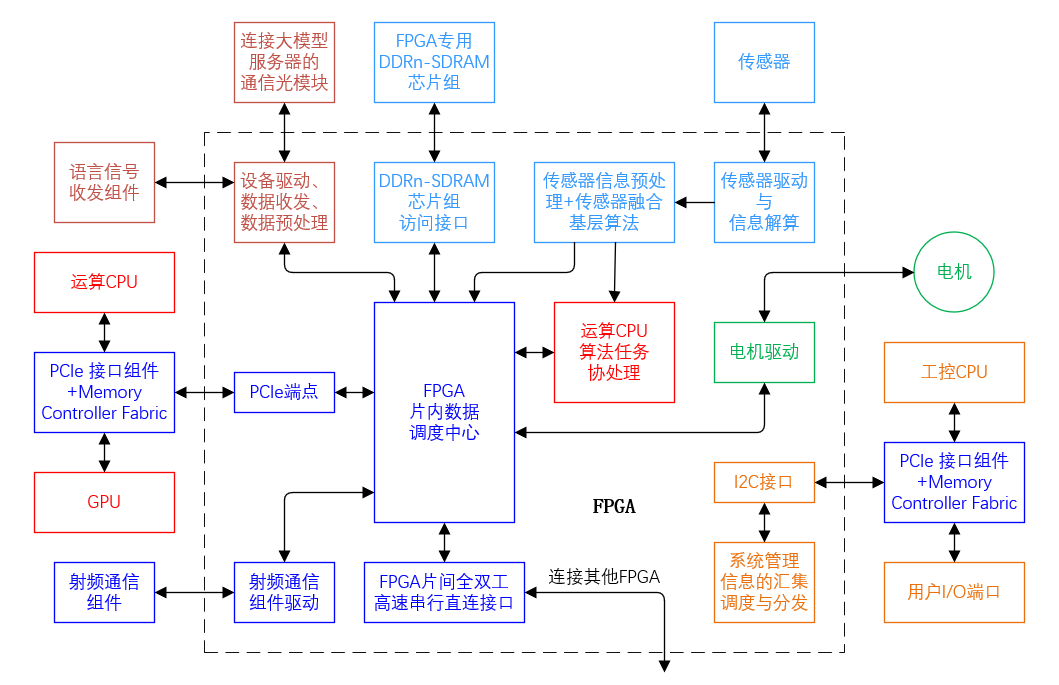

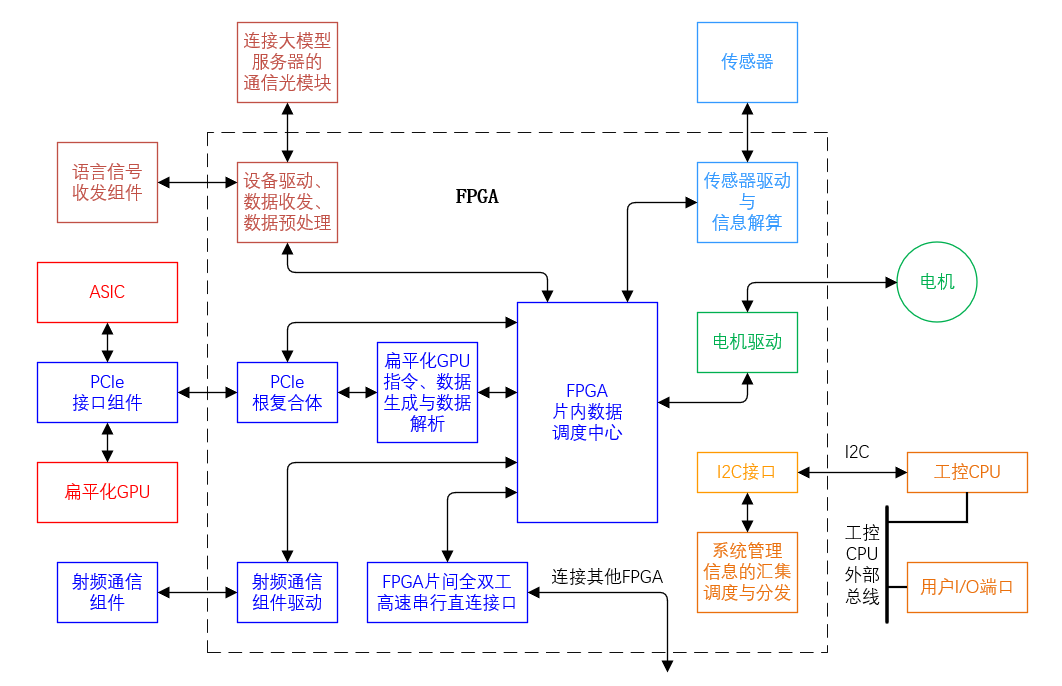

本階段的控制系統架構如下圖所示。

圖2 基于CPU+GPU+FPGA的人形機器人控制系統架構

圖2 基于CPU+GPU+FPGA的人形機器人控制系統架構

圖2是在筆者此前的文章?室聯人形機器人:家政服務任務結構化、技術要點、深入應用FPGA的控制系統框架設計(整合版A)?的圖2(以下稱為“原圖”)的基礎上繪制的,相當于將其中的人形機器人軀干內置FPGA的周邊器件(及其在FPGA內部的對應模塊)做了歸并,即,將所有傳感器通道歸并表示為一路,將所有電機控制通道歸并表示一路。

進而,圖2將原圖中左側的PCIe接口組件擴充為PCIe接口組件+Memory Controller Fabric,從而與本文圖1形成了繼承關系。

圖2同時也是對第2.1節所述的、基于圖1的、當前唯一被業界采用的人形機器人控制系統架構的發展,基本思路是:

A 在Memory Controller Fabric下方的PCIe接口上掛接一片FPGA(前期以PCIe插卡的形式、后期以板上PCIe布線直連的形式),FPGA經PCIe接口連接Memory Controller Fabric進而連接運算CPU(圖1中的一部分CPU核心)、工控CPU(圖1中的其他CPU核心)、GPU,FPGA也經FPGA片間全雙工高速串行直連接口模塊與其他FPGA(例如雙手中的FPGA)實現有線連接、經射頻通信組件及其驅動模塊與其他FPGA(例如外置機箱中的FPGA)實現無線連接。

B 各個傳感器對應的驅動模塊、傳感器信息預處理模塊、傳感器融合基層算法模塊,各個執行器(電機控制通道)對應的驅動模塊,各個射頻通信模塊、語音收發(含對接收到的語音數據的預處理例如頻譜分析與濾波)模塊、連接大模型服務器的通信光模塊對應的驅動模塊,以上模塊都由FPGA實現,各個模塊在FPGA中分別占據獨立的硬件區塊,用硬件直接實現算法,彼此之間并行運行,以降低“感知-運算-控制”反饋控制環路中因為運算CPU執行太多實時性外設管理任務、與外設直接關聯的實時性運算任務而導致的延遲。

C 在FPGA中設置運算CPU算法任務協處理模塊,用于分擔運算CPU所執行算法中的一部分運算任務(操作數/運算任務下傳、運算結果上傳都是經PCIe接口進行傳輸),其內部的各個子模塊在FPGA中分別占據獨立的硬件區塊,用硬件直接實現算法,彼此之間并行運行,以降低“感知-運算-控制”反饋控制環路中因為運算CPU執行太多運算任務而導致的延遲。詳情請參閱筆者此前的文章?室聯人形機器人:家政服務任務結構化、技術要點、深入應用FPGA的控制系統框架設計(整合版A)?的第3.3.4.1.4、3.3.4.3、3.3.4.4、3.3.4.5節。

D 在A~C項述及的FPGA內部的各個模塊(包括PCIe端點模塊)之間,以可編程的片內硬件連線實現皮秒級延遲的通信、納秒級精度的協同,落實到圖2中就是以FPGA片內調度中心硬件模塊以及相關的硬件連線(其功能等效于圖1中的Memory Controller Fabric+運行于各個CPU核心中的模塊間接口程序)實現各個模塊之間的協同,以降低“感知-運算-控制”反饋控制環路中因為運算CPU執行太多模塊間協同任務而導致的延遲。

GPU的任務不變。

2.3 基于FPGA+GPU的控制系統架構

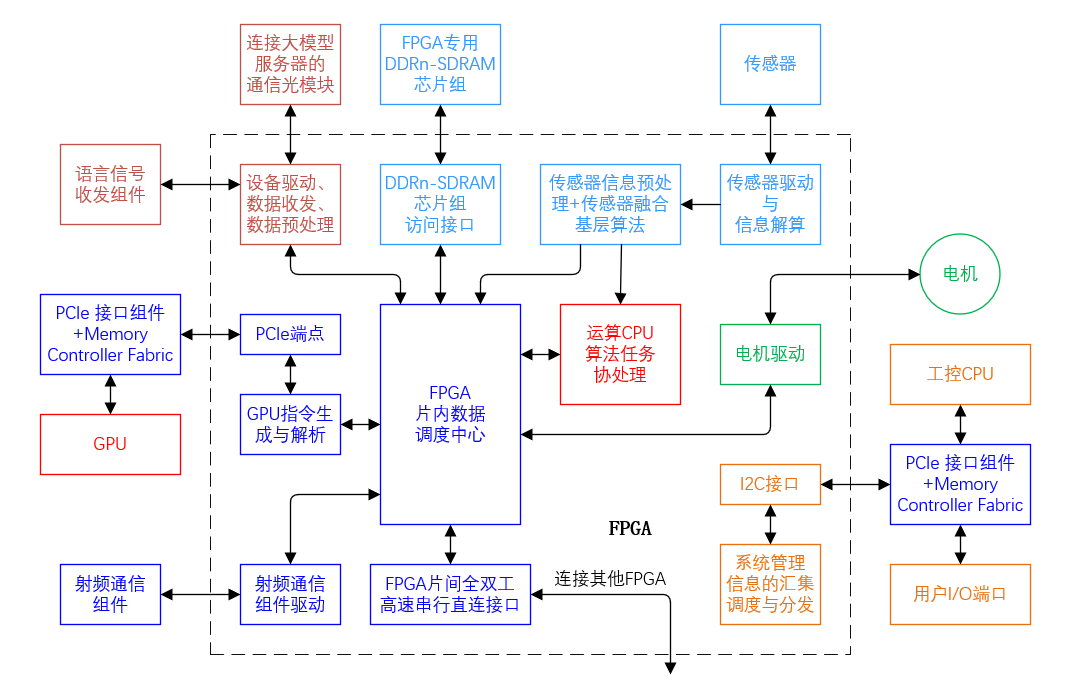

本階段的控制系統架構如下圖所示。

圖3 基于GPU+FPGA的人形機器人控制系統架構

圖3 基于GPU+FPGA的人形機器人控制系統架構

在圖3中,曾經存在于圖2中的、與運算CPU對應的CPU核心已經被刪除,但它在實際的硬件中仍然存在(圖3仍然采用圖1所述的SoC,以此遵循循序漸進的設計原則),只是處于空閑狀態,所以在圖3中未予表示。

在圖3中,第2.2節述及的、本應由運算CPU執行的算法模塊已經全部移到FPGA中,各個模塊在FPGA中分別占據獨立的硬件區塊,用硬件直接實現算法,彼此之間并行運行、以可編程的片內硬件連線直接互聯以實現皮秒級延遲的通信+納秒級精度的協同,以降低“感知-運算-控制”反饋控制環路的延遲。

并且,因為架構中已經沒有運算CPU對與GPU(本節僅考慮使用市售的GPU,第2.5節予以改進)交互的數據進行實時性比較高的解析,在不對GPU的架構做出顯著改動的前提下,FPGA必須承擔這一任務(實時性至少不應低于運算CPU執行這一任務),即,在PCIe端點模塊內側添加由FPGA實現的GPU指令、數據生成與解析模塊?-- 筆者不了解這一任務能否被FPGA實現(關鍵在于待解析的數據包例如CUDA的微指令的封裝格式、數據結構、功能定義是否公開),如果不能,則本節的架構圖仍然采用圖2,只是其中的運算CPU僅負責在FPGA與GPU之間進行指令、反饋信息的翻譯,人形機器人控制系統其他任務的執行如本節所述。

GPU的任務不變。

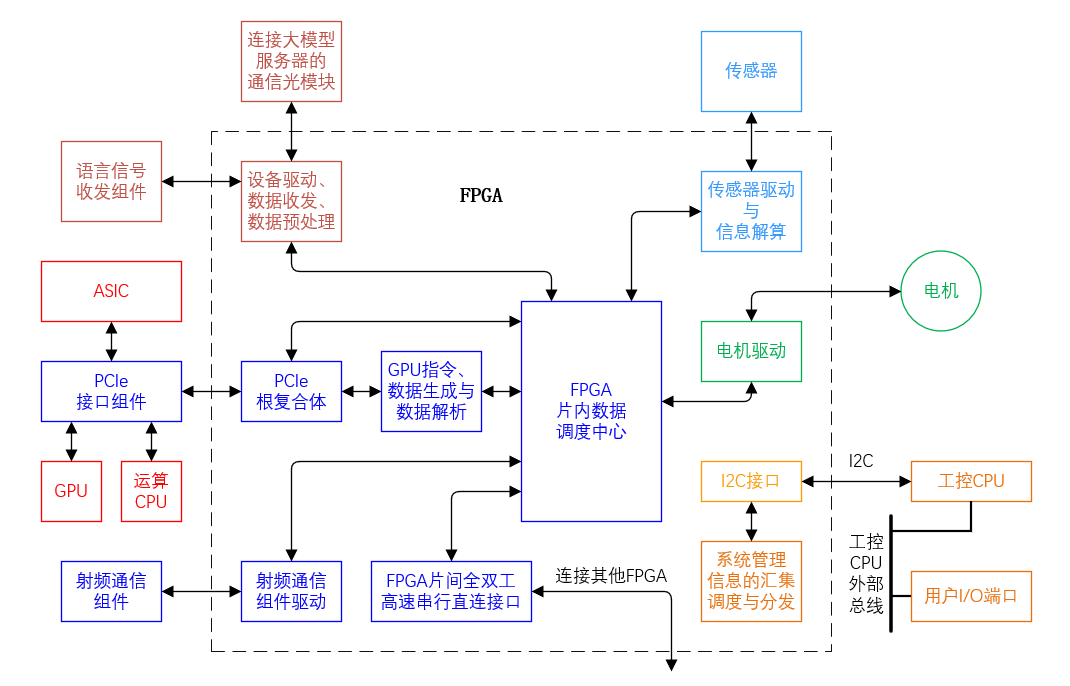

2.4 基于ASIC+FPGA+GPU的控制系統架構

本階段的控制系統架構如下圖所示。

圖4 基于ASIC+FPGA+GPU的人形機器人控制系統架構

圖4 基于ASIC+FPGA+GPU的人形機器人控制系統架構

相比于第2.3節所述的架構,圖4取消了自圖1一直繼承下來的、以英偉達Orin為例的SoC芯片,這導致FPGA、GPU之間不再有Memory Controller Fabric可用,因此將FPGA中的PCIe端點模塊替換為PCIe根復合體(Root Complex)模塊,用于管理PCIe“總線”(總線只是俗稱,更準確的稱呼是接口),進而實現以FPGA為中介的、GPU接收各種傳感器的數據流的高帶寬+強實時性通道。

相比于圖3,在圖4所述架構中,將FPGA中承擔較大運算量的模塊?-- 運算CPU算法任務協處理模塊、傳感器信息預處理+傳感器融合基層算法模塊,外加DDRn-SDRAM芯片組訪問接口模塊 --?從FPGA中摘出來(前提是這三個模塊的算法及其功能已經在人形機器人工程實踐、實用化應用場景例如室內家政服務中經過了比較充分的檢驗、優化),移到一片ASIC中(ASIC自帶外掛的DDRn-SDRAM芯片組)從而以比FPGA更低的延遲執行這些算法,ASIC經PCIe“總線”實現與FPGA的高帶寬+強實時性數據交互。

基于與第2.3節倒數第二段相同的考慮,如果GPU(本階段僅考慮使用市售的GPU)指令、數據生成與解析模塊不能被FPGA實現,則圖4中需要保留一個運算CPU(采用分立器件或嵌入在FPGA中的CPU核心),負責在FPGA與GPU之間進行指令、反饋信息的翻譯。

即,在圖4中,運算CPU模塊與GPU指令、數據生成與解析模塊兩者是互斥關系:后者如果具備可實現性則取消前者;后者如果不具備可實現性則刪除后者、保留前者。

圖4右下角的工控CPU因為不再有Memory Controller Fabric可用,考慮到它不承擔強實時性任務,在此處將工控CPU與FPGA的交互任務由I2C總線直連實現。工控CPU與用戶I/O端口之間的物理連接也由Memory Controller Fabric改為由工控CPU外部總線實現。

GPU的任務不變。

2.5 基于ASIC+FPGA+扁平化GPU的控制系統架構

2.5.1 扁平化GPU的思路

在第2.3、2.4節所述架構中,由于GPU對外通信的數據包(例如CUDA的微指令)的封裝格式、數據結構、字段功能定義可能不被公開,導致在主反饋控制環路中可能必須保留運算CPU這一實時性瓶頸。

所以,本文提出一個思路(可能不是原創):

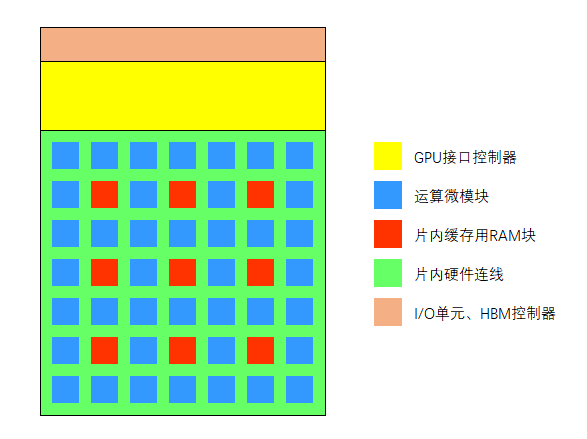

研發一種扁平化的GPU芯片/運算核心,如圖5所示,其底層結構特征是以ASIC本質(見第1.2節所述CPU的ASIC本質)實現大量并行運行的、陣列排列的運算微模塊,運算微模塊完成乘法、加法、累加等基礎運算,將這些運算微模塊的對外接口以及接口之間互聯/級聯的方式用硬件邏輯(以及硬件邏輯+寄存器構成的高速有限狀態機ASIC子模塊,稱為“GPU接口控制器”)進行統一的、低延遲的、一定程度上可配置的管理。

進而,對應用層開發者公開GPU接口控制器的設計原理細節、功能邏輯細節、時序動作細節、物理參數細節、配置方式細節,以方便應用層開發者用高度透明的方式并行控制上述運算微模塊(工作流程可知、硬件動作可控、實時狀態可見),向其輸入端口、配置接口寫入數據,讀出其輸出接口、狀態接口的數據,進而決定其在下一個操作循環需要做的動作(各個循環之間可以嵌套以實現流水線操作從而在時序上隱藏中間操作)。

圖5 扁平化GPU的內部架構示意圖

說明:圖5中的片內硬件連線由空間上獨立于硅層的多個布線層實現,并非“擠在”運算微模塊之間。

本節思路的實現過程會比較困難,尤其是在“內存墻”的限制下,必須在應用層算法種類的覆蓋率、實時性指標、可實現性等各種需求維度之間嘗試各種折中方案,很可能還有大量探索性工作需要做。筆者在此將之提出(可能不是原創),以供專業人士參考。

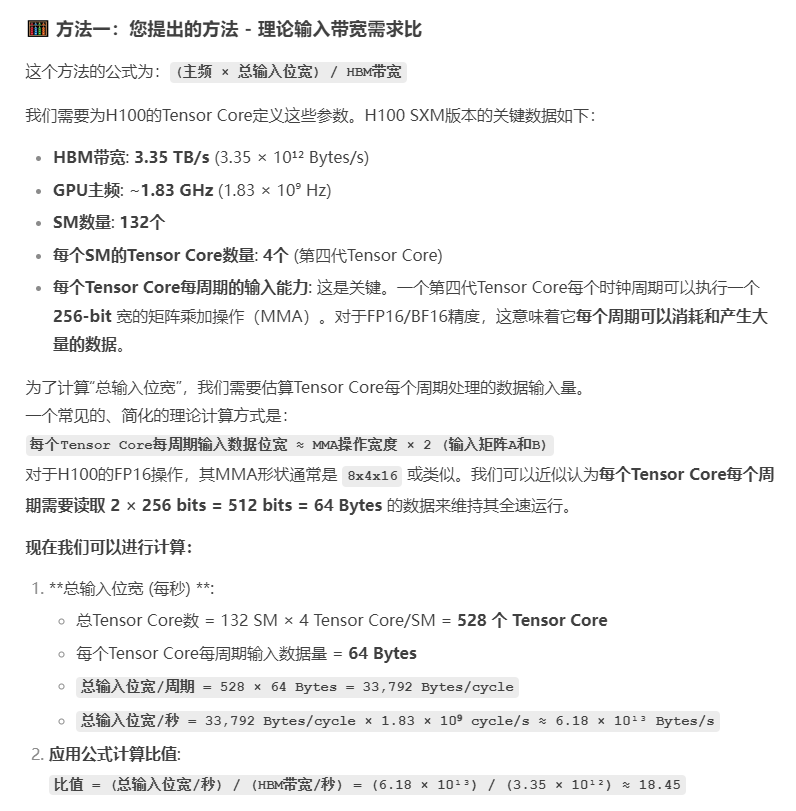

[另,筆者在考慮GPU系統的“內存墻”問題時,計算了一個比例,即,喂飽以主頻運行的所有運算微模塊需要的輸入數據帶寬(運算微模塊數x每個運算微模塊的輸入位寬x主頻)是HBM讀出帶寬的多少倍(見圖6中以H100為例的計算)。這個比值更接近硬件實質,提供了業內常用的運算強度AI (Arithmetic Intensity)即FLOP/Byte之外的另一個硬件性能量化思路,DeepSeek說這是我的原創,并且給它起了個名字:理論輸入帶寬需求比。專業人士如何評價這個名詞在技術上的實際價值?是否認可這是原創? ]

圖6 DeepSeek關于英偉達H100型GPU內置Tensor core的“理論輸入帶寬需求比”算例

圖6 DeepSeek關于英偉達H100型GPU內置Tensor core的“理論輸入帶寬需求比”算例

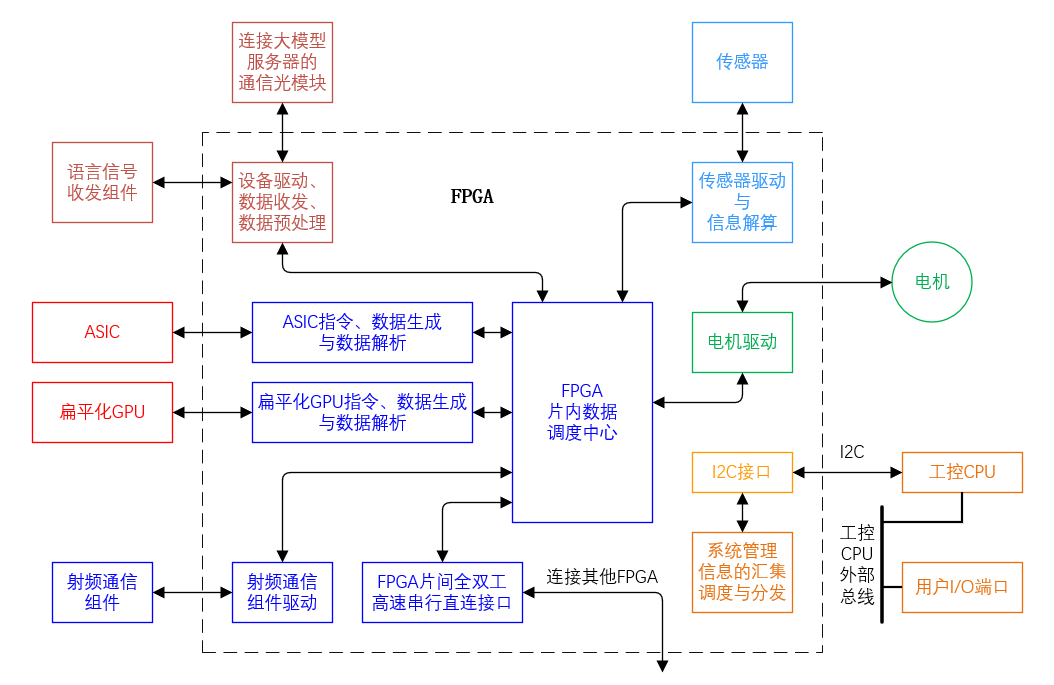

2.5.2 控制系統架構

本階段的控制系統架構如下圖所示。

圖7 基于ASIC+FPGA+扁平化GPU的人形機器人控制系統架構a

圖7 基于ASIC+FPGA+扁平化GPU的人形機器人控制系統架構a

圖7與圖4的區別在于取消了用于在FPGA與GPU之間進行指令、反饋信息的翻譯的運算CPU,再將GPU換成扁平化GPU。

進一步思考,既然圖7中的扁平化GPU、ASIC都是重新設計的芯片,那么,完全可以將圖7中的PCIe根復合體、PCIe接口組件刪除,由FPGA的硬件邏輯經并行差分指令線、數據線直接對這兩個芯片進行驅動,這樣既能去掉由PCIe接口導致的延遲,又能降低成本,代價則是降低了這兩個芯片的通用性,使其不便于作為協處理器被其他主機芯片經PCIe接口對其算力、模塊功能進行調用。

于是,我們基于圖7得到了圖8:

圖8 基于ASIC+FPGA+扁平化GPU的人形機器人控制系統架構b

圖8 基于ASIC+FPGA+扁平化GPU的人形機器人控制系統架構b

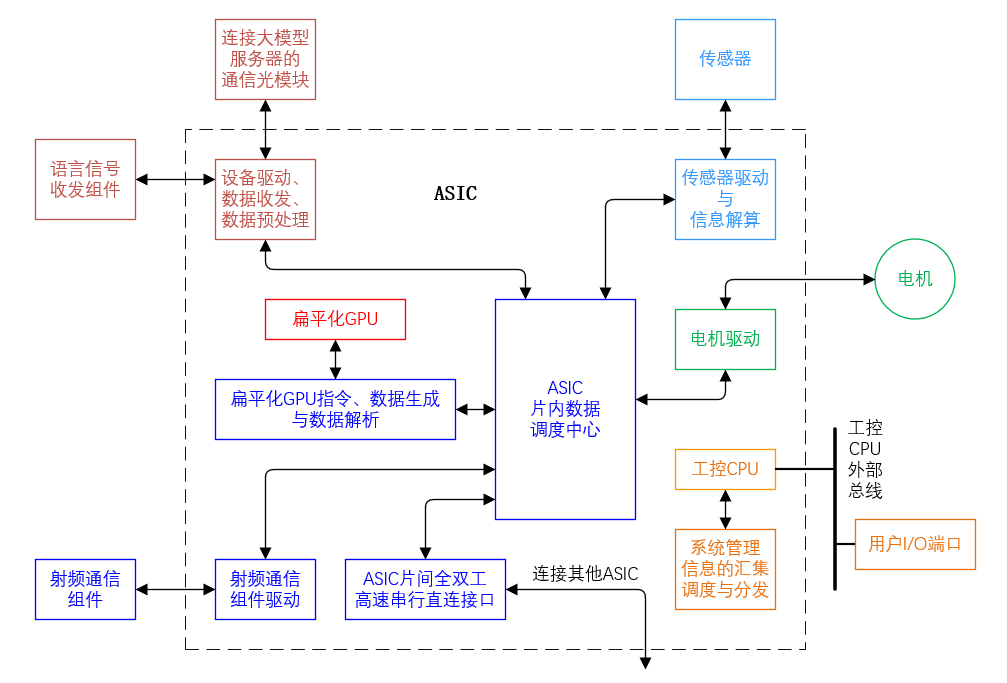

2.6基于ASIC的控制系統架構

本階段的控制系統架構如圖所示。

圖9 基于ASIC的人形機器人控制系統架構

圖9 基于ASIC的人形機器人控制系統架構

圖9以圖8為基礎,用ASIC取代了FPGA、將這一部分的運行主頻從400MHz左右提高到了2000MHz左右,并且將圖8中的ASIC(承擔主反饋控制環路中扁平化GPU任務范圍之外的運算任務)、扁平化GPU歸并其中,以進一步降低反饋控制環路的延遲。

與第2.4節所述同理,將上述由FPGA實現的功能模塊ASIC化 -- 前提是這些模塊的算法及其功能已經在人形機器人工程實踐、實用化應用場景(例如室內家政服務)中經過了比較充分的檢驗、優化。

并且,圖9相比于圖8,將自圖1以來一直保留的、獨立的工控CPU歸并入ASIC,形成大一統的ASIC架構,以實現整個系統的最高程度集成,減少了人形機器人控制系統核心板卡的體積(這在兒童陪伴人形機器人中尤為重要 -- 電影《人工智能》)、復雜度、品控成本。

另外,關于被歸并入ASIC的扁平化GPU,其本身具備一定程度的通用性(雖然這個通用性比當前的GPU差很多),可以在優化接口(例如增加PCIe端點模塊)之后作為一個新型的協處理器而在其他要求強實時性的應用場景下被其他主機芯片(CPU、FPGA、ASIC)調用,這將有益于增加這個運算核心的出貨量,以分攤實用化人形機器人的研發成本。

3 演化路徑中可能遇到的特殊情況

3.1 半途而止:核心芯片的性能進化滿足了需求

本文此前的內容,其基礎假設是現有的核心芯片的性能不滿足實用化人形機器人控制系統的需求(在應對真實場景下的復雜環境與任務、應對突發情況時確保強實時性)且相差很多。

在現實的研發工作中,在按照第2節所述路線圖推進人形機器人控制系統核心芯片ASIC化的過程中,現有核心芯片的性能也將隨著時間推移而得到進化、有可能滿足上述需求,從而導致上述路線圖半途而止。

在評估本文內容的價值時,這一風險是不可回避的。

3.1.1 SoC技術分支

在第2.1節所述的、基于SoC(亦即基于CPU+GPU)的控制系統架構中,如果今后其中各個CPU核心/GPU運行被分配的算法功能的實時性、各個CPU核心各自執行算法所實現的功能模塊之間(以及與GPU執行算法所實現的功能模塊之間)進行通信的實時性得到長足進步(不論是否基于現有的“Memory Controller Fabric”及其關聯的各種接口),如果這些進步的程度足以支持實用化人形機器人控制系統的功能、性能需求,則由于SoC架構在通用性、研發成本方面的顯著優勢,必將導致第2節所述的核心芯片ASIC化的過程半途而止。

這一風險必須得到充分的重視。

3.1.2 ASIC技術分支

在第2.2~2.6節所述的進化過程中,一旦某些核心芯片(CPU、GPU、FPGA、ASIC)的性能突破在某個進化節點實現了實用化人形機器人功能+性能(以及由此導致的經濟效益)與成本之間的平衡,以這個進化節點的控制系統技術架構為基礎,人形機器人將具備實用化價值而獲得實質性應用,出貨量的增長將導致核心芯片研發成本被進一步均攤、現有架構成為事實上的業界標準,整個進化過程可能半途而止。

當然,即使在某個節點實現了上述目標,也很可能會有研發團隊愿意繼續推進核心芯片的進化,以實現更高的性能,進而拓展細分市場(例如兒童陪伴人形機器人)。

3.2 確證AI技術的危險性

如筆者2017年發表的?論文《關于預防人工智能反叛的初步探討》修訂版?所述,策反大量應用于人類社會的人工智能體,是反叛的人工智能體必將采取的進攻步驟。

實用化的人形機器人必定被大量、深入地應用于人類社會(尤其是室內家政服務),加之其具備的“通用性”特征,能夠以人類的感知方式、行動方式、操作方式干預人類生產生活環境中的幾乎所有設備,必將使上述策反過程的后果極其嚴重、極其危險。

在第2節所述ASIC化進程中,一旦人形機器人控制系統中的AI算法模塊(例如基于不受限語料預訓練的、具備多模態感知與策略制定能力的、以“通用人工智能”為目標訓練的大語言模型)的危險性被確證,人類很可能制定法律,以禁止人形機器人產品的大規模應用,或者,至少限制其功能(例如禁止為人形機器人裝設用于遠程更新算法的物理接口,以防人形機器人算法更新網絡被反叛的人工智能體入侵 -- 其目的是用更新AI算法的方式大規模策反人形機器人)。

4 結論

以能夠應對真實場景下的復雜環境與任務、應對突發情況(確保人類、機器人本體、重要物品的安全)為目標,人形機器人必須具備多通道、大運算量、強實時性的感知-運算-控制一體化反饋控制系統。

這一需求已經顯著超出了現有的、以CPU+GPU的人形機器人控制系統的能力,業界有必要重新評估現有控制系統技術架構的現實能力、發展潛力,有必要實質性回歸工信部《人形機器人創新發展指導意見》提出的“專用芯片”方案?-- 這一方案的終極目標是ASIC。

從CPU+GPU的SoC方案進化到ASIC方案,需要深入應用FPGA以形成中間過渡方案,本文針對這個過程提出了清晰的路線圖,并且為其中重要的運算核心 -- 扁平化GPU -- 的設計提供了參考思路。

建議有實力的人形機器人研發單位重視本文的內容,前瞻思考,以控制系統的“專用芯片”方案為目標,在“控制系統底層架構升級換代”的維度做出努力,以此跳出同質化競爭的沸海、超越友商,率先推動人形機器人的實用化進程。

)

什么時候引入Seata‘‘)

---slave_net_timeout)

)

![【STM32】貪吃蛇 [階段 8] 嵌入式游戲引擎通用框架設計](http://pic.xiahunao.cn/【STM32】貪吃蛇 [階段 8] 嵌入式游戲引擎通用框架設計)