加法器是數字電路中用于執行加法運算的基本邏輯單元,廣泛應用于計算機、計算器、數字信號處理器等電子設備中。它能將兩個二進制數相加,并輸出結果及可能產生的進位。

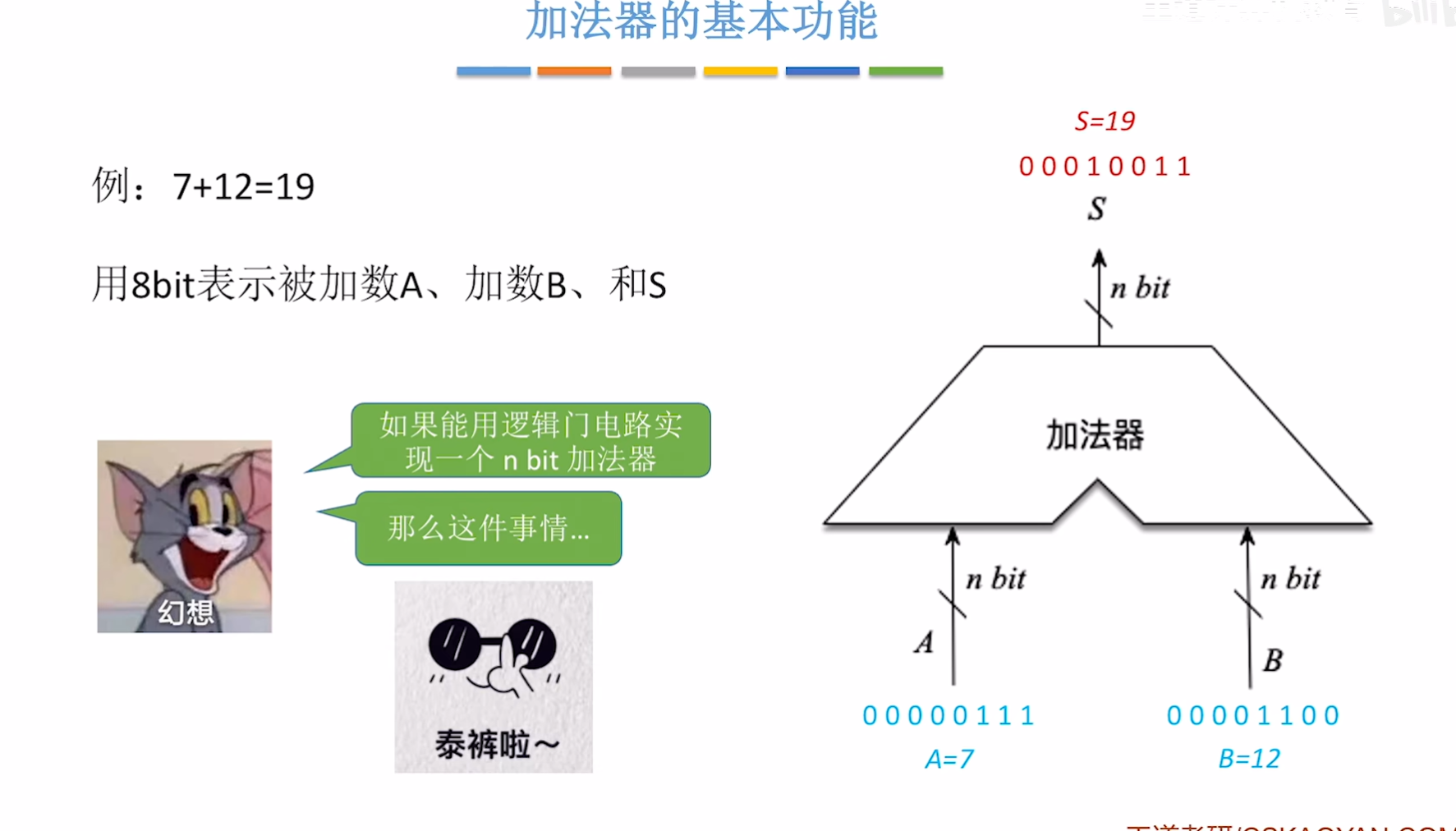

一、加法器的基本功能

加法器的基本功能是在數字電路中對輸入的二進制數執行加法運算,具體可從以下幾個核心層面理解:

- 核心運算:對兩個二進制數字(通常是 0 或 1)進行相加,輸出運算結果。這一過程遵循二進制加法規則:0+0=0、0+1=1、1+0=1、1+1=0(同時產生進位 1)。

- 處理進位:根據設計不同,可處理運算中產生的進位信息:

- 半加器:僅對兩個 1 位二進制數相加,輸出本位和與向高位的進位,但不考慮來自低位的進位。

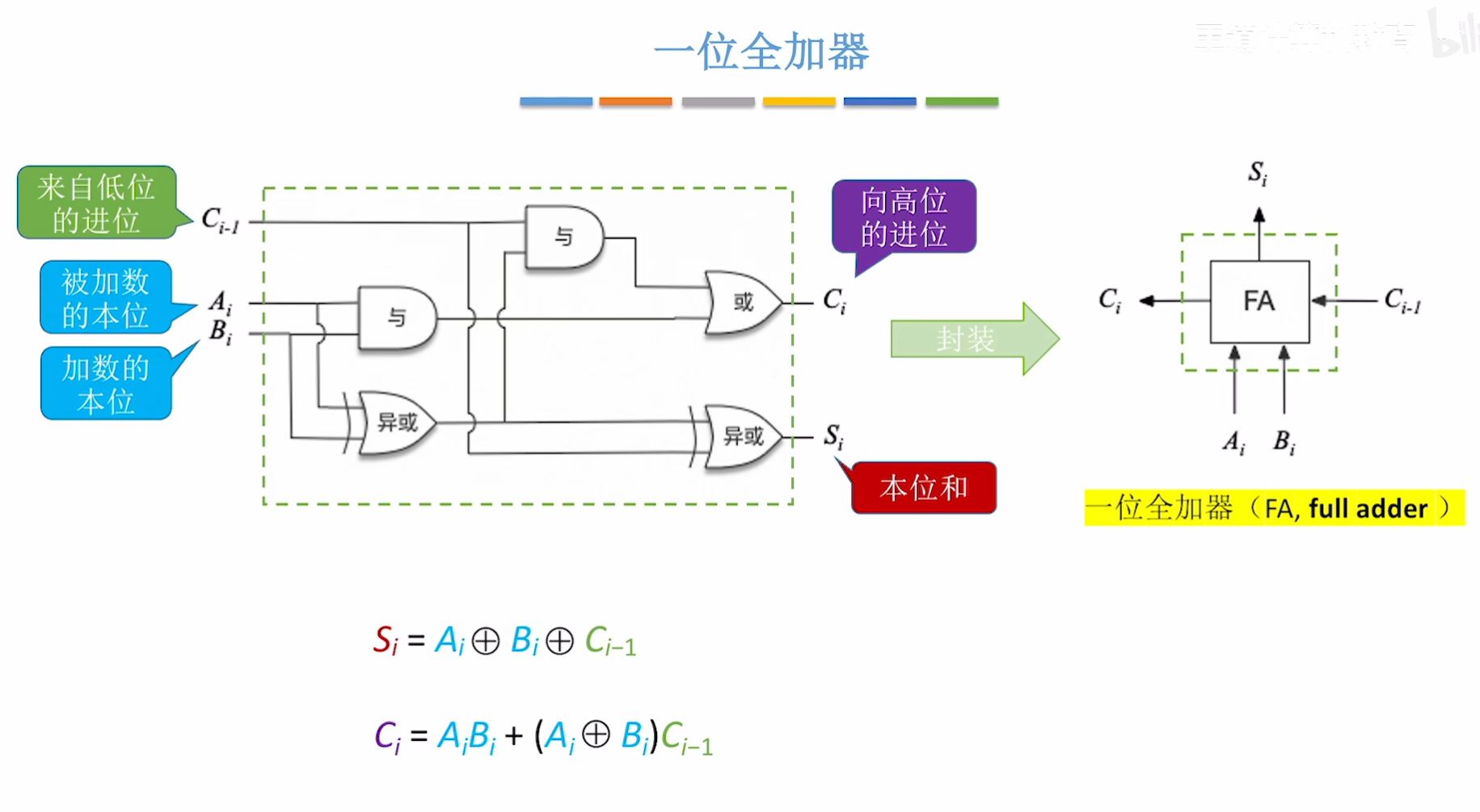

- 全加器:在兩個 1 位二進制數相加的基礎上,額外接收來自低位的進位輸入,最終輸出本位和與向高位的進位輸出,完整處理三級輸入(兩個加數 + 低位進位)的加法邏輯。

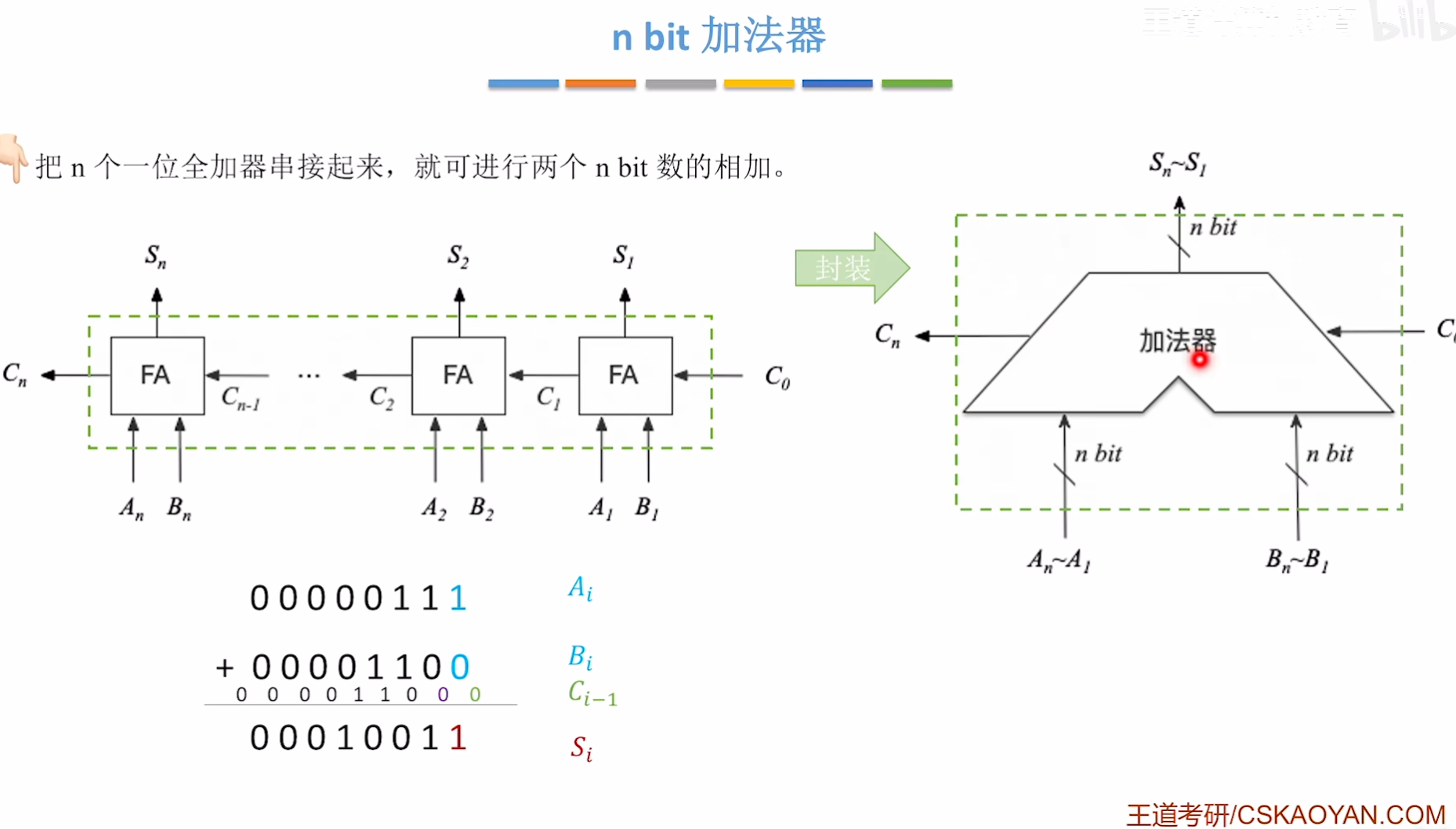

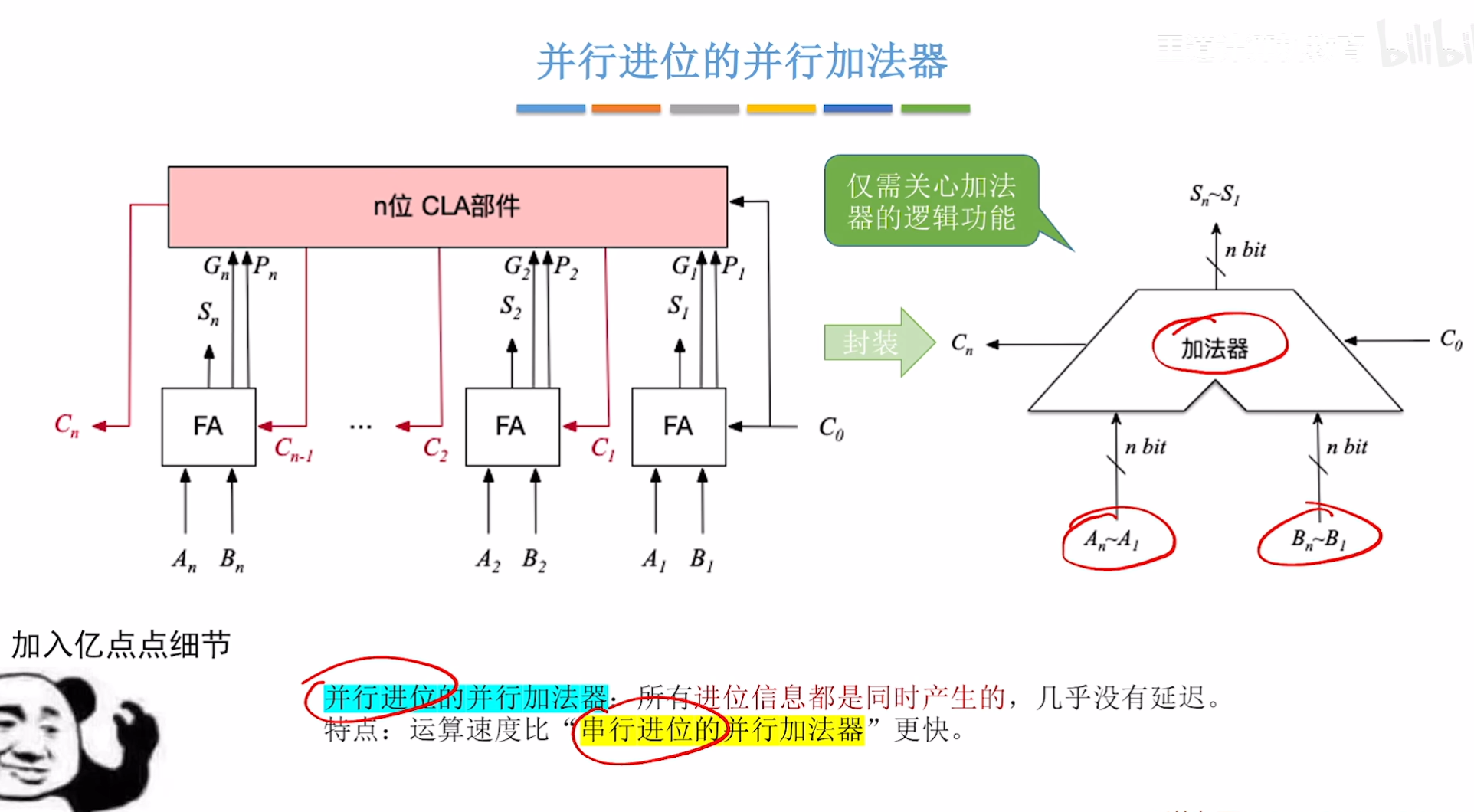

- 擴展運算:通過多個加法器級聯(如串行進位加法器、超前進位加法器),可實現多位二進制數的加法,滿足對更大數值(如 8 位、16 位、32 位等)的運算需求,為計算機、計算器等設備的算術功能提供基礎支持。

?

?

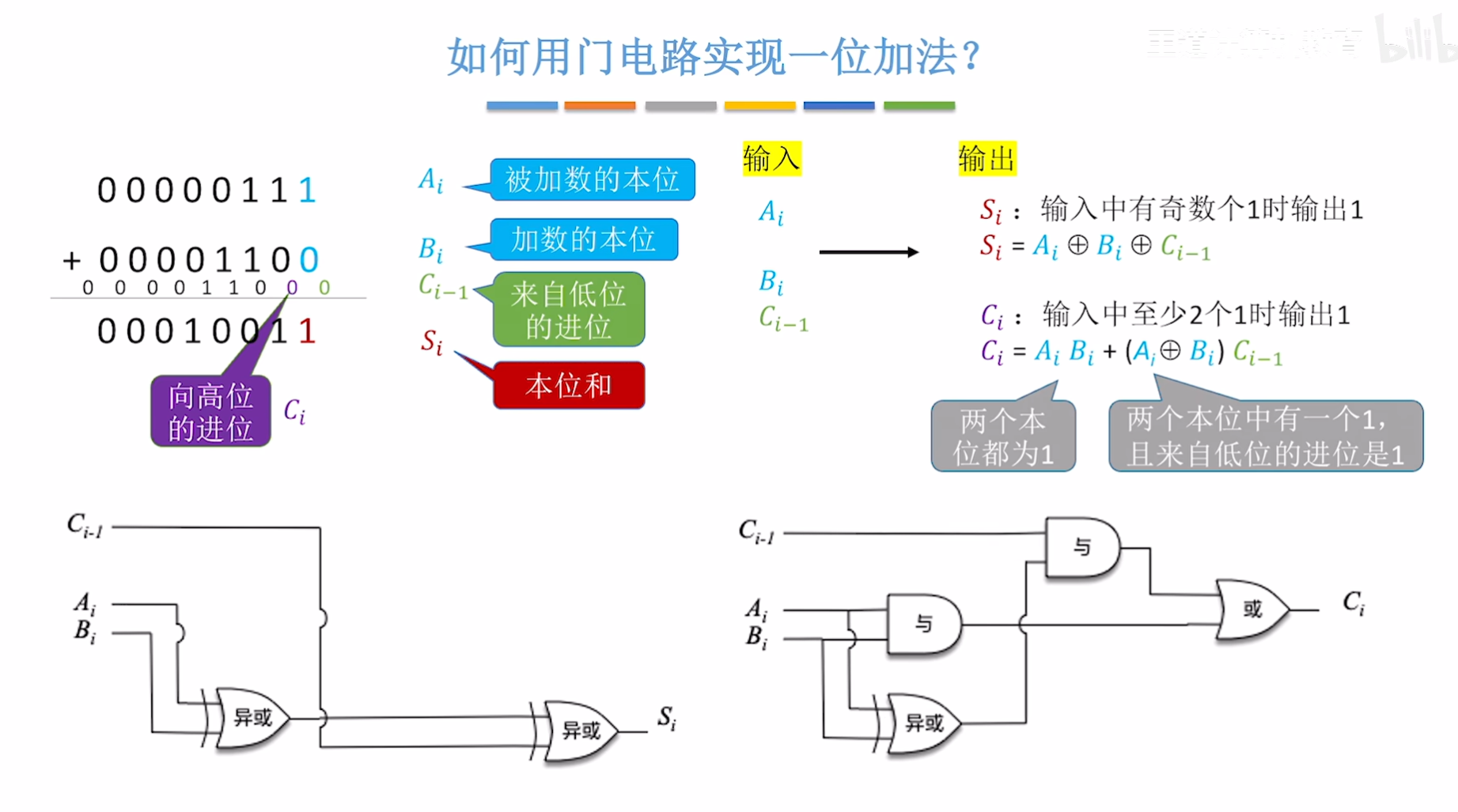

二、如何用門電路實現一位加法?

大家如果還有不理解的可以去看B站看王道考研去琢磨一下,第一次的時候可能難以理解,多琢磨琢磨,可以思考下為什么會有與 或 異或 同或這四種邏輯運算?然后在根據他們的運算法則理解電路

?

功能:對兩個 1 位二進制數(A、B)和來自低位的進位(C_in)進行加法,輸出本位和(Sum)與向高位的進位(C_out)。

邏輯分析:

- 求和(Sum):三個輸入(A、B、C_in)中 “1” 的個數為奇數時結果為 1(可通過兩次異或實現)。

- 進位(C_out):三個輸入中至少兩個為 1 時產生進位 1(可通過與門和或門組合實現)。

門電路實現:

求和:

Sum = (A ⊕ B) ⊕ C_in

(先用異或門處理 A 和 B,再將結果與 C_in 通過異或門)進位:

C_out = (A · B) + (A · C_in) + (B · C_in)

(三個與門分別處理 A&B、A&C_in、B&C_in,再通過或門合并結果)

三、 一位全加器

?

四、n bit 全加器

?

?

不足之處: 串行的計算速度取決于進位和傳遞的速度,所以根據技術的發展,這種肯定是不可以用的,我們需要一個并行的加法器

?

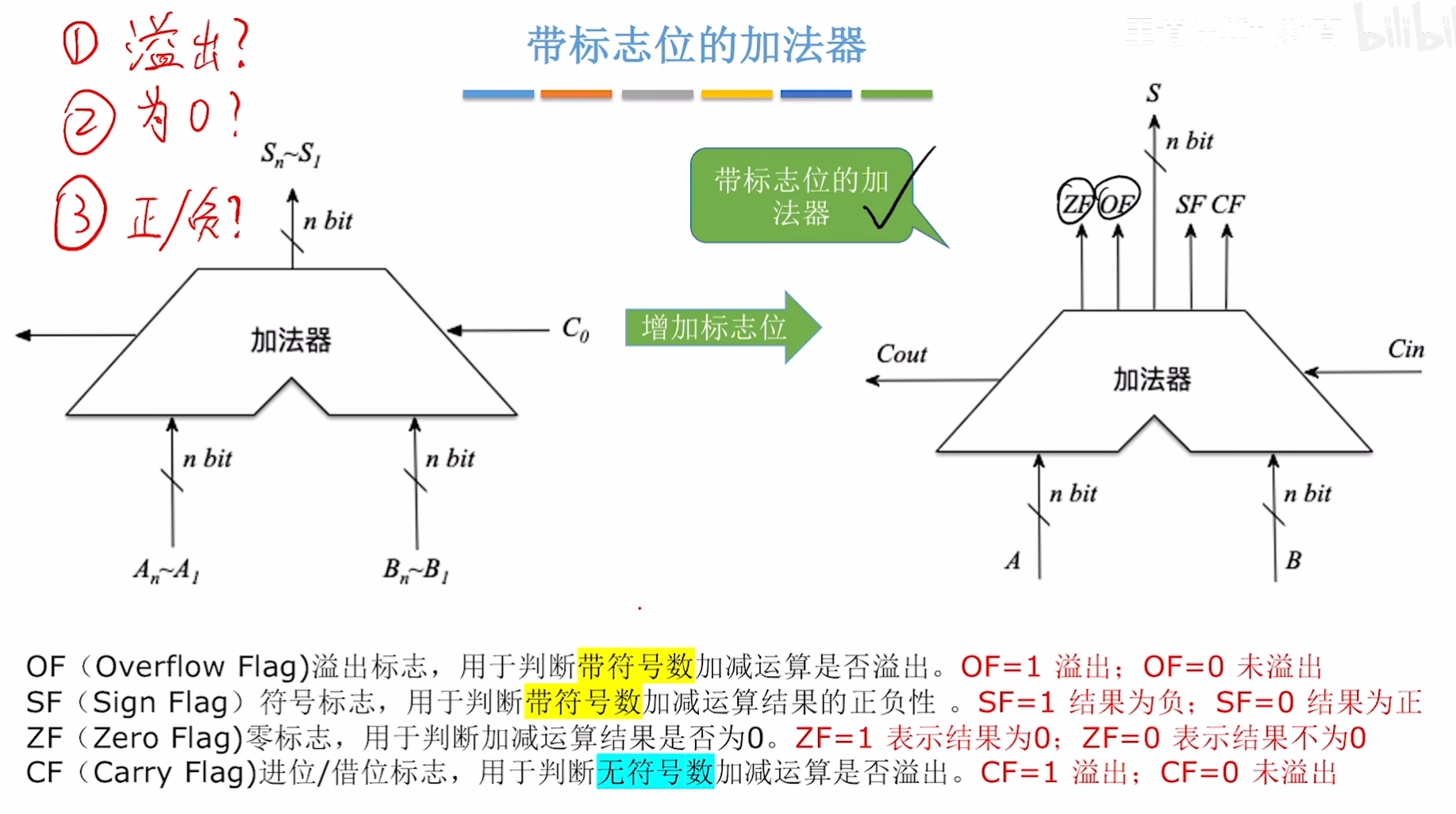

五、帶標志位的加法器

?在實際的運行過程中,我們的運算一定是正確的么? 不一定的,出錯了硬件應該發現這種問題,所以又有了帶標志位的加法器

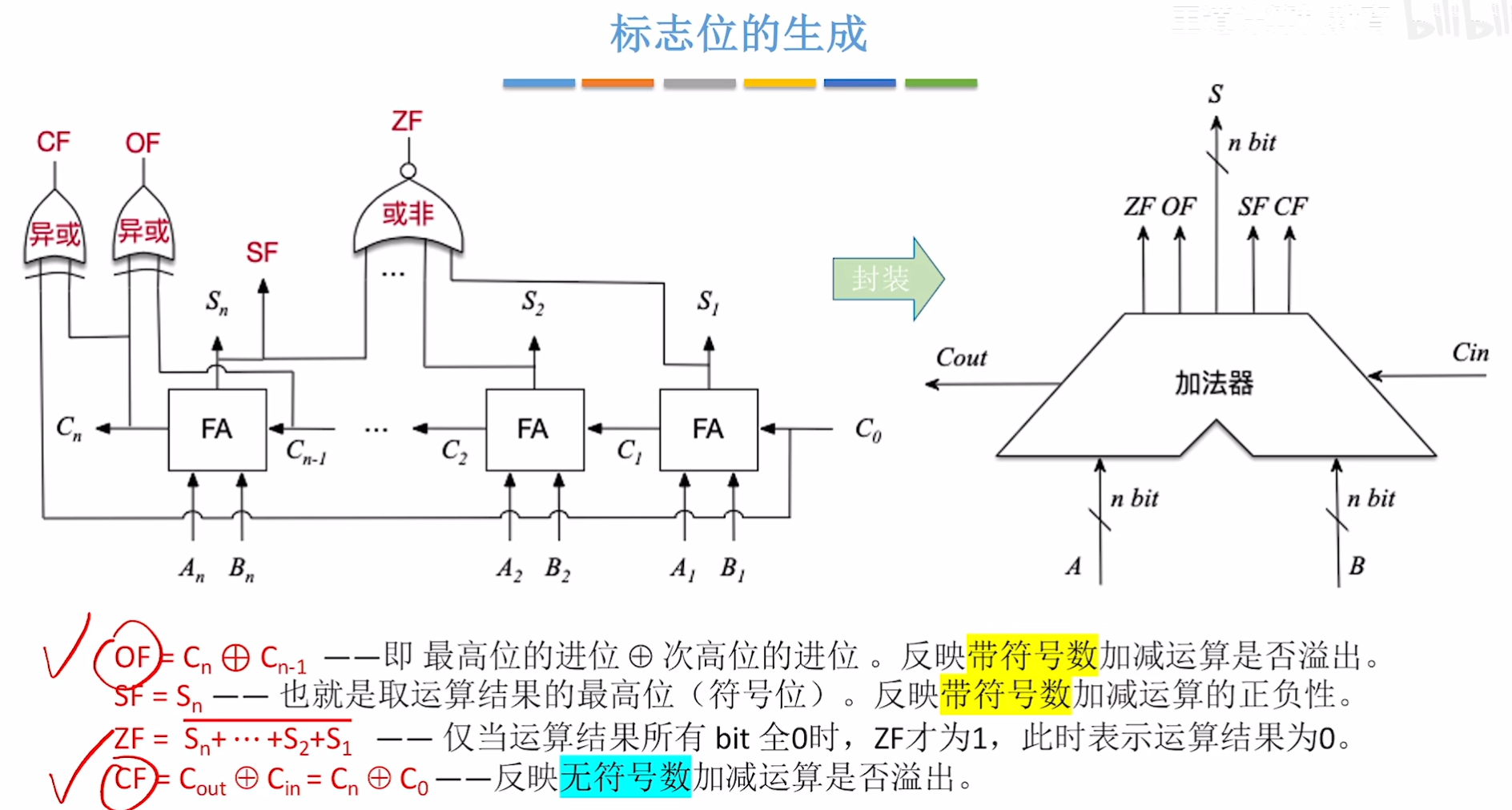

1. 標志位的生成

標志位是怎么生成的呢,大家可以了解下下面的圖,稍微了解即可,我們并不需要關心里面的細節

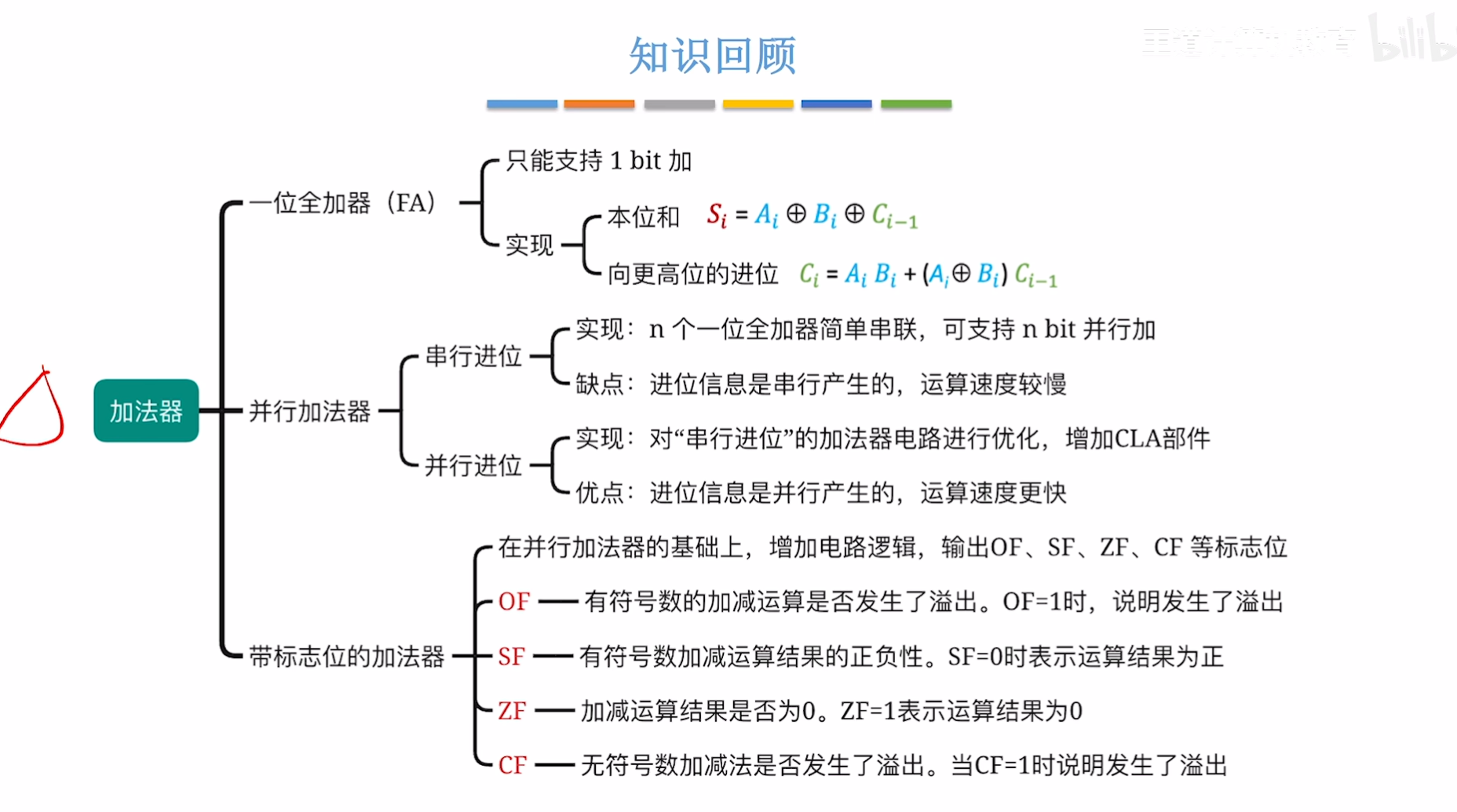

六、 總結

這里大家了解即可,實際我們的開發過程中只需要清楚CPU 內加法器的工作原理,我們并不需要知道他的工作細節是什么,除非你要考研,你搞的這么6,是要考研么!, 那另當別論。

這里大家了解即可,實際我們的開發過程中只需要清楚CPU 內加法器的工作原理,我們并不需要知道他的工作細節是什么,除非你要考研,你搞的這么6,是要考研么!, 那另當別論。

我只是了解了下其中的工作原理,有一個很有意思的思考,就是與 或 異或 同或的這四個邏輯運算的思考。

)

傳輸層(上)運輸層協議概述)

vllm在線啟動集成openweb-ui)

)

之ForwardAdd(簡化版))