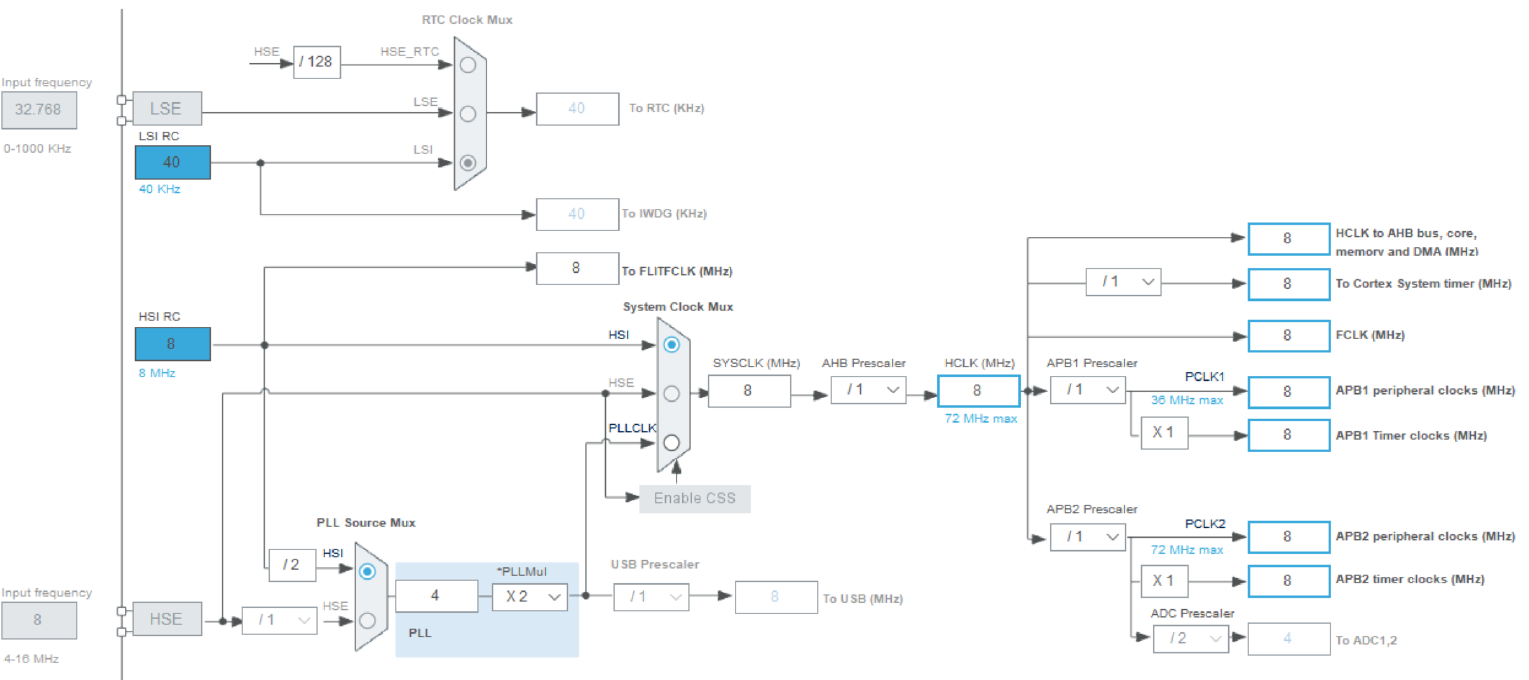

STM32的時鐘系統是其微控制器(MCU)的核心組成部分,負責為CPU、外設和存儲器等模塊提供精確的時序信號。其設計靈活且復雜,通過多級時鐘樹(Clock Tree)實現時鐘源的選擇、分頻和分配。以下是詳細介紹:

一、STM32時鐘系統的核心概念

- 時鐘源(Clock Source)

STM32提供多種時鐘源,通常包括:- HSI(High-Speed Internal Oscillator):內部高速RC振蕩器,頻率通常為8MHz(部分型號為16MHz),啟動快但精度低(±1%~2%)。

- HSE(High-Speed External Oscillator):外部高速晶振,頻率范圍廣(4~26MHz,部分型號支持更高),精度高(±0.1%~0.01%)。

- LSI(Low-Speed Internal Oscillator):內部低速RC振蕩器,頻率約32kHz,用于獨立看門狗(IWDG)或RTC備用時鐘。

- LSE(Low-Speed External Oscillator):外部低速晶振,頻率通常為32.768kHz,專為RTC(實時時鐘)設計,精度高。

- PLL(Phase-Locked Loop):鎖相環,可將輸入時鐘倍頻(如將HSE的8MHz倍頻至72MHz),提供更高頻率的主時鐘。

- 時鐘樹(Clock Tree)

STM32的時鐘信號通過多級分頻和選擇器分配到不同模塊,形成樹狀結構。時鐘樹的主要功能包括:- 時鐘源選擇:通過寄存器配置選擇HSI、HSE或PLL作為系統時鐘。

- 分頻控制:對時鐘信號進行預分頻(Prescaler),以適應不同外設的頻率需求。

- 時鐘分配:將分頻后的時鐘分配到CPU、APB總線、外設等模塊。

二、STM32時鐘樹的關鍵路徑

以STM32F1系列為例,時鐘樹的主要路徑如下:

- 系統時鐘(SYSCLK)

- 來源:HSI、HSE或PLL。

- 作用:為CPU核心、AHB總線(高速總線)和內存提供時鐘。

- 配置:通過RCC_CFGR寄存器的

SW位選擇時鐘源。

- AHB總線時鐘(HCLK)

- 來源:SYSCLK經過AHB預分頻器(AHB Prescaler)分頻。

- 作用:驅動AHB總線上的外設(如DMA、GPIO)和APB預分頻器。

- 分頻系數:通過RCC_CFGR寄存器的

HPRE位配置(1~512分頻)。

- APB總線時鐘(PCLK1/PCLK2)

- 來源:HCLK經過APB預分頻器分頻。

- 作用:

- PCLK1:驅動低速外設(如USART2、TIM2~TIM7)。

- PCLK2:驅動高速外設(如USART1、TIM1、ADC)。

- 分頻系數:通過RCC_CFGR寄存器的

PPRE1和PPRE2位配置(1~16分頻)。

- 外設時鐘

- 每個外設通過獨立的時鐘使能位(如

RCC_APB2ENR中的USART1EN)控制是否啟用時鐘。 - 外設實際工作頻率可能經過二次分頻(如USART的波特率分頻)。

- 每個外設通過獨立的時鐘使能位(如

- PLL時鐘

- 輸入源:HSI/2或HSE(可配置是否經過分頻)。

- 倍頻系數:通過RCC_CFGR寄存器的

PLLMUL位配置(2~16倍頻)。 - 輸出:PLLCLK可作為SYSCLK或USB、RTC等專用時鐘源。

三、先把“時鐘”想象成“城市供水系統”

水源(振蕩器) → 水庫/水井

水管網(時鐘樹) → 主管→支管→入戶

水表(預分頻器) → 控制每戶水壓

用水設備(CPU、外設) → 廚房、浴室、花園……

STM32 的時鐘樹就是一套多級“供水系統”:

先選水源 → 經過開關/閥門(Mux) → 加壓站(PLL) → 各級減壓閥(Prescaler) → 最終送到每家每戶。

四、圖片里出現的“水源”逐個講解

| 名字 | 頻率 | 類型 | 作用 | 比喻 |

|---|---|---|---|---|

| HSI RC | 8 MHz | 內部 RC 振蕩器 | 上電默認水源,省晶振 | 自家院子里的手壓井 |

| HSE | 4-16 MHz(常用 8 MHz) | 外部晶振/時鐘 | 精度高,可倍頻到 72 MHz | 城市自來水廠 |

| LSI RC | 40 kHz | 低速內部 RC | 獨立看門狗 IWDG、RTC 低功耗計時 | 備用小水桶 |

| LSE | 32.768 kHz | 32.768 kHz 外部晶振 | RTC 精準日歷時鐘 | 標準石英鐘 |

| PLLCLK | ≤72 MHz | PLL 倍頻輸出 | 把 HSI/HSE 放大,給 CPU 和高速外設 | 加壓泵站 |

五、時鐘樹的流向(對照圖片箭頭)

SYSCLK(總水源)

由 HSI / HSE / PLLCLK 三選一決定,最大 72 MHz。

圖中“SYSCLK (MHz)”就是最終給 CPU 喝的“主水管”。HCLK(主管道)

SYSCLK → AHB Prescaler(1、2、4…512 分頻)→ HCLK

給 AHB 總線、CPU 核心、內存、DMA 使用。

圖中“HCLK (MHz)”就是這條主管的水壓。PCLK1 / PCLK2(兩條支管)

HCLK → APB1 Prescaler → PCLK1(≤36 MHz)

掛在 APB1 的外設:USART2/3、I2C1/2、SPI2、TIM2~4…HCLK → APB2 Prescaler → PCLK2(≤72 MHz)

掛在 APB2 的外設:GPIO、USART1、SPI1、TIM1、ADC1/2…

圖中 APB1、APB2 后面分別標注了“8 MHz、72 MHz max”。

專用小水管

ADC 時鐘:PCLK2 → ADC Prescaler(2/4/6/8)→ 4~18 MHz

USB 時鐘:PLL 直接 48 MHz 分支(圖上 USB (MHz) 48)

RTC 時鐘:LSE(32.768 kHz) / LSI(40 kHz) / HSE/128 三選一,圖上“RTC Clock Mux”

獨立看門狗 IWDG:固定 LSI 40 kHz

SysTick:可以走 HCLK 或 HCLK/8,給操作系統節拍用。

六、把數字換成“水壓值”(一個常見配置舉例)

| 節點 | 實際計算 | 結果 |

|---|---|---|

| HSE | 8 MHz 晶振 | 8 MHz |

| PLL | 8 MHz × 9 | 72 MHz |

| SYSCLK | 選 PLL | 72 MHz |

| HCLK | AHB 不分頻 | 72 MHz |

| PCLK1 | 72 / 2 | 36 MHz(APB1 最大) |

| PCLK2 | 72 / 1 | 72 MHz(APB2 最大) |

| ADC | 72 / 6 | 12 MHz |

| USB | PLL / 1.5 | 48 MHz(固定) |

| RTC | 選 LSE | 32.768 kHz |

)

![[CISCN2019 總決賽 Day2 Web1]Easyweb](http://pic.xiahunao.cn/[CISCN2019 總決賽 Day2 Web1]Easyweb)

詳解)

![【python實用小腳本-205】[HR揭秘]手工黨逐行查Bug的終結者|Python版代碼質量“CT機”加速器(建議收藏)](http://pic.xiahunao.cn/【python實用小腳本-205】[HR揭秘]手工黨逐行查Bug的終結者|Python版代碼質量“CT機”加速器(建議收藏))

——網絡連接場景的 C++ 實戰)

)

)