此示例展示如何在 NI? USRP? 無線電的 FPGA 上部署雷達目標仿真算法。

介紹

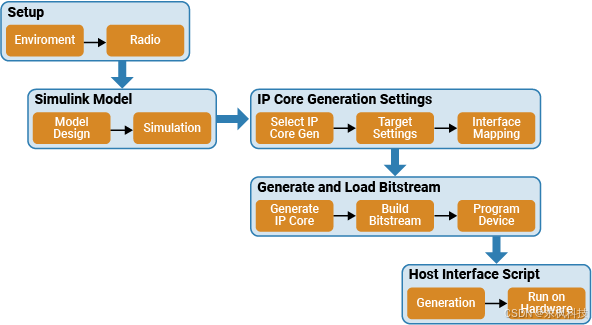

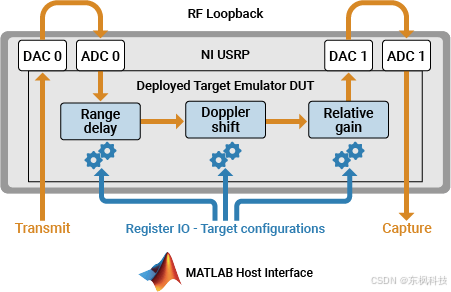

在本例中,您將從 Simulink? 模型入手,該模型可模擬最多四個雷達目標響應。您將按照分步指南,在 Simulink 中從該模型生成比特流,并使用生成的 MATLAB? 主機接口腳本將其部署到 NI USRP 無線電上。該示例允許您發送線性 FM 雷達脈沖序列,然后在 MATLAB 中捕獲并繪制模擬目標距離-多普勒響應。

有關如何在 NI USRP 無線電的 FPGA 上原型化和部署軟件定義無線電算法的更多信息,請參閱目標 NI USRP 無線電工作流程。

設計概述

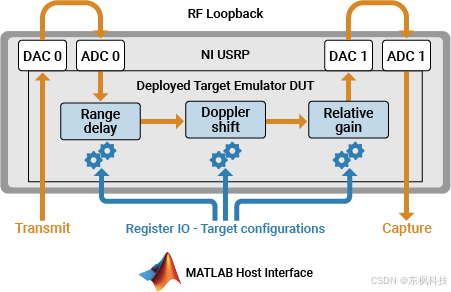

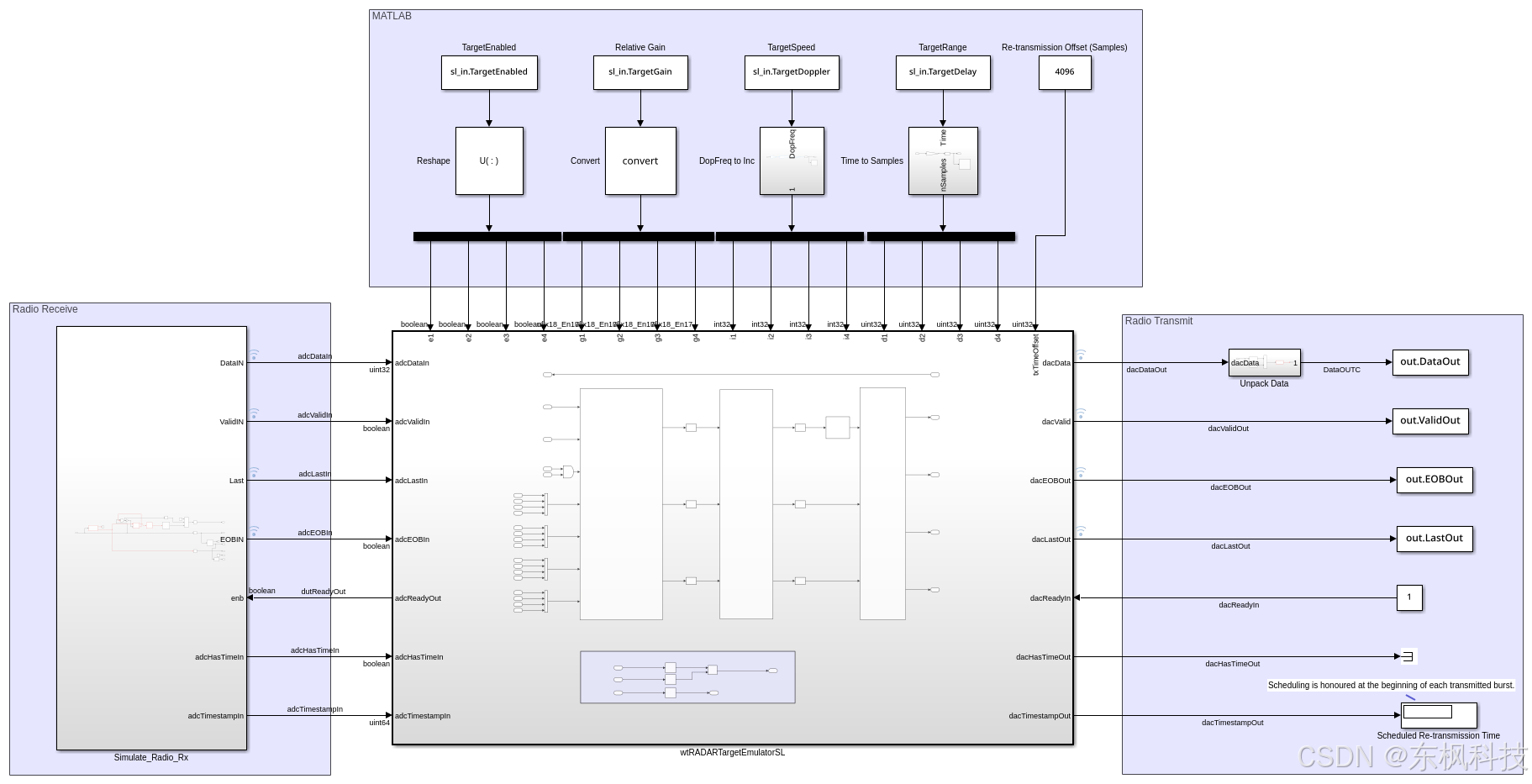

該示例使用了來自雷達目標仿真器和 HDL 編碼器(雷達工具箱)示例的算法。該算法接收線性 FM 脈沖序列,并通過對接收波形應用可變距離延遲、多普勒頻移和增益來模擬最多四個目標。然后,該算法以已知的時間偏移重新傳輸修改后的波形。此設計修改了接口,使您能夠將生成的比特流部署到 NI USRP 無線電的 FPGA 上。

打開 Simulink 模型

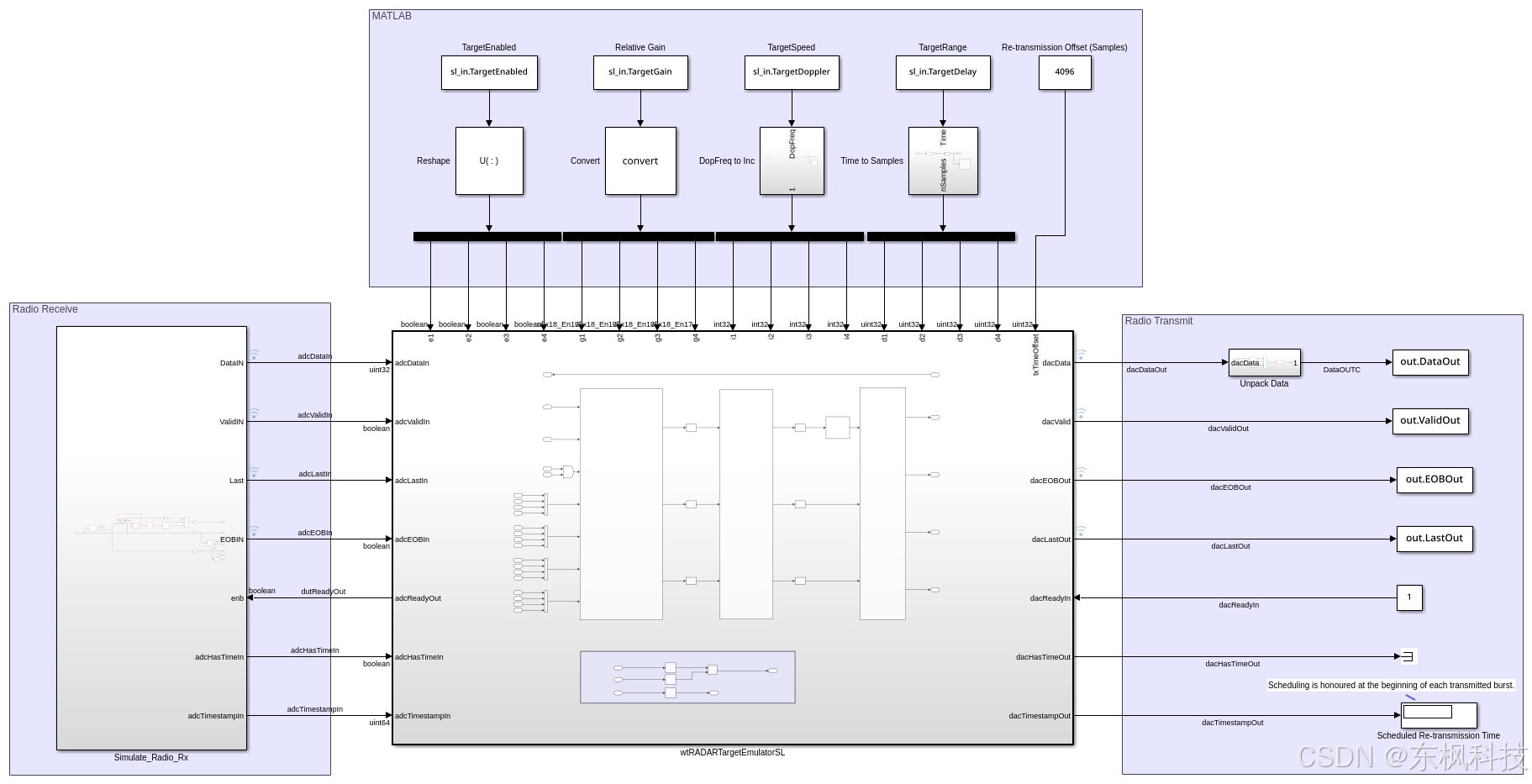

Simulink 模型采用硬件建模方式實現目標仿真算法,并使用支持 HDL 代碼生成的模塊。它采用定點算法,并包含控制模型數據流的控制信號。

從 MATLAB 打開模型。

open_system('wtRADARTargetEmulatorSL');

該模型為子系統提供數據并保存其輸出數據wtRADARTargetEmulatorSL。

打開wtRADARTargetEmulatorSL子系統。

open_system('wtRADARTargetEmulatorSL/wtRADARTargetEmulatorSL');

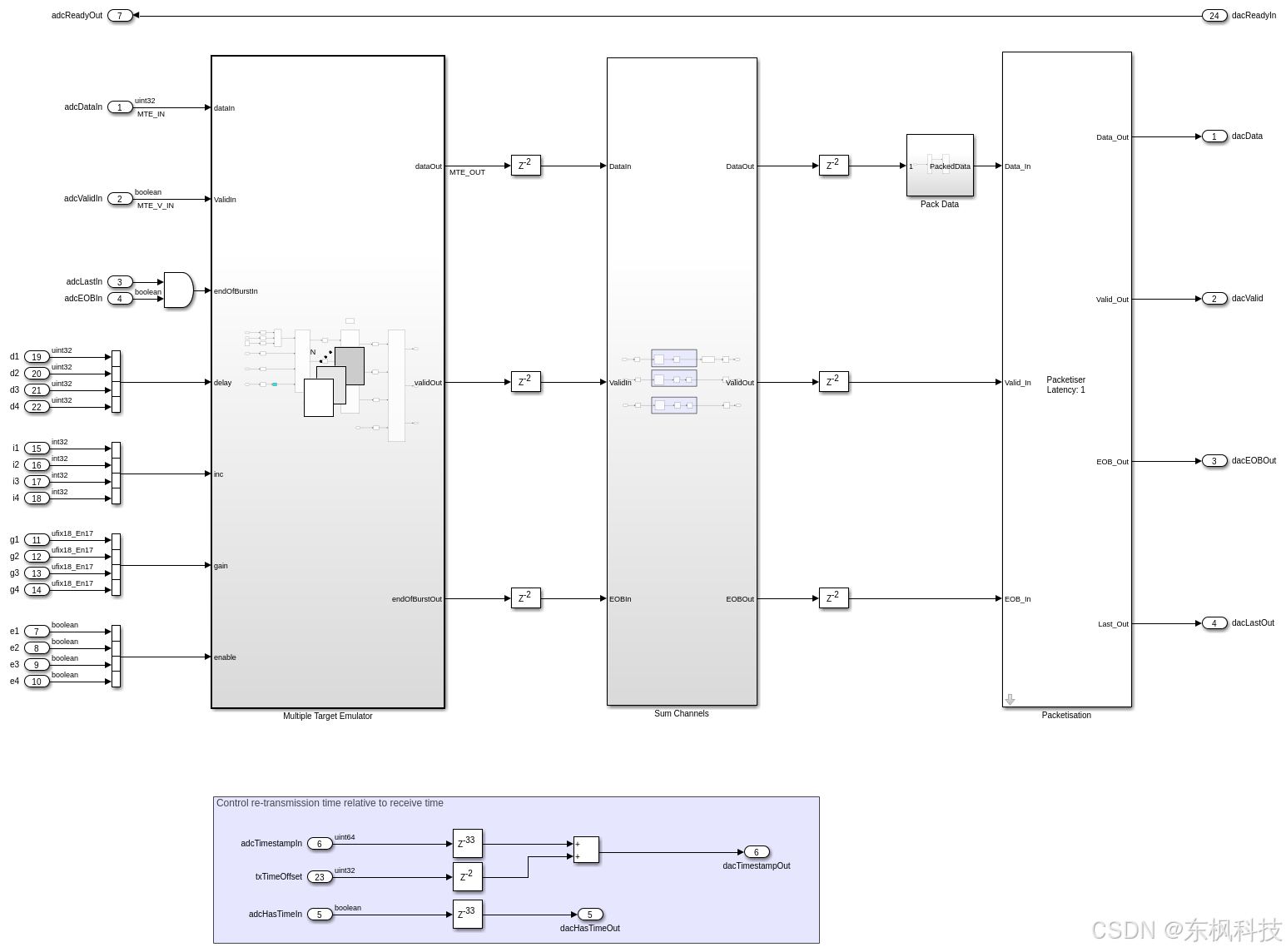

數據流經這些塊和子系統:

-

AND 塊在每個突發的最后一個數據包的最后一個樣本上聲明突發結束 (EOB) 信號。

-

該Multiple Target Emulator子系統模擬四個不同目標的響應。

-

該Sum Channels子系統將來自四個目標的響應合并為單個數據流。

-

每 256 個有效樣本或 EOB 信號被斷言時,分組塊就會斷言最后一個信號。

-

該區域通過由txTimeOffsetControl retransmission time relative to receive time端口控制的固定值生成從無線電重新傳輸下一個數據包的時間戳。

打開Multiple Target Emulator子系統。

open_system('wtRADARTargetEmulatorSL/wtRADARTargetEmulatorSL/Multiple Target Emulator');

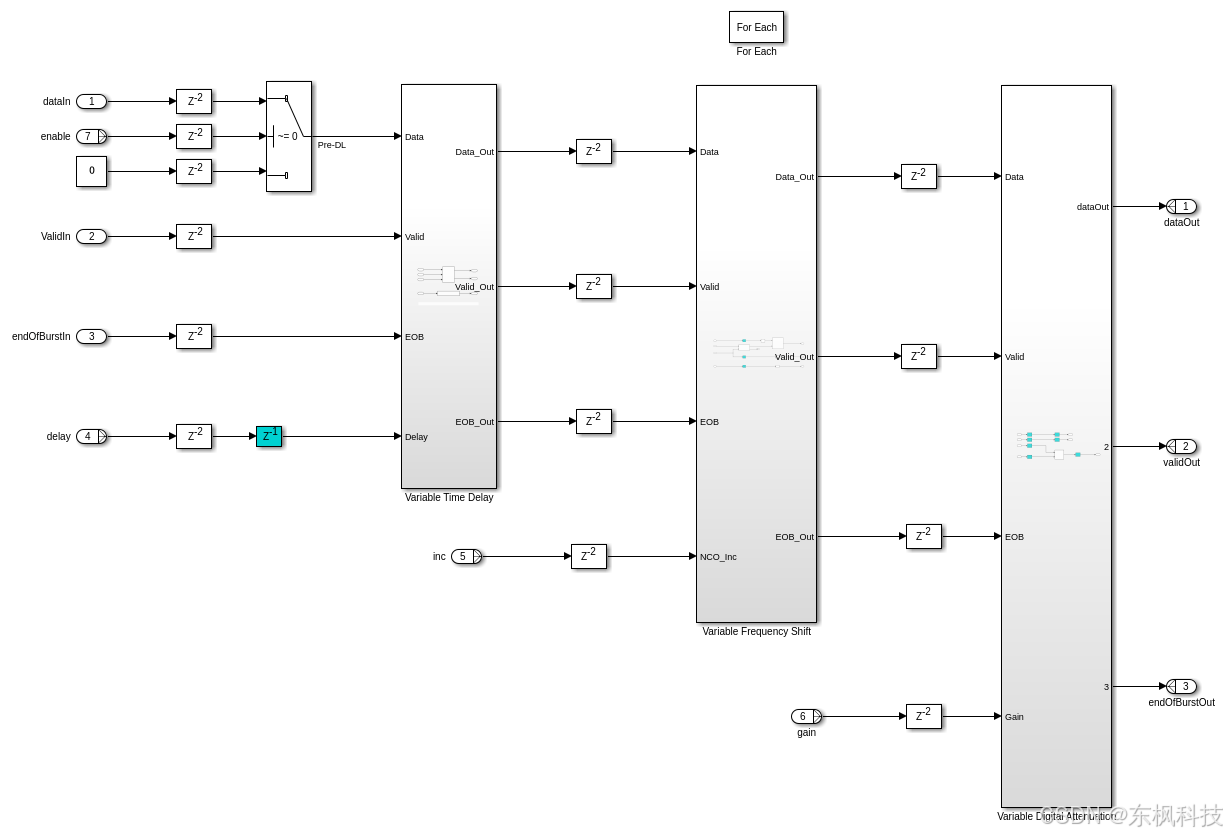

該Multiple Target Emulator子系統根據輸入enable、delay、inc和gain端口,應用可變時間延遲、可變頻移和可變衰減,模擬四個不同目標的響應。操作如下:

-

當enable為真時,輸入數據將提供給可變時間延遲。

-

可變時間延遲將輸入樣本緩沖在內存中,緩沖的樣本數量由延遲端口指定。

-

延遲數據與數控振蕩器 (NCO) 的輸出相乘,以實現可變頻率偏移。NCO 由inc端口值控制。

-

延遲和移位的數據與增益端口值相乘,以實現可變衰減。

open_system('wtRADARTargetEmulatorSL');

每個目標的輸入都被指定為wtRADARTargetEmulatorSL子系統上的輸入寄存器端口:e1、e2、e3和e4對應于啟用輸入端口;d1、d2、d3和d4對應于延遲輸入;i1、i2、i3和i4對應于inc輸入端口;g1、g2、g3和g4分別對應于四個目標的增益輸入端口。

模擬設計

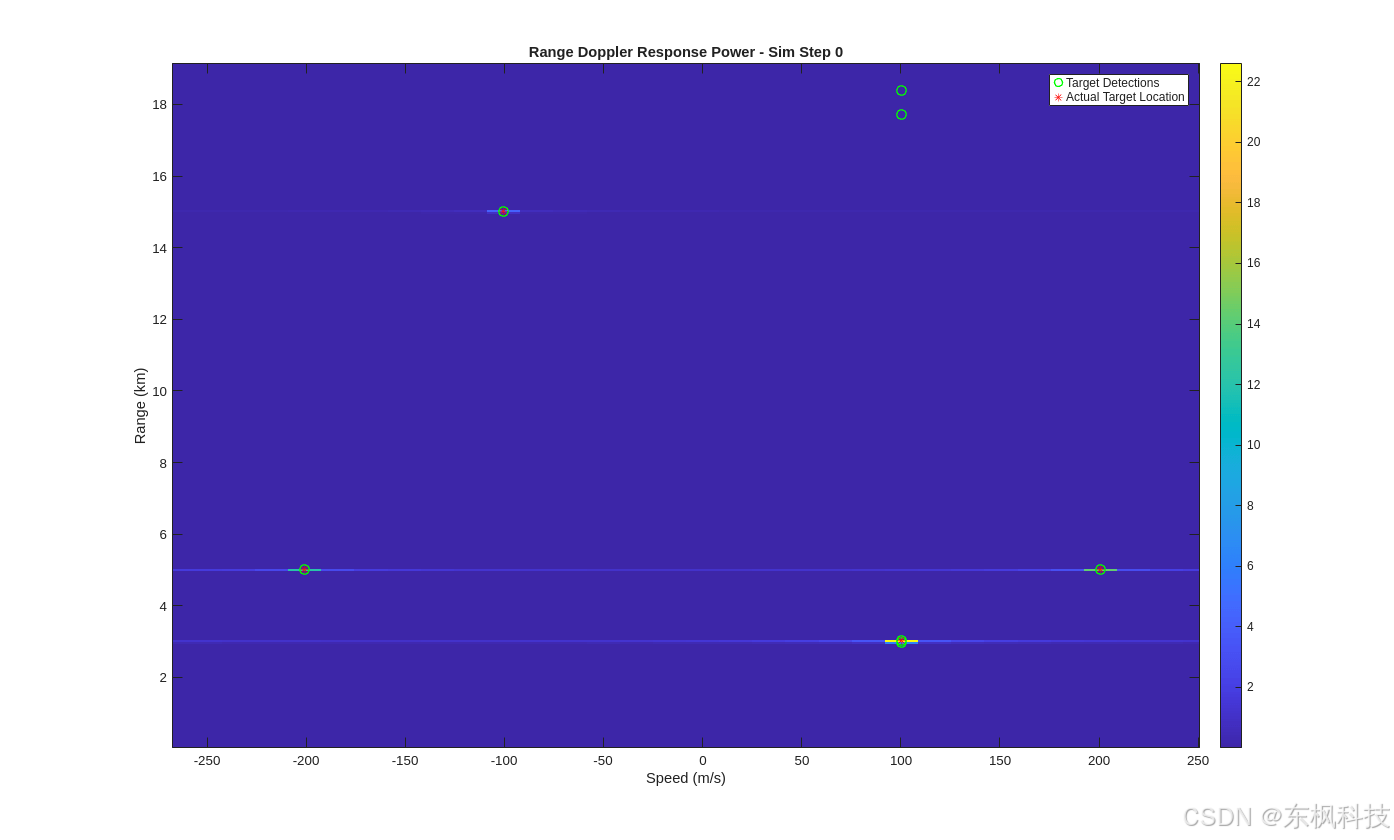

通過仿真模型驗證設計。啟用四個目標并指定初始雷達截面 (RCS)、距離和速度。

targetEnabled = [true true true true]; % 設置為 true 以模擬目標

targetRCS = [1 2 3 4]; % dBsm

targetRange = [5e3 15e3 3e3 5e3]; % m

targetSpeed = [-200 -100 100 200]; % m/s設置模型應用的相對增益所基于的最大增益。這可以避免由于定點數據類型造成的不必要的信號損失,并且可以通過使用無線電前端的無線電增益來計算。指定maxGain為空可在輔助函數中使用計算出的最高實際增益helperRadarTargetSimulationSetup。

maxGain = [];

使用輔助函數在 MATLAB 中設置模型所使用的目標仿真參數helperRadarTargetSimulationSetup。

sl_in = helperRadarTargetSimulationSetup(targetEnabled,targetRCS,targetRange,targetSpeed,maxGain);

運行 Simulink 模型。

sl_out = sim("wtRADARTargetEmulatorSL.slx");### Searching for referenced models in model 'wtRADARTargetEmulatorSL'.

### Total of 1 models to build.

### Building the rapid accelerator target for model: wtRADARTargetEmulatorSL

### Successfully built the rapid accelerator target for model: wtRADARTargetEmulatorSL

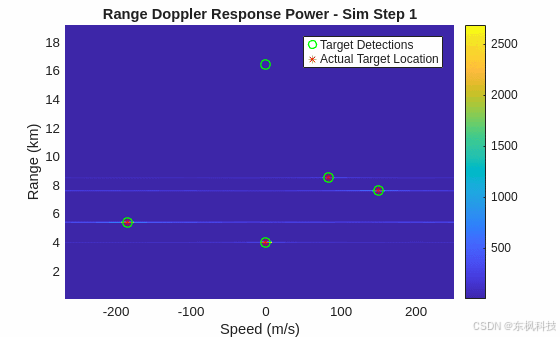

處理模擬輸出數據并使用輔助函數繪制距離多普勒響應helperVisualizeRadarTargetSimulation。

創建距離多普勒響應對象來處理數據

設置環境和無線電

要使用 Wireless Testbench? 連接 NI USRP 無線電,您必須首先安裝并配置其他工具箱、支持包和第三方工具。更多信息,請參閱NI USRP 無線電安裝指南。

如果您之前未保存過無線電硬件的無線電設置配置,請使用此radioSetupWizard功能打開“無線電設置”向導并按照步驟操作。要查看之前保存的無線電設置配置,請使用此radioConfigurations功能。

配置模型以生成 IP 核

首先,使用(HDL Coder)函數設置 Xilinx? 工具鏈。指定 Vivado? bin 目錄的路徑。更多信息,請參閱設置第三方工具。hdlsetuptoolpath

>> hdlsetuptoolpath('ToolName','Xilinx Vivado','ToolPath','/opt/Xilinx/Vivado/2021.1/bin');

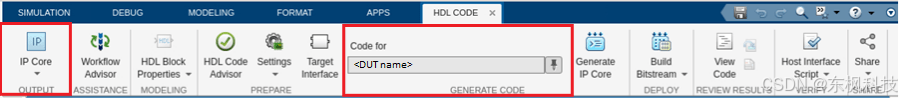

在Simulink 工具條的“應用”選項卡中,選擇“HDLCoder”。打開“HDL 代碼”選項卡并按照以下步驟操作:# 確保子系統已在“代碼”選項wtRADARTargetEmulatorSL中固定。要固定此選項,請在 Simulink 模型中選擇子系統,然后單擊固定圖標。# 在“輸出”>“IP 核”選項中選擇“IP 核”。wtRADARTargetEmulatorSL

配置 HDL 代碼生成設置

要打開“配置參數”窗口,請點擊“HDL 代碼”選項卡中的“設置”。然后,請按照以下步驟操作:

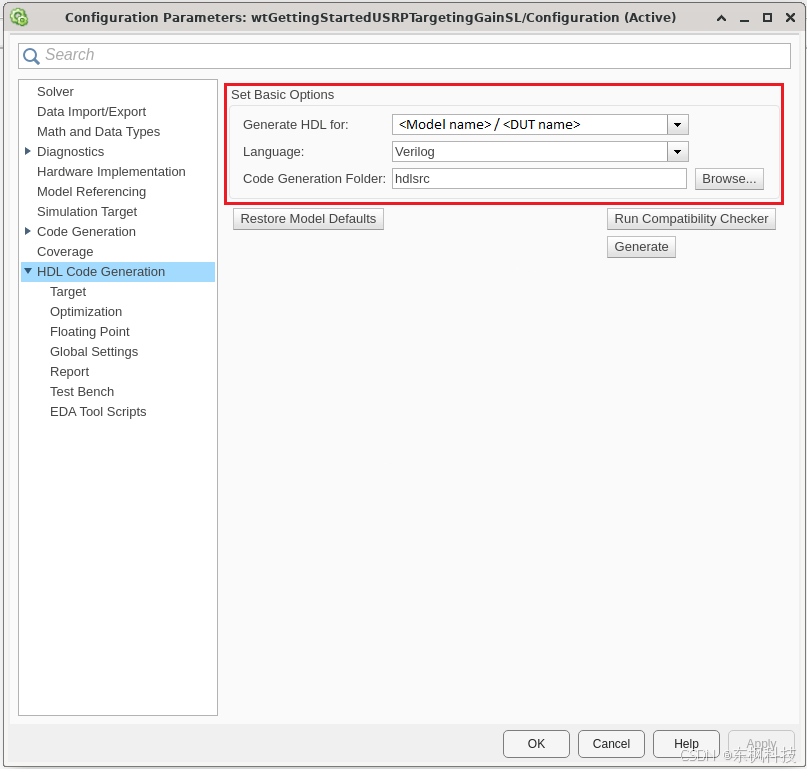

在HDL 代碼生成面板的基本選項中,確保將語言設置為Verilog。默認情況下,HDL Coder 會在文件夾中生成 Verilog 文件hdlsrc。您可以選擇其他位置。如果您進行了任何更改,請點擊應用。

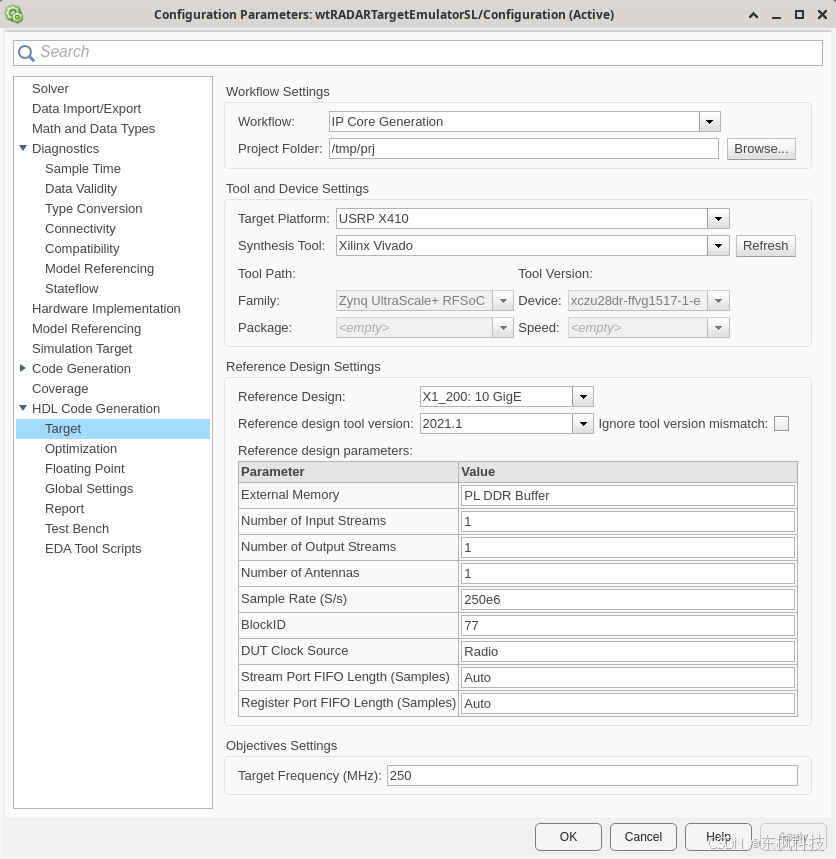

在HDL 代碼生成 > 目標 > 工作流設置中,單擊瀏覽并選擇要保存生成的項目文件的項目文件夾。

在HDL 代碼生成 > 目標 > 工具和設備設置中,將目標平臺設置為USRP X410。如果您使用的是其他 USRP 無線電,請選擇相應的目標平臺并相應地調整參考設計參數。

在“HDL 代碼生成”>“目標”>“參考設計設置”中,將“參考設計”設置為X1_200 10GigE,或者如果您使用的是其他 USRP 無線電,則設置為所需的參考 FPGA 映像。使用以下值設置參考設計參數:

-

外部存儲器- 設置為PL DDR Buffer通過無線電上的內存緩沖區傳輸樣本。此設置可確保 MATLAB 和無線電之間的樣本連續。

-

輸入流的數量- 設置為1,因為 DUT 連接到一個數據輸入流。

-

輸出流的數量- 設置為1,因為 DUT 連接到一個數據輸出流。

-

天線數量- 設置為1,因為 DUT 有一個無線電接收和發射通道。

-

采樣率 (S/s) - 設置250e6為無線電支持的目標模擬器硬件所需的基帶采樣率。有關支持的采樣率列表,請參閱NI USRP 無線電中的基帶采樣率。

-

BlockID - 設置為任意 32 位十六進制數。默認值為12345678。

-

DUT 時鐘源- 設置為Radio。此選項選擇無線電前端的主時鐘速率 (MCR) 作為 DUT 時鐘。

-

流端口 FIFO 長度(樣本) - 設置為Auto。

-

寄存器端口 FIFO 長度(樣本) - 設置為Auto。

在HDL 代碼生成 > 目標 > 目標設置中,目標頻率默認設置為無線電支持的最大 MCR。

單擊“應用”。

有關更多信息,請參閱配置 HDL 代碼生成設置。

配置目標接口

-

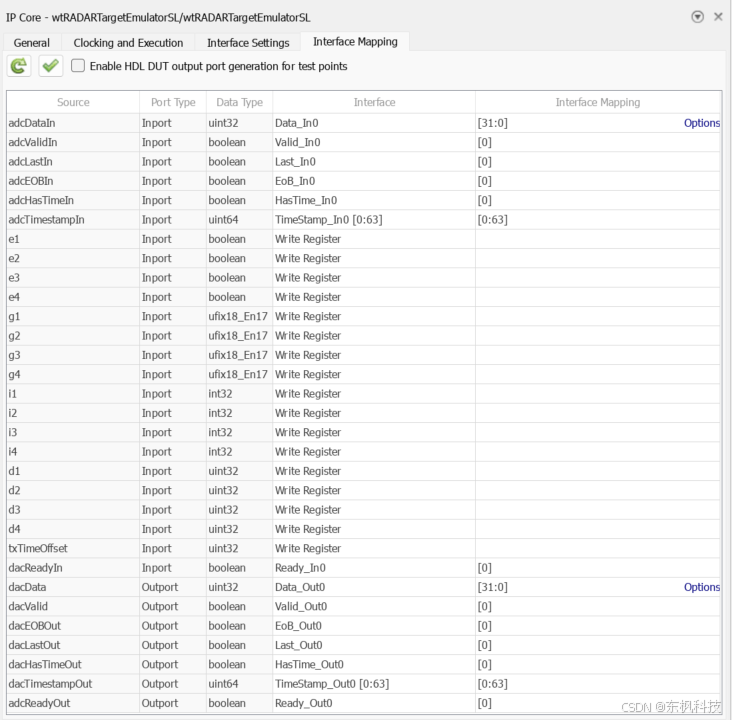

在HDL Code選項卡中,單擊Target Interface以打開 IP Core 編輯器。

-

在“接口映射”選項卡中,單擊重新加載端口接口映射選項Reload IP core settings and interface mapping table from model:

-

將 DUT 的輸入寄存器指定為寫入寄存器。

-

為輸入和輸出流接口分配數據、有效、就緒、最后、突發結束 (EOB)、hastime 和時間戳信號。

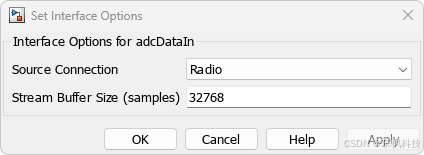

每個流接口數據輸入和輸出端口都有一個選項菜單。要重新傳輸接收到的樣本,請將源和接收器連接選項設置為Radio。對于這些adcDataIn選項,請將流緩沖區大小設置為32768,這是默認設置。緩沖區大小必須是 2 的冪,以確保最佳利用 FPGA RAM 資源。緩沖區大小根據樣本數量指定。

單擊以下按鈕驗證接口映射Validate IP core settings and interface mapping:

生成并加載比特流

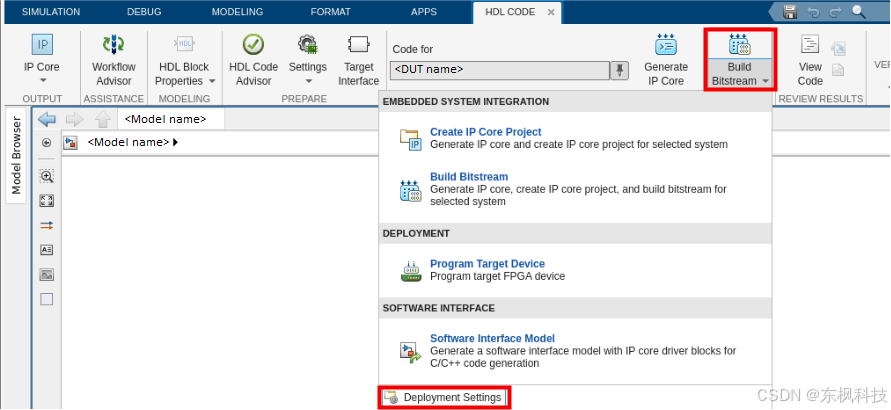

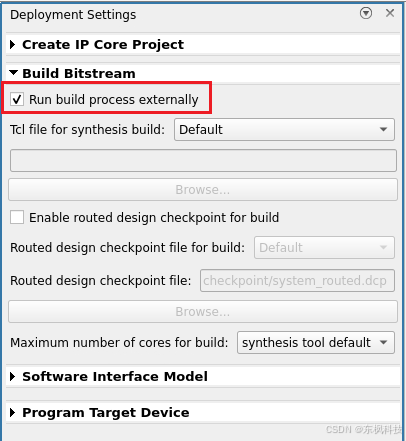

要從 IP 核生成比特流,首先從“構建比特流”菜單中打開部署設置,并確保選中“在外部運行構建過程”選項。此設置是默認設置,可確保比特流構建在外部 Shell 中執行,從而允許您在構建 FPGA 映像時繼續使用 MATLAB。

點擊“構建比特流”即可創建 Vivado IP 核項目并構建比特流。基本項目檢查完成后,診斷查看器會顯示一條Build Bitstream Successful消息以及警告消息。但是,您必須等到外部 shell 顯示比特流構建成功后才能繼續下一步。比特流構建過程可能需要幾個小時。在顯示構建成功提示之前關閉外部 shell 將終止構建。成功構建比特流后,此項目的比特流將以名稱生成x4xx.bit,并位于build_X410_X1_200/build_X410_X1_200工作目錄的文件夾中。

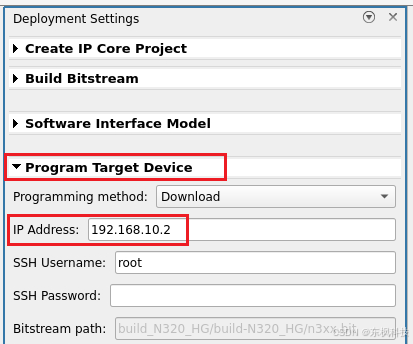

在“構建比特流”中,打開“部署設置”。在“程序目標設備”設置中,設置 IP 地址。默認值為 192.168.10.2。如果您在使用“無線電設置”向導設置硬件時更改了默認 IP 地址,請相應地設置 IP 地址。

要將比特流加載到收音機上,有兩個選項:

-

在后續步驟中使用生成的主機接口腳本加載比特流,該腳本調用該programFPGA函數。

-

現在通過單擊“構建比特流”菜單中的“編程目標設備”將比特流加載到設備上。

如果您的無線電設備是 USRP X310,則編程大約需要五分鐘。對于其他無線電設備,則只需不到一分鐘。有關更多信息,請參閱生成比特流和編程 FPGA。

生成和修改主機接口腳本

要生成 MATLAB 腳本,以便連接到無線電并在其上運行已部署的設計,請點擊“HDL 代碼”選項卡中的“主機接口腳本”。這將生成一個接口腳本文件和設置函數文件,它們特定于 IP 核的目標接口映射。更多信息,請參閱運行和驗證硬件實現。

運行主機接口腳本

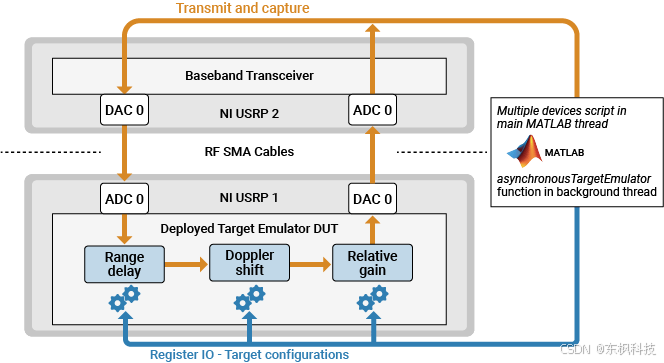

此示例提供了兩個現成的實時腳本,用于連接、配置和控制部署在 FPGA 上的目標仿真算法的無線電設備。您可以選擇使用單個無線電設備運行和驗證 DUT,或者使用第二個無線電設備發送測試信號并接收響應。

在單無線電上運行并驗證 DUT

打開RADARTargetEmulator_SingleDevice.mlx。運行此實時腳本,從 MATLAB 發送雷達脈沖序列,將脈沖序列接收到目標模擬器 DUT 中,發送目標模擬器響應,并將響應捕獲到 MATLAB 中。

繪制響應圖,并疊加目標位置和恒虛警率 (CFAR) 目標檢測結果,以驗證被測器件 (DUT) 的運行情況。該圖顯示了示例輸出。

open("./RADARTargetEmulator_SingleDevice.mlx")

使用外部刺激運行 DUT

打開RADARTargetEmulator_MultiDevice.mlx。運行此實時腳本,在一個無線電的后臺線程中模擬雷達場景。同時,在 MATLAB 主線程中,將第二個無線電配置為基帶收發器,以發射雷達脈沖序列并捕獲響應。

您還可以使用此方法來模擬其他無線電硬件的目標響應。

open("./RADARTargetEmulator_MultiDevice.mlx")

(貪心算法))

)

![[langchain] Sync streaming vs Async Streaming](http://pic.xiahunao.cn/[langchain] Sync streaming vs Async Streaming)

)

)

,背包問題總結)

)