目錄

一、時鐘樹:M3---STM32F103

1、主要時鐘來源

?2、時鐘系統線路分析

HSE時鐘

HSI時鐘

LSE時鐘

LSI時鐘

PPLCLK ---鎖相環時鐘

SYSCLK ---系統時鐘

HCLK時鐘

PCLK1時鐘

PCLK2時鐘

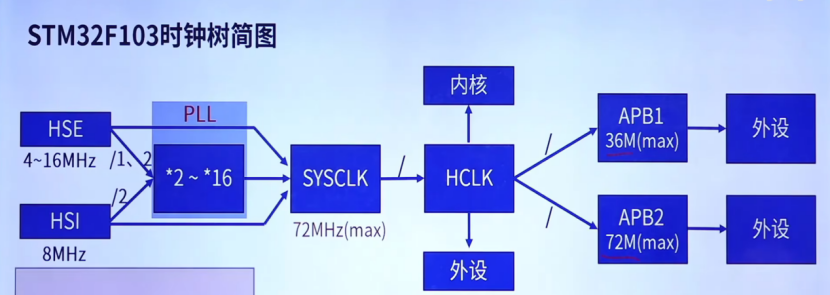

3、時鐘樹簡圖

4、構成部分作用分析?

二、時鐘樹:M4---STM32F407

1、主要時鐘來源

2、時鐘簡圖?

?3、時鐘系統線路分析

HSE時鐘

HSI時鐘

LSE時鐘

LSI時鐘

SYSCLK ---系統時鐘

PPLCLK ---鎖相環時鐘

HCLK時鐘

PCLK1時鐘

PCLK2時鐘

4、構成部分作用分析

為什么要有時鐘?

STM32時鐘系統主要的目的就是給相對獨立的外設模塊提供時鐘,主要也是為了降低整個芯片的功耗,所有外設時鐘默認都是關閉狀態(disable)當我們使用某個外設就要開啟這個外設的時鐘(enable),不同外設需要的時鐘頻率不同,沒必要所有外設都用高速時鐘造成浪費,而且有些外設也接受不了這么高的頻率,這也是為什么STM32有四個時鐘源的原因,就是兼容不同速度的外設,STM32的四個時鐘源分別為:HSE、 LSE、HSI、LSI。其中,一般情況下我們使用HSE時鐘來作為我們的系統時鐘,它可以用來驅動APB,DMA,Cortex等系統;而低速時鐘一般用于驅動RTC

一、時鐘樹:M3---STM32F103

1、主要時鐘來源

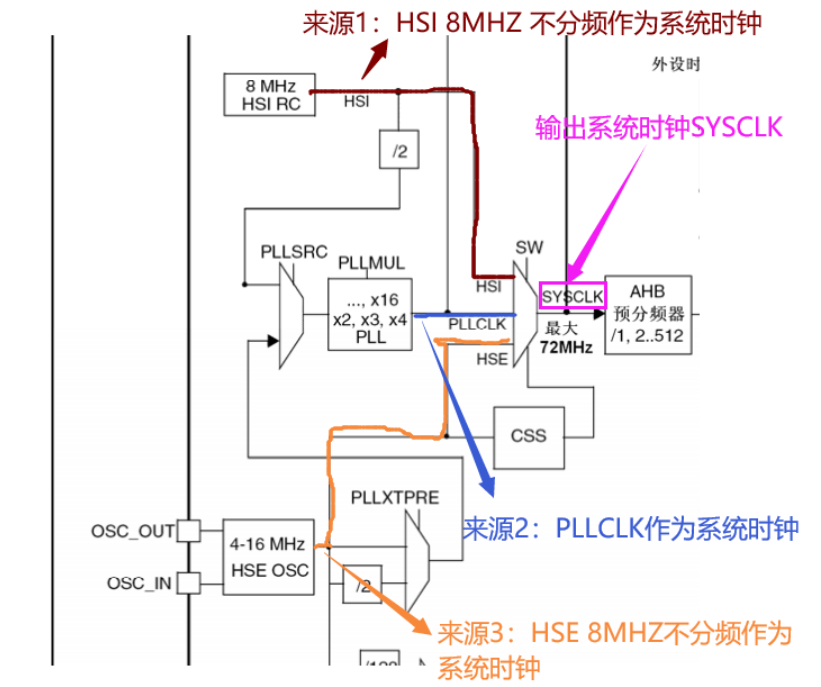

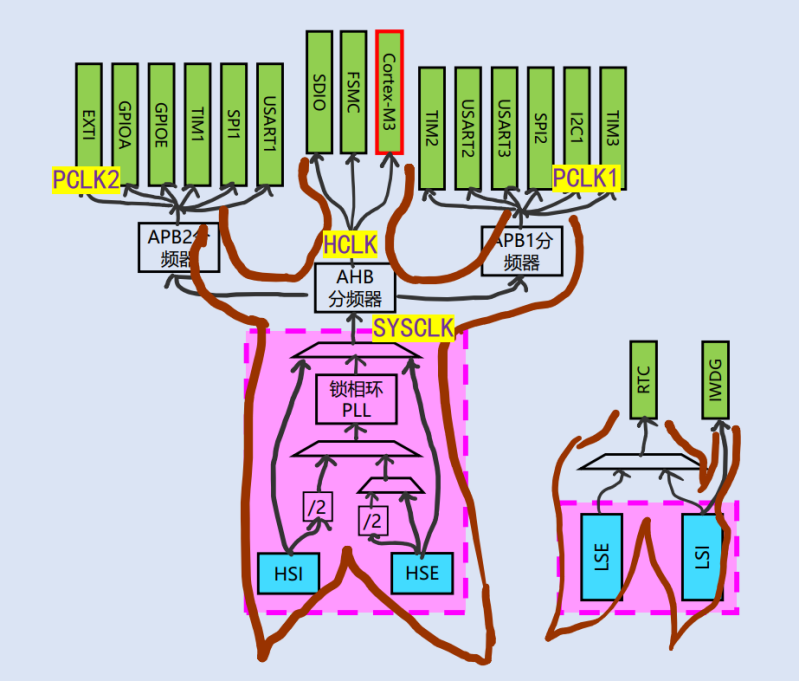

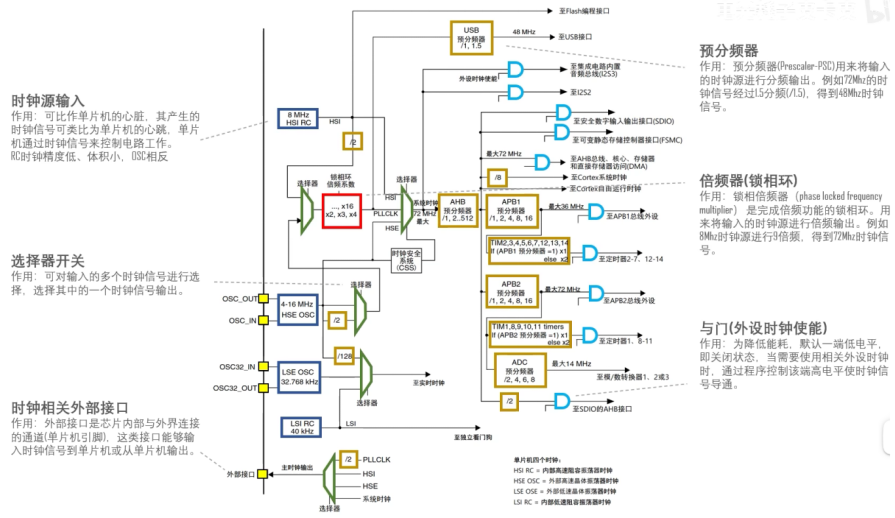

2、時鐘系統線路分析

2、時鐘系統線路分析

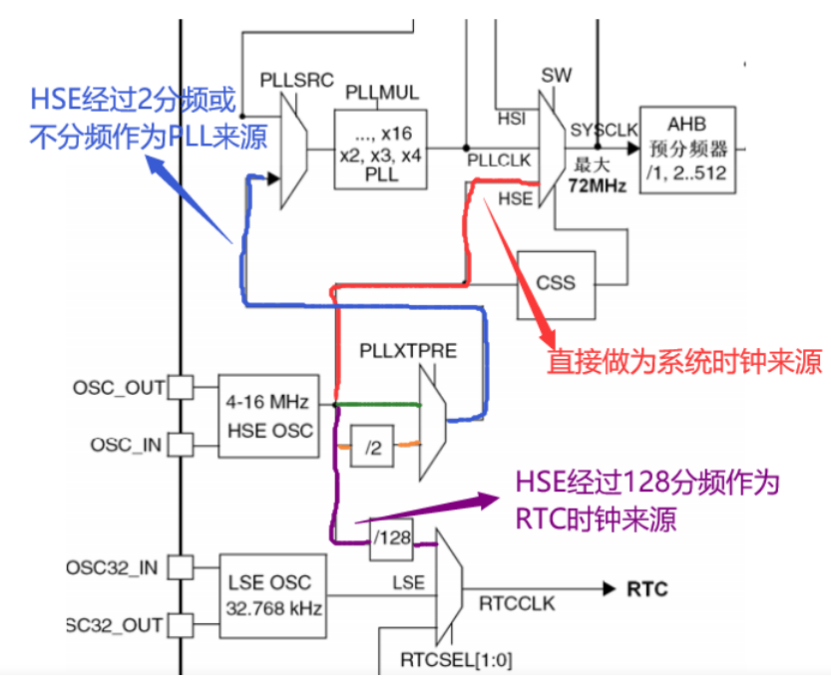

HSE時鐘

來源:無源晶振(4-16M),通常使用8M。

作用:可不分頻或2分頻(頻率/2)作為PLL鎖相環的輸入,還可直接不分頻作為系統時鐘,128分頻作為外設RTC時鐘的輸入

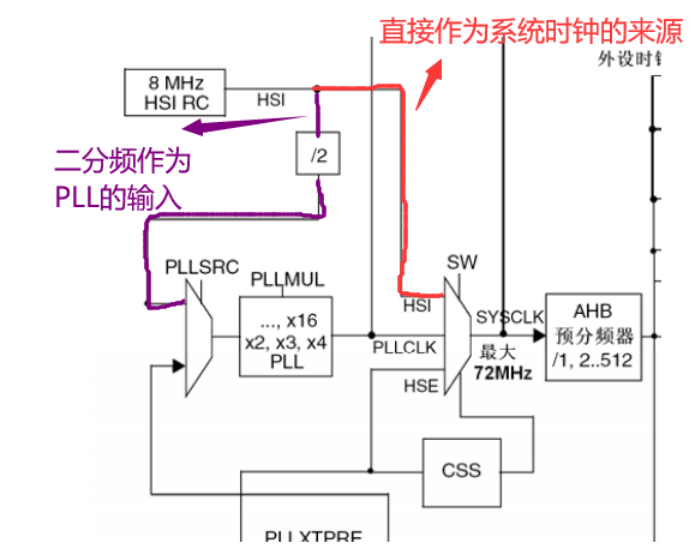

HSI時鐘

來源:芯片內部,大小為8M,當HSE故障時,系統時鐘會自動切換到HSI,直到HSE啟動成功。

作用:可直接作為系統時鐘或在2分頻后作為PLL輸入。HSI RC振蕩器能夠在不需要任何外部器件的條件下提供系統時鐘。它的啟動時間比HSE晶體振蕩器短。然而,即使在校準之后它的時鐘頻率精度仍較差

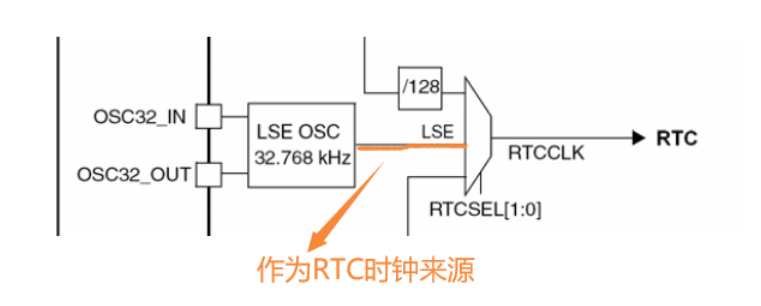

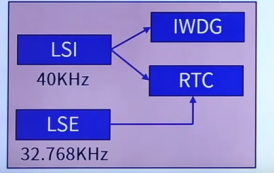

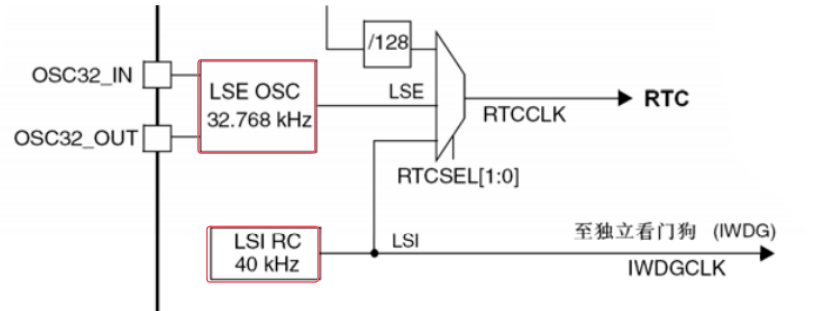

LSE時鐘

來源:芯片內部,LSE晶體是一個32.768kHz的低速外部晶體或陶瓷諧振器。它為實時時鐘或者其他定時功能提供一個低功耗且精確的時鐘源。

作用:直接作為RTC是時鐘來源

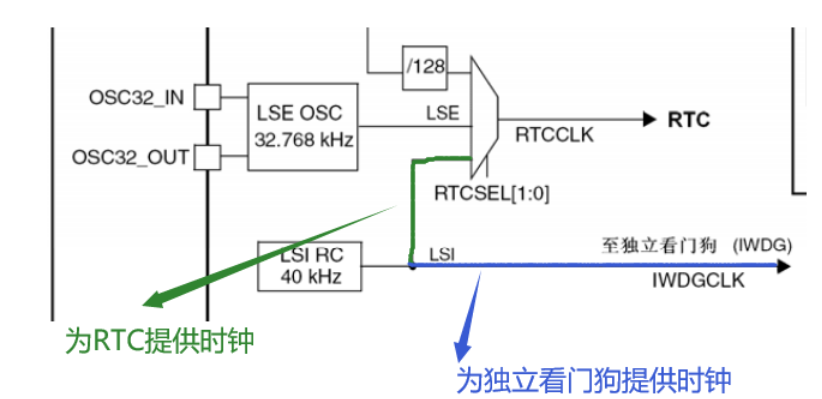

LSI時鐘

來源:內部芯片,LSI RC擔當一個低功耗時鐘源的角色,它可以在停機和待機模式下保持運行,LSI時鐘頻率大約40kHz(在30kHz和60kHz之間)。

作用:為獨立看門狗和自動喚醒單元(RTC)提供時鐘

PPLCLK ---鎖相環時鐘

來源:選擇HSI振蕩器除2或HSE振蕩器為PLL的輸入時鐘,和選擇倍頻因子,必須在其被激活前完成。一旦PLL被激活,這些參數就不能被改動。

作用:內部PLL可以用來倍頻HSI RC的輸出時鐘或HSE晶體輸出時鐘(倍頻數2~16倍),而經過倍頻變成PLLCLK可以作為系統時鐘源

?

SYSCLK ---系統時鐘

系統時鐘:SYSCLK,最高為72M(ST官方推薦的)

來源:HSI、HSE、PLLCLK

?

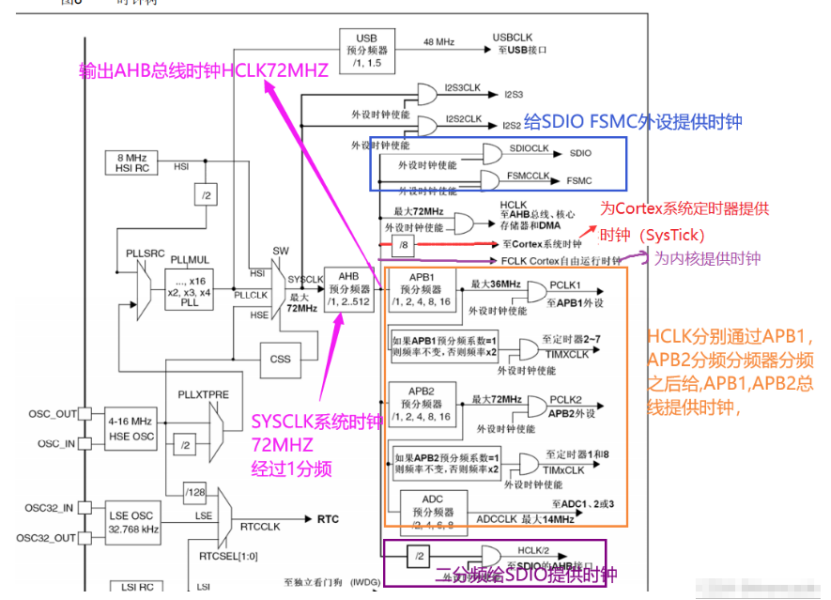

HCLK時鐘

HCLK:AHB高速總線時鐘,速度最高為72M。

作用:為AHB總線的外設提供時鐘、為Cortex系統定時器提供時鐘(SysTick)、為內核提供時鐘(FCLK)。

來源:系統時鐘分頻得到,一般設置HCLK=SYSCLK=72

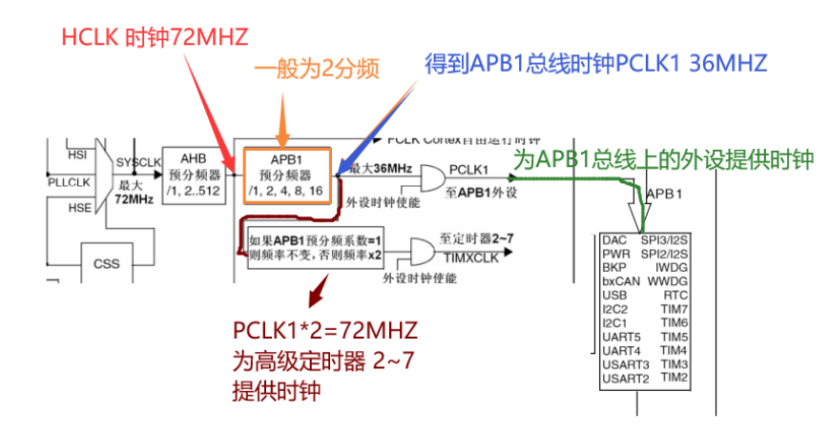

PCLK1時鐘

PCLK1:APB1低速總線時鐘,最高為36M。

作用:為APB1總線的外設提供時鐘。1或2倍頻之后則為APB1總線的定時器2~7提供時鐘來源:HCLK分頻得到,一般配置PCLK1=HCLK/2=36M

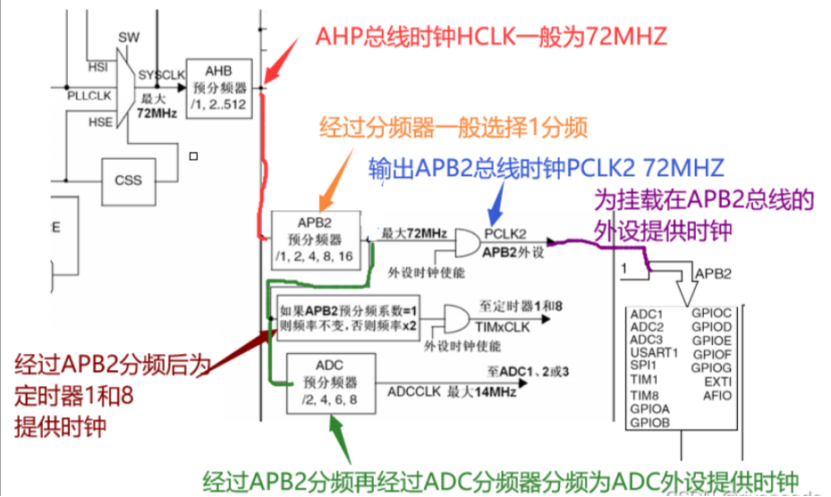

PCLK2時鐘

PCLK2:APB2高速總線時鐘,最高為72M。

作用:為APB2總線的外設提供時鐘。為APB2總線的定時器1和8提供時鐘APB2分頻器還有一路輸出供ADC分頻器使用,分頻后送給ADC模塊使用。

來源:HCLK分頻得到,一般配置PCLK2=HCLK=72M

?

3、時鐘樹簡圖

簡圖①

簡圖②

大樹:?

小樹:

4、構成部分作用分析?

二、時鐘樹:M4---STM32F407

1、主要時鐘來源

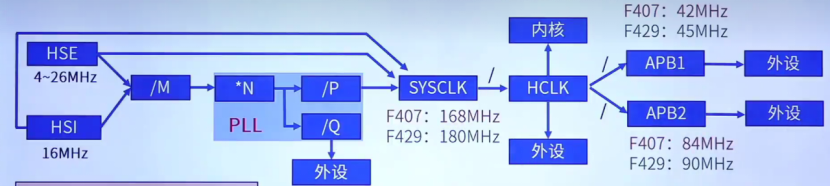

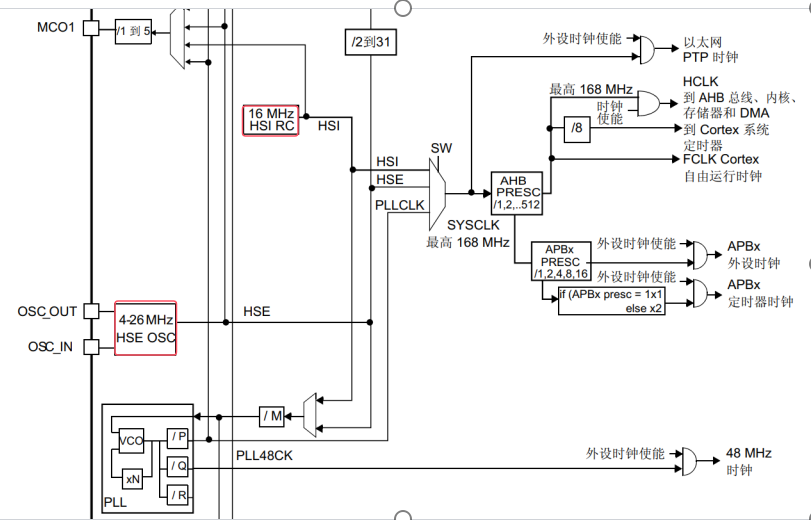

2、時鐘簡圖?

大樹:

小樹:?

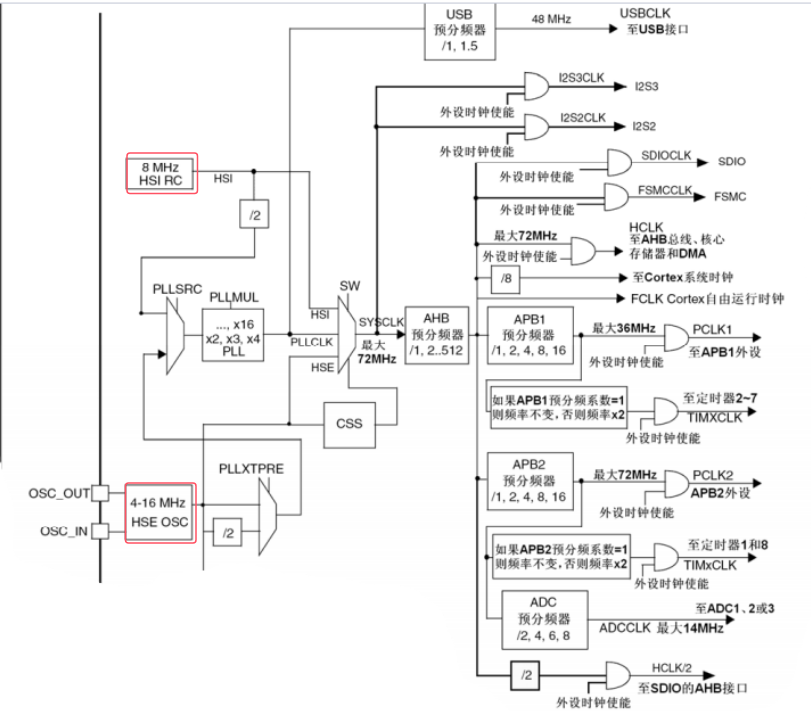

3、時鐘系統線路分析

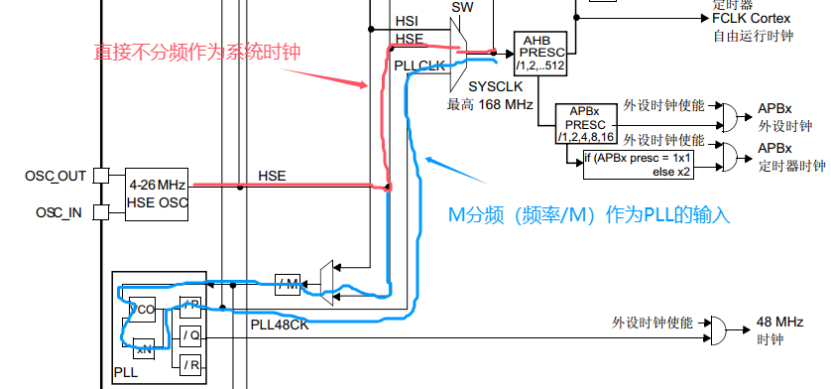

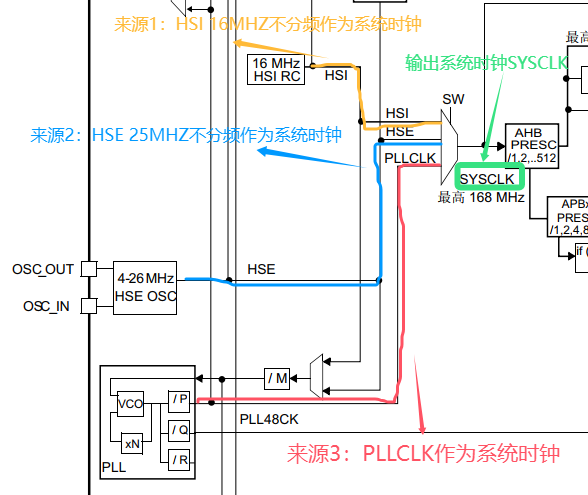

HSE時鐘

來源:無源晶振(4-26M),通常使用25M。

作用:M分頻(頻率/M)作為PLL鎖相環的輸入,還可直接不分頻作為系統時鐘

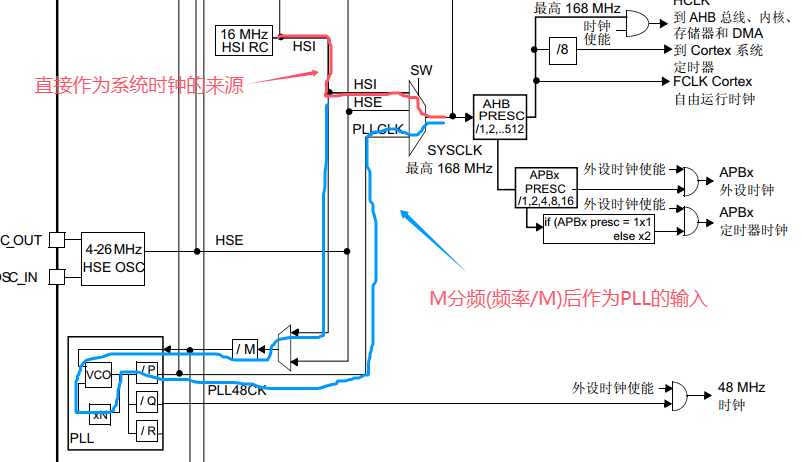

HSI時鐘

來源:芯片內部,大小為16M,當HSE故障時,系統時鐘會自動切換到HSI,直到HSE啟動成功。

作用:可直接作為系統時鐘或在M分頻后作為PLL輸入。HSI RC振蕩器能夠在不需要任何外部器件的條件下提供系統時鐘。它的啟動時間比HSE晶體振蕩器短。然而,即使在校準之后它的時鐘頻率精度仍較差

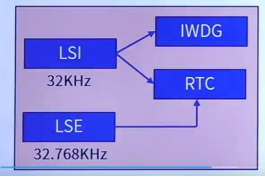

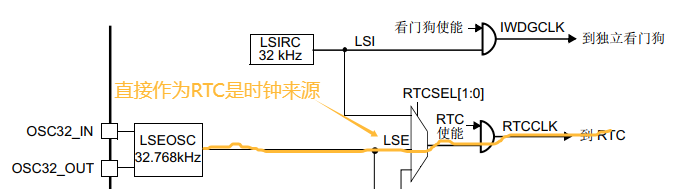

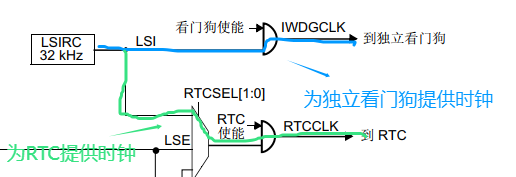

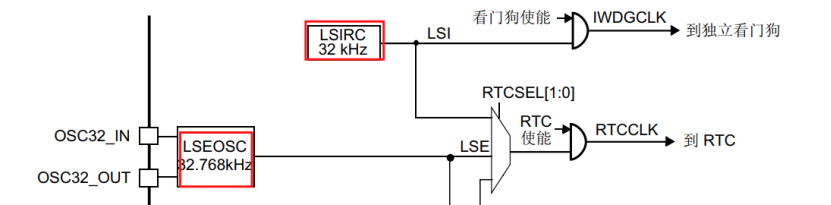

LSE時鐘

來源:芯片內部,LSE晶體是一個32.768kHz的低速外部晶體或陶瓷諧振器。它為實時時鐘或者其他定時功能提供一個低功耗且精確的時鐘源。

作用:直接作為RTC是時鐘來源

LSI時鐘

來源:內部芯片,LSI RC擔當一個低功耗時鐘源的角色,它可以在停機和待機模式下保持運行,LSI時鐘頻率大約32kHz。

作用:為獨立看門狗和自動喚醒單元(RTC)提供時鐘

?

SYSCLK ---系統時鐘

系統時鐘:SYSCLK,最高為168M(ST官方推薦的)

來源:HSI、HSE、PLLCLK。

PPLCLK ---鎖相環時鐘

來源:選擇HIS振蕩器除2或HSE振蕩器為PLL的輸入時鐘,和選擇倍頻因子,必須在其被激活前完成。一旦PLL被激活,這些參數就不能被改動。

作用:內部PLL可以用來倍頻HSI RC的輸出時鐘或HSE晶體輸出時鐘,而經過倍頻變成PLLCLK可以作為系統時鐘源

HSE輸入輸出的計算:

PPL(HSE):25Mhz ?/M分頻 * N倍頻 / ??P分頻

25Mhz ?/ ??25 ??* ?336 ??/ 2 = 168Mhz

HSI輸入輸出的計算:

PPL(HSI):25Mhz ?/M分頻 * N倍頻 / ??P分頻

PLL_M = 16

PLL_N = 336

PLL_P = 2

16Mhz ?/ ??16 ??* ?336 ??/ 2 = 168Mhz

因為基于精度和穩定性要求、同步需求、靈活性和可擴展性以及可靠性考慮等方面的原因,所以HSI一般不用,只有在HSE發生故障的時候,系統時鐘會自動切換到HSI,直到HSE啟動成功。

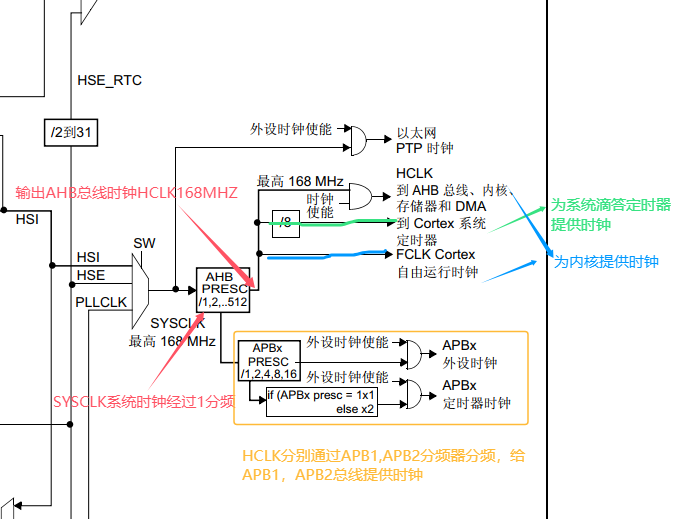

HCLK時鐘

HCLK:AHB高速總線時鐘,速度最高為168M。

作用:為AHB總線的外設提供時鐘、為Cortex系統定時器提供時鐘(SysTick)、為內核提供時鐘(FCLK)。

來源:系統時鐘分頻得到,一般設置HCLK=SYSCLK=168M

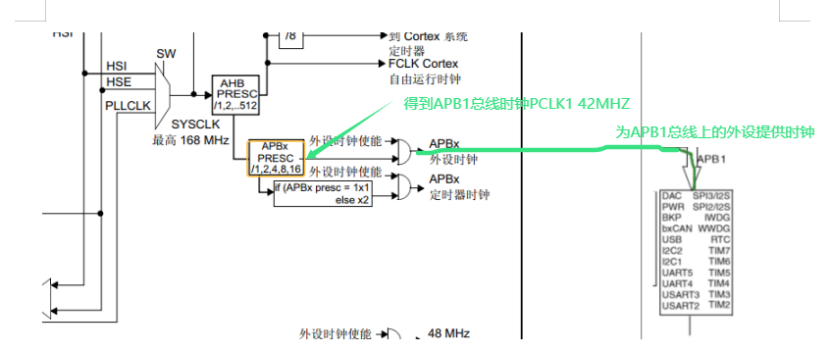

PCLK1時鐘

PCLK1:APB1低速總線時鐘,最高為42M。

作用:為APB1總線的外設提供時鐘。1或2倍頻之后則為APB1總線的定時器2~7、12~14提供時鐘

來源:HCLK分頻得到,一般配置PCLK1=HCLK/4=42M

PCLK2時鐘

PCLK2:APB2高速總線時鐘,最高為84M。

作用:為APB2總線的外設提供時鐘。為APB2總線的定時器1或8、定時器9~11提供時鐘來源:HCLK分頻得到,一般配置PCLK2=HCLK/2=84M

4、構成部分作用分析

同上STM32F03

)

)

)

)

)