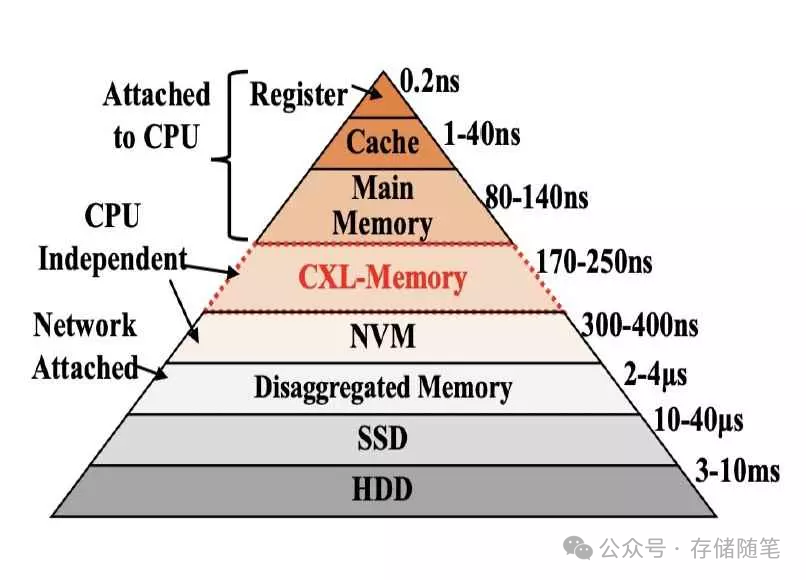

數據中心在追求更高性能和更低總擁有成本(TCO)的過程中面臨三大主要內存挑戰。首先,當前服務器內存層次結構存在局限性。直接連接的DRAM與固態硬盤(SSD)存儲之間存在三個數量級的延遲差異。當處理器直接連接的內存容量耗盡時,就必須轉向SSD,導致處理器處于等待狀態。這種等待,即延遲,對計算性能產生重大負面影響。

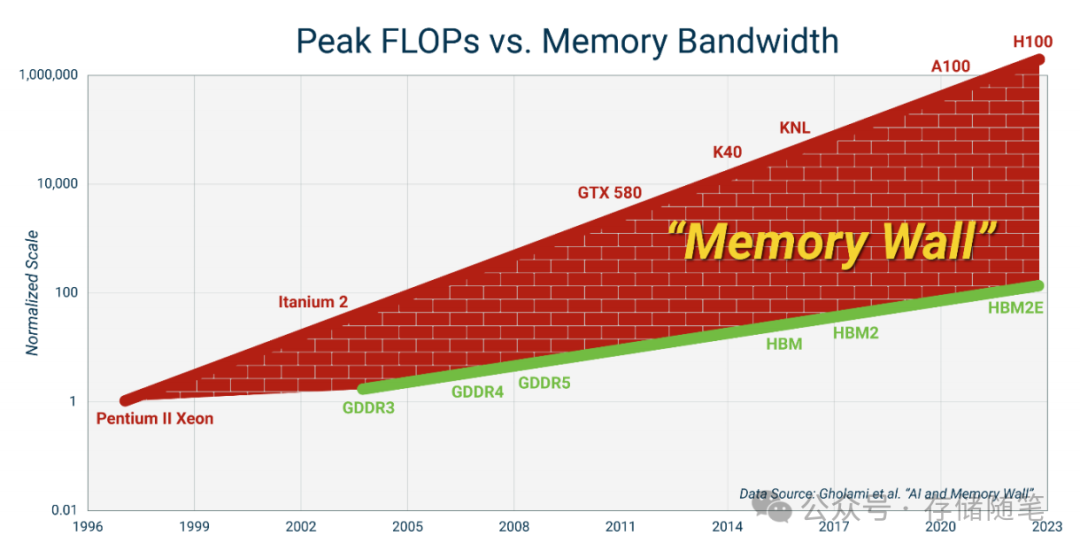

其次,多核處理器的核心數增長速度遠遠超過主內存通道的數量。這意味著超過一定數量的處理器核心會因缺乏足夠的內存帶寬而無法充分發揮效能,從而削弱了額外核心帶來的優勢,也就是出現了內存墻的問題。

高端GPU設計中,比如英偉達發布的HGXH200 GPU搭載了141GB的HBM3e內存,用于提升性能和處理大型數據集的能力,已經在一定程度上緩解了內存容量不足的問題。但,隨著加速計算的普及,即加速器配備有自己的直接連接內存,未充分利用或被閑置的內存資源問題日益凸顯。

在過去的嘗試中,面對內存墻的問題,主要遇到以下四個挑戰:

-

有限的內存帶寬和容量可擴展性:傳統內存系統在增加帶寬和容量方面面臨局限。隨著數據密集型應用需求的增長,對內存資源的消耗急劇上升,但內存技術的發展卻難以匹配這種快速增長的需求。這導致在處理大規模數據集時,系統因內存不足或數據交換速率慢而受到限制。

-

與本地內存顯著的延遲差距:當引入外部或擴展內存解決方案時,它們通常具有比直接連接在CPU上的本地內存更高的訪問延遲。這種延遲差影響了應用程序的響應時間和整體性能,特別是在那些對延遲敏感的應用場景下,如實時交易處理或高性能計算。

-

專有的系統配置和部署:早期嘗試通過定制或專有解決方案來克服內存墻,這些方案往往需要特定的硬件和軟件配置,導致部署復雜且不靈活。這種專屬性意味著升級或維護成本高,且不能輕松地跨不同平臺復用。

-

與流行應用軟件的復雜集成:為了利用新的內存技術,軟件需要進行相應的修改或優化,以便能夠有效利用擴展的內存資源。然而,這種集成工作不僅技術上復雜,還可能需要大量的開發資源和時間,特別是當涉及到已經廣泛使用的流行應用程序時,它們的代碼庫龐大且改動影響廣泛。

以往嘗試突破內存墻的努力受限于技術、成本和兼容性等多方面的難題,這些挑戰阻礙了內存系統的高效擴展和應用性能的全面提升。

為了解決這些問題,業界正積極尋求新的技術和標準,比如Compute Express Link (CXL),它旨在通過提供標準化的高速互連來提高內存帶寬、降低延遲,并簡化內存擴展的軟件集成,從而有效地打破內存墻的限制。

擴展閱讀:

-

CXL:拯救NVMe SSD緩存不足設計難題

-

如何利用CXL技術突破內存墻?

-

CXL與PCIe世界的盡頭|你相信光嗎?

-

淺析CXL P2P DMA加速數據傳輸的原理

-

下一代分層存儲方案:CXL SSD

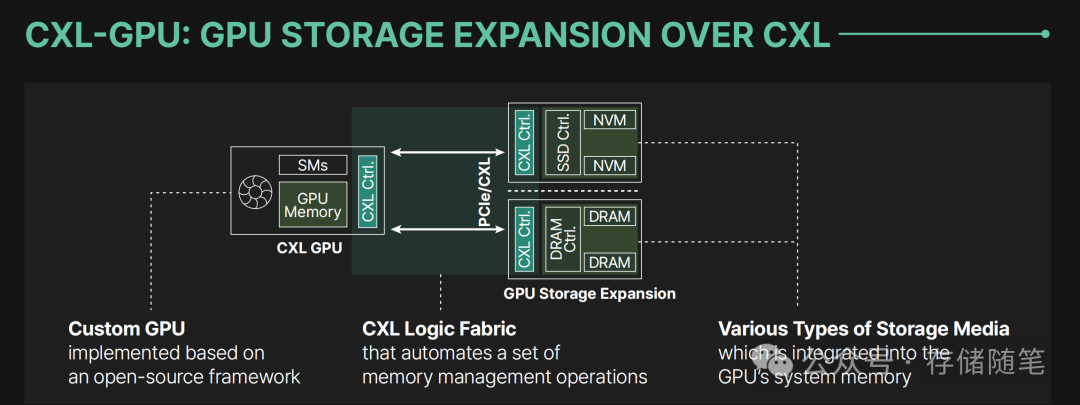

為了克服GPU內存容量限制,同時盡量減少性能損失,韓國一家公司Panmnesia提出了一項基于CXL技術的GPU存儲擴展方案。

Panmnesia是一家在內存擴展和計算加速技術方面走在前列的創新型企業,其解決方案對于推動AI、云計算和高性能計算等領域的發展具有重要意義。通過不斷技術創新和優化,Panmnesia正努力將CXL技術推向新的高度,為全球的系統開發商和制造商提供高性能、低成本的內存擴展解決方案。

-

端點(Endpoints, EPs):在CXL架構中,EPs可以是各種類型的存儲設備,包括基于非易失性存儲器(NVM)的固態硬盤(SSDs)和DRAM。這些設備通過CXL接口直接與計算單元通訊,降低了訪問延遲,提升了數據傳輸速率。

-

計算單元訪問:CXL允許GPU或其他計算單元如同訪問本地內存一樣,直接通過標準的加載/存儲指令來讀寫這些外掛的存儲設備,從而避免了通過CPU和系統內存作為中介的傳統做法,減少了數據搬運的開銷和延遲。

-

異步通信機制:CXL的異步通信特性為數據密集型應用提供了重要優勢,特別是在深度學習、大規模數據分析等場景下,能夠更加高效地管理數據流,減少等待時間,提升整體計算效率。

-

內存空間映射:CXL通過PCIe物理層,將EPs映射到主機的內存空間中,使得這些存儲資源對計算單元來說就像是擴展的系統內存,簡化了編程模型,便于軟件層面的利用和管理。

Panmnesia公司突破性地開發出了全球首款實現兩位數納秒級往返延遲的CXL控制器,這一創新直接回應了GPU存儲擴展領域的一項重大挑戰。當前,GPU內部缺乏原生支持CXL邏輯結構和子系統的機制,無法直接將DRAM或SSD作為端點(EPs)來擴展內存。為此,Panmnesia填補了市場空白,設計了一系列至關重要的硬件層級,這些層級全面支持CXL的所有關鍵子協議,并將它們整合進了一個統一的控制器之中。

Panmnesia的創新之處

Panmnesia研發的CXL控制器,憑借其獨特的低延遲CXL IP,解決了內存擴展中的一大難題——延遲。公司成功開發并完成了CXL控制器IP的硅片制造過程,確保所有CXL通信操作均能在極低的延遲下執行。這一控制器展現出了兩位數納秒級的往返延遲,這是迄今為止報道中最快的。

通過優化物理層、鏈接層和事務層的操作,Panmnesia的CXL控制器能夠應用于包括CPU、交換機、加速器和內存擴展器在內的多種系統設備,自動化加速內存管理操作。這樣,用戶可以在保證性能損失最小化的同時,實現理想的內存擴展方案,降低TCO。

Panmnesia CXL IP控制器技術亮點

-

先進制程技術:展示了控制器的硅片布局,采用了臺積電(TSMC)的先進技術進行制造。這意味著控制器不僅在技術上處于前沿,還具備高性能和低功耗的特性。

-

全面協議兼容:該CXL控制器設計符合CXL 3.1標準,同時向下兼容CXL 2.0和1.1版本,保證了其在不同平臺上的廣泛適用性。

-

低延遲性能:經過嚴格測試,控制器實現了兩位數納秒級別的往返延遲,這一成績包括了標準內存操作與CXL數據包(flit)傳輸間的協議轉換時間。這樣的低延遲對于高性能計算和實時數據處理至關重要。

-

硬件集成驗證:控制器不僅在硬件RTL上被成功集成到內存擴展器中,還在GPU和CPU的原型設計中進行了驗證,展現了其在多樣化計算硬件環境下的高效能與高兼容性。

性能對比分析

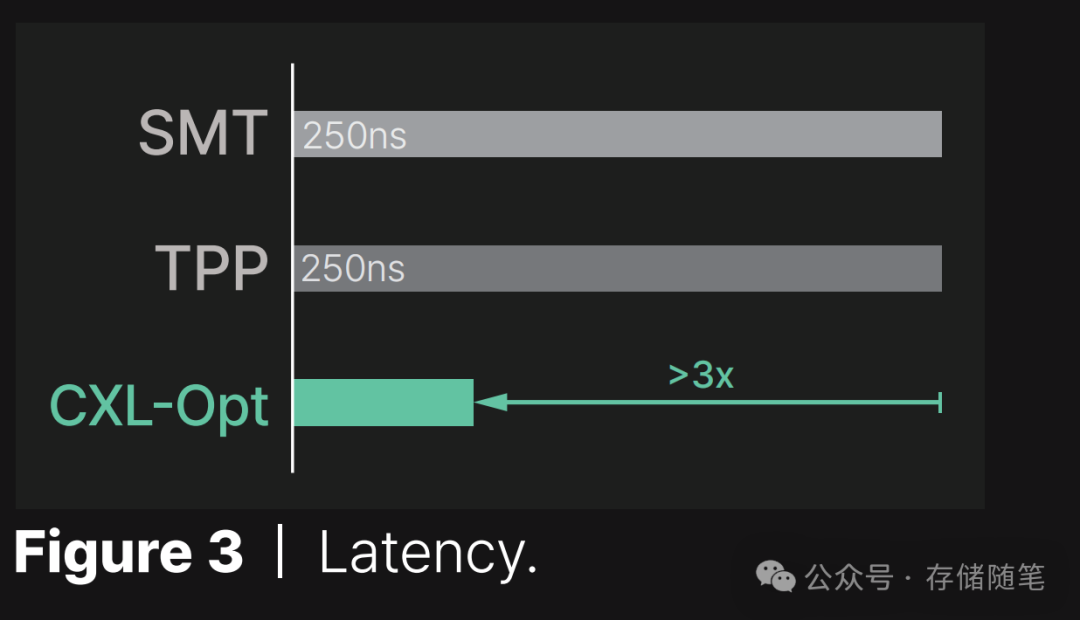

為了更好地說明其技術優勢,Panmnesia將自家CXL控制器(CXL-Opt)的往返延遲與市場上其他兩款解決方案SMT5和TPP6進行了比較。結果顯示,CXL-Opt控制器的延遲至少比SMT和TPP快3倍(具體數字還未公開)。盡管關于SMT和TPP的具體硅片信息并未公開,但據推測它們可能是基于PCIe架構。相比之下,Panmnesia的CXL控制器從物理層到鏈路層,再到事務層,都針對CXL進行了全方位的優化,這解釋了其顯著的性能優勢。

在設計和集成GPU架構以開發用于存儲擴展的EP設備時,Panmnesia采取了一種創新策略,將CXL控制器的功能與內存/SSD控制器的功能相結合。這一結合使得CXL控制器能夠將其后端存儲空間擴展到主機系統中,這部分被定義為主機管理的設備內存(HDM)。然而,與GPU架構的集成面臨著獨特的挑戰,因為EP需要被GPU的緩存系統識別。與常規EP直接對接的方式不同,這種情況需要更精細的設計。

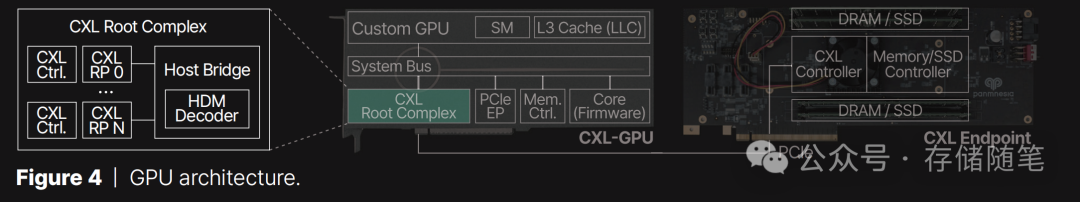

為了解決這些挑戰,Panmnesia設計了一個特殊的CXL RC,它配備了一個帶有多個RP的主機橋接器。下圖左側展示了這一配置,其中主機橋接器一側連接到系統總線端口,另一側則連接多個CXL根端口。這一設置的關鍵組件之一是一個HDM解碼器,負責管理每個根端口的系統內存地址范圍,即主機物理地址(HPA)。這些根端口設計靈活,可以通過PCIe連接支持DRAM或SSD EP。

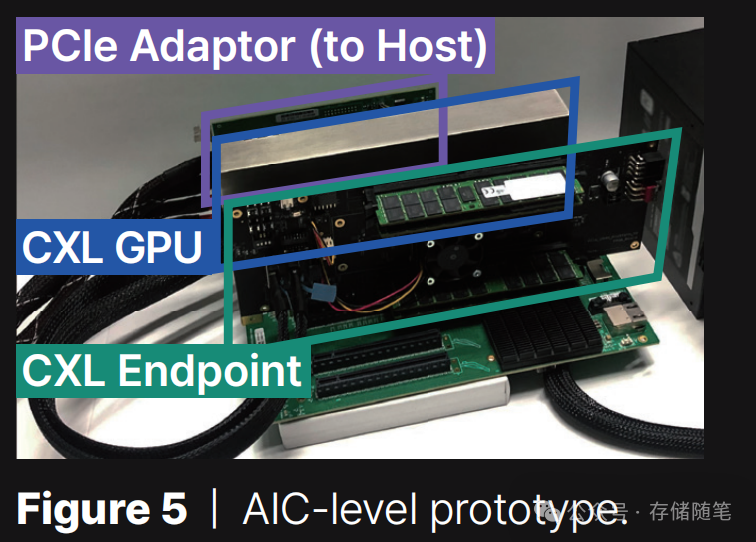

將CXL RC嵌入到Panmnesia基于開源框架定制的GPU架構中,該定制GPU專門設計以優化CXL功能的集成,確保與CXL控制器和EP設備的無縫協作。為了實現這一高度集成的系統,包括定制GPU和EP設備,Panmnesia利用了基于7納米FPGA的定制AIC卡,如下圖所示。這一FPGA平臺不僅提供了快速原型設計和驗證的途徑,還允許高度的硬件靈活性和可編程性,從而適應未來可能的升級和優化。

Panmnesia的GPU架構設計和集成方案通過創新地融合CXL控制器與內存/SSD控制器功能,創建了一個高度優化的系統,該系統不僅解決了與GPU緩存系統兼容的問題,還通過一個靈活且高效的CXL RC設計,實現了對不同類型EP設備的支持。這一方案利用先進的FPGA技術實現,展示了面向未來的大規模深度學習和高性能計算應用的內存擴展解決方案。

Panmnesia在解決大型數據處理挑戰方面,對比了三種不同的GPU系統配置,以評估它們在提高存儲容量和效率方面的效果。這三種配置分別是:

-

UVM(Unified Virtual Memory): UVM技術通過在CPU和GPU間共享統一虛擬地址空間,允許兩者通過共享指針訪問數據。盡管此方法簡化了內存管理,但在處理GPU頁面錯誤時,必須依靠主機運行時軟件進行干預,這導致了較高的延遲和性能開銷。UVM以頁面而非緩存行粒度遷移數據,經常導致數據傳輸量超出GPU實際需求。

-

CXL-Proto: 通過采用三星和Meta報告中提及的CXL端點原型,將CXL技術應用于GPU存儲擴展,實現了250納秒的延遲。雖然相比UVM有所改進,但仍有優化空間。

-

CXL-Opt: 同樣基于CXL技術進行GPU存儲擴展,但采用了Panmnesia自主研發的CXL控制器,該控制器實現了兩位數納秒級的往返延遲,并引入了額外的優化措施以減少讀寫延遲。這是目前性能最佳的解決方案。

性能評估

-

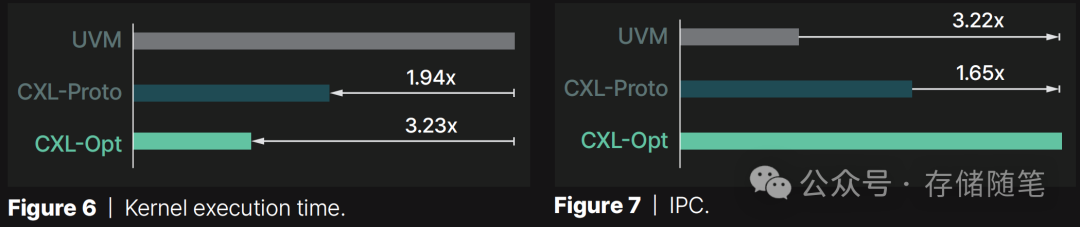

執行時間:通過比較三種配置在不同GPU內核上的執行時間,并以UVM為基準進行歸一化,結果顯示UVM的性能在所有測試中表現最差,這主要歸因于處理GPU頁面錯誤時主機運行時的干預開銷。CXL-Proto通過允許GPU直接通過加載/存儲指令訪問擴展存儲,避免了上述問題,使得執行時間比UVM縮短1.94倍。而CXL-Opt進一步優化,使用了低延遲的CXL控制器,執行時間比UVM縮短3.23倍。

-

每周期指令數(IPC):IPC值是衡量處理器效率的重要指標,表示每個時鐘周期內完成的指令數量。在這個指標上,CXL-Opt相對于UVM和CXL-Proto分別展現出3.22倍和1.65倍的性能提升,進一步證明了其在提升GPU計算效率方面的顯著效果。

這一創新的CXL控制器不僅解決了GPU內存擴展的迫切需求,也為AI、高性能計算及大數據處理等內存密集型應用提供了強大的支持。通過實現超低延遲的內存訪問,Panmnesia的解決方案有望大幅提升系統的整體性能和效率,降低數據傳輸瓶頸,進而推動相關行業技術的進一步發展。此外,其全面的兼容性和高度優化的設計,為未來CXL技術在更廣泛領域的應用奠定了堅實的基礎。

另外,Panmnesia的CXL-GPU技術將在即將7月份于美國加州圣克拉拉舉辦的USENIX會議和ACM HotStorage活動中展示,具體細節預計會有更多的展示,小編持續關注中!

參考文獻:https://panmnesia.com/#solution

如果您看完有所受益,歡迎點擊文章底部左下角“關注”并點擊“分享”、“在看”,非常感謝!

精彩推薦:

-

萬字長文|下一代系統內存數據加速接口SDXI解讀

-

數據中心:AI范式下的內存挑戰與機遇

-

WDC西部數據閃存業務救贖之路,會成功嗎?

-

屬于PCIe 7.0的那道光來了~

-

深度剖析:AI存儲架構的挑戰與解決方案

-

淺析英偉達GPU NCCL P2P與共享內存

-

3D NAND原廠:哪家芯片存儲效率更高?

-

大廠阿里、字節、騰訊都在關注這個事情!

-

磁帶存儲:“不老的傳說”依然在繼續

-

淺析3D NAND多層架構的可靠性問題

-

SSD LDPC軟錯誤探測方案解讀

-

關于SSD LDPC糾錯能力的基礎探究

-

存儲系統如何規避數據靜默錯誤?

-

PCIe P2P DMA全景解讀

-

深度解讀NVMe計算存儲協議

-

淺析不同NAND架構的差異與影響

-

SSD基礎架構與NAND IO并發問題探討

-

字節跳動ZNS SSD應用案例解析

-

CXL崛起:2024啟航,2025年開啟新時代

-

NVMe SSD:ZNS與FDP對決,你選誰?

-

淺析PCI配置空間

-

淺析PCIe系統性能

-

存儲隨筆《NVMe專題》大合集及PDF版正式發布!

—Vue 3自定義指令的藝術:實戰中的最佳實踐)

![[我靠升級逆襲成為大師]韓漫日漫無刪減完整版,免費在線觀看漫畫](http://pic.xiahunao.cn/[我靠升級逆襲成為大師]韓漫日漫無刪減完整版,免費在線觀看漫畫)

:Nuitka庫)