系列文章目錄

文章目錄

- 系列文章目錄

- 前言

- 一、晶振主要參數

- 二、有源與無源區別

- 三、無源晶振

- 四、有源晶振

- 總結

前言

在硬件電路的設計中,晶振電路是必不可少的,它充當了整個電路心臟的作用。在這個晶振電路的設計中負載電容、電阻參數的選型是很重要的,選型失敗不僅會波形失真,嚴重的芯片都無法工作。本文將從實驗出發給出一種通用的配置。

一、晶振主要參數

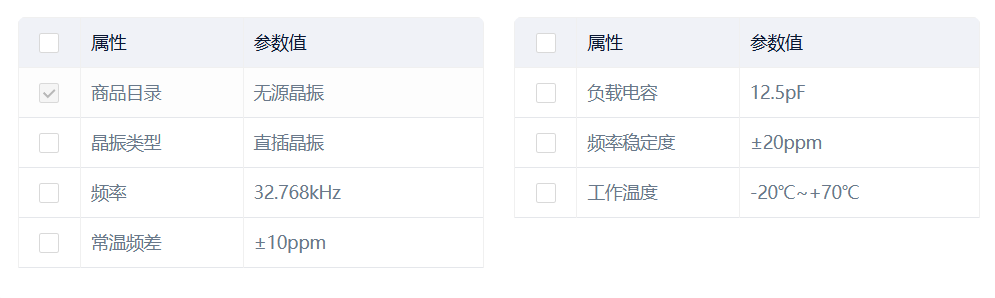

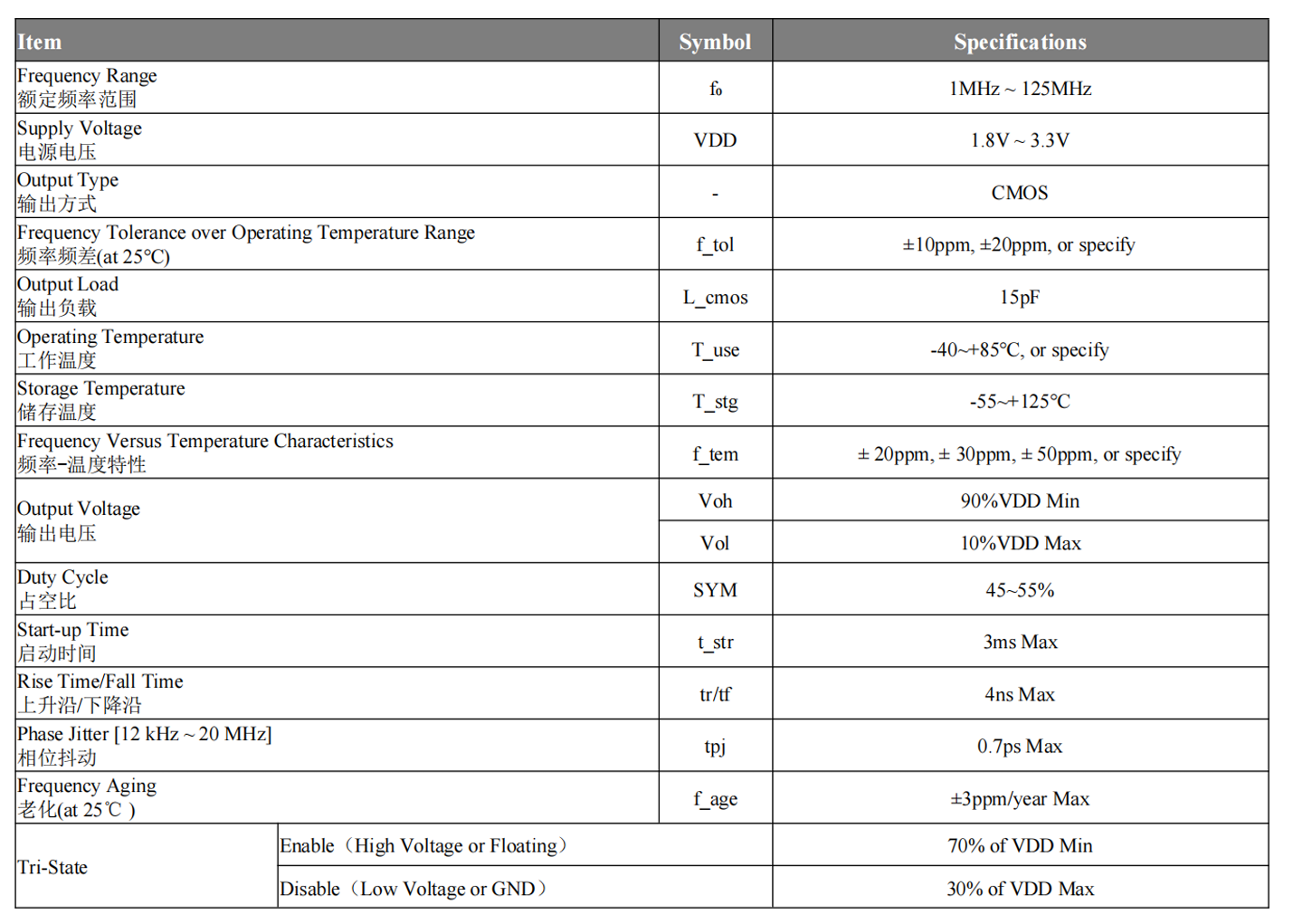

對于一款晶振主要參數如下

常溫頻差±10ppm

ppm 是 “parts per million” 的縮寫,意為 “百萬分之一”。在晶振參數中,±10ppm 表示在規定的工作溫度范圍內晶振的實際輸出頻率與標稱頻率之間的偏差范圍,不超過標稱頻率的百萬分之十。

若標稱頻率為 1MHz(1,000,000Hz),則頻率偏差范圍為 ±10Hz(1,000,000×10/1,000,000),實際頻率在 999,990Hz 到 1,000,010Hz 之間。

負載電容12.5pF

負載電容(Load Capacitance,通常用CL表示)是指晶振在振蕩電路中,從晶振兩端看進去的總等效電容值(單位為皮法 pF)。它并非晶振自身的電容,而是由電路中外部電容(如振蕩電路的匹配電容)、分布電容(PCB 布線、元件引腳等寄生電容)共同構成的總電容。12.5pF 表示該晶振正常工作時,需要外部電路提供的總等效負載電容為 12.5pF。

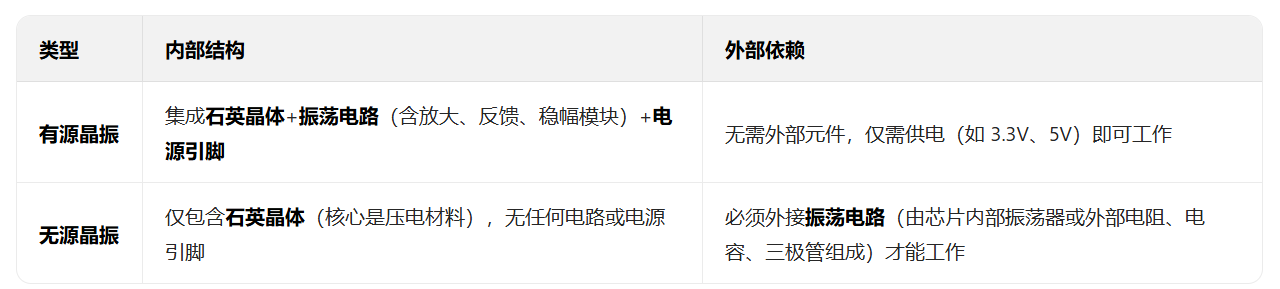

二、有源與無源區別

晶振分為有源和無源兩種,區別如下

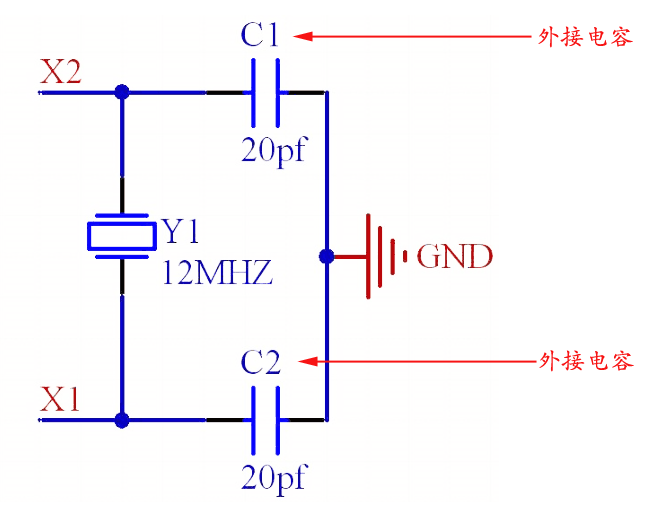

三、無源晶振

無源晶振一般是兩個引腳,無方向之分,兩個引腳接入芯片的OSC_IN與OSC_OUT引腳就可以工作了。一般電路設計如圖所示。

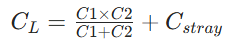

按前面介紹可得出外接電容(通常為兩個對稱的電容,C1 和 C2)來匹配 12.5pF 的負載電容,公式如下:

其中,Cstray 為分布電容(通常約 2~5pF,由 PCB 布線決定)。C1=C2從而能計算出C1=C2≈20pF。

一般無源晶振的產生的波形大多為三角波,頻率準確性有限,所有對于精密電路都是使用有源晶振。

四、有源晶振

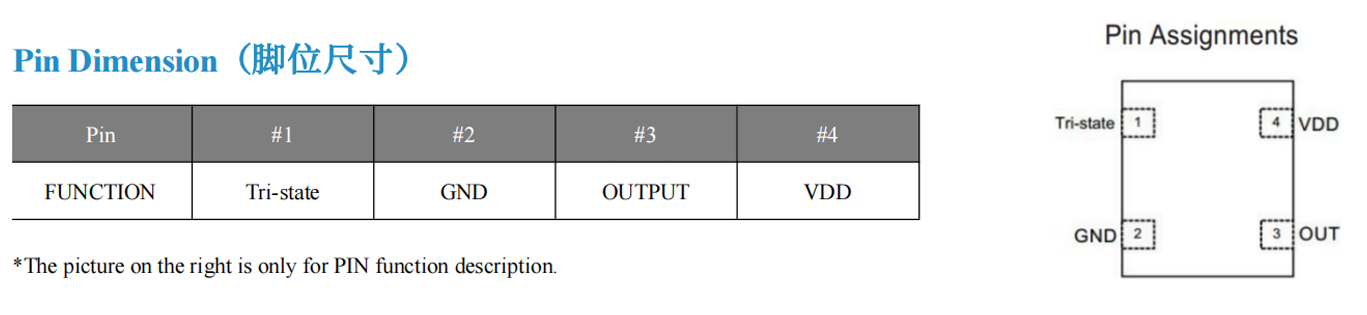

?有源晶振一般是4個引腳,大多是表貼型,如圖

其中的Tri-state是使能引腳,接高電平或高阻態輸出波形,接低電平不輸出波形,一般不適應,設計中保持懸空(高阻態)。

其中的Tri-state是使能引腳,接高電平或高阻態輸出波形,接低電平不輸出波形,一般不適應,設計中保持懸空(高阻態)。

OUTPUT就是波形輸出引腳,設計中該引腳接入芯片的OSC_IN,芯片的OSC_OUT懸空。

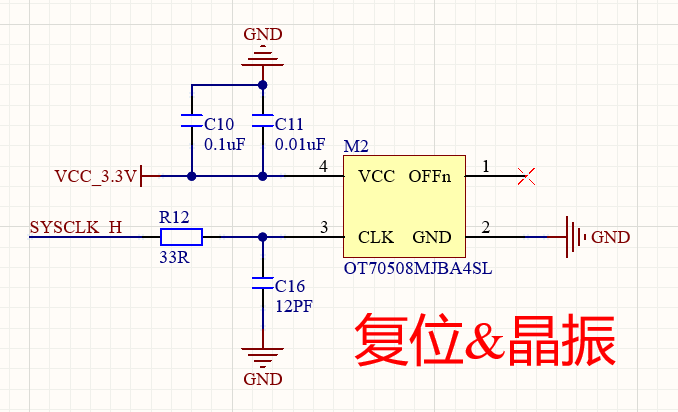

設計如圖所示

其中的C16就是CL(負載電阻),R12為負載電容,有源晶振無需電容并聯,直接CL=C16+Cstray即可。

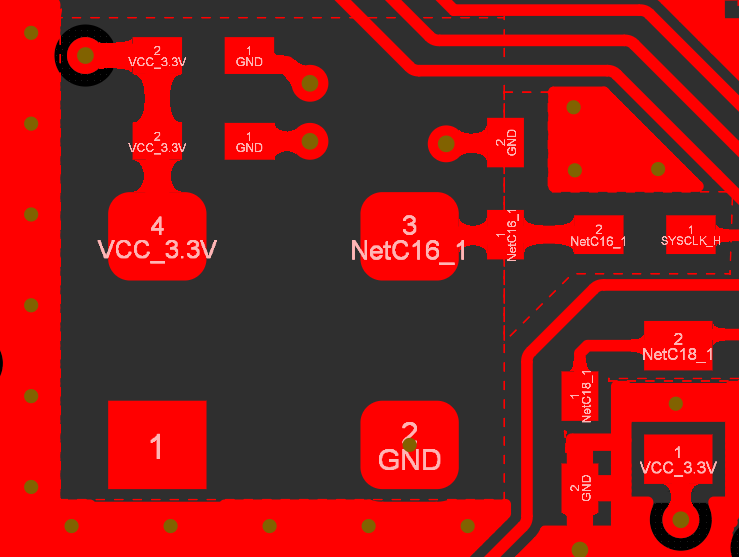

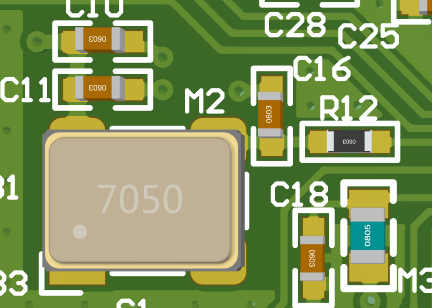

AD電路設計如圖,頂層晶振電路周圍圍繞地銅,四周打上過孔與內電層或底層地銅形成良好連接,晶振電路內部不要鋪銅,避免干擾高頻電路,晶振電路底下(內電層或底層)最好的鋪滿大片銅皮,形成良好的電磁屏蔽。另外最好不要在晶振電路的內部和底下走線,保持銅片連續和避免信號干擾。

這是該電容的具體參數圖

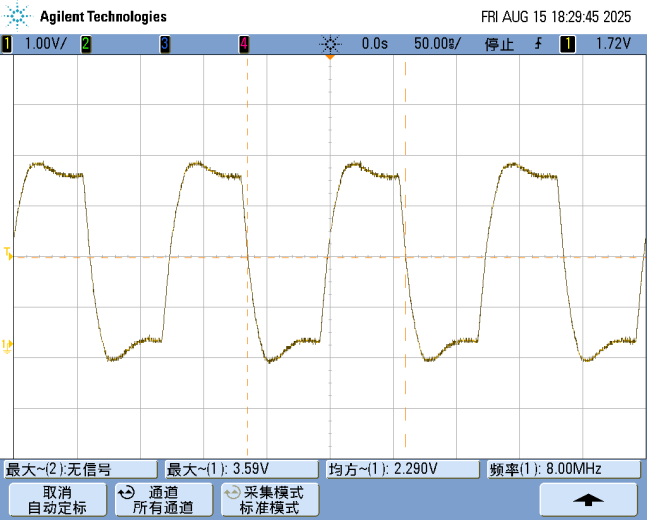

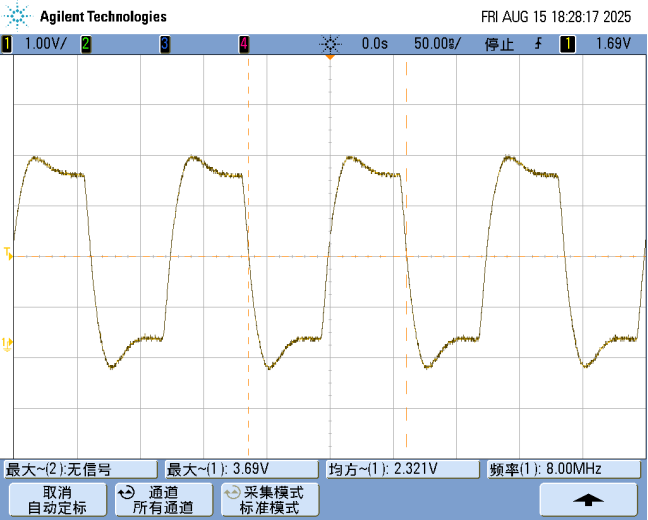

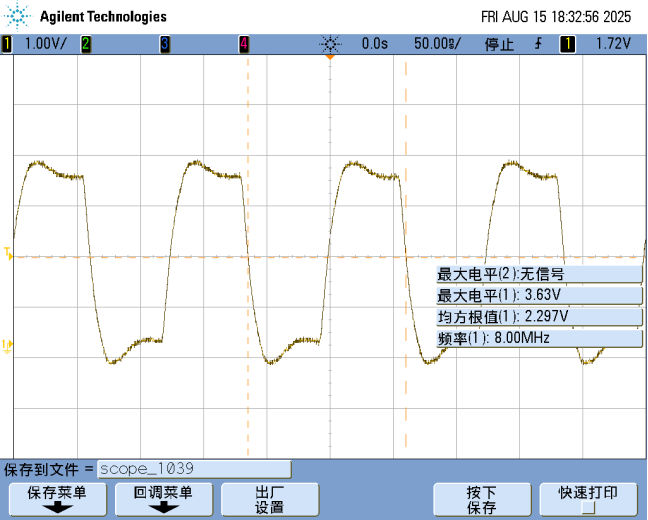

下面按照該電路設計,改變C16和R12的值,依靠示波器尋找最合適的搭配,大家可以仔細對比。

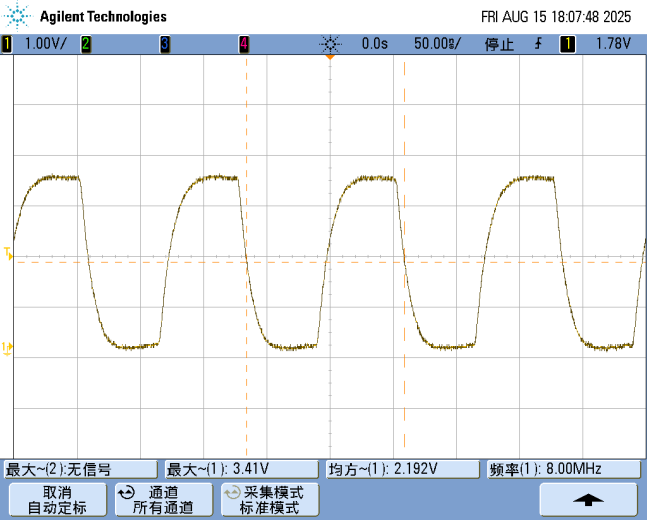

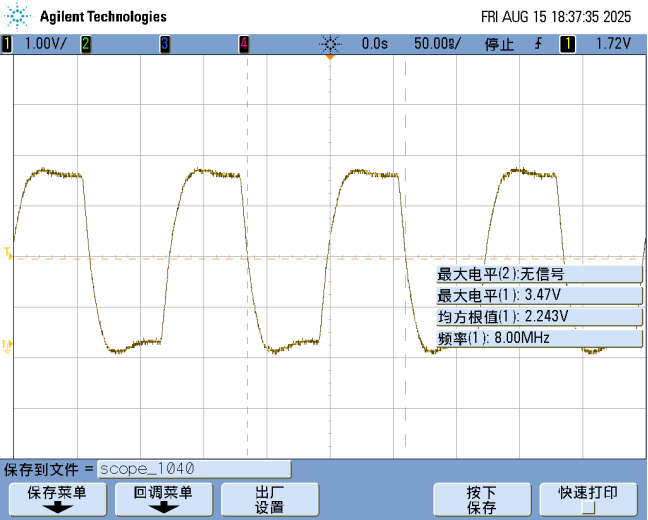

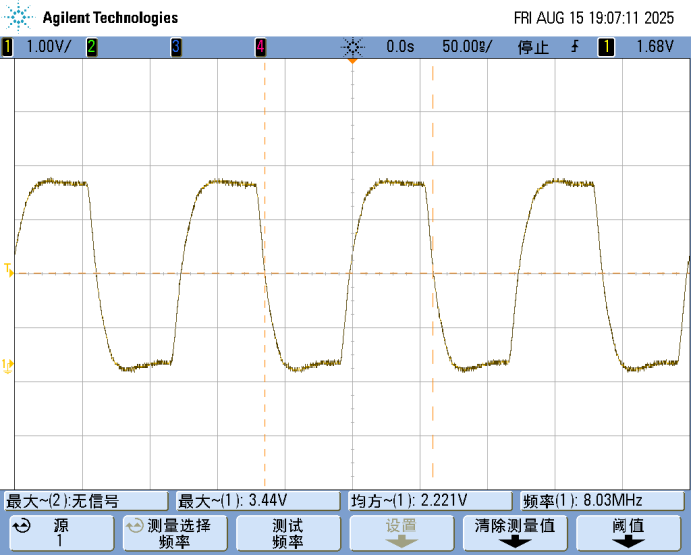

負載電容0PF、負載電阻0R

負載電容12PF、負載電阻0R

負載電容15PF、負載電阻0R

負載電容12PF、負載電阻33R

負載電容15PF、負載電阻10R

負載電容15PF、負載電阻20R

最后我選擇了C16=15PF,R12=20R的設計,因為比較之下這是在上升時間短的要求下幾乎無超調的一款設計,最貼近理論方波。

總結

可以看出因為有源晶振自身具有起振電路在負載匹配的要求上不是那么苛刻,上面所有的波形都可以滿足驅動芯片運行,可以按照我的設計圖,查晶振手冊,負載電容和手冊規格相等或低幾PF,復雜電阻保持為20R,這樣幾乎可以使用絕大多數硬件設備的時鐘頻率要求了。在設計時也盡可能的選擇有源晶振。

多說一句,一般MCU內部也具有內部晶振,不過要說的是這個內部晶振頻率非常不準,如果使用內部晶振會導致USART通訊失敗,這種失敗還不好察覺,因為失敗的原因是時鐘不準導致的波特率和設定的不符,從而收到亂碼,盡量不要使用內部晶振工作。

|輕量化 MobileNetV2 高光譜分類)

的進化之路)

)

)