目錄

- 1、前言:SRIO在FPGA+DSP架構中的作用

- 工程概述

- 免責聲明

- 2、相關方案推薦

- 我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

- 我這里已有的FPGA+DSP異構方案

- 我這里已有的 GT 高速接口解決方案

- 3、工程詳細設計方案

- 工程設計原理框圖

- FPGA端工程源碼

- FPGA端SRIO從設備(Target)

- FPGA端SRIO請求響應事務模塊

- DSP端工程

- 4、工程源碼1詳解:FPGA邏輯工程

- 5、工程源碼2詳解:DSP裸機工程

- 6、工程源碼3詳解:DSP RTOS系統工程

- 7、工程移植說明

- vivado版本不一致處理

- FPGA型號不一致處理

- 其他注意事項

- 8、上板調試驗證

- 準備工作

- 程序下載bit

- DSP裸機工程測試

- DSP RTOS系統工程測試

- 9、工程代碼獲取

FPGA實現SRIO高速接口與DSP交互,FPGA+DSP異構方案,提供3套工程源碼和技術支持

1、前言:SRIO在FPGA+DSP架構中的作用

SRIO簡介:

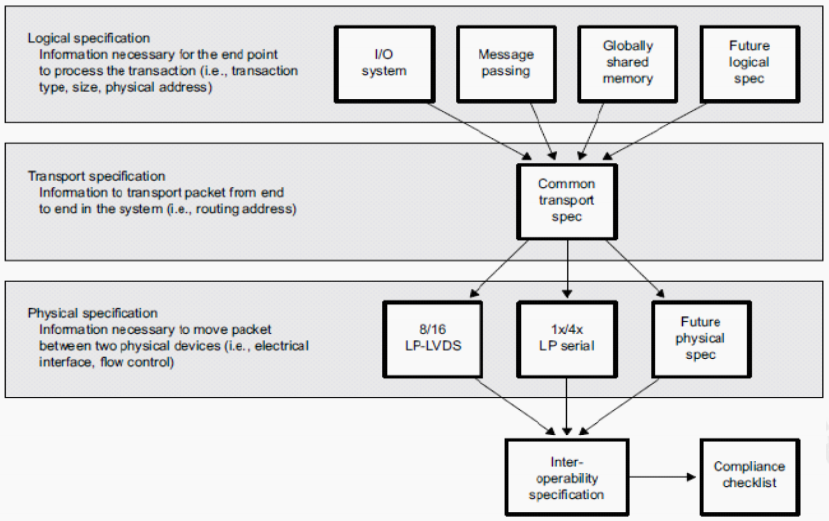

RapidIO 是由 Motorola 和 Mercury 等公司率先倡導的一種高性能、 低引腳數,基于數據包交換的互連體系結構,是為滿足高性能嵌入式系統需求而設計的一種開放式互連技術標準;SRIO 包含三層結構協議,即物理層、傳輸層、邏輯層,SRIO體系結構如下:

邏輯層:定義包的類型、大小、物理地址、傳輸協議等必要配置信息。

傳輸層:定義包交換、路由和尋址規則,以確保信息在系統內正確傳輸。

物理層:包含設備級接口信息,如電氣特性、錯誤管理數據和基本流量控制數據等信息。

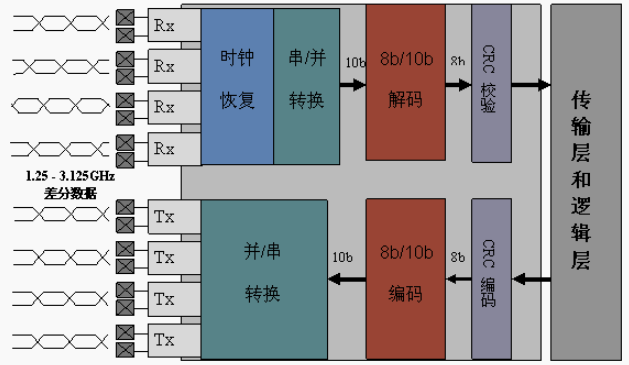

SRIO收發邏輯框圖如下:

SRIO(Serial RapidIO)在FPGA+DSP異構架構中扮演著高速數據通道與系統互連核心的角色,其作用與優勢主要體現在以下方面:

SRIO的核心作用

1、高速數據通道

實時數據傳輸:FPGA負責前端數據采集(如雷達回波、圖像信號),通過SRIO將原始數據直接傳輸至DSP處理,速率可達 8-10 Gbps(實測效率>80%理論值)。

低延遲交互:點對點傳輸延遲僅微秒級,滿足實時處理需求(如電機控制、雷達成像)。

2、直接內存訪問(DMA)

DSP可通過SRIO直接讀寫FPGA的片上存儲或外掛DDR,無需CPU干預。例如:

SWRITE事務實現零開銷突發傳輸,效率達95%以上。

FPGA作為協處理器時,DSP直接獲取處理結果(如濾波后圖像)。

3、可靠消息通知

門鈴(Doorbell)中斷:DSP向FPGA發送16位輕量級消息,觸發實時響應(如任務啟動/停止)。

中斷延遲<1μs,優于傳統GPIO。

4、系統級擴展性

通過SRIO交換器連接多DSP/FPGA,構建分布式計算網絡(如4個DSP+FPGA的基帶處理卡)。

支持動態路由與多播傳輸,適應復雜拓撲。

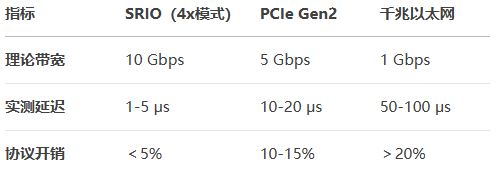

SRIO的技術優勢

1、高帶寬與低延遲

2、硬件級可靠性

錯誤檢測與重傳:內置CRC校驗與鏈路層重傳機制,誤碼率<10?12。

路徑冗余:支持多路徑備份,單點故障不影響系統運行(關鍵用于航天電子)。

3、靈活的協議支持

傳輸模式:

Direct I/O:直接存儲映射(NWRITE/NREAD),適合大數據塊傳輸。

Message Passing:信箱機制,支持復雜命令交互(如FPGA向DSP發送狀態報告)。

物理層適配:支持1x/2x/4x鏈路聚合,兼容背板(VPX)、光模塊等連接方式。

4、低功耗設計

相比PCIe,SRIO功耗低30-40%(實測1.5W@5Gbps)。

靜態功耗<0.1W,適合電池供電設備(如無人機雷達)。

典型應用場景

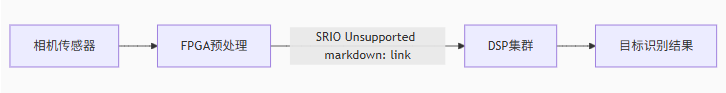

1、實時圖像處理系統

FPGA完成像素校正,DSP執行AI識別,傳輸延遲<10ms

2、無線通信基帶

FPGA處理ADC采樣數據,經SRIO分發至多DSP核(如LDPC解碼)。

支持5G Massive MIMO的μs級波束成型。

3、高可靠性系統

航天器中的FPGA+DSP通過SRIO互連,抗輻射設計(如三模冗余)確保太空環境下的數據傳輸

總結

SRIO在FPGA+DSP架構中的核心價值是:

? 突破總線瓶頸:提供>8Gbps的穩定帶寬,替代共享總線。

? 實現異構協同:FPGA并行預處理 + DSP復雜算法,通過SRIO無縫銜接。

? 構建高可靠網絡:冗余鏈路與硬件校驗機制,滿足軍工/航天級需求

工程概述

本文詳細描述了Xilinx的7系列FPGA實現FPGA實現SRIO高速接口與DSP交互;以下從FPGA工程和DSP工程兩個方向描述整個設計:

FPGA工程

FPGA工程調用Xilinx官方的SRIO IP核實現SRIO協議的物理層、傳輸層、邏輯層,作為SRIO的從設備(target),SRIO IP核留出了用戶邏輯接口,用戶只需要寫自己的邏輯電路與之對接即可完成SRIO通信;本設計只做簡單的數據緩存和讀寫,所以用戶邏輯為純verilog代碼實現的請求響應事務模塊,模塊例化了兩個RAMB36SDP的BRAM原語用戶數據讀寫的緩存(4K Byte),為接收到的請求事務生成對應的響應事務,該模塊參考了Xilinx官方SRIO IP核的仿真工程,根據請求-響應機制構造HELLO數據包,并根據讀寫地址操作BRAM以實現基于SRIO協議的數據收發架構;

DSP工程

DSP工程實現 DSP作為SRIO主設備(Initiator),通過SRIO總線與遠程設備通信,進行高速數據傳輸測試。核心功能包括SRIO子系統初始化與鏈路建立、NWRITE/SWRITE寫操作性能測試、NREAD讀操作與數據完整性驗證、傳輸速率實時統計與錯誤檢測等,DSP工程分為裸機工程和RTOS系統工程,裸機工程不帶操作系統,實時性更好,RTOS系統工程帶輕量版RTOS操作系統,穩定性更好,測試結果通過串口打印觀察;

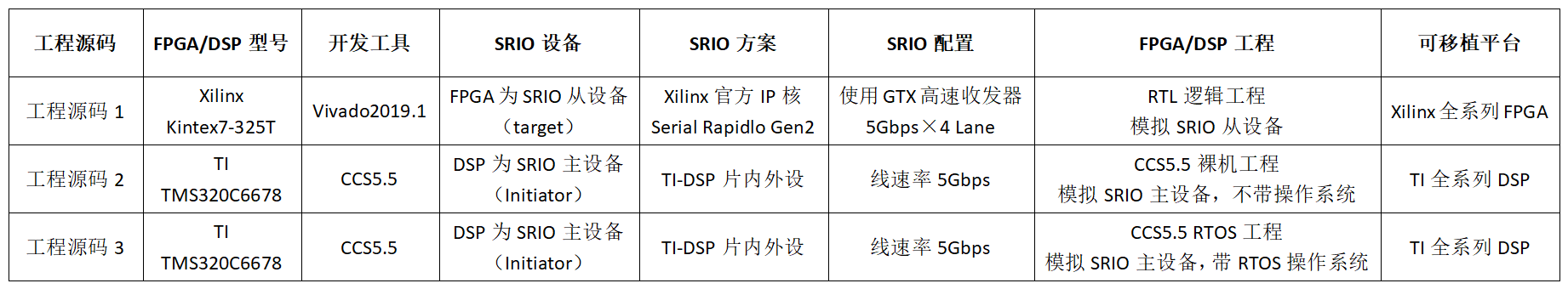

針對市場主流需求,本博客提供3套工程源碼,具體如下:

現對上述3套工程源碼做如下解釋,方便讀者理解:

工程源碼1

開發板FPGA型號為Xilinx公司的XC7K325T-2FFG676I;FPGA工程調用Xilinx官方的SRIO IP核實現SRIO協議的物理層、傳輸層、邏輯層,作為SRIO的從設備(target),SRIO IP核留出了用戶邏輯接口,用戶只需要寫自己的邏輯電路與之對接即可完成SRIO通信;本設計只做簡單的數據緩存和讀寫,所以用戶邏輯為純verilog代碼實現的請求響應事務模塊,模塊例化了兩個RAMB36SDP的BRAM原語用戶數據讀寫的緩存(4K Byte),為接收到的請求事務生成對應的響應事務,該模塊參考了Xilinx官方SRIO IP核的仿真工程,根據請求-響應機制構造HELLO數據包,并根據讀寫地址操作BRAM以實現基于SRIO協議的數據收發架構;

工程源碼2

開發板DSP型號為TI公司的TMS320C6678;DSP工程實現 DSP作為SRIO主設備(Initiator),通過SRIO總線與遠程設備通信,進行高速數據傳輸測試。核心功能包括SRIO子系統初始化與鏈路建立、NWRITE/SWRITE寫操作性能測試、NREAD讀操作與數據完整性驗證、傳輸速率實時統計與錯誤檢測等,本套工程為CCS 裸機工程,不帶操作系統,實時性更好,測試結果通過串口打印觀察;

工程源碼3

開發板DSP型號為TI公司的TMS320C6678;DSP工程實現 DSP作為SRIO主設備(Initiator),通過SRIO總線與遠程設備通信,進行高速數據傳輸測試。核心功能包括SRIO子系統初始化與鏈路建立、NWRITE/SWRITE寫操作性能測試、NREAD讀操作與數據完整性驗證、傳輸速率實時統計與錯誤檢測等,本套工程為CCS RTOS工程,帶RTOS操作系統,穩定性更好,測試結果通過串口打印觀察;

本文詳細描述了FPGA實現SRIO高速接口與DSP交互的設計方案,工程代碼可綜合編譯上板調試,可直接項目移植,適用于在校學生、研究生項目開發,也適用于在職工程師做項目開發,可應用于醫療、軍工等行業的高速接口領域;

提供完整的、跑通的工程源碼和技術支持;

工程源碼和技術支持的獲取方式放在了文章末尾,請耐心看到最后;

免責聲明

本工程及其源碼即有自己寫的一部分,也有網絡公開渠道獲取的一部分(包括CSDN、Xilinx官網、Altera官網等等),若大佬們覺得有所冒犯,請私信批評教育;基于此,本工程及其源碼僅限于讀者或粉絲個人學習和研究,禁止用于商業用途,若由于讀者或粉絲自身原因用于商業用途所導致的法律問題,與本博客及博主無關,請謹慎使用。。。

2、相關方案推薦

我已有的所有工程源碼總目錄----方便你快速找到自己喜歡的項目

其實一直有朋友反饋,說我的博客文章太多了,亂花漸欲迷人,自己看得一頭霧水,不方便快速定位找到自己想要的項目,所以本博文置頂,列出我目前已有的所有項目,并給出總目錄,每個項目的文章鏈接,當然,本博文實時更新。。。以下是博客地址:

點擊直接前往

我這里已有的FPGA+DSP異構方案

目前我這里有大量FPGA+DSP異構方案的工程源碼,包括EMIF、SRIO、PCIE等等,對FPGA+DSP異構方案有需求的兄弟可以去看看:

直接點擊前往

我這里已有的 GT 高速接口解決方案

我的主頁有FPGA GT 高速接口專欄,該專欄有 GTP 、 GTX 、 GTH 、 GTY 等GT 資源的視頻傳輸例程和PCIE傳輸例程,其中 GTP基于A7系列FPGA開發板搭建,GTX基于K7或者ZYNQ系列FPGA開發板搭建,GTH基于KU或者V7系列FPGA開發板搭建,GTY基于KU+系列FPGA開發板搭建;以下是專欄地址:

點擊直接前往

3、工程詳細設計方案

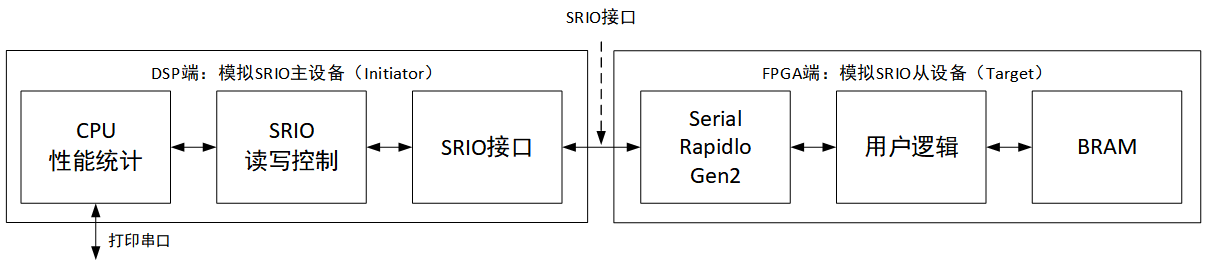

工程設計原理框圖

工程設計原理框圖如下:

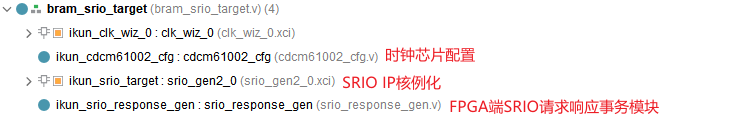

FPGA端工程源碼

FPGA端工程源碼架構如下:

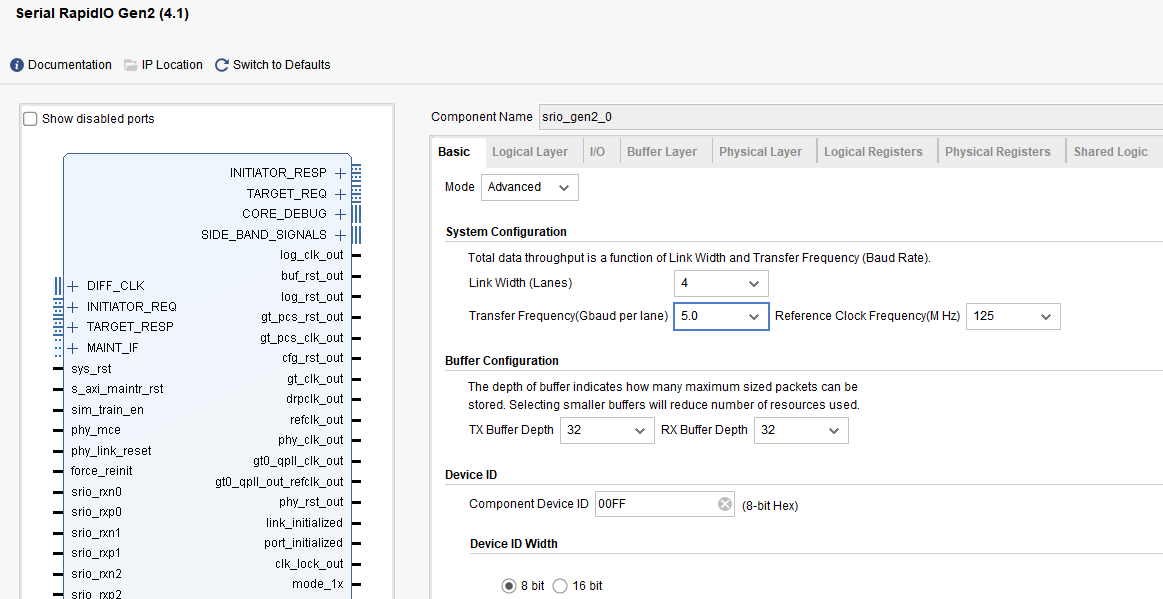

FPGA端SRIO從設備(Target)

FPGA工程調用Xilinx官方的SRIO IP核實現SRIO協議的物理層、傳輸層、邏輯層,作為SRIO的從設備(target),SRIO IP核留出了用戶邏輯接口,用戶只需要寫自己的邏輯電路與之對接即可完成SRIO通信;本設計使用Xilinx官方的Serial Rapidlo Gen2 IP核,基礎配置如下:

SRIO配置為5Gbps×4 Lane,對應的GT差分時鐘需為125M;工程代碼中通過配置cdcm61002時鐘芯片輸出125M連接至GTX高速收發器BANK;SRIO設計請參考Xilinx官方數據手冊《pg007_srio_gen2》;I/O 端口配置使用 HELLO 格式包,其他參數保持默認值即可;

FPGA端SRIO請求響應事務模塊

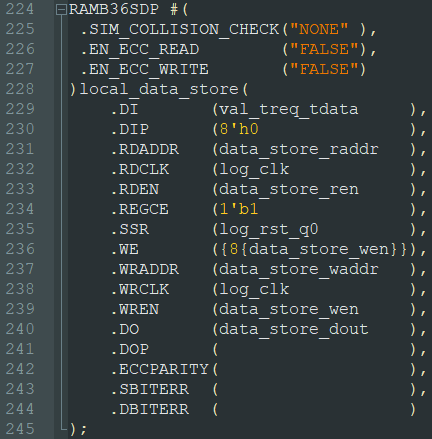

本設計只做簡單的數據緩存和讀寫,所以用戶邏輯為純verilog代碼實現的請求響應事務模塊,模塊例化了兩個RAMB36SDP的BRAM原語用戶數據讀寫的緩存(4K Byte),為接收到的請求事務生成對應的響應事務,該模塊參考了Xilinx官方SRIO IP核的仿真工程,根據請求-響應機制構造HELLO數據包,并根據讀寫地址操作BRAM以實現基于SRIO協議的數據收發架構;

當 Initiator 發過來的寫請求的目標地址的第 31 位到 16 位為 0x1087(address[31:16]=8’h1087),數據將會存儲至 BRAM;其他所有無需返回響應的寫請求將會被丟棄,該模塊不會為 SWRITE 返回響應。當 Initiator 發過來的讀請求的目標地址的第 31 位到 16 位為 0x1087(address[31:16]=8’h1087),數據將會從實際地址讀出;

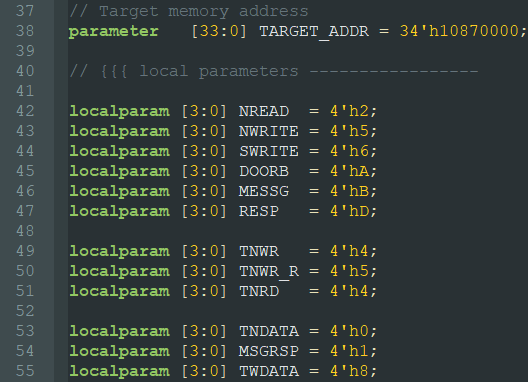

定義 HELLO 格式包頭 FTYPE 字段與 TTYPE 字段的值,這兩個字段的值與事務的類型有關。如下:

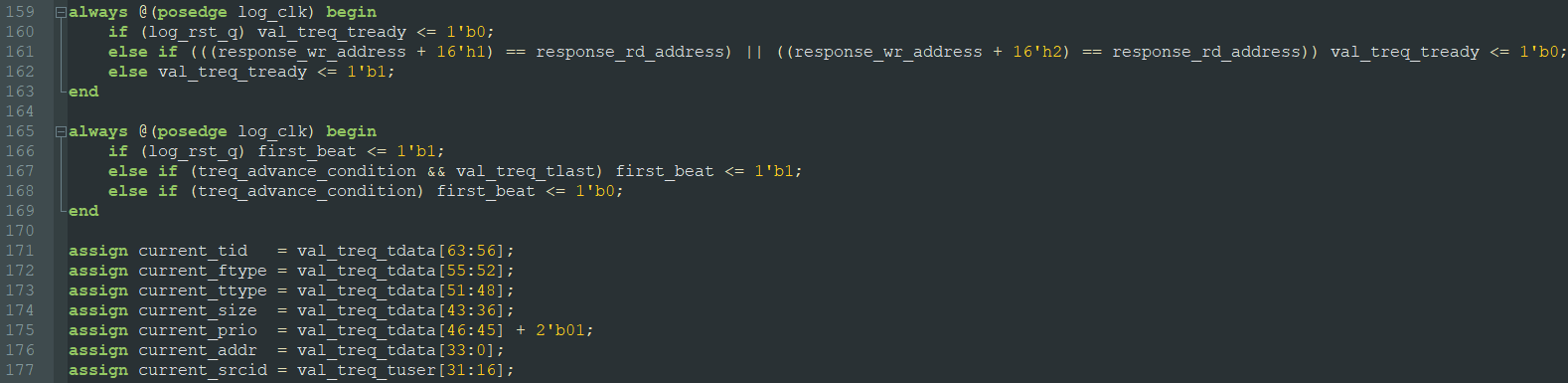

將 Initiator 發送的請求 treq_tdata 中的數據,按照 HELLO 格式的定義把對應的關鍵字段分離出來,如下:

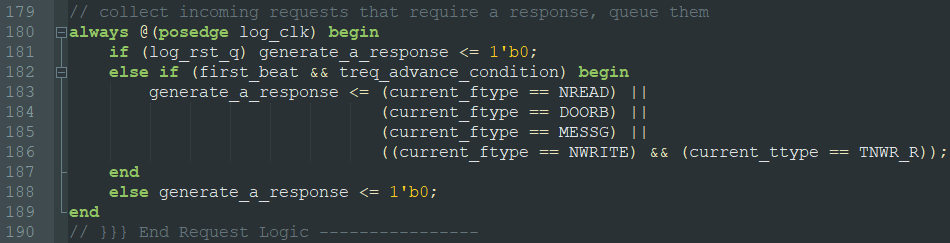

生成有響應事務的標志,可看到沒有 SWRITE 的標志,如下:

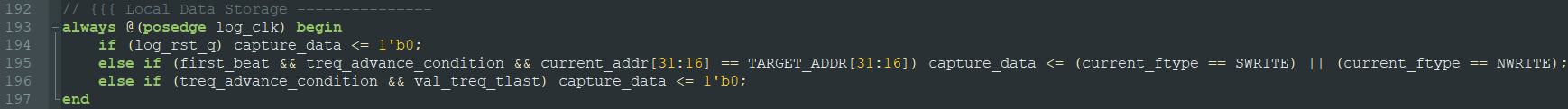

配置 SRIO Initiator 發送的讀寫事務基地址為 0x10870000;當地址字段的第 31 位到第 16 位為 0x1087,寫事務的數據將會存儲至 BRAM,如下:

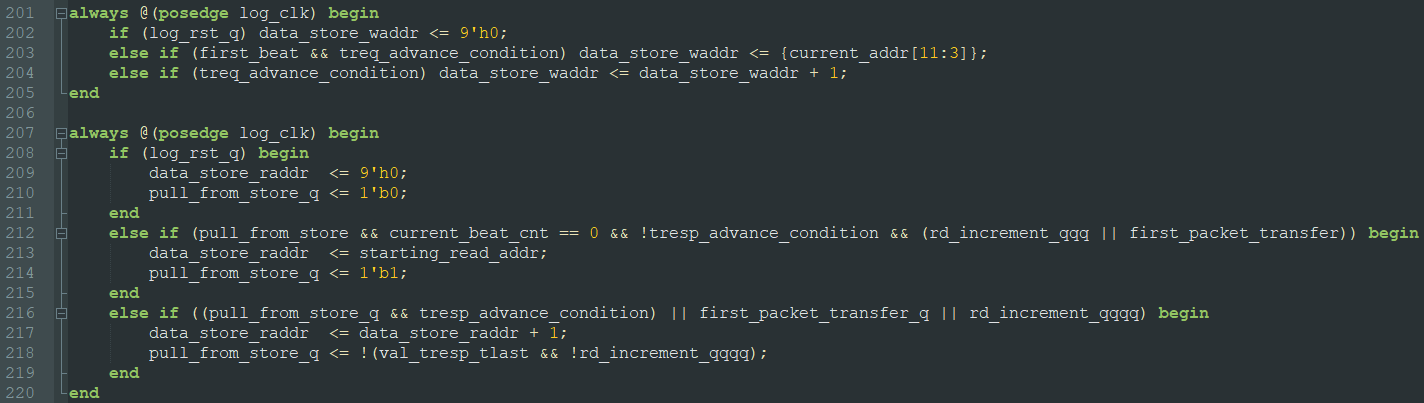

生成數據存儲的寫地址信號 data_store_waddr 和讀地址信號 data_store_raddr,該模塊的數據位寬為 64bit,其中地址取了 current_addr[11:3],而不是從第 0bit 開始取,即一次從 BRAM 讀寫 8Byte 大小的數據,一個地址對應一個字節,所以每讀寫一

次地址需遞增(加 8),如下:

例化一個 RAMB36SDP,用于存儲數據。DATA_WIDTH 為 64bit,ADDR 為 9bit,總容量為 2^9 x (64 / 8) = 512 x 8Byte = 4KByte,如下:

DSP端工程

DSP工程實現 DSP作為SRIO主設備(Initiator),通過SRIO總線與遠程設備通信,進行高速數據傳輸測試。核心功能包括SRIO子系統初始化與鏈路建立、NWRITE/SWRITE寫操作性能測試、NREAD讀操作與數據完整性驗證、傳輸速率實時統計與錯誤檢測等,DSP工程分為裸機工程和RTOS系統工程,裸機工程不帶操作系統,實時性更好,RTOS系統工程帶輕量版RTOS操作系統,穩定性更好,測試結果通過串口打印觀察;

代碼功能概述

此代碼實現 DSP作為SRIO主設備(Initiator),通過Serial RapidIO(SRIO)總線與遠程設備通信,進行高速數據傳輸測試。核心功能包括:

1、SRIO子系統初始化與鏈路建立

2、NWRITE/SWRITE寫操作性能測試

3、NREAD讀操作與數據完整性驗證

4、傳輸速率實時統計與錯誤檢測

DSP端工程流程圖如下:

DSP端SRIO讀寫核心細節

1、SRIO物理層配置(srio_device_init)

關鍵配置參數如下:

// SERDES PLL配置(250MHz參考時鐘→2.5GHz)

CSL_BootCfgSetSRIOSERDESConfigPLL(0x51); // MPY=10x

// 接收器配置(5Gbps速率)

CSL_BootCfgSetSRIOSERDESRxConfig(i, 0x00468495); // EQ/CDR/TERM使能

// 發送器配置(5Gbps速率)

CSL_BootCfgSetSRIOSERDESTxConfig(i, 0x001C8F95); // TAP權重/輸出擺幅

鏈路建立流程如下:

while(!CSL_SRIO_IsPortOk(hSrio, 0)) { // 輪詢端口狀態cpu_delaycycles(1000000); // 延遲1ms

}

2、數據傳輸機制(srio_test)

NWRITE寫操作配置如下:

tparams.ftype = Srio_Ftype_WRITE; // 快速非確認寫

tparams.ttype = Srio_Ttype_Write_NWRITE;

tparams.bytecount = 4096; // 4KB傳輸

tparams.rapidIOLSB = 0x10870000; // 目標設備地址

tparams.dspAddress = w_buff_global; // 源數據地址(DSP全局地址)

SWRITE寫操作配置如下:

tparams.ftype = Srio_Ftype_SWRITE; // 流式寫(低開銷)

tparams.ttype = Srio_Ttype_Write_SWRITE;

NREAD讀操作配置如下:

tparams.ftype = Srio_Ftype_REQUEST; // 請求類型

tparams.ttype = Srio_Ttype_Request_NREAD;

tparams.rapidIOLSB = 0x10870000; // 源數據地址(遠程)

tparams.dspAddress = r_buff_global; // 目標地址(DSP)

傳輸控制流程

傳輸控制流程如下:

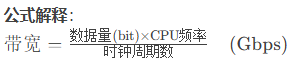

性能計算原理

transStart = _itoll(TSCH, TSCL); // 記錄開始時間戳

// ...傳輸執行...

transCost = _itoll(TSCH, TSCL) - transStart; // 計算周期數// 計算帶寬(Gbps)

w_rate = (transfer_size * 8) * (main_pll_freq / transCost) / 1e9;

關鍵代碼解析

1、地址轉換機制

w_buff_global = (uint8_t*)Convert_CoreLocal2GlobalAddr((uint32_t)w_buff);

2、數據驗證方法

for(i=0; i<transfer_size; i++) {if(w_buff_global[i] != r_buff_global[i]) {err_count++;// 記錄首個錯誤位置}

}

測試數據生成:基于種子隨機數(保證可重復性)

srand(i);

w_buff[i] = rand() % 0xFF;

3、傳輸狀態監控

CSL_SRIO_GetLSUCompletionCode(hSrio, LSU_Number, transactionID, &uiCompletionCode, &context);

DSP端性能測試結果

典型輸出示例如下:

=== loop times: 0 | err_count: 0 |

trans_size: 4096 Byte | NWRITE write times: 1200 ns(3.28 Gbps) |

NREAD read times: 1500 ns(2.73 Gbps)SRIO test 8 cycles, errcnt: 0, total size 32 KB,

write type: NWRITE, avg write rate: 3.20 Gbps,

read type: NREAD, avg read rate: 2.70 Gbps

性能分析:

NWRITE優勢:無確認開銷,實測帶寬達理論值(5Gbps)的 64%

NREAD瓶頸:需等待遠程響應,帶寬利用率降至 54%

核心價值總結

此代碼實現的價值在于:

1、驗證SRIO物理層:通過SERDES配置確保5Gbps穩定鏈路

2、量化傳輸性能:精確測量NWRITE/SWRITE/NREAD的實時帶寬

3、構建可靠基礎:錯誤檢測機制滿足軍工/航天級數據傳輸要求

4、提供優化基準:為異構系統(FPGA+DSP)提供高速互聯參考實現

通過該測試框架,可快速評估SRIO在特定硬件平臺上的極限性能,為實時信號處理、無線通信基帶等場景提供關鍵互聯技術支持。

4、工程源碼1詳解:FPGA邏輯工程

開發板FPGA型號:Xilinx–XC7K325T-2FFG676I;

FPGA開發環境:Vivado2019.1;

輸入輸出接口:SRIO高速接口;

實現功能:FPGA為SRIO從設備(Target);

工程作用:此工程目的是讓讀者掌握FPGA實現SRIO高速接口與DSP交互的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

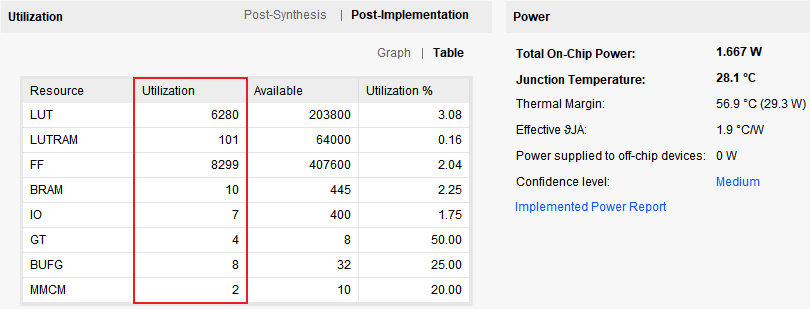

工程的資源消耗和功耗如下:

5、工程源碼2詳解:DSP裸機工程

開發板DSP型號:TI–TMS320C6678;

FPGA開發環境:CCS5.5;

輸入輸出接口:SRIO高速接口;

實現功能:DSP為SRIO主設備(Initiator);

DSP工程操作系統:裸機,無操作系統;

工程作用:此工程目的是讓讀者掌握FPGA實現SRIO高速接口與DSP交互的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

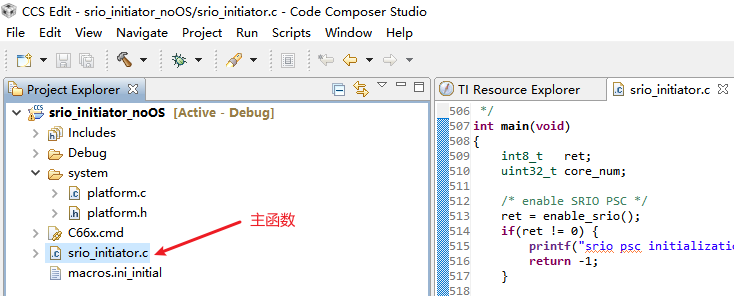

DSP裸機工程源碼架構如下:

6、工程源碼3詳解:DSP RTOS系統工程

開發板DSP型號:TI–TMS320C6678;

FPGA開發環境:CCS5.5;

輸入輸出接口:SRIO高速接口;

實現功能:DSP為SRIO主設備(Initiator);

DSP工程操作系統:RTOS操作系統;

工程作用:此工程目的是讓讀者掌握FPGA實現SRIO高速接口與DSP交互的設計能力,以便能夠移植和設計自己的項目;

工程Block Design和工程代碼架構請參考第3章節的《工程源碼架構》小節內容;

DSP裸機工程源碼架構如下:

7、工程移植說明

vivado版本不一致處理

1:如果你的vivado版本與本工程vivado版本一致,則直接打開工程;

2:如果你的vivado版本低于本工程vivado版本,則需要打開工程后,點擊文件–>另存為;但此方法并不保險,最保險的方法是將你的vivado版本升級到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解決如下:

打開工程后會發現IP都被鎖住了,如下:

此時需要升級IP,操作如下:

FPGA型號不一致處理

如果你的FPGA型號與我的不一致,則需要更改FPGA型號,操作如下:

更改FPGA型號后還需要升級IP,升級IP的方法前面已經講述了;

其他注意事項

1:由于每個板子的DDR不一定完全一樣,所以MIG IP需要根據你自己的原理圖進行配置,甚至可以直接刪掉我這里原工程的MIG并重新添加IP,重新配置;

2:根據你自己的原理圖修改引腳約束,在xdc文件中修改即可;

3:純FPGA移植到Zynq需要在工程中添加zynq軟核;

8、上板調試驗證

準備工作

需要準備的器材如下:

FPGA+DSP異構開發板;

測試用PC電腦;

串口線;

程序下載bit

步驟如下:(順序一定要對)

1、先下載FPGA程序

2、再下載DSP程序

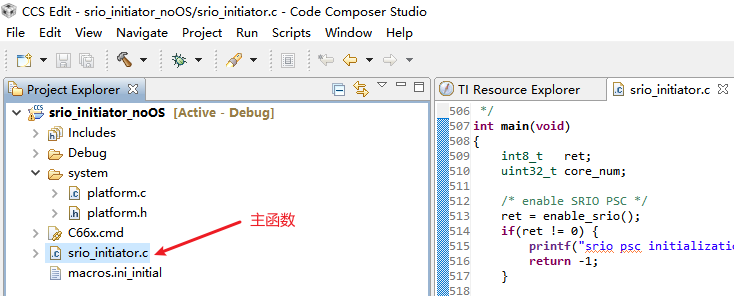

DSP裸機工程測試

DSP裸機工程測試結果如下:

NWRITE + NREAD 模式:NWRITE=12.50Gbps NREAD=7.74Gbps

SWRITE + NREAD 模式:SWRITE=12.49Gbps NREAD=7.74G

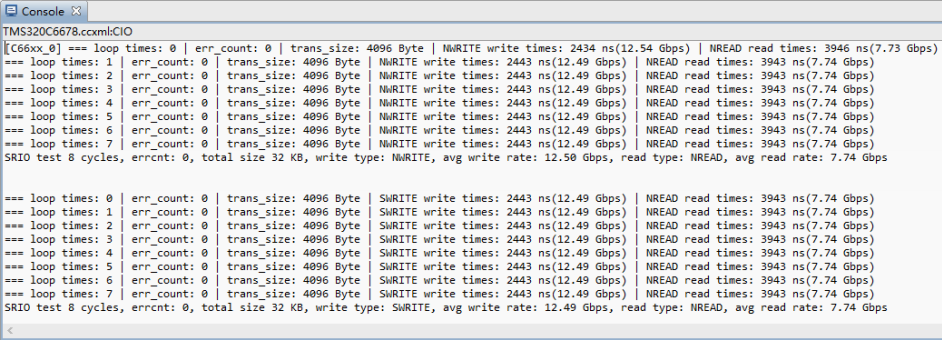

DSP RTOS系統工程測試

DSP RTOS系統工程測試結果如下:

NWRITE + NREAD 模式:NWRITE=12.53Gbps NREAD=7.73Gbps

SWRITE + NREAD 模式:SWRITE=12.55Gbps NREAD=7.73Gbps

打印信息解析

loop time: N :當前處于第 N 次循環讀寫;

err_count : 讀寫校驗誤碼率;

trans_size : 讀寫大小;

NWRITE、SWRITE、”NREAD : 表示使用 NWRITE、SWRITE 等方式傳輸;

write_time、read_times : 讀寫耗時,并根據 trans_size 計算讀寫速率;

SRIO test 8 cycles, errcnt: 0, total size 32 KB,

write type: NWRITE, avg write rate: xx.xx Gbps,

read type: NREAD, avg read rate: xx.xx Gbps

表示共進行了 8 次循環讀寫,總讀寫大小為32KByte,碼率為 0,并打印在 NWRITE + NREAD模式 8 次循環的平均速率;

9、工程代碼獲取

工程代碼如下:

單鏈表算法題(中))

是什么?)

Python基礎入門-核心數據結構)

v1.2.19 免費版)

)