好消息,好消息,小編最愛的國漫凡人修仙傳電視劇版本的終于可以看了,小編我推薦一波啊,感興趣的道友們可以去某酷視頻去追劇啊。

好了,咱們言歸正傳啊。本期的案例是這個月中旬我們組的測試大哥阿永去某田實驗室去測試我們的GMSL_poc 部分,在測試的時候發現很多路GMSL2的走線插損和回損都是不滿足其限值要求的。于是阿永就給我電話說了一下這個情況,讓我先幫忙做一下仿真看下情況,仿真的具體情況如下所示。

一,RX0_96712_FAKRA_1測試結果是不過的,目前可以優化的地方就是把POC電感的CUTOUT的H值加大即可,就是在POC電感下面多凈空一層,挖空L6-L7六層,參考L5層。

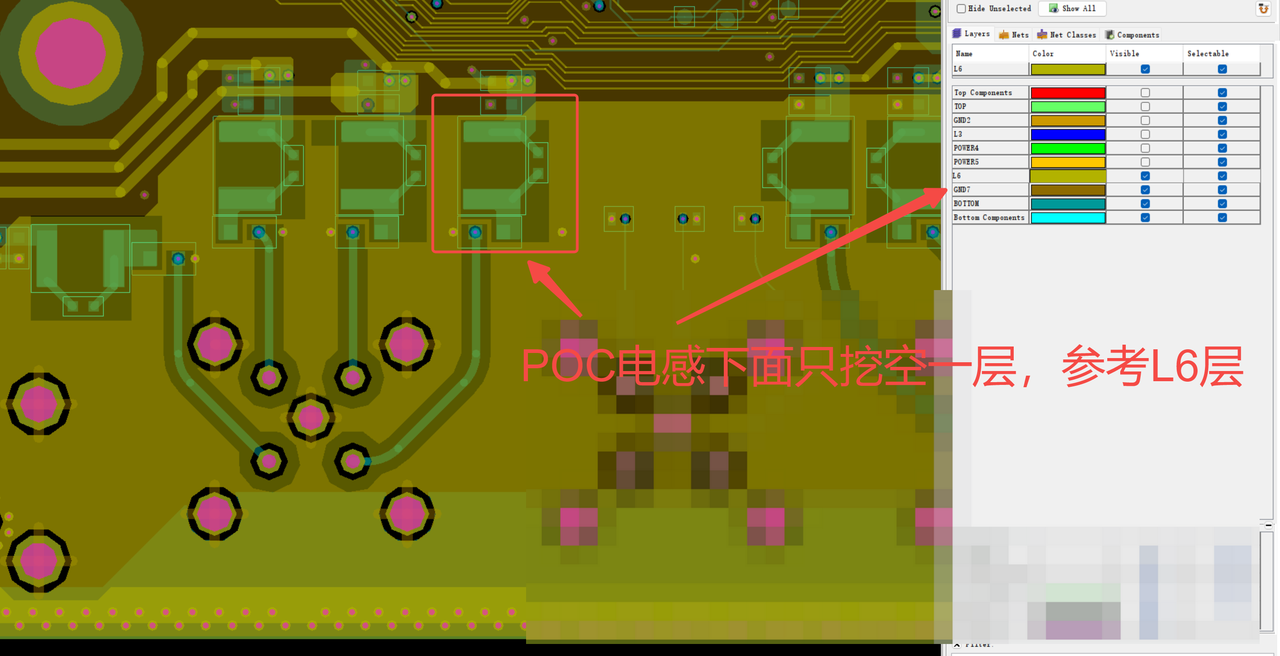

1,初始版本是POC電感下面挖空相鄰一層L7,參考L6層。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?(初始版本的PCB)

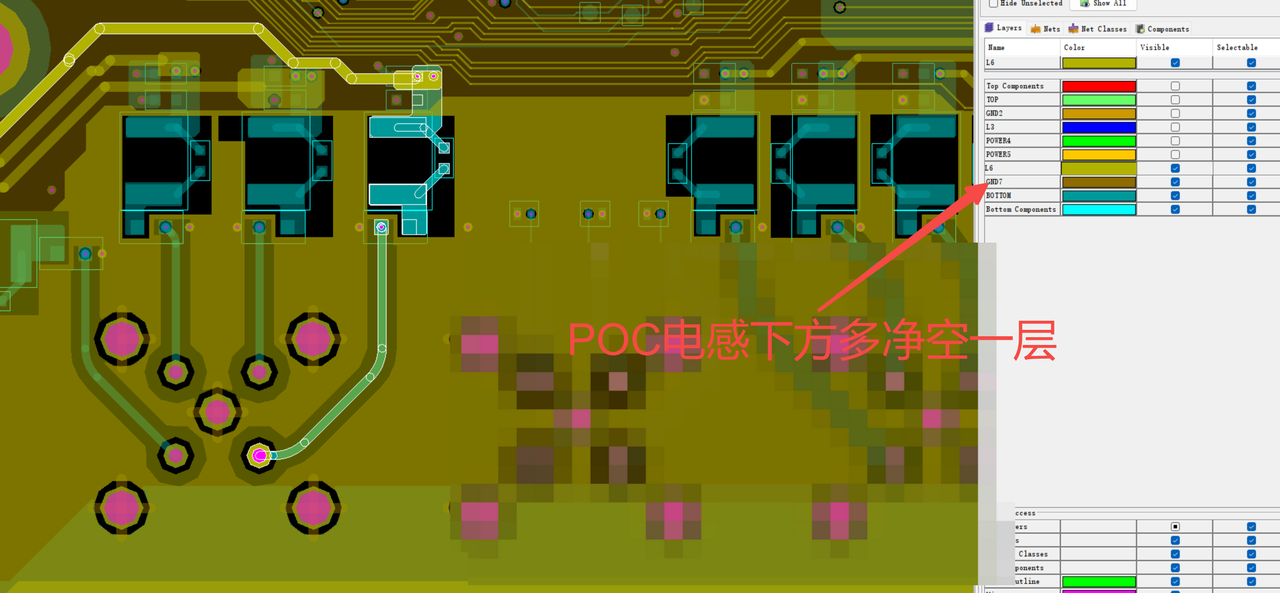

2,現在是改為POC電感下面挖空相鄰的兩層,即挖空L6,L7兩層,參考L5層。

? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ? ?(優化后版本的PCB)

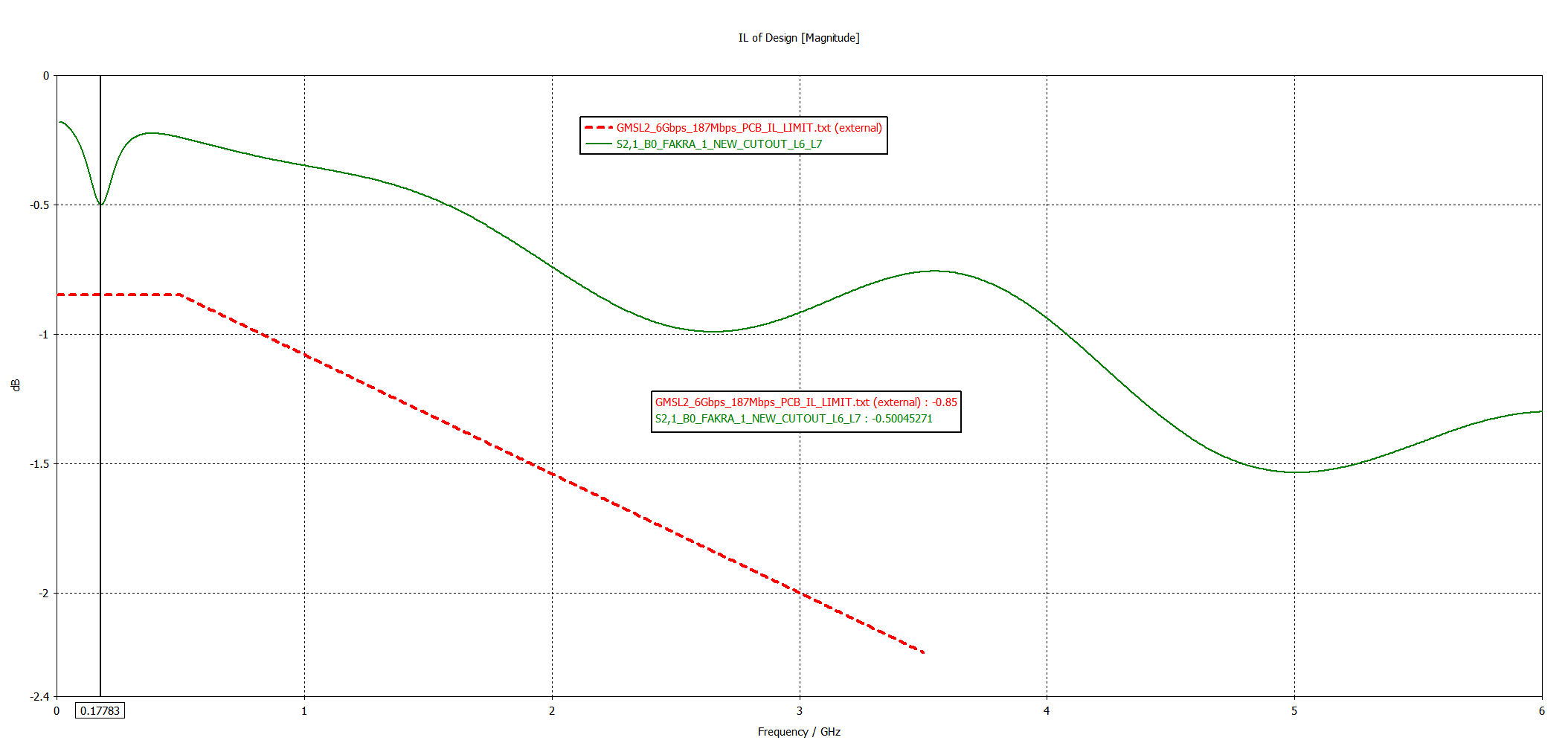

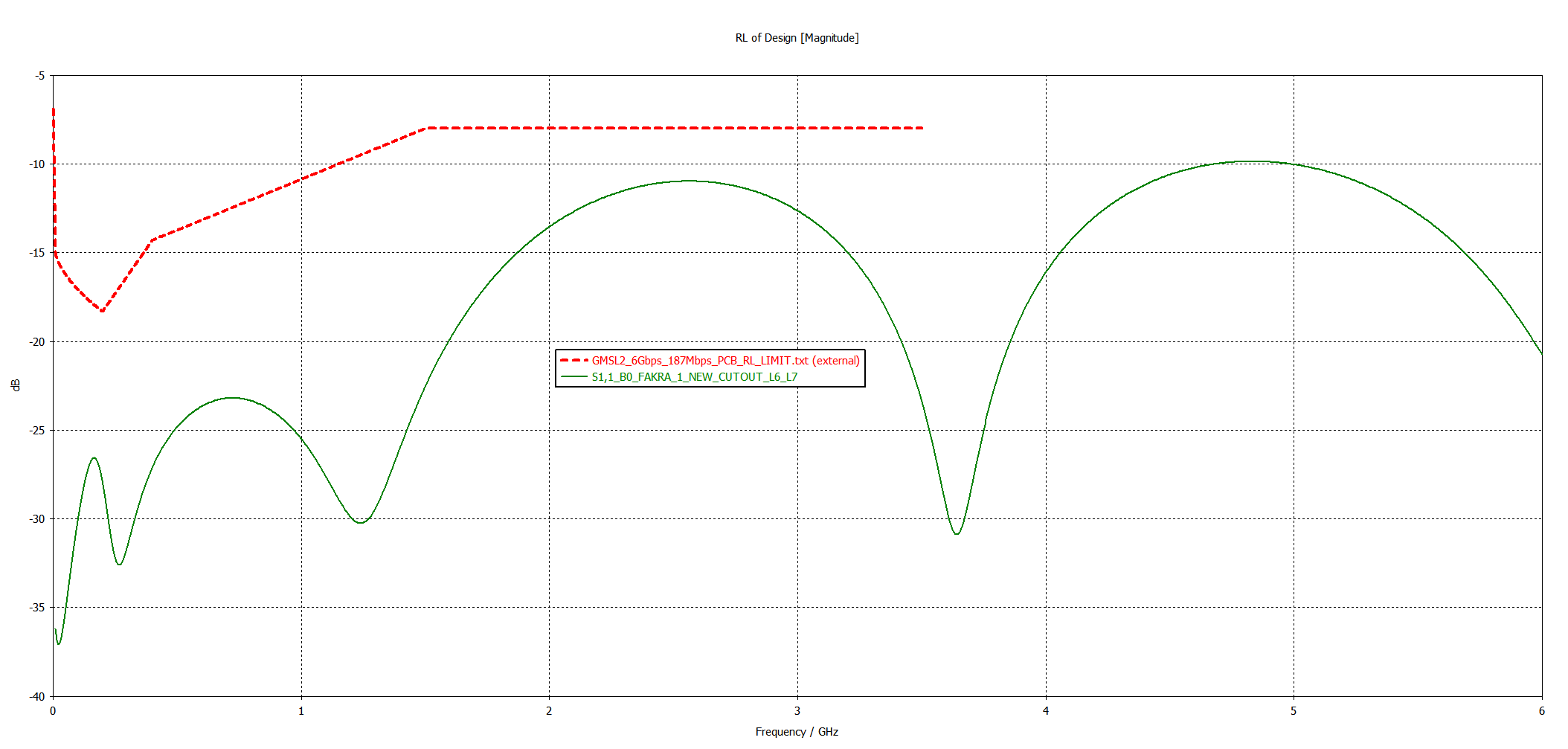

二,優化后看下其仿真效果:

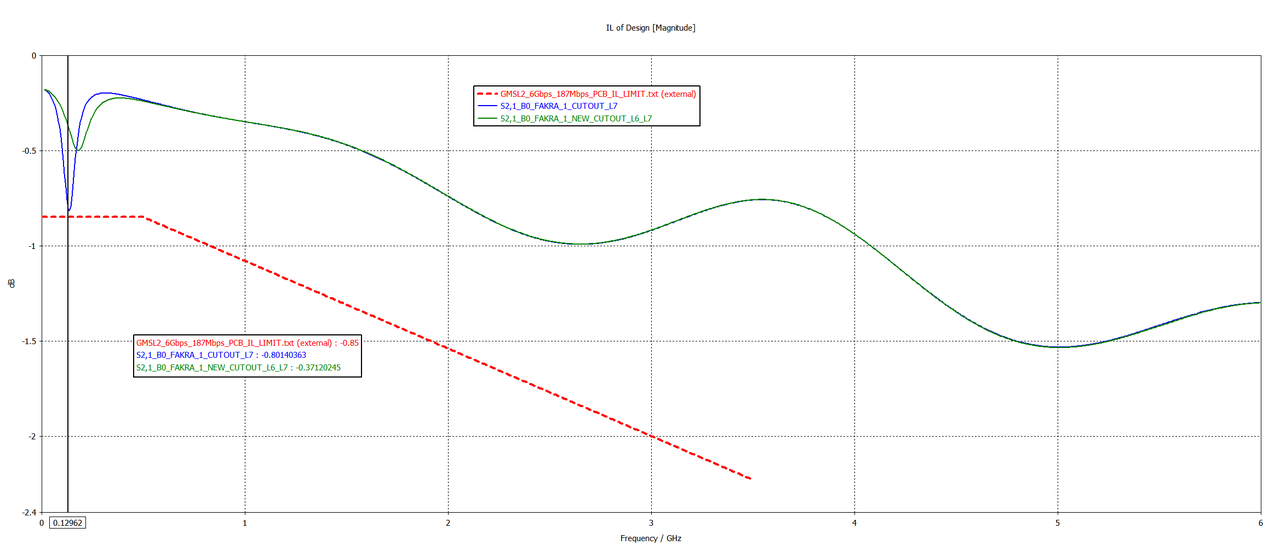

1, RX0_96712_FAKRA_1_S21:

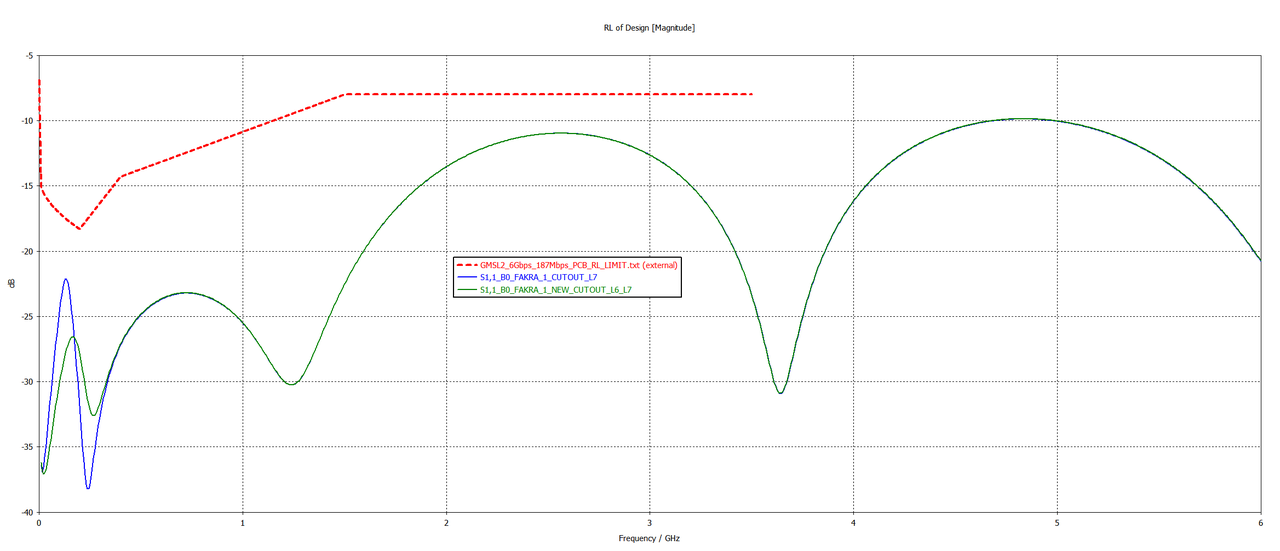

2, RX0_96712_FAKRA_1_S11:

3,RX0_96712_FAKRA_1_S21對比之前的版本:

4,RX0_96712_FAKRA_1_S11對比之前的版本:

三,若是測試的時候發現我們的GMSL走線在低頻段的時候其S21插損是不能滿足手冊的限值要求,我們可以從以下幾個方面去改善:

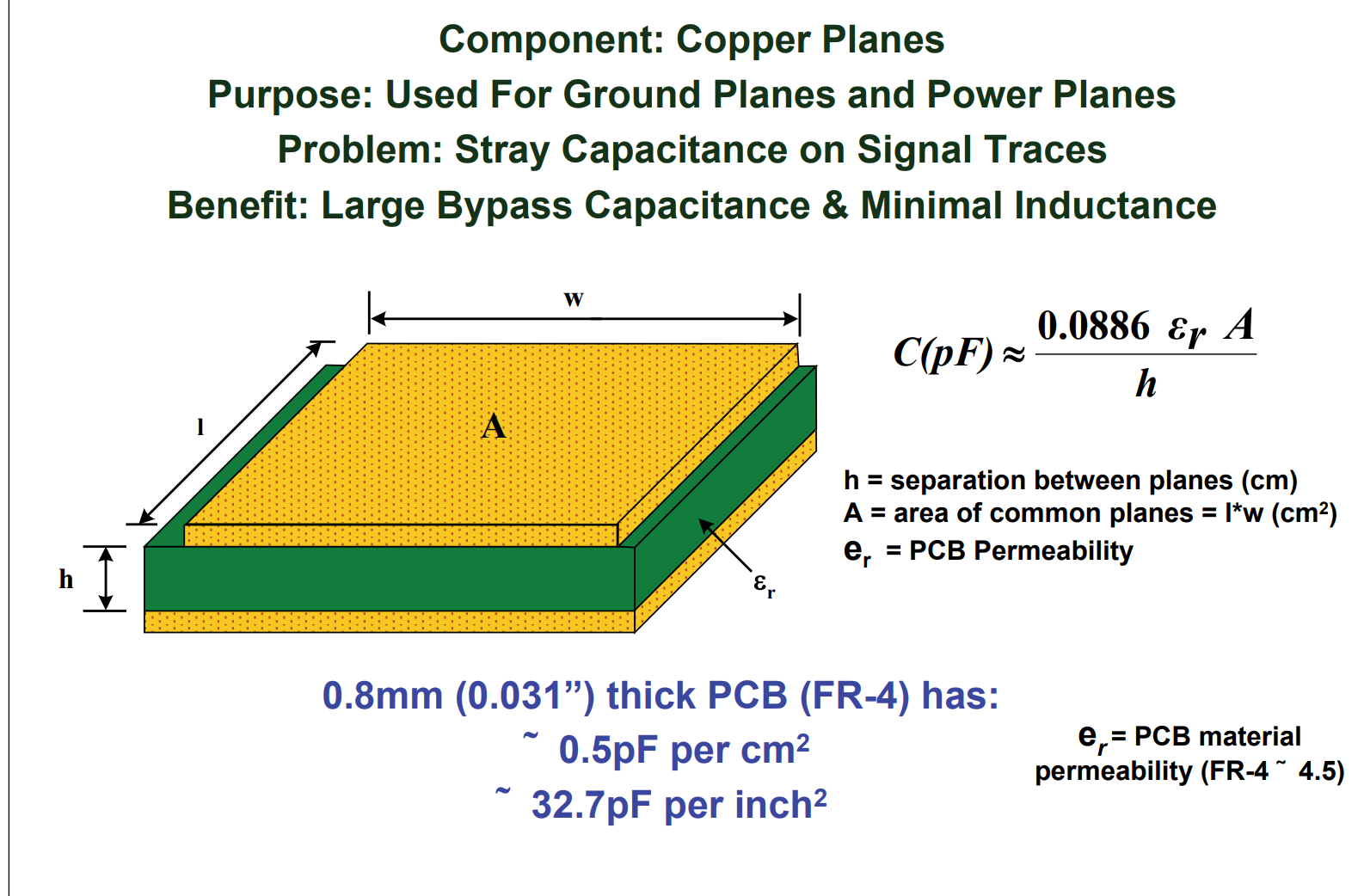

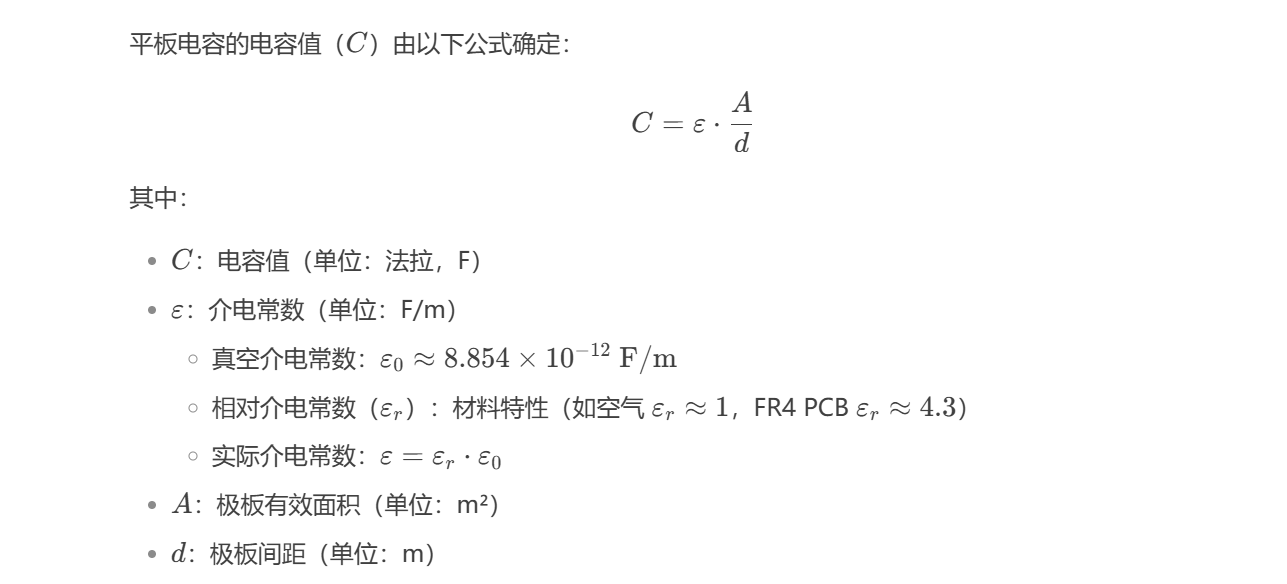

1,增加POC電感到其參考平面的距離H,即POC電感正下方在布線空間允許的情況下,多挖空幾層。(主要是減少POC電感下面的寄生電容,因為寄生電容的引入,會導致POC電感在某些頻段的阻抗性能嚴重下降,對信號的隔離效果也達不到設計要求,對信號的隔離效果也達不到設計要 求)

小編之前也有寫過一遍文章專門講解電感的Q值的:

Marin說PCB之Coilcraft&Bourns POC 電感的性能對比![]() https://blog.csdn.net/weixin_45223454/article/details/133828580

https://blog.csdn.net/weixin_45223454/article/details/133828580

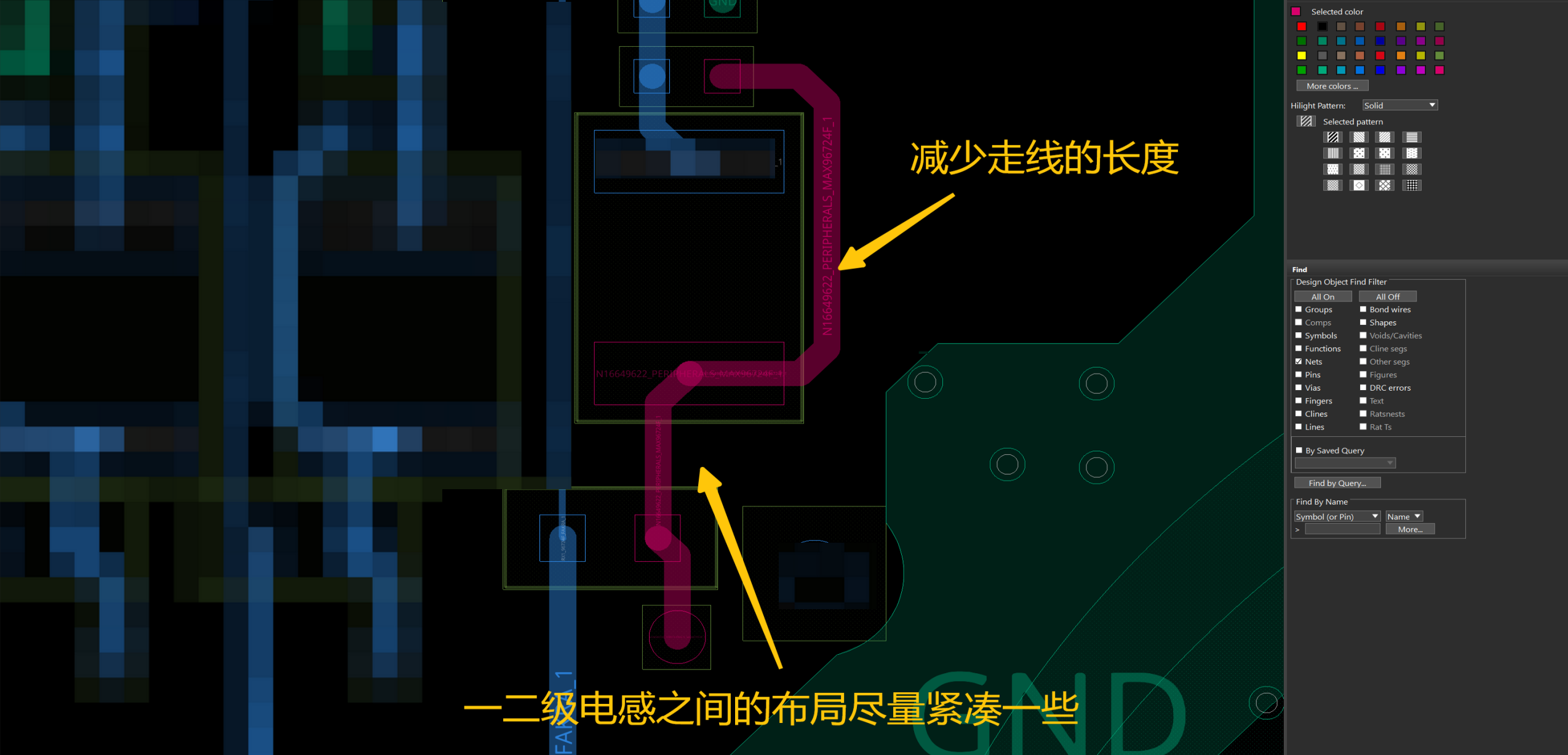

2,POC一二級電感之間的布局盡量緊湊,不要離的太遠或者是有間隙,(主要就是減少銅皮的面積A)

3,二級電感上并聯的電阻盡量并排和電感擺放,與其電感的走線也要盡量短一些,減少其寄生參數對GMSL2的插損性能的影響。

4,挖空相鄰的GND層面的時候,注意檢查一下POC器件層的走線是否有投影在這個挖空區域內,盡量避免這個情況出現。

5,增加POC電感的挖空尺寸,挖空的尺寸還是參考之前要求:挖空區域的寬度≥1.75倍(ratio值)的pad寬度為宜, ratio值具體要視pad 的尺寸、設計的疊構和信號要求(tr)而定。

6,? ?盡量減少POC電感上的走線或者是鋪銅皮的寬度,在滿足其載流的前提下。(主要就是減少銅皮的面積A)

7,??使用相對介電常數更低的板材,這樣也可以減少POC電感下面的寄生電容。但是這個建議不太實用,因為板材一般在PCB設計前期的時候就差不多定下來了,不太可能因為這個減少走線上的寄生電容就去改板材的,這只是一個使用建議之一,小編我個人感覺不太實用的,也不推薦的。

好了,諸位道友們以上就是本期的所有內容了,我們下期文章不見不散。

?

--------聲明:本文屬于小編的原創文章,如需轉載請注明來源!