1.概念

時鐘(clock):在電子系統中是一個產生穩定、周期性振蕩信號的電路或組件。這個信號像節拍器或心跳一樣,為數字電路中的各種操作提供同步時序基準。

PLL(phase locked loop)鎖相環電路: 倍頻

PFD(phase fractional Prescale)相位分數分頻器: 輸出頻率可升可降

2.時鐘配置

1.CCM

CCM 是 i.MX6U 時鐘系統的 “大腦”,通過?PLL(鎖相環,倍頻)?和?Divider(分頻器)?實現時鐘信號的 “精準縮放”,核心模塊包括:

PLL 模塊(倍頻核心)

接收低頻時鐘源(如 24MHz XTAL),通過倍頻生成高頻時鐘,供高性能模塊使用。i.MX6U 針對不同時鐘域設計了專用 PLL:PLL1(ARM PLL):Cortex-A7 CPU 的專屬 PLL,最高可將 24MHz 倍頻至?792MHz(即 CPU 最高主頻 792MHz,需配合電壓調整)。PLL2(System PLL):為外設域提供基礎時鐘,輸出固定 528MHz,再通過分頻供給 UART、SPI、GPT 等外設。PLL3(USB PLL):專門為 USB 模塊提供 480MHz 時鐘(USB 2.0 高速模式需求)。PLL4(Audio PLL):為音頻模塊(如 I2S)提供精準時鐘,支持靈活配置頻率。

Divider 模塊(分頻調節)

對 PLL 輸出的高頻時鐘進行 “降壓”,適配不同模塊的時鐘需求(如 UART 常用 115200bps 波特率,需 8MHz 或 16MHz 時鐘)。

例:PLL2 輸出 528MHz → 經分頻器(÷66)得到 8MHz → 供給 UART1 模塊。Clock Gate(時鐘門控)

為每個模塊提供獨立的 “時鐘開關”—— 未使用的模塊可關閉時鐘(如 UART2 未使用時,關閉其時鐘),是 i.MX6U 低功耗設計的關鍵。

2.PLL模塊

1.PLL1

kernal: CCM_ANALOG_PLL_ARMn

配置步驟:

- 先選擇osc_clk,讓step_clk為24MHz

- 再將PLL1的輸出改成step_clk,讓ARM暫時工作在24MHz;

- 配置PLL為1056MHz,注意設置倍頻因子之前先把PLL之后的二分頻設置好,避免ARM內核故障!!

- 最后改回pll1_main_clk

示例

//ARM工作時鐘配置 先分頻再倍頻保證ARM內核正常工作CCM->CACRR &= ~(7 << 0); //先清0CCM->CACRR |= (1 << 0); //設置為2分頻(001)CCM->CCSR &= ~(1 << 8); //設置24MHzCCM->CCSR |= (1 << 2); //設為另外一路(step_clk),此時 鎖相環短路(pll1_main_clk)(PPL_ARM), 可安全配置PPL_ARMunsigned int t = CCM_ANALOG->PLL_ARM; //此時可安全配置PPL_ARMt &= ~(0x7F << 0);t |= (88 << 0);t |= (1 << 13);t &= ~(3 << 14);CCM_ANALOG->PLL_ARM = t;CCM->CCSR &= ~(1 << 2); //切換回PPL_ARM路2.528PLL

它是 i.MX6U 芯片中負責為高速外設和關鍵功能模塊提供穩定、高頻時鐘的核心鎖相環(PLL),因輸出時鐘最高可配置為528MHz而得名,是整個芯片時鐘樹中至關重要的 “高頻時鐘源” 之一。

CCM_ANALOG_PFD_528n

由手冊知,相關配置為

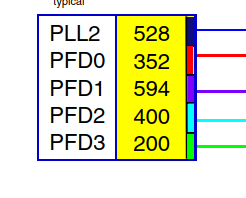

故PLL2下的PFDn需要配置的MHz如圖,相關計算公式為

故對于PFD0來說為528 * 18 / 352 = 27

示例

t = CCM_ANALOG->PFD_528;t &= ~((0x3F << 0) | (0x3F << 8) | (0x3F << 16) | (0x3F << 24)); //先清0t |= ((27 << 0) | (16 << 8) | (24 << 16) | (32 << 24));CCM_ANALOG->PFD_528 = t;3.PLL3

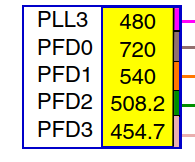

在 i.MX6U 芯片中,PLL3(USB PLL)?是專門為 USB(通用串行總線)模塊設計的鎖相環(PLL),其核心作用是為 USB 控制器提供符合協議規范的高精度時鐘信號

相關配置如圖

![]()

示例如圖

t = CCM_ANALOG->PFD_480;t &= ~((0x3F << 0) | (0x3F << 8) | (0x3F << 16) | (0x3F << 24)); //先清0t |= ((12 << 0) | (16 << 8) | (17 << 16) | (19 << 24));CCM_ANALOG->PFD_480 = t;3.時鐘根配置

需配置AHB_CLK_ROOT? ? 132MHZ

???????????PERCLK_CLK_ROOT? 66MHz

? ? ? ? ? ?IPG_CLK_ROOT? ? ? ? 66MHz

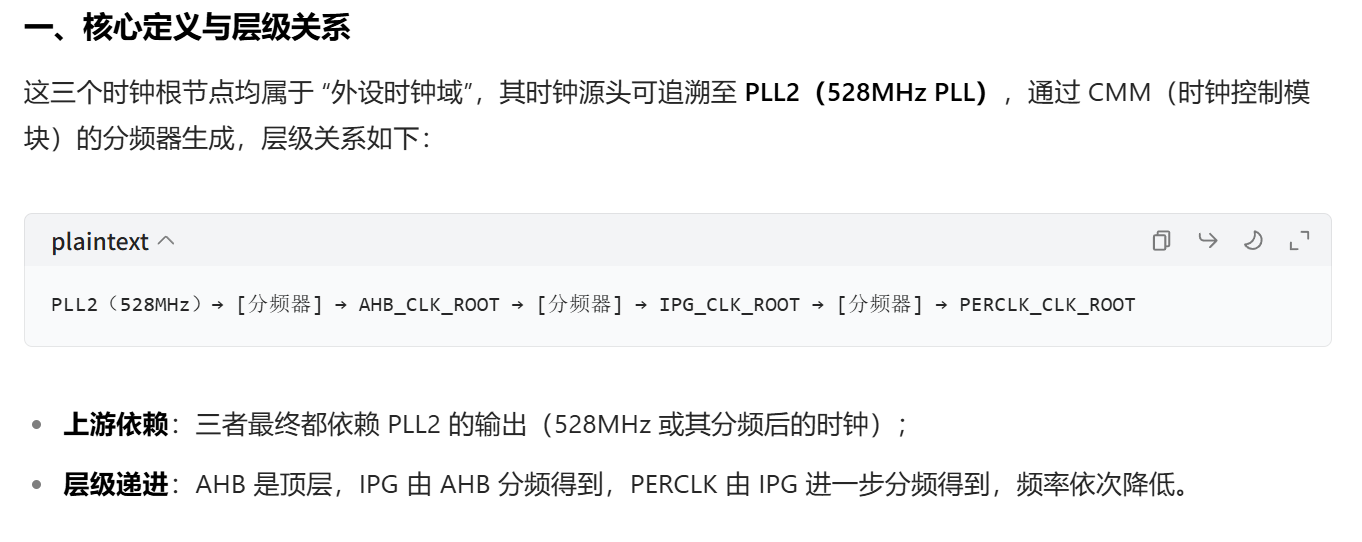

在 i.MX6U(基于 Cortex-A7 架構)的時鐘樹中,AHB_CLK_ROOT、PERCLK_CLK_ROOT?和?IPG_CLK_ROOT?是三個核心的 “時鐘根節點”,它們從上層 PLL 獲取時鐘信號后,通過分頻或直接分配,為不同類型的外設、總線和功能模塊提供時鐘。三者的定位、頻率來源和服務對象有明確分工,共同構成了外設時鐘域的核心架構。

AHB(Advanced High-performance Bus,高級高性能總線)是芯片內部的高速數據傳輸總線,AHB_CLK_ROOT?是該總線的根時鐘,決定了高速外設和內存接口的數據傳輸速率。

IPG(Internal Peripheral Bus,內部外設總線)是 AHB 總線的 “子總線”,主要連接中速外設,IPG_CLK_ROOT?是該總線的根時鐘,也是多數通用外設的基礎時鐘源。

PERCLK(Peripheral Clock,外設時鐘)是 IPG 總線的 “低速分支”,PERCLK_CLK_ROOT?專為對時鐘頻率要求較低的外設設計,是低速外設的統一時鐘源。

示例

//AHB_clk_root配置CCM->CBCMR &= ~(3 << 18); //先清0CCM->CBCMR |= (1 << 18); //選擇 pll2的pfd2t = CCM->CBCDR;t &= ~(1 << 25); //選通pll2的門t &= ~(7 << 10); //清0t |= (2 << 10); //設為010三分頻//IPG_CLK_ROOT配置t &= ~(3 << 8); //清0t |= (1 << 8); //設為001二分頻 IPG_CLK_ROOTCCM->CBCDR = t;//PRECLK-CLK_ROOT配置t = CCM->CSCMR1;t &= ~(1 << 6); //選通所要選擇的路t &= ~(0x3F << 0); //設為1分頻 PRECLK-CLK_ROOTCCM->CSCMR1 = t;3.EPIT

1.工作模式

EPIT 支持兩種經典工作模式,核心差異在于計數到 0 后的行為:

1. 重裝載模式(Reload Mode)

- 工作邏輯:計數器從 LR(重裝載寄存器)的值開始向下計數,當計數到 0 時:

- 觸發 “計數結束中斷”;

- 自動將 LR 的值重新裝

- 載到計數器,開始新一輪計數(無需軟件干預)。

- 核心特點:中斷間隔嚴格固定(周期 = LR 值 × 計數周期),無累積誤差,適合周期性任務(如 1ms 一次的系統節拍)。

- 示例:若 LR=1000,計數周期 = 1μs,則每 1000μs(1ms)觸發一次中斷,循環往復。

2. 自由運行模式(Free-Run Mode)

- 工作邏輯:計數器從 LR 的值開始向下計數,當計數到 0 時:

- 觸發 “計數結束中斷”;

- 計數器停止計數(保持 0 值),需通過軟件重新寫入 LR 值才能再次啟動。

- 核心特點:僅觸發一次中斷,適合單次定時(如延時 10ms 后執行某個初始化操作)。

- 示例:若 LR=10000,計數周期 = 1μs,則 10ms 后觸發一次中斷,之后計數器停止。

2.相關配置

示例

void epit1_init(void)

{unsigned int t;t = EPIT1->CR;t &= ~(3 << 24); //先清0,再寫1t |= (1 << 24); //設置時鐘源為外設時鐘irq_clk_roott |= (1 << 17);t &= ~(0xFFF << 4); //清0t |= (65 << 4); //分頻66倍(65+1)后即為1MHzt |= (1 << 3); //set-forget模式t |= (1 << 2); //比較中斷啟用t |= (1 << 1); EPIT1->CR = t;EPIT1->LR = 1000000;EPIT1->CMPR = 0;EPIT1->CNR = 1000000;//注冊中斷處理函數system_interrupt_register(EPIT1_IRQn, epit1_irq_handler);//GIC中斷使能GIC_EnableIRQ(EPIT1_IRQn);//GIC中斷優先級設置GIC_SetPriority(EPIT1_IRQn, 0);//enableEPIT1->CR |= (1 << 0); //EPIT啟用,注意最后再啟用

})

)

)

-渲染列表)

![[硬件電路-212]:電流的本質確實是電子的移動](http://pic.xiahunao.cn/[硬件電路-212]:電流的本質確實是電子的移動)

)

打開工程文件的幾種方法)

:2.點燈與ubuntu安裝)