由于Verilog中X態的微妙語義,RTL仿真可能PASS,而網表仿真卻會fail。

目前進行的網表仿真越來越少,這個問題尤其嚴重,主要是網表仿真比RTL仿真慢得多,因此對整個回歸測試而言成本效益不高。

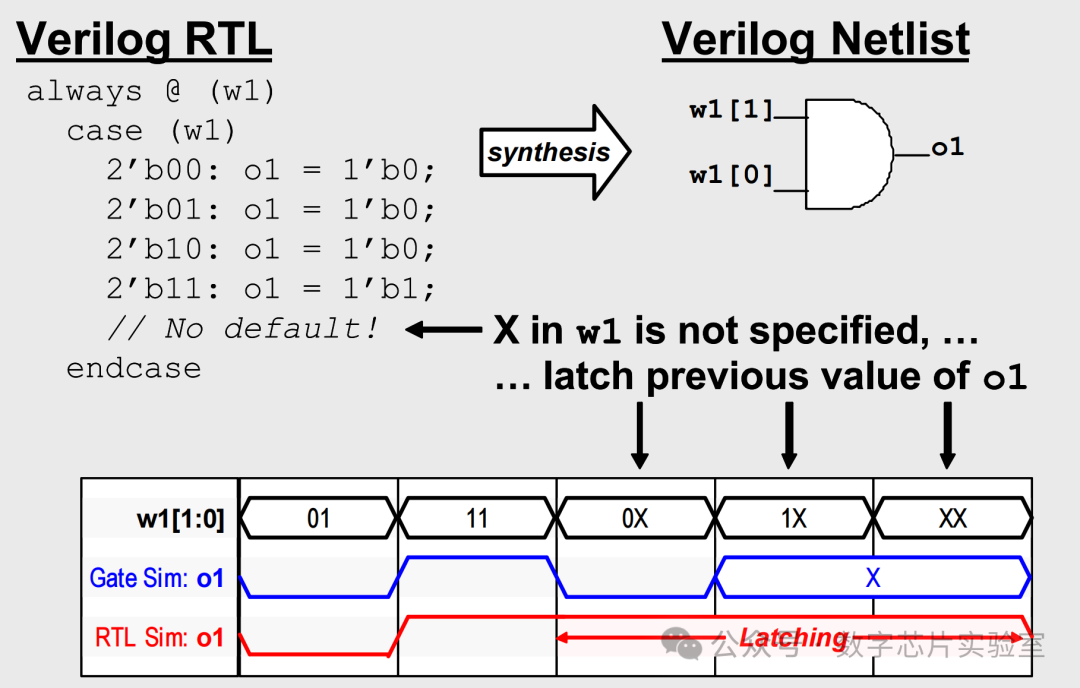

上面的例子中,用Verilog RTL中的case語句描述了一個簡單的AND函數,它被綜合成AND2門。然而,波形圖顯示RTL仿真與網表仿真存在差異。

當w1信號上出現任何X值時(可能來自顯式的X賦值或未初始化的寄存器),仿真差異就會發生。w1上的X值意味著w1無法匹配任何一個case項。由于沒有default行,輸出o1必須保持其之前的值,這意味著在上面的波形中o1會保持高電平鎖存狀態。

最有趣的差異出現在w1==2'b0X時:

-

網表仿真正確地顯示o1為低電平

-

RTL仿真錯誤地保持o1為高電平(相反的值)

無論w1上的X值如何優化,每個網表都會表現得像這樣。綜合工具不會警告這個“鎖存行為”,但當RTL驗證僅因為這種X態解釋而通過某些測試用例時,RTL和網表仿真之間的差異就變得危險了。

)

)