目錄

- 1、前言

- 免責聲明

- 2、相關方案推薦

- 我這里已有的 GT 高速接口解決方案

- 我目前已有的SDI編解碼方案

- 3、詳細設計方案

- 設計框圖

- 3G-SDI攝像頭

- LMH0384均衡EQ

- UltraScale GTH 的SDI模式應用

- UltraScale GTH 基本結構

- 參考時鐘的選擇和分配

- UltraScale GTH 發送和接收處理流程

- UltraScale GTH 發送接口

- UltraScale GTH 接收接口

- UltraScale GTH IP核調用和使用

- UltraScale GTH 控制說明

- SMPTE UHD-SDI詳解

- SMPTE UHD-SDI 接收

- SMPTE UHD-SDI 發送

- SMPTE UHD-SDI IP核調用和使用

- VGA時序恢復

- 圖像緩存

- VTC模塊(VGA時序)

- YUV422轉RGB888模塊

- DP輸出

- 4、vivado工程1:1路SDI視頻解碼--DP輸出

- PL端邏輯設計

- PS端Vitis SDK 軟件設計

- 5、vivado工程2:4路SDI視頻解碼--DP輸出

- PL端邏輯設計

- PS端Vitis SDK 軟件設計

- 6、工程移植說明

- vivado版本不一致處理

- FPGA型號不一致處理

- 其他注意事項

- 7、上板調試驗證

- 準備工作

- 輸出演示

- 8、福利:工程代碼的獲取

FPGA高端項目:UltraScale GTH + SDI 視頻解碼,SDI轉DP輸出,提供2套工程源碼和技術支持

1、前言

Xilinx系列FPGA實現SDI視頻編解碼目前有兩種方案:

一是使用專用編解碼芯片,比如典型的接收器GS2971,發送器GS2972,優點是簡單,比如GS2971接收器直接將SDI解碼為并行的YCRCB,GS2972發送器直接將并行的YCRCB編碼為SDI視頻,缺點是成本較高,可以百度一下GS2971和GS2972的價格;另一種方案是使用FPGA實現編解碼,利用FPGA的GTP/GTX/GTH/UltraScale GTH等資源實現解串,優點是合理利用了FPGA資源,缺點是操作難度大一些,對FPGA水平要求較高;UltraScale GTH 適用于Xilinx UltraScale系列的FPGA上,包括Virtex UltraScale、Kintex UltraScale、Zynq? UltraScale等器件,在UltraScale系列之下只有GTH,而UltraScale GTH相比于GTH,線速率更高,支持協議類型更多,功耗更低,帶寬更高;同樣的,Xilinx也提供了SDI視頻編解碼的專用IP,比如SMPTE UHD-SDI,該IP支持3G-SDI、6G-SDI、12G-SDI等視頻編解碼;

本文使用Xilinx的Zynq UltraScale+MPSoCs–xczu7ev-ffvc1156-2-i 型號的FPGA實現UltraScale GTH + SDI 視頻編解碼;攝像頭為標準的3G-SDI攝像頭,開發板板載LMH0384芯片,SDI視頻經過LMH0384起到均衡EQ的作用,也可以理解為單端轉差分;然后調用Xilinx官方的UltraScale GTH IP核實現SDI視頻的解串與串化,IP配置為GTH-3G-SDI模式,該模式專門用于SDI視頻協議的解串與串化;然后調用Xilinx官方的SMPTE UHD-SDI IP核實現SDI視頻解碼與編碼,該IP支持3G-SDI、6G-SDI、12G-SDI等視頻編解碼,本設計配置為3G-SDI模式;SDI視頻接收流程至此已經由原始的同軸線傳輸的單端視頻變為了并行的視頻數據了,此時可以作為圖像處理的輸入源了,可以緩存、顏色轉換、縮放等等操作;本設計采用DP+SDI同步輸出方式;首先需要將圖像緩存進DDR4中,所以需要用到VGA時序恢復模塊,將SDI視頻有效數據恢復為帶有行同步信號(hs)、場同步信號(vs)、數據有效信號(de)、像素數據(data)的標準VGA時序;然后使用我常用的FDMA圖像緩存架構將SDI視頻寫入DDR4再讀出,圖像在DDR4中做三幀緩存,如果你覺得延時太高,可以選擇緩存2幀即可;使用VTC模塊,即VGA時序生成模塊,分辨率為1080P@60Hz,VTC模塊控制DFMA模塊從DDR4中把視頻讀出來;SDI視頻從DDR4中讀出來時為YUV422格式,需要使用YUV422轉RGB888模塊將SDI視頻轉換為24位的RGB888,此時的視頻就是標準的VGA時序視頻了;再調用Zynq軟核,打開其DP接口的配置并引出DP輸入時序信號,將VGA時序視頻輸入DP即可;DP的輸出功能在Vitis SDK中以C語言軟件方式實現,然后輸出DP顯示器即可;

注意!!

注意!!

注意!!

本工程和方案只適用于Xilinx UltraScale和UltraScale+系列FPGA器件,因為用到了UltraScale GTH IP核,其他系列FPFA不包含UltraScale GTH,諸如Xilinx 的A7、K7、V7、Zynq7000系列等均不可用,遑論其他公司的FPGA;緩存用的DDR4,用DDR3也是可以的;

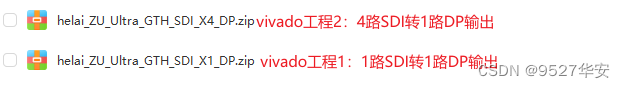

提供2套vivado2022.2版本的FPGA工程源碼,兩套工程的區別在于SDI攝像頭的路數,第一套工程只用到了1路SDI攝像頭;第二套工程用到了4路SDI攝像頭,解碼4路SDI,但只選擇第一路作為DP輸出;詳情如下:

vivado工程1:1路SDI輸入,DDR4做三幀緩存后DP輸出;

vivado工程2:4路SDI輸入,DDR4做三幀緩存后DP輸出;

本博客詳細描述了Xilinx的Zynq UltraScale+MPSoCs–xczu7ev-ffvc1156-2-i 型號的FPGA實現UltraScale GTH + SDI 視頻編解碼的設計方案,工程代碼可綜合編譯上板調試,可直接項目移植,適用于在校學生、研究生項目開發,也適用于在職工程師做學習提升,可應用于醫療、軍工等行業的高速接口或圖像處理領域;

提供完整的、跑通的工程源碼和技術支持;

工程源碼和技術支持的獲取方式放在了文章末尾,請耐心看到最后;

免責聲明

本工程及其源碼即有自己寫的一部分,也有網絡公開渠道獲取的一部分(包括CSDN、Xilinx官網、Altera官網等等),若大佬們覺得有所冒犯,請私信批評教育;基于此,本工程及其源碼僅限于讀者或粉絲個人學習和研究,禁止用于商業用途,若由于讀者或粉絲自身原因用于商業用途所導致的法律問題,與本博客及博主無關,請謹慎使用。。。

2、相關方案推薦

我這里已有的 GT 高速接口解決方案

我的主頁有FPGA GT 高速接口專欄,該專欄有 GTP 、 GTX 、 GTH 、 GTY 等GT 資源的視頻傳輸例程和PCIE傳輸例程,其中 GTP基于A7系列FPGA開發板搭建,GTX基于K7或者ZYNQ系列FPGA開發板搭建,GTH基于KU或者V7系列FPGA開發板搭建,GTY基于KU+系列FPGA開發板搭建;以下是專欄地址:

點擊直接前往

我目前已有的SDI編解碼方案

我的博客主頁開設有SDI視頻專欄,里面全是FPGA編解碼SDI的工程源碼及博客介紹;既有基于GS2971/GS2972的SDI編解碼,也有基于GTP/GTX資源的SDI編解碼;專欄地址鏈接:點擊直接前往

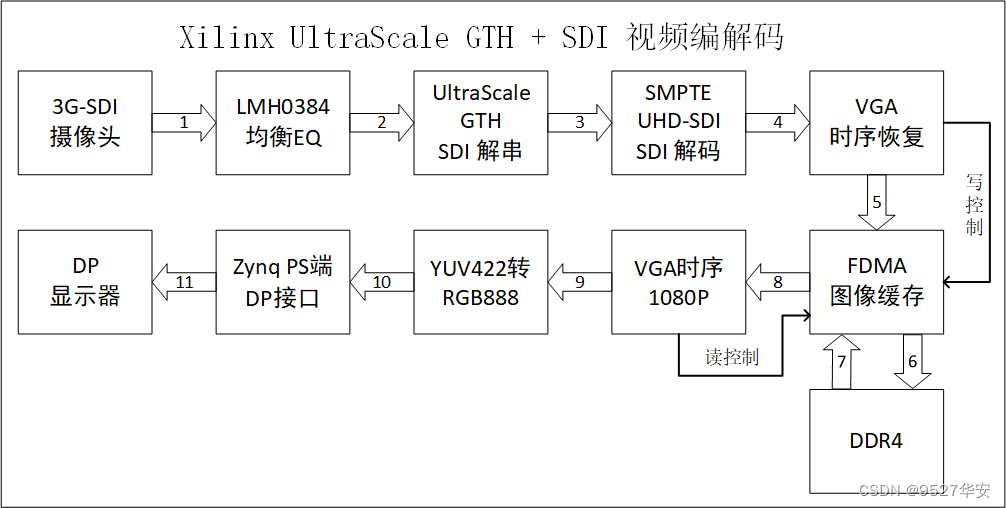

3、詳細設計方案

本文使用Xilinx的Zynq UltraScale+MPSoCs–xczu7ev-ffvc1156-2-i 型號的FPGA實現UltraScale GTH + SDI 視頻編解碼;攝像頭為標準的3G-SDI攝像頭,開發板板載LMH0384芯片,SDI視頻經過LMH0384起到均衡EQ的作用,也可以理解為單端轉差分;然后調用Xilinx官方的UltraScale GTH IP核實現SDI視頻的解串與串化,IP配置為GTH-3G-SDI模式,該模式專門用于SDI視頻協議的解串與串化;然后調用Xilinx官方的SMPTE UHD-SDI IP核實現SDI視頻解碼與編碼,該IP支持3G-SDI、6G-SDI、12G-SDI等視頻編解碼,本設計配置為3G-SDI模式;SDI視頻接收流程至此已經由原始的同軸線傳輸的單端視頻變為了并行的視頻數據了,此時可以作為圖像處理的輸入源了,可以緩存、顏色轉換、縮放等等操作;本設計采用DP+SDI同步輸出方式;首先需要將圖像緩存進DDR4中,所以需要用到VGA時序恢復模塊,將SDI視頻有效數據恢復為帶有行同步信號(hs)、場同步信號(vs)、數據有效信號(de)、像素數據(data)的標準VGA時序;然后使用我常用的FDMA圖像緩存架構將SDI視頻寫入DDR4再讀出,圖像在DDR4中做三幀緩存,如果你覺得延時太高,可以選擇緩存2幀即可;使用VTC模塊,即VGA時序生成模塊,分辨率為1080P@60Hz,VTC模塊控制DFMA模塊從DDR4中把視頻讀出來;SDI視頻從DDR4中讀出來時為YUV422格式,需要使用YUV422轉RGB888模塊將SDI視頻轉換為24位的RGB888,此時的視頻就是標準的VGA時序視頻了;再調用Zynq軟核,打開其DP接口的配置并引出DP輸入時序信號,將VGA時序視頻輸入DP即可;DP的輸出功能在Vitis SDK中以C語言軟件方式實現,然后輸出DP顯示器即可;

提供2套vivado2022.2版本的FPGA工程源碼,兩套工程的區別在于SDI攝像頭的路數,第一套工程只用到了1路SDI攝像頭做回環;第二套工程用到了4路SDI攝像頭做回環;詳情如下:

vivado工程1:1路SDI輸入,DDR4做三幀緩存后DP輸出;

vivado工程2:4路SDI輸入,DDR4做三幀緩存后DP輸出;

設計框圖

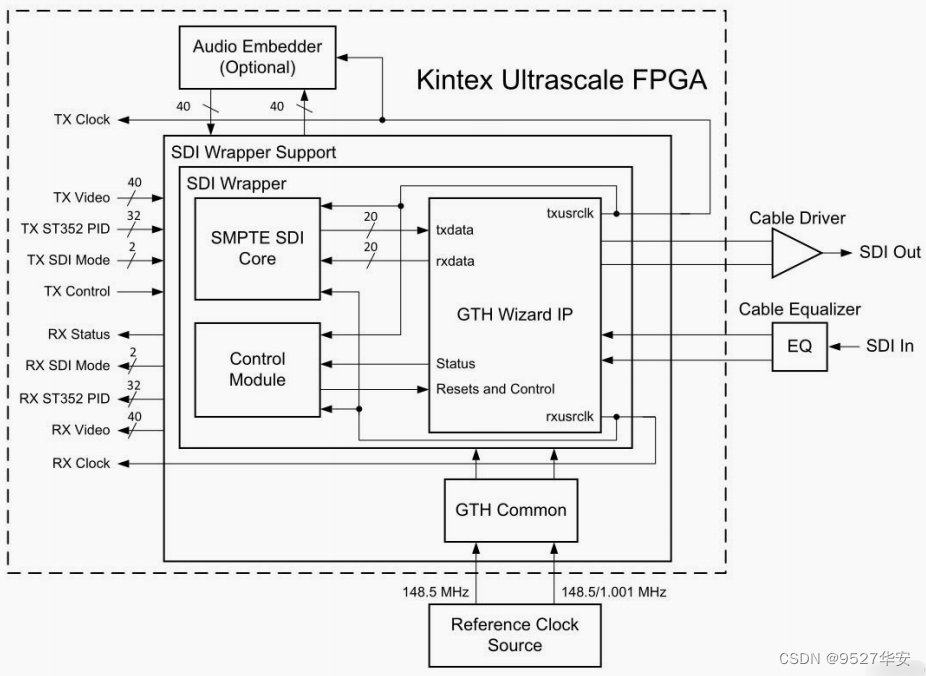

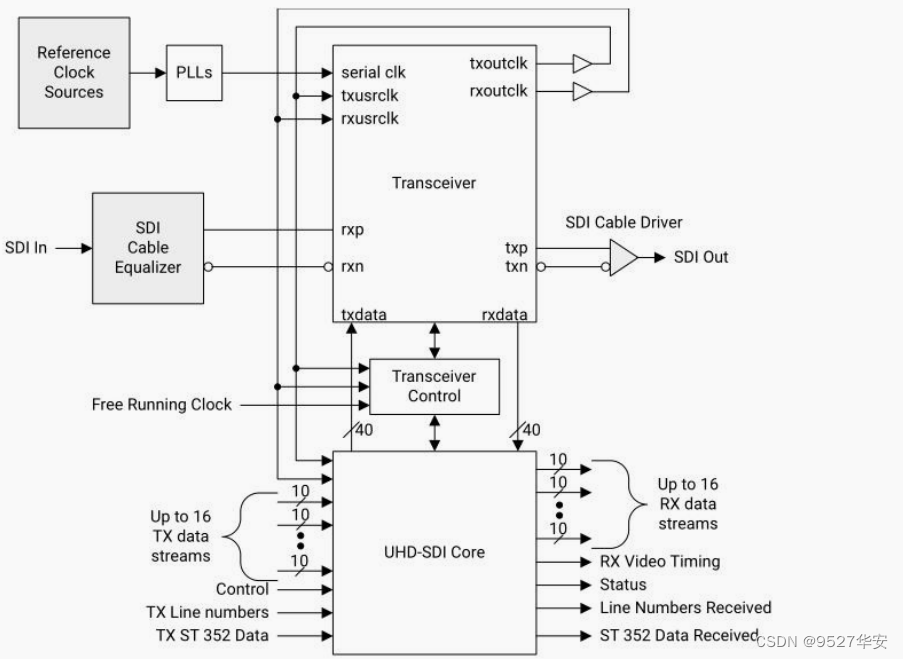

本設計參考了Xilinx官方設計文檔,官方的參考設計框圖如下:

具體到本工程詳細設計方案框圖如下:

框圖解釋:箭頭表示數據流向,箭頭內文字表示數據格式,箭頭外數字表示數據流向的步驟;

3G-SDI攝像頭

大體就是這種相機:

分辨率:1920x1080@60Hz;

視頻格式:YUV422;

數據速率:2.97Gbps;

輸出方式:BNC頭同軸線輸出;

LMH0384均衡EQ

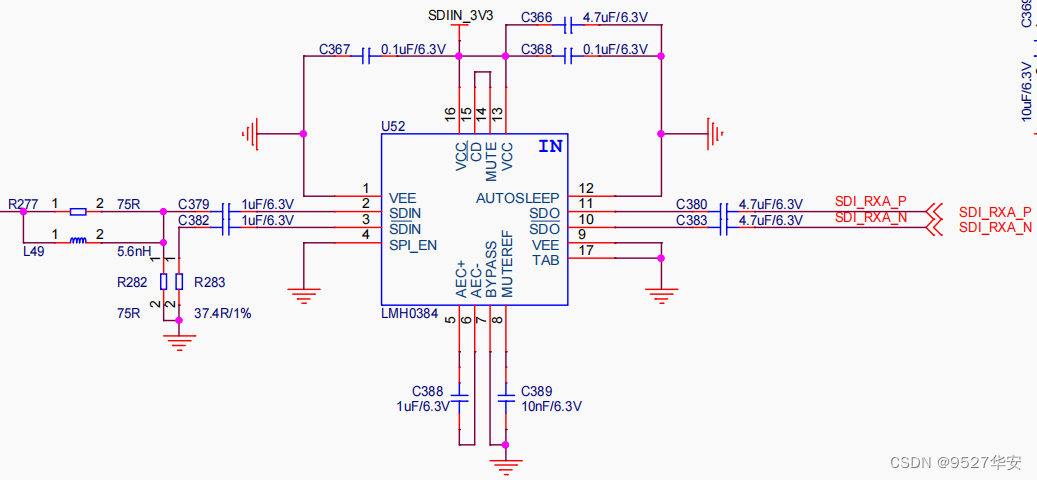

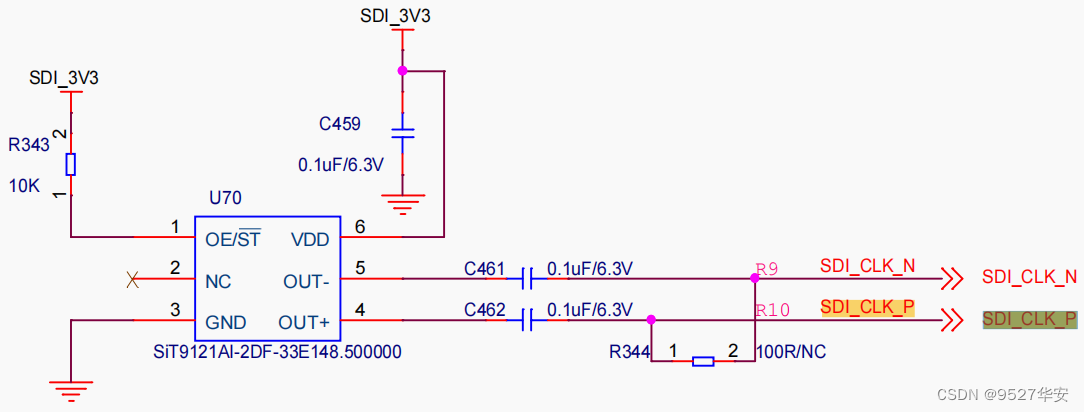

開發板板載LMH0384芯片,SDI視頻經過LMH0384起到均衡EQ的作用,也可以理解為單端轉差分;原理圖部分如下:

UltraScale GTH 的SDI模式應用

關于UltraScale GTH介紹最詳細的肯定是Xilinx官方的《ug576-ultrascale-gth-transceivers》,我們以此來解讀:

《ug576-ultrascale-gth-transceivers》的PDF文檔我已放在了資料包里,文章末尾有獲取方式;

我用到的開發板FPGA型號為Kirtex7-UltraScale-xcku060-ffva1156-2-i;UltraScale GTH的收發速度為 500 Mb/s 到 16.375 Gb/s 之間,比GTH高出3G;UltraScale GTH收發器支持不同的串行傳輸接口或協議,比如 PCIE 1.1/2.0 接口、萬兆網 XUAI 接口、OC-48、串行 RapidIO 接口、 SATA(Serial ATA) 接口、數字分量串行接口(SDI)等等;

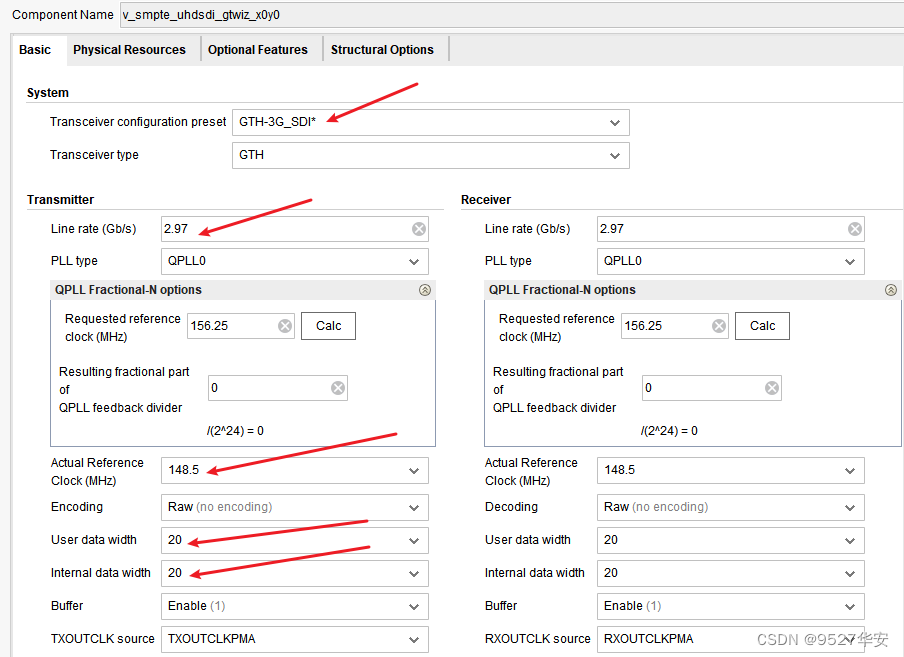

工程調用UltraScale GTH配置為GTH-3G-SDI模式,該模式專門用于SDI視頻協議的解串與串化;代碼位置如下:

UltraScale GTH基本配置如下:板載差分晶振148.5M,線速率配置為2.97G,協議類型配置為GTH-3G-SDI;

還有其他的配置選項,比如勾選DRP動態配置接口等,具體請參考工程;

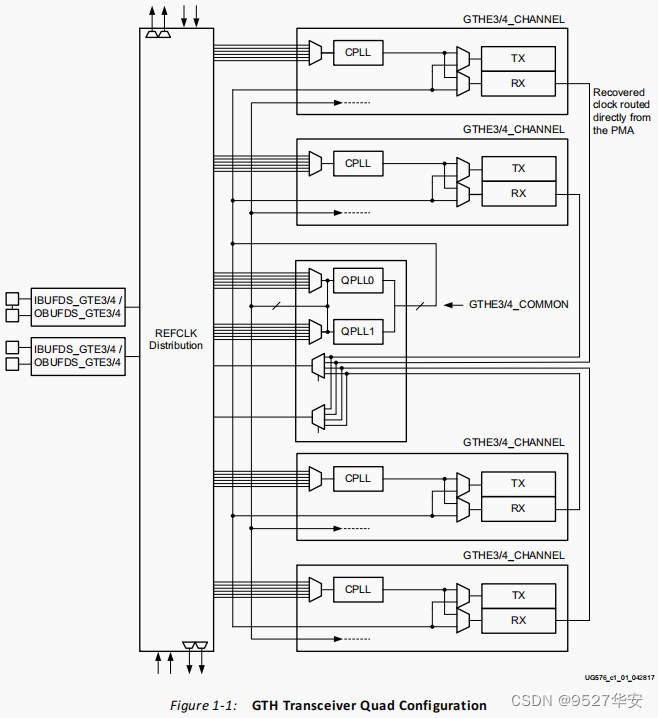

UltraScale GTH 基本結構

Xilinx 以 Quad 來對串行高速收發器進行分組,四個串行高速收發器和一個 COMMOM(QPLL)組成一個 Quad,每一個串行高速收發器稱為一個 Channel(通道),下圖為UltraScale GTH 收發器在Kintex7 UltraScale FPGA 芯片中的示意圖:《ug576-ultrascale-gth-transceivers》第19頁;

在 Ultrascale/Ultrascale+架構系列的 FPGA 中,GTH 高速收發器通常使用 Quad 來劃分,一個 Quad 由四個GTHE3/4_CHANNEL 原語和一個 GTHE3/4_COMMON 原語組成。每個GTHE3/4_COMMON 中包含兩個 LC-tank pll(QPLL0 和 QPLL1)。只有在應用程序中使用 QPLL 時,才需要實例化 GTHE3/4_COMMON。每個 GTHE3/4_CHANNEL 由一個 channel PLL(CPLL)、一個 transmitter,和一個 receiver 組成。一個參考時鐘可以直接連接到一個 GTHE3/4_CHANNEL 原語,而不需要實例化 GTHE3/4_COMMON;

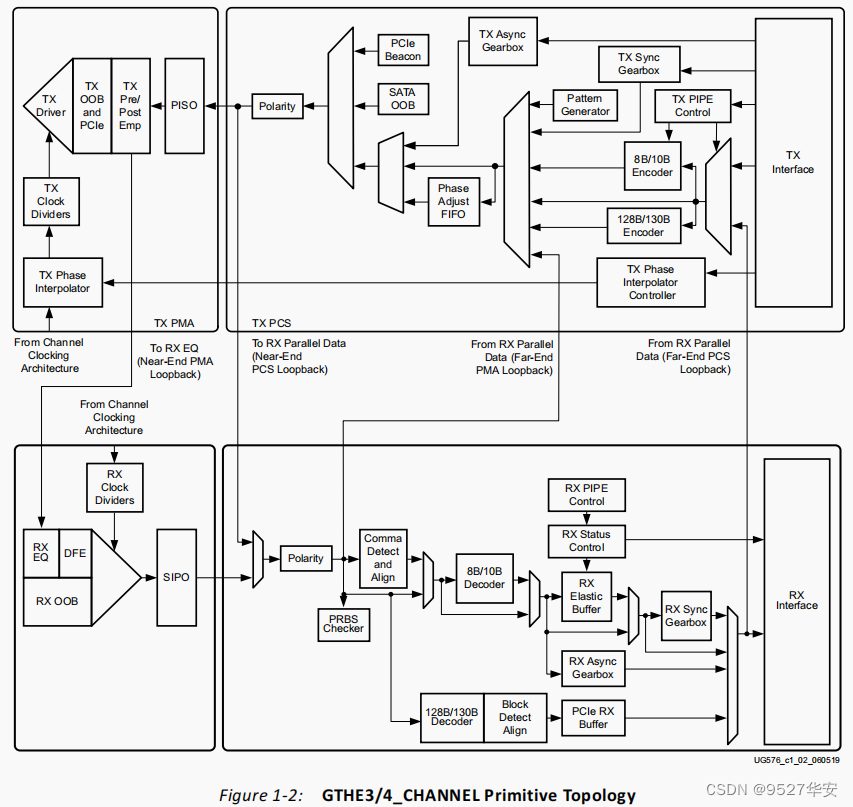

Ultrascale GTH 收發器的發送端和接收端功能是相互獨立,都是由 Physical Media Attachment(物理媒介適配層 PMA)和Physical Coding Sublayer(物理編碼子層 PCS)組成。PMA 內部集成了串并轉換(PISO)、預加重、接收均衡、時鐘發生器和時鐘恢復等;PCS 內部集成了GTH-3G-SDI、彈性緩沖區、通道綁定和時鐘修正等,每個 GTHE3/4_CHANNEL源語的邏輯電路如下圖所示:《ug576-ultrascale-gth-transceivers》第20頁;

這里說多了意義不大,因為沒有做過幾個大的項目是不會理解這里面的東西的,對于初次使用或者想快速使用者而言,更多的精力應該關注IP核的調用和使用,后面我也會重點將到IP核的調用和使用;

參考時鐘的選擇和分配

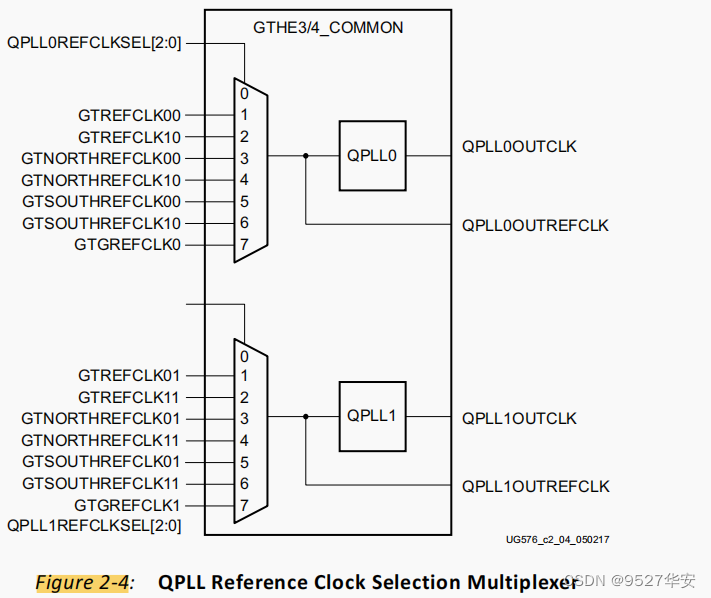

UltraScale 器件中的 GTH 收發器提供了不同的參考時鐘輸入選項。參考時鐘選擇架構支持 QPLL0、QLPLL1 和CPLL。從架構上講,每個 Quad 包含四個 GTHE3/4_CHANNEL 原語,一個 GTHE3/4_COMMON 原語,兩個專用的外部參考時鐘引腳對,以及專用的參考時鐘路由。如果使用到了高性能 QPLL,則必須實例化 GTHE3/4_COMMON,如下面 GTHE3/4_COMMON 時鐘多路復用器結構的詳細視圖所示,(《ug576-ultrascale-gth-transceivers》第33頁)在一個 Quad 中有 6 個參考時鐘引腳對,兩個本地參考時鐘引腳對:GTREFCLK0或GTREFCLK1,兩個參考時鐘引腳對來自上面的兩個Quads:GTSOUTHREFCLK0或 GTSOUTHREFCLK1,兩個參考時鐘引腳對來自下面的兩個 Quads: GTNORTHREFCLK0 或GTNORTHREFCLK1。

由下圖可知,這個 GTHE3/4_COMMON 就是一個基準時鐘選擇器,用來選擇不同來源的時鐘作為收發器的基準時鐘。GTHE3/4_COMMON 支持 7 種基準時鐘源的選擇。當然,一般來說,性能最好的基準時鐘源就是最近的這個 Quad 自身的 refclk,也就是 GTREFCLK00 和 GTREFCLK10。在高清視頻傳輸中,美國、加拿大等使用 NTSC 標準,基準時鐘為 148.35MHZ、74.176MHZ。中國、德國等國家采用的 PAL 標準,基準時鐘為 148.5MHZ 和 74.25MHZ。在高清視頻領域,這兩者的差別只在于基準時鐘,而視頻時序都是相同的。這也造成了在設備上我們經常看到兩種幀率,如 60hz 和 59.94hz。所以本設計GTH的參考時鐘為差分148.5M,原理圖如下:

UltraScale GTH 發送和接收處理流程

首先用戶邏輯數據經過GTH-3G-SDI后,進入一個發送緩存區(Phase Adjust FIFO),該緩沖區主要是 PMA 子層和 PCS 子層兩個時鐘域的時鐘隔離,解決兩者時鐘速率匹配和相位差異的問題,最后經過高速 Serdes 進行并串轉換(PISO),有必要的話,可以進行預加重(TX Pre-emphasis)、后加重。值得一提的是,如果在 PCB 設計時不慎將 TXP 和 TXN 差分引腳交叉連接,則可以通過極性控制(Polarity)來彌補這個設計錯誤。接收端和發送端過程相反,相似點較多,這里就不贅述了,需要注意的是 RX 接收端的彈性緩沖區,其具有時鐘糾正和通道綁定功能。這里的每一個功能點都可以寫一篇論文甚至是一本書,所以這里只需要知道個概念即可,在具體的項目中回具體用到,還是那句話:對于初次使用或者想快速使用者而言,更多的精力應該關注IP核的調用和使用。

UltraScale GTH 發送接口

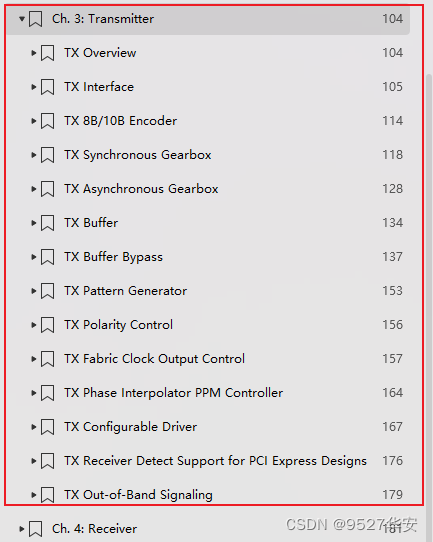

《ug576-ultrascale-gth-transceivers》的第104到179頁詳細介紹了發送處理流程,其中大部分內容對于用戶而言可以不去深究,因為手冊講的基本都是他自己的設計思想,留給用戶可操作的接口并不多,基于此思路,我們重點講講UltraScale GTH例化時留給用戶的發送部分需要用到的接口;

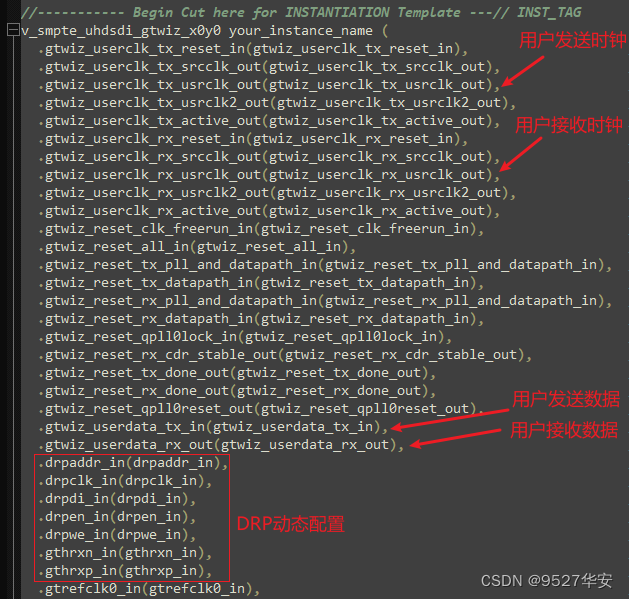

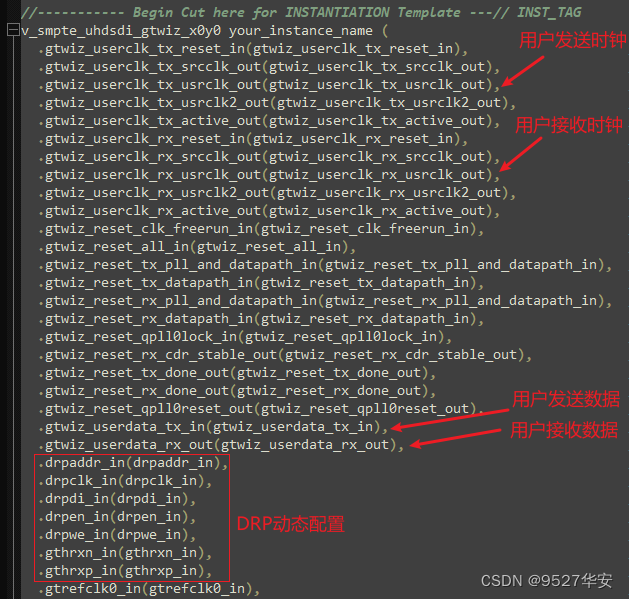

用戶只需要關心發送接口的時鐘和數據即可,UltraScale GTH例化模塊的這部分接口如下:該文件名為例化GTH后官方生成的供例化的文件;

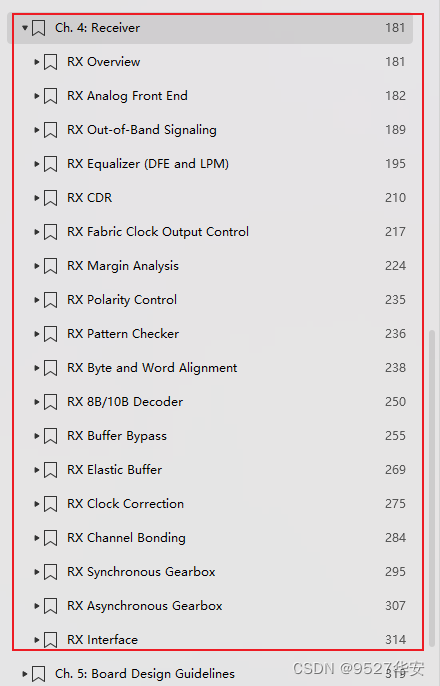

UltraScale GTH 接收接口

《ug576-ultrascale-gth-transceivers》的第181到314頁詳細介紹了發送處理流程,其中大部分內容對于用戶而言可以不去深究,因為手冊講的基本都是他自己的設計思想,留給用戶可操作的接口并不多,基于此思路,我們重點講講UltraScale GTH 例化時留給用戶的發送部分需要用到的接口;

用戶只需要關心接收接口的時鐘和數據即可,UltraScale GTH例化模塊的這部分接口如下:該文件名為例化GTH后官方生成的供例化的文件;

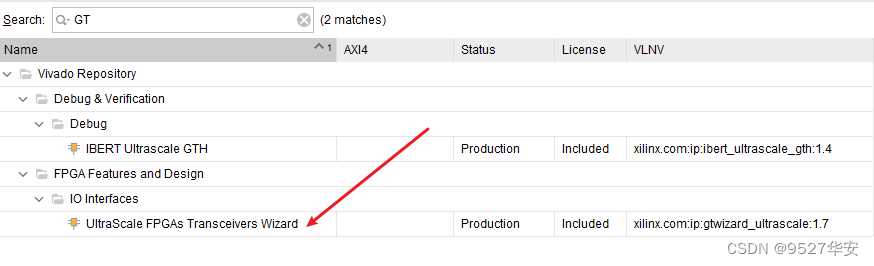

UltraScale GTH IP核調用和使用

UltraScale GTH基本配置如下:板載差分晶振148.5M,線速率配置為2.97G,協議類型配置為GTH-3G-SDI;

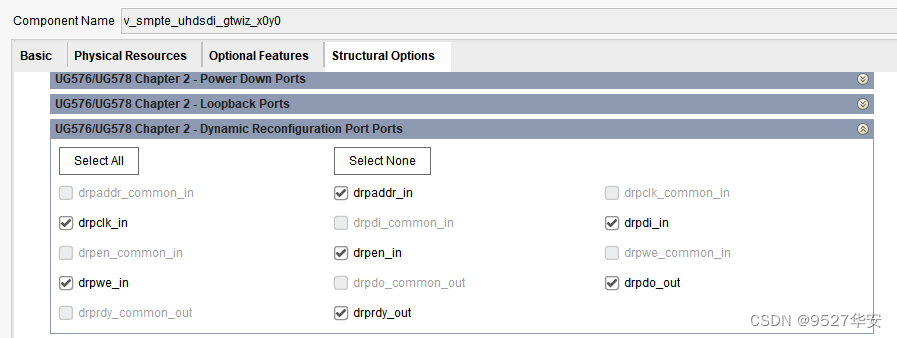

為了適應三種SD-SDI、HD-SDI 和 3G-SDI 不同模式,需要對GTH做變速和復位操作,所以需要打開DRP接口,如下:

更多GTH配置細節請參考vivado工程;

UltraScale GTH 控制說明

為了適應三種SD-SDI、HD-SDI 和 3G-SDI 不同模式,需要對GTH做變速和復位操作,主要通過DRP接口完成,為此,使用了Xilinx官方的參考代碼,UltraScale GTH 控制部分代碼如下:

UltraScale GTH 控制模塊包含以下幾種功能:1、用于控制 GTH 收發器的復位邏輯;2、允許 RX 和 TX 串行分頻器進行動態切換,以支持 SD-SDI、HD-SDI 和 3G-SDI 不同模式;3、TX 參考時鐘的動態切換,用以支持 HD-SDI和 3G-SDI 標準中的兩種不同比特率: HD-SDI 模式下的 1.485 Gb/s 和 1.485/1.001 Gb/s 比特率、3G-SDI 模式下的2.97 Gb/s 和 2.97/1.001 Gb/s 比特率;4、數據恢復單元,用于以 SD-SDI 模式下恢復數據;5、RX 比特率檢測,以確定接收器正在接收整數幀速率信號還是分數幀速率信號。

詳細請參考代碼;

SMPTE UHD-SDI詳解

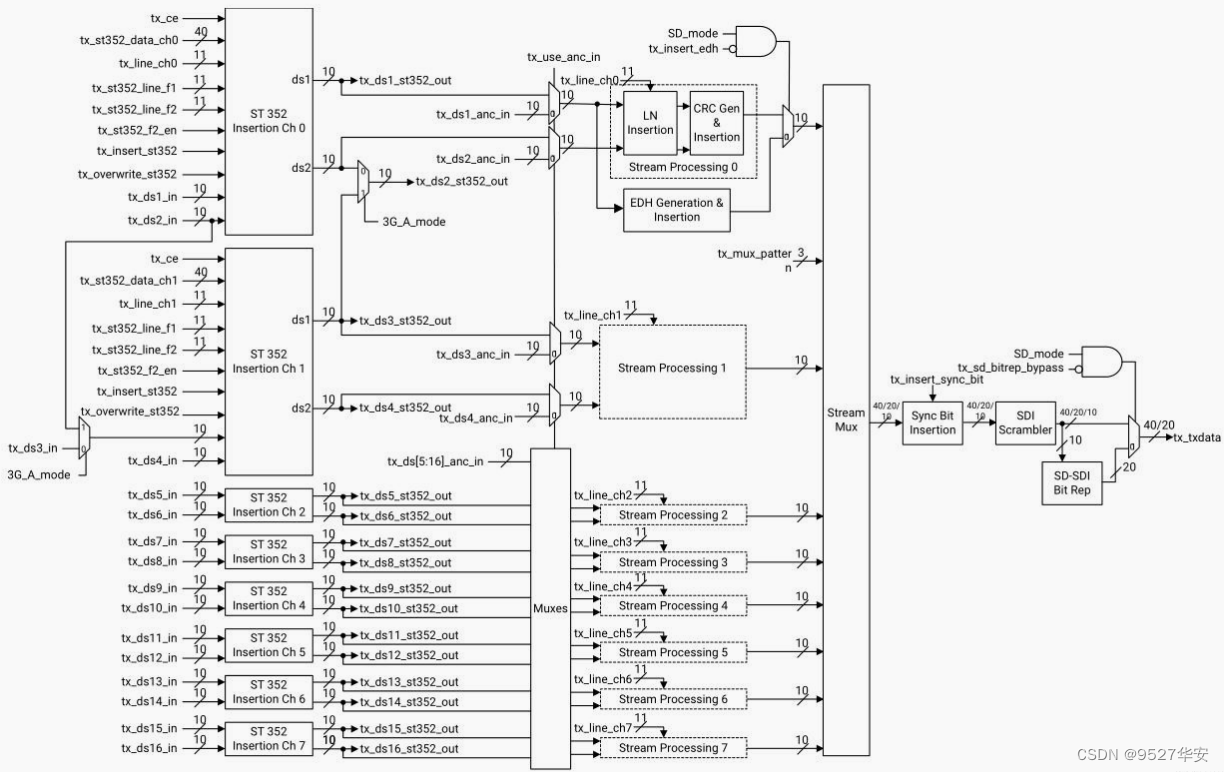

調用Xilinx官方的SMPTE UHD-SDI IP核實現SDI視頻解碼與編碼,該IP支持3G-SDI、6G-SDI、12G-SDI等視頻編解碼,本設計配置為3G-SDI模式;根據官方手冊,SMPTE UHD-SDI數據收發架構如下:

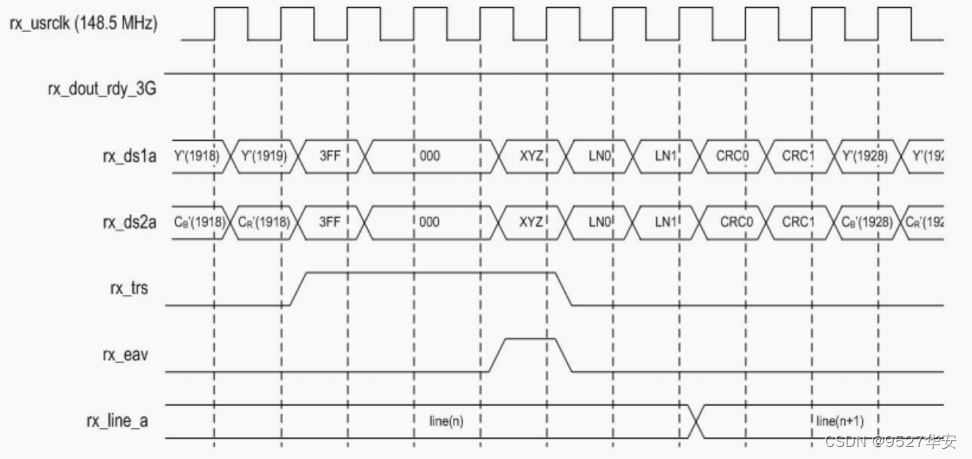

SMPTE UHD-SDI 接收

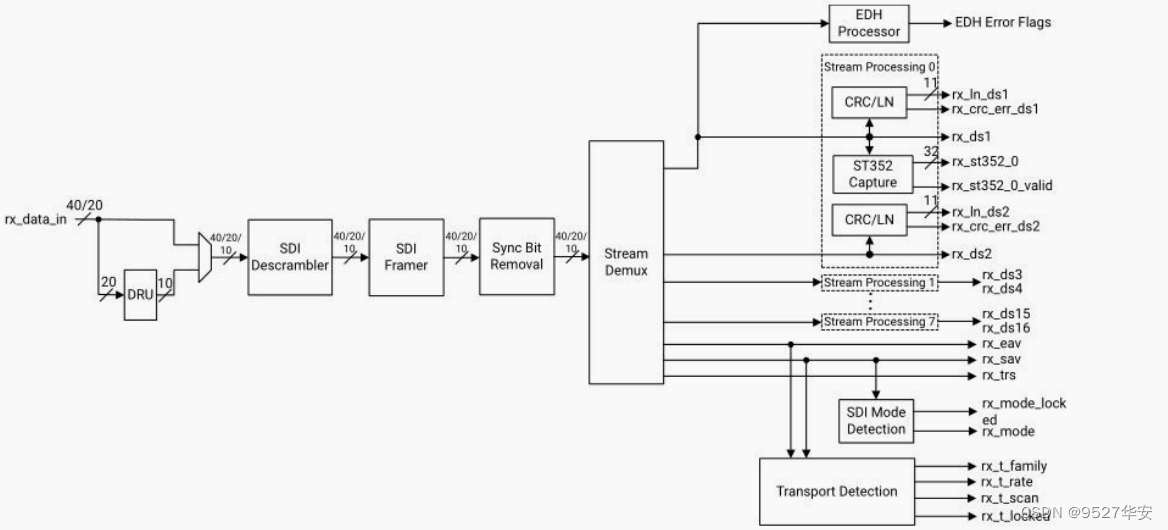

SMPTE UHD-SDI 接收端的框圖如下:

來自串行收發器 RX 的數據通過 rx_data_in 端口進入 SMPTE UHD-SDI接收器,對于 SD、HD 和 3G 模式,每個時鐘周期 20 位;對于 6G 和 12G 模式,每個時鐘周期 40 位。在 SD 模式下,rx_data_in 上的 20 位數據轉到 DRU (data recovery unit), DRU 從 11 倍過采樣數據中恢復 10 位數據。數據由 SDI解擾器解擾,然后由 SDI 成幀器進行字對齊。之后就是同步位恢復功能。 此功能可還原由變送器修改的 3FF 和 000值,以減少 6G 和 12G-SDI 模式下的運行長度。這三個模塊以全 rx_clk 速度運行,并根據 SDI 模式在每個時鐘周期處理 40、20 或 10 位數據。 數據進入 stream demux,該 demux 確定有多少數據流交織在一起,然后在單獨的數據路徑上分離每個數據流,最多支持 16 個數據流。每路數據流進入一個處理單元,該單元進行 CRC 錯誤檢查、行號捕獲和 ST 352 包捕獲。還可以從 stream demux 中

提取視頻時序并產生 rx_eav,rx_sav 和 rx_trs 時序信號。這些時序信號由 SDI 模式檢測并給傳輸檢測模塊使用。

SMPTE UHD-SDI 發送

SMPTE UHD-SDI 發射端的框圖如下:

SMPTE UHD-SDI最多可以支持 16 路 SDI 數據流,數據流首先通過 ST 352 插入模塊,可以有選擇地插入 ST 352 有效負載 ID 數據包,從 ST 352 插入模塊輸出的數據流稱為 tx_ds1_st352_out 至tx_ds16_st352_out。輸出這些流可以方便用戶在 ST 352 數據包后插入輔助數據。 發送器的其余部分可以直接使用ST 352 數據包插入模塊輸出的流,也可以使用 16 個 tx_ds1_anc_in 到 tx_ds16_anc_in 數據流。請注意,如果使用tx_dsn_anc_in 數據流,則它們必須是完整的 SDI 數據流,而不僅僅是輔助數據。通常情況下,每個 Y/C 數據流對的 Y 數據流中只插入 ST 352 包。而在 3G-SDI level A mode-only 模式下,數據流 1 和數據流 2 都必須插入 ST 352 報文。然后每對 Y / C 數據流經過一個數據流處理模塊,該模塊可以進行進行行號插入和 CRC 生成及插入。在流處理之后,數據流被 MUX 交織,形成 40、20 或 10 位寬的多路復用 SDI 數據流。然后,由 SDI 加擾器對多路復用的數據流進行加擾。最后,數據在 tx_txdata 端口上輸出到對應的串行收發器。

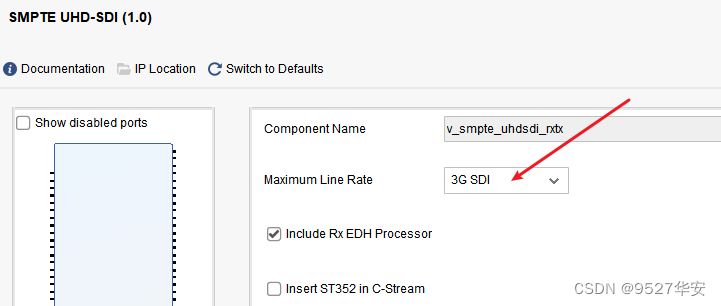

SMPTE UHD-SDI IP核調用和使用

SMPTE UHD-SDI配置界面很簡單,本設計配置為3G-SDI模式,如下:

SMPTE UHD-SDI的使用請參考工程代碼,因為接口很多,這里寫不下;

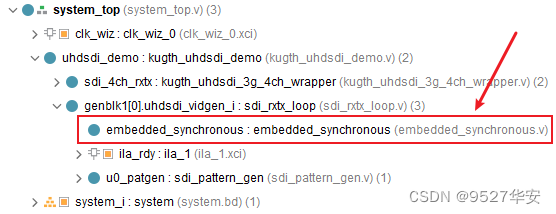

VGA時序恢復

本設計采用緩存回環方式,所以需要用到VGA時序恢復模塊,將SDI視頻有效數據恢復為帶有行同步信號(hs)、場同步信號(vs)、數據有效信號(de)、像素數據(data)的標準VGA時序;代碼位置如下:

VGA時序恢復模塊頂層接口如下:

VGA時序恢復模塊的輸入來自于SMPTE UHD-SDI IP核的輸出,該IP的輸出提供了 rx_eav、rx_sav、rx_trs 這些表示同步字信息的信號,這些信號的時序關系如下圖:

從上圖可以看到,rx_trs 與四個同步字同步,rx_eav 在XYZ(嵌入式同步字第四個字)拉高一個時鐘周期表示為有效像素結束。rx_sav 在上圖中并沒有表示出來,但是類似的,rx_sav 在XYZ(嵌入式同步字第四個字)拉高一個時鐘周期表示為有效像素開始。在模塊 embedded_synchronous 中就是根據這幾個信號提取圖像區域的。對于數據流,我們前面也已經提及過,SDI 信號使用20bits 表示一個像素點,分為 10bits 亮度數據Y,10bits 色度數據 C。在接收部分,對應的是 rx_ds1a、rx_ds2a,我們將兩個 10bits 數據拼接為一個 20bits 數據。 由于我們已經有了時序同步信號,不需要再數據口中做序列檢測提取同步字。我們只需要在 rx_trs 信號到來時, 同步獲取對應的控制字即可,從而解出對應的 H、V 、F 標志位。通過這些標志信號提取 de_p 有效像素區域。 有了這些信號后,我們就可以按照我們熟悉的行場同步的方式來處理圖像數據了。

圖像緩存

經常看我博客的老粉應該都知道,我做圖像緩存的套路是FDMA,他的作用是將圖像送入DDR中做3幀緩存再讀出顯示,目的是匹配輸入輸出的時鐘差和提高輸出視頻質量,關于FDMA,請參考我之前的博客,博客地址:點擊直接前往

VTC模塊(VGA時序)

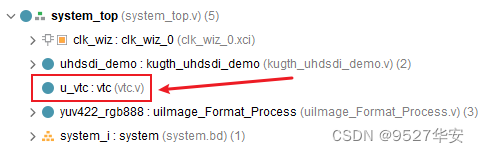

使用VTC模塊,即VGA時序生成模塊,分辨率為1080P@60Hz,VTC模塊控制DFMA模塊從DDR4中把視頻讀出來;該模塊很簡單,不需要過多描述,代碼位置如下:

YUV422轉RGB888模塊

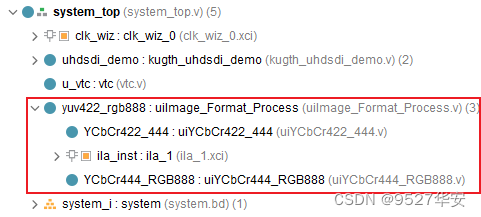

SDI視頻從DDR4中讀出來時為YUV422格式,需要使用YUV422轉RGB888模塊將SDI視頻轉換為24位的RGB888,此時的視頻就是標準的VGA時序視頻了;代碼位置如下:

由上圖可知,YUV422轉RGB888模塊由YUV422轉YUV444模塊和YUV444轉RGB888模塊兩個模塊組成,兩者流水線操作;

DP輸出

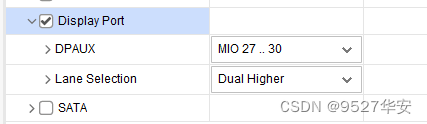

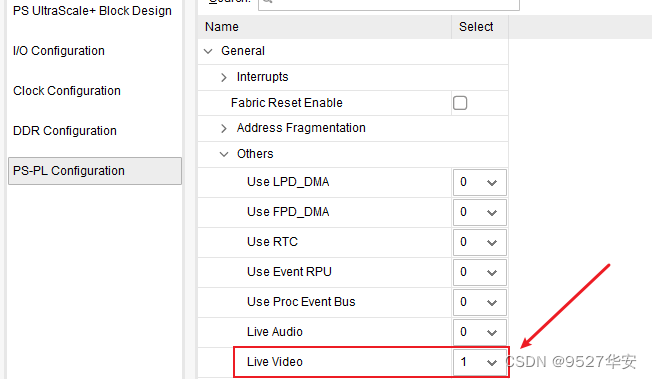

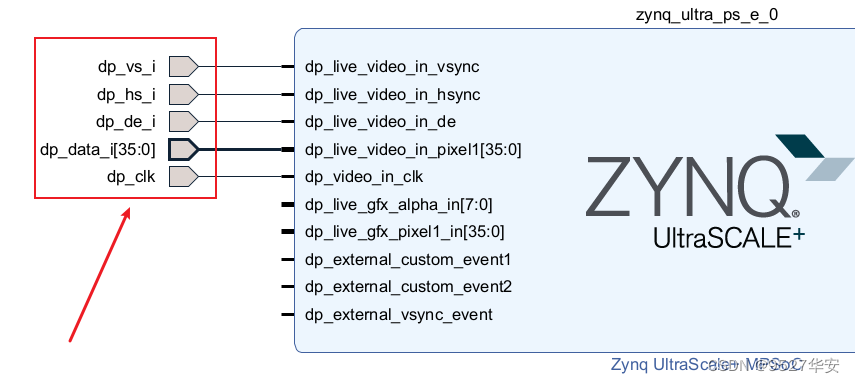

調用Zynq,配置DP接口,如下:

將VGA時序視頻輸入DP即可;DP的輸出功能在Vitis SDK中以C語言軟件方式實現,然后輸出DP顯示器即可;

4、vivado工程1:1路SDI視頻解碼–DP輸出

PL端邏輯設計

開發板FPGA型號:Xilinx–Zynq UltraScale+MPSoCs–xczu7ev-ffvc1156-2-i;

開發環境:Vivado2022.2;

輸入:1路3G-SDI攝像頭,分辨率1920x1080@60Hz;

輸出:DP;分辨率1920x1080@60Hz;

應用:FPGA高端項目:FPGA高端項目:UltraScale GTH + SDI 視頻解碼,SDI轉DP輸出;

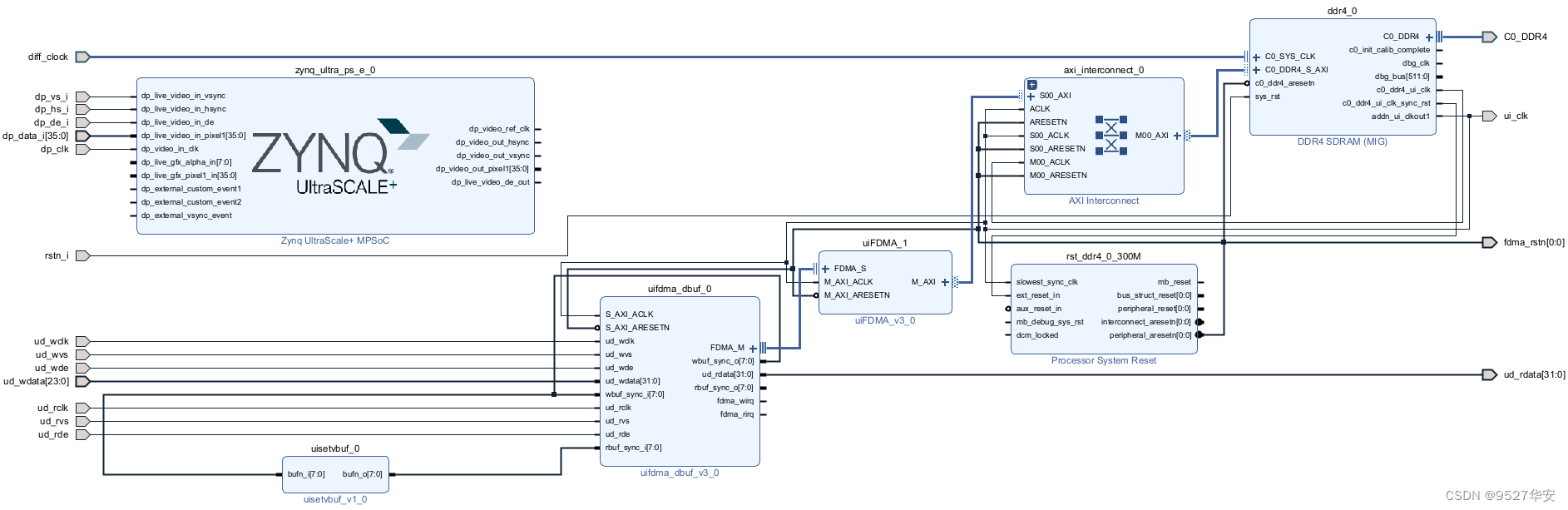

Block Design如下:

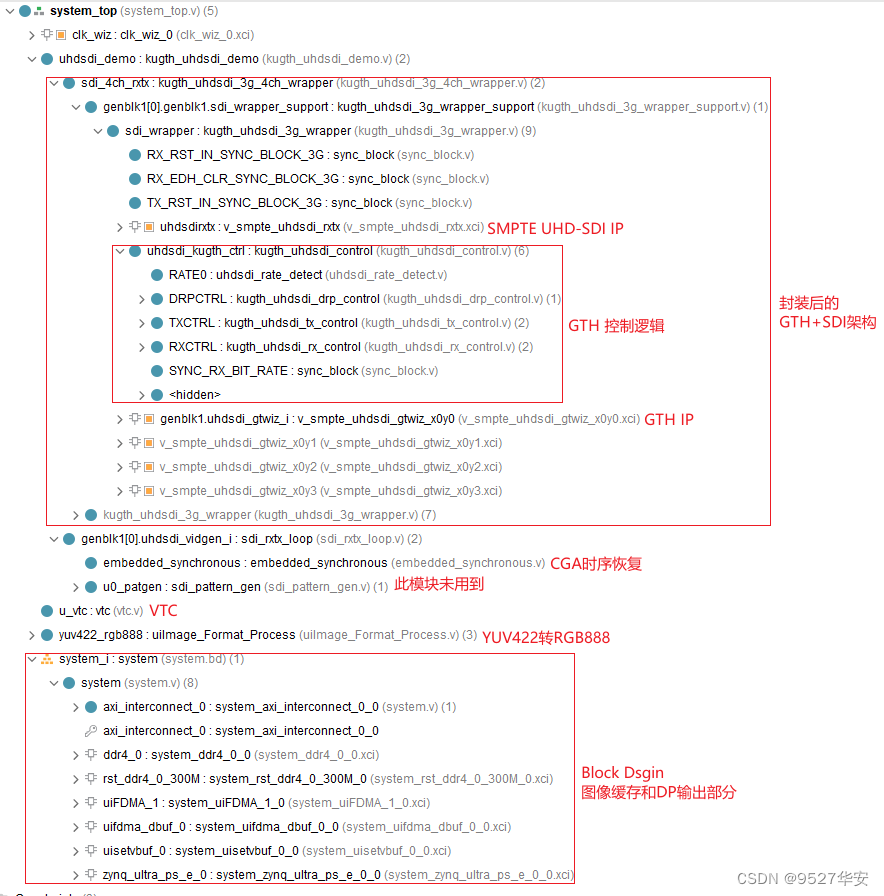

工程代碼架構如下:

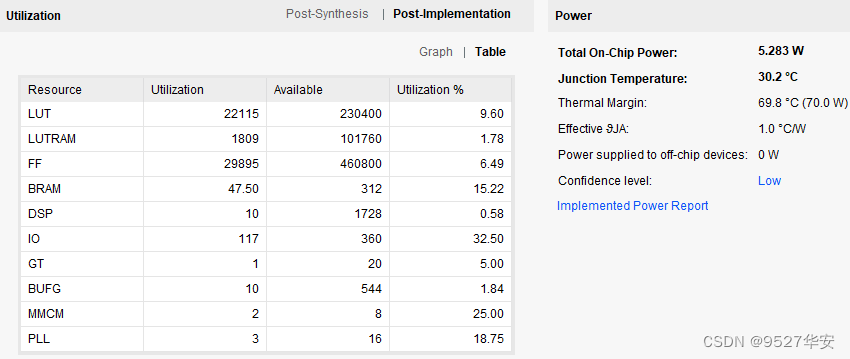

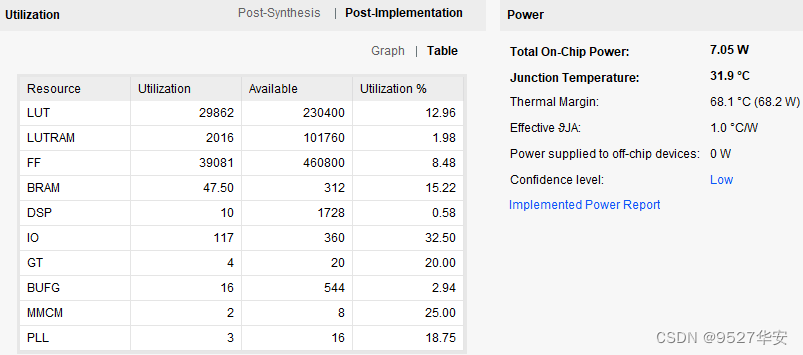

綜合編譯完成后的FPGA資源消耗和功耗預估如下:

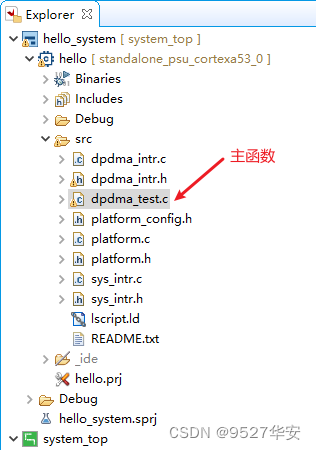

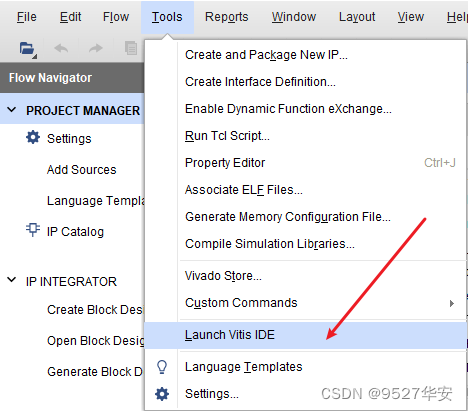

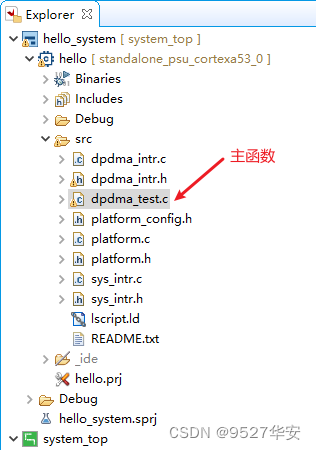

PS端Vitis SDK 軟件設計

PS端Vitis SDK 軟件采用C語言設計,調用Xilinx提供的DP驅動API實現DP輸出,代碼架構如下:

主函數很簡單,源碼如下:

int main(){Xil_DCacheDisable();Xil_ICacheDisable();init_intr_sys();xil_printf("DPDMA Generic Video Example Test \r\n");while(1);return XST_SUCCESS;

}

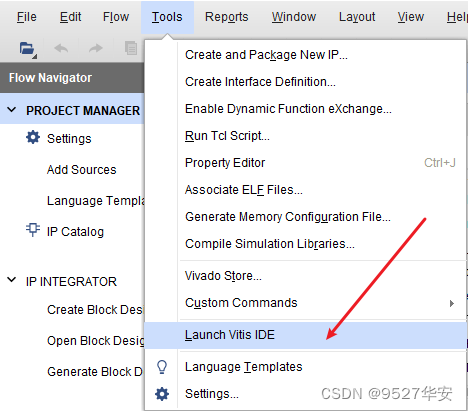

加載SDK的方法如下:

5、vivado工程2:4路SDI視頻解碼–DP輸出

PL端邏輯設計

開發板FPGA型號:Xilinx–Zynq UltraScale+MPSoCs–xczu7ev-ffvc1156-2-i;

開發環境:Vivado2022.2;

輸入:4路3G-SDI攝像頭,分辨率1920x1080@60Hz;

輸出:DP;分辨率1920x1080@60Hz;

應用:FPGA高端項目:FPGA高端項目:UltraScale GTH + SDI 視頻解碼,SDI轉DP輸出;

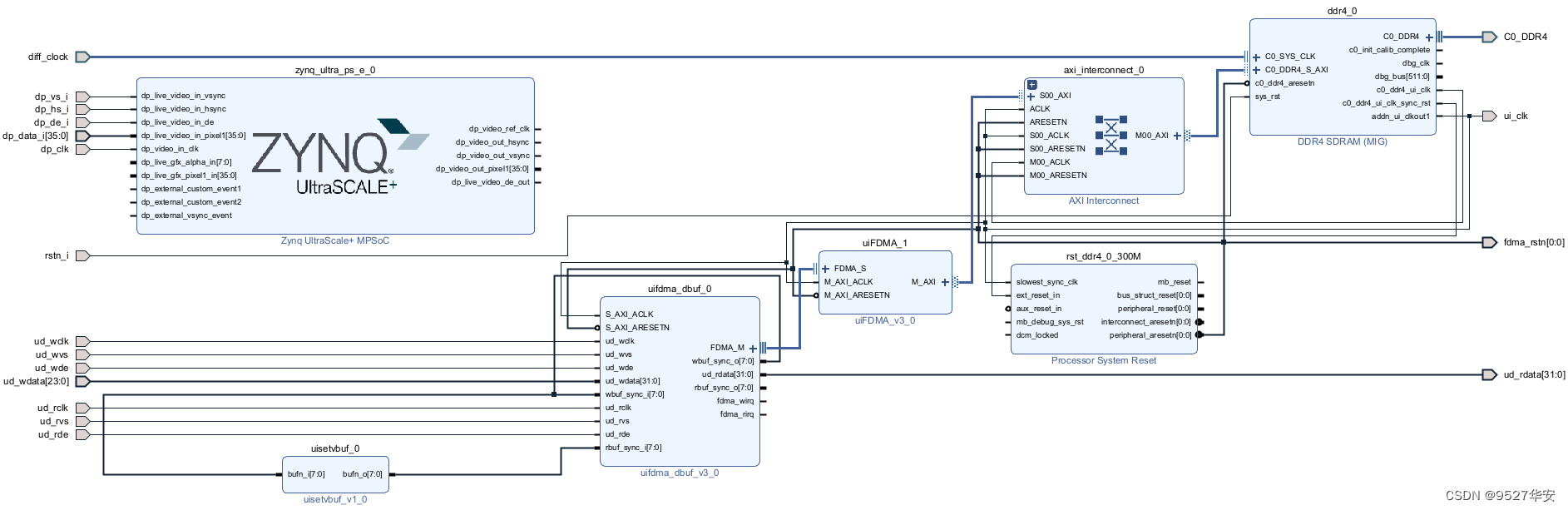

Block Design如下:

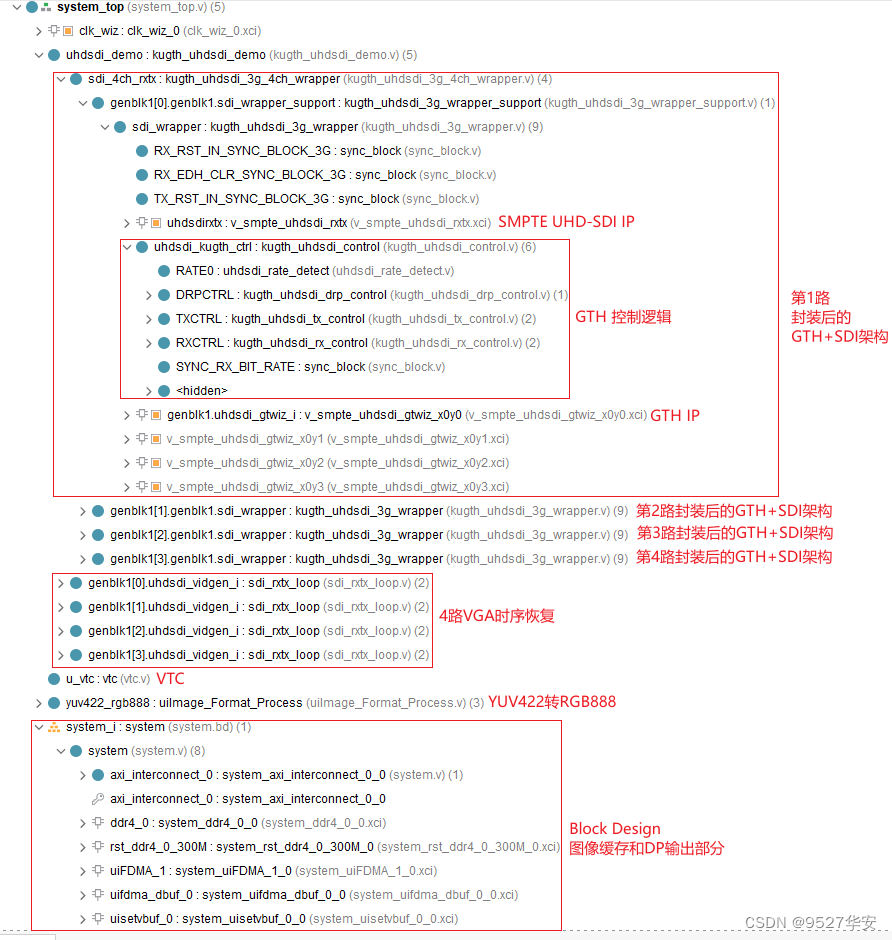

工程代碼架構如下:

綜合編譯完成后的FPGA資源消耗和功耗預估如下:

PS端Vitis SDK 軟件設計

PS端Vitis SDK 軟件采用C語言設計,調用Xilinx提供的DP驅動API實現DP輸出,代碼架構如下:

主函數很簡單,源碼如下:

int main(){Xil_DCacheDisable();Xil_ICacheDisable();init_intr_sys();xil_printf("DPDMA Generic Video Example Test \r\n");while(1);return XST_SUCCESS;

}

加載SDK的方法如下:

6、工程移植說明

vivado版本不一致處理

1:如果你的vivado版本與本工程vivado版本一致,則直接打開工程;

2:如果你的vivado版本低于本工程vivado版本,則需要打開工程后,點擊文件–>另存為;但此方法并不保險,最保險的方法是將你的vivado版本升級到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解決如下:

打開工程后會發現IP都被鎖住了,如下:

此時需要升級IP,操作如下:

FPGA型號不一致處理

如果你的FPGA型號與我的不一致,則需要更改FPGA型號,操作如下:

更改FPGA型號后還需要升級IP,升級IP的方法前面已經講述了;

其他注意事項

1:由于每個板子的DDR不一定完全一樣,所以MIG IP需要根據你自己的原理圖進行配置,甚至可以直接刪掉我這里原工程的MIG并重新添加IP,重新配置;

2:根據你自己的原理圖修改引腳約束,在xdc文件中修改即可;

3:純FPGA移植到Zynq需要在工程中添加zynq軟核;

7、上板調試驗證

準備工作

FPGA開發板;

3G-SDI相機;

BNC轉SMA同軸線;

SDI轉HDMI盒子;

顯示器,需要支持1080P;

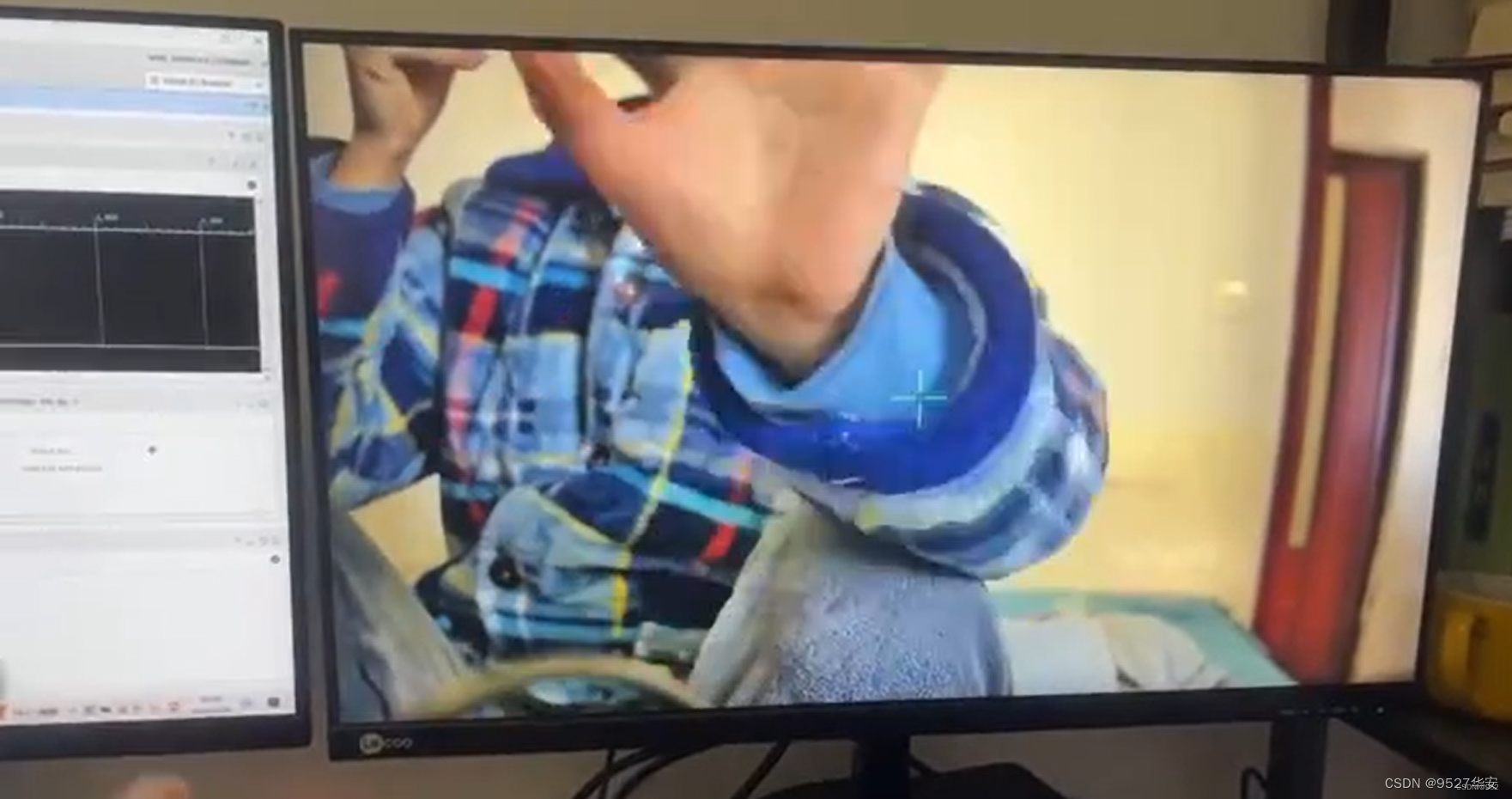

輸出演示

輸出演示如下:

8、福利:工程代碼的獲取

福利:工程代碼的獲取

代碼太大,無法郵箱發送,以某度網盤鏈接方式發送,

資料獲取方式:私,或者文章末尾的V名片。

網盤資料如下:

)

)

進程)

MBIM協議詳解)

)