GPIO 深度解析:引腳特性、工作模式、速度選型及上下拉電阻詳解

- 一、GPIO概述

- 二、GPIO的工作模式

- 1、簡述

- (1)4種輸入模式

- (2)4種輸出模式

- (3)4種最大輸出速度

- 2、引腳速度

- (1)輸出速度設置及其意義

- (2)輸出速度與驅動電路的關系

- 3、配置建議

- 4、詳細分析

- (1)對 I/O 端口進行編程作為輸出時

- (2)對 I/O 端口進行編程作為輸入時

- (3)對 I/O 端口進行編程作為復用功能時

- (4)對 I/O 端口進行編程作為模擬配置時

- 三、上下拉電阻

- 1、上拉電阻

- 2、下拉電阻

一、GPIO概述

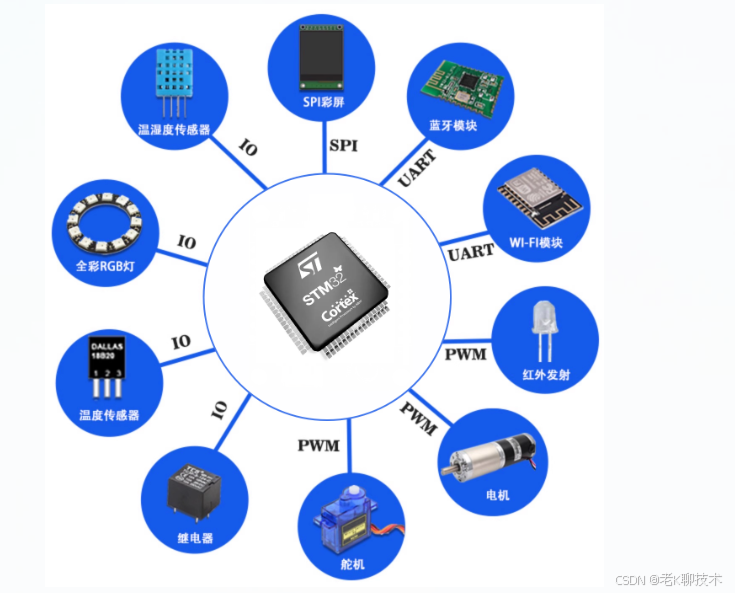

GPIO(英語:General-purpose input/output),即通用I/O(輸入/輸出)端口,是STM32可控制的引腳。STM32芯片的GPIO引腳與外部設備連接起來,可實現與外部通訊、控制外部硬件或者采集外部硬件數據的功能。

STM32F407有8組IO。分別為GPIOA~GPIOH,除了GPIOH只有兩個IO引腳,其余每組IO有16根引腳。

GPIO的復用:引腳復用是指將單個引腳配置為多個功能的能力。在 STM32 中,每個引腳都可以配置為多個不同的功能,如GPIO、定時器、UART、SPI等。這樣一來,通過配置引腳復用功能,可以實現多種硬件功能的連接和實現,提高了芯片的靈活性和可擴展性。引腳默認為IO口。

GPIO的電平:引腳電平對芯片的某個引腳進行高低電平的輸出,以及可以去檢測某個引腳的電平狀態。一般電平采用都是TTL電平信號,TTL電平信號規定:+5V等價于邏輯“1”,0V等價于邏輯“0”。

電平其實有一個電平范圍:>2V就表示高電平,<0.8V就表示低電平。

二、GPIO的工作模式

1、簡述

(1)4種輸入模式

- 浮空輸入(即不連接內部上下拉電阻)

- 上拉輸入(連接上拉電阻)

- 下拉輸入(連接下拉電阻)

- 模擬輸入(用于檢測模擬信號的輸入)

(2)4種輸出模式

- 開漏輸出(帶上拉或者下拉)

- 復用開漏輸出(帶上拉或者下拉)

- 推挽輸出(帶上拉或者下拉)

- 復用推挽輸出(帶上拉或者下拉)

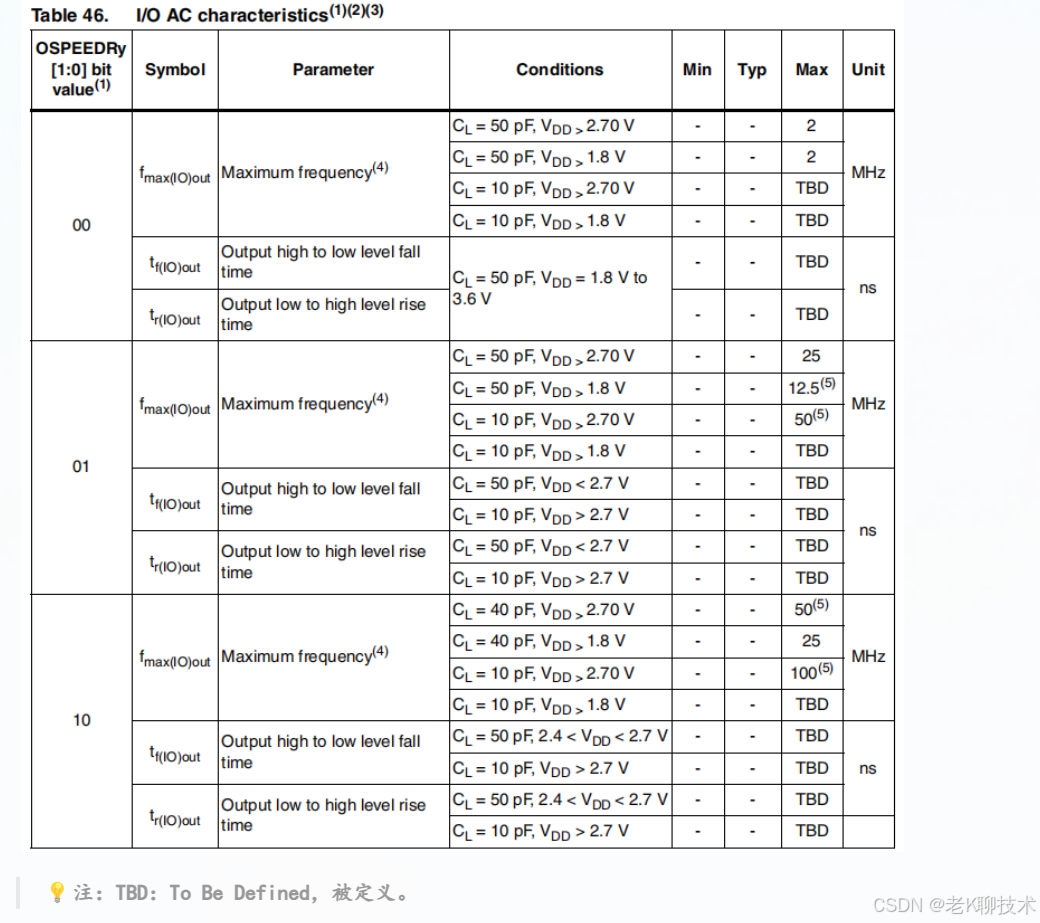

(3)4種最大輸出速度

- 2MHZ (低速)

- 25MHZ (中速)

- 50MHZ (快速)

- 100MHZ (高速)

2、引腳速度

STM32微控制器的GPIO(General Purpose Input/Output)引腳速度設置是一個關鍵的配置參數,它影響著I/O口的性能,特別是當用于高速信號傳輸時。

(1)輸出速度設置及其意義

STM32的GPIO端口在設置為輸出模式時,通常提供幾種速度選項,這些選項代表了I/O口驅動電路的不同響應速度,旨在優化噪聲控制和降低功耗。常見的速度設置包括:

- 2MHz:適用于對噪聲敏感的應用或者低速信號傳輸。這種設置下,輸出驅動電路的響應較慢,但功耗較低,噪聲也相對較小。

- 25MHz:平衡了速度和噪聲控制的需求,適用于中速信號傳輸。相比2MHz,它的響應更快,但仍能保持較好的信號完整性。

- 50MHz:用于高速信號傳輸,如SPI或某些高速總線通信。雖然提供了最快的響應速度,但會增加噪聲并消耗更多功耗。

- 100MHz:這是最快的速度設置,用于超高速信號傳輸,如更高速SPI或某些高速總線通信。雖然提供了最快的響應速度,但會增加更多的噪聲并消耗更多功耗。

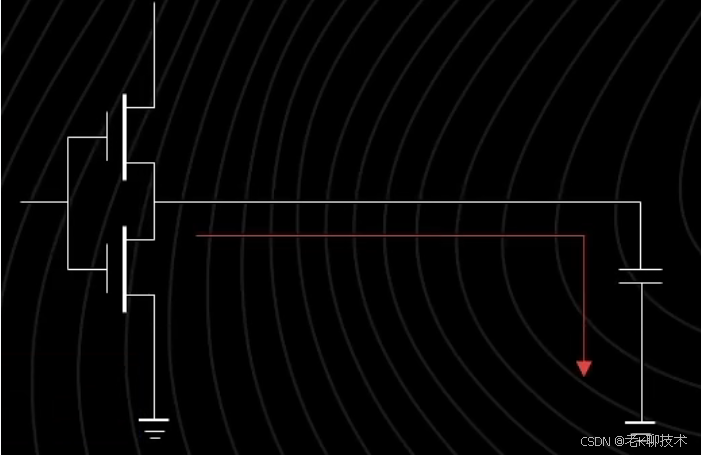

(2)輸出速度與驅動電路的關系

每個GPIO引腳都有與其關聯的輸出驅動電路,這些電路的設計能夠適應不同的速度要求。選擇更高的輸出速度意味著選擇了響應更快的驅動電路,這能夠更迅速地切換輸出狀態(即從高電平到低電平或反之),從而支持更高的數據傳輸速率。但是,更快的切換速度往往伴隨更大的開關噪聲和稍高的功耗。

📔專業名詞

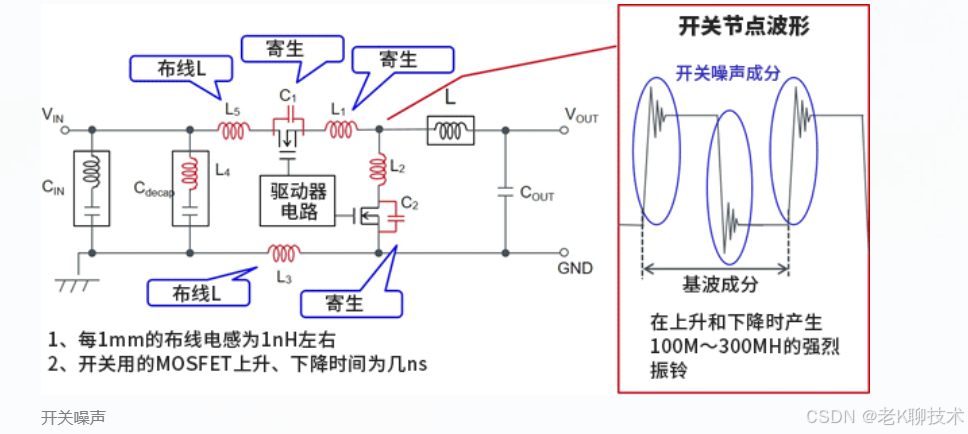

1.開關噪聲:電子電路中的開關噪聲通常是指由于開關操作引起的電磁干擾(Electromagnetic Interference, EMI)或瞬態電壓現象。這種噪聲可能對電路的正常運行產生負面影響,特別是在高頻和高速數字電路中更為明顯。 定義與成因:.開關噪聲主要發生在電路中的快速切換元件上,比如晶體管、繼電器等。

.當這些元件從一種狀態迅速切換到另一種狀態時(如從導通變為截止),會在電路中產生瞬間的電流變化或電壓突變。

.這種突變會導致寄生電感和電容之間的能量交換,從而產生振蕩或尖峰信號。

2.寄生電容:寄生電容是電路設計中常見的非理想效應,它們并不是設計師特意加入的元件,而是由于電路物理結構自然形成的。這些“寄生”元件可以影響電路的行為,尤其是在高頻應用中。

定義:寄生電容是指在兩個導體之間無意中形成的一種電容效應。它通常出現在集成電路內部、印刷電路板(PCB)上的走線間或與地平面之間等地方。

影響:.在高頻電路中,寄生電容可以導致信號延遲增加。

.它可能造成不必要的耦合,使得一個信號路徑中的變化影響到另一個不相關的路徑。

.對于高速數字電路來說,寄生電容還會影響信號完整性,如引起過沖、下沖或者振鈴現象。

3.過沖 (Overshoot)

定義:當信號從低電平切換到高電平時,如果信號超過目標電壓水平并達到更高的峰值,這種現象就稱為過沖。

原因:通常是由于信號路徑上的寄生電感和電容相互作用造成的。當快速上升沿遇到寄生電感時,會產生一個反向電動勢,這會導致電壓超出預期值。

影響:過沖可能導致器件承受高于其額定工作電壓的壓力,從而可能縮短器件壽命或直接造成損害。

4.下沖 (Undershoot)

定義:與過沖相反,當下降沿信號低于目標低電平,并進一步跌落到更低的電壓水平時,這種現象被稱為下沖。

原因:同樣是由寄生元件引起的,尤其是當信號通過較長的走線或者具有較大電感的路徑時。

影響:下沖可能會使信號暫時達不到正確的邏輯電平,從而引起邏輯判斷錯誤。

5.振鈴 (Ringing)

定義:振鈴是指在信號邊沿之后出現的一系列振蕩現象。這些振蕩可能圍繞著最終穩定的目標電壓上下波動。

原因:振鈴通常是由于信號路徑上存在的寄生LC(電感-電容)諧振網絡造成的。當信號經過這樣的網絡時,會激發起振蕩模式。

影響:振鈴不僅會影響當前信號的質量,還可能干擾相鄰線路的信號,尤其是在高密度布線的PCB上。

3、配置建議

- 應用需求導向:根據實際應用需求選擇合適的速度。例如,如果使用I2C接口且波特率為400kHz,選擇2MHz的速度可能已足夠,但如果希望預留更多的余量,可以考慮使用10MHz。

- 信號完整性和噪聲考慮:高速信號傳輸時,應考慮信號的完整性,可能需要增加適當的終端電阻或其他抗干擾措施,以減少高速切換引起的反射和串擾。

- 功耗考量:在低功耗應用中,應優先考慮低速設置以減少功耗。

電路的驅動能力由負載電容決定的,當負載電容一定時,GPIO端口的驅動能力越大,充放電的電流也越大,上升時間就越短。另外速度越高,EMI電磁干擾就越高,因此必須平衡GPIO性能與噪聲,特別是產品出口時要取得EMC(電磁兼容:Electro Magnetic Compatibility)認證。

速度越高,需要電壓就越高,對應功耗也越高。

4、詳細分析

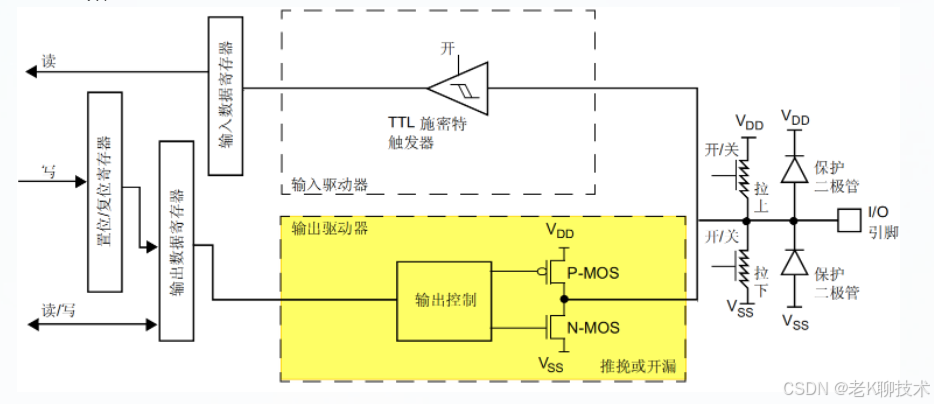

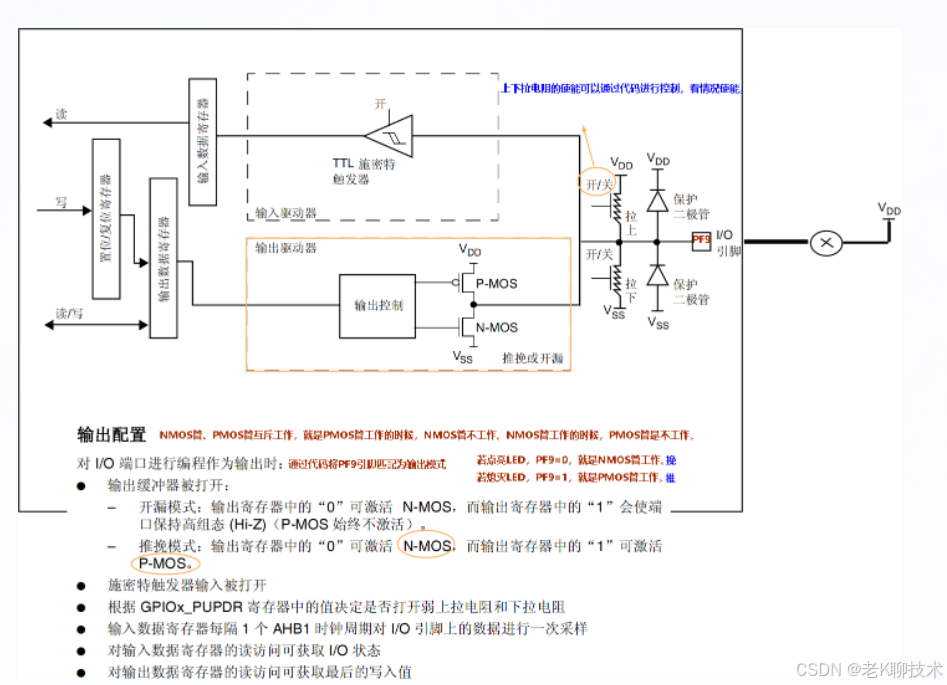

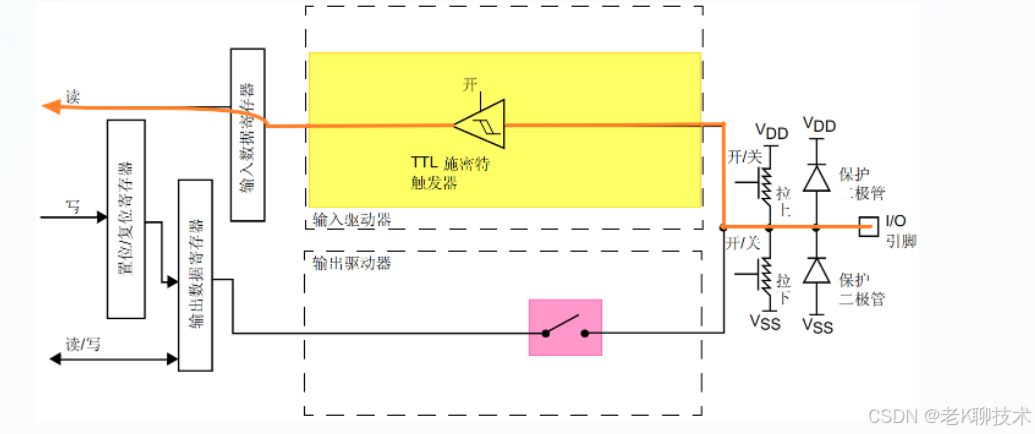

(1)對 I/O 端口進行編程作為輸出時

-

輸出緩沖器被打開:

-

開漏模式(常用于總線,典型特征是引腳外部有上拉電阻):輸出寄存器中的“0”可激活 N-MOS,而輸出寄存器中的“1”會使端口保持高阻態 (Hi-Z)(P-MOS 始終不激活)。

-

推挽模式:輸出寄存器中的“0”可激活 N-MOS,而輸出寄存器中的“1”可激活P-MOS。

-

施密特觸發器輸入被打開

-

根據 GPIOx_PUPDR 寄存器中的值決定是否打開弱上拉電阻和下拉電阻

-

輸入數據寄存器每隔 1 個 AHB1 時鐘周期對 I/O 引腳上的數據進行一次采樣

-

對輸入數據寄存器的讀訪問可獲取 I/O 狀態

-

對輸出數據寄存器的讀訪問可獲取最后的寫入值

-

當輸入信號為高電平的時候,上面的管子導通,下面的管子截止,輸出信號為高電平。

-

當輸入信號為低電平的時候,上面的管子截止,下面的管子導通,輸出信號為低電平。

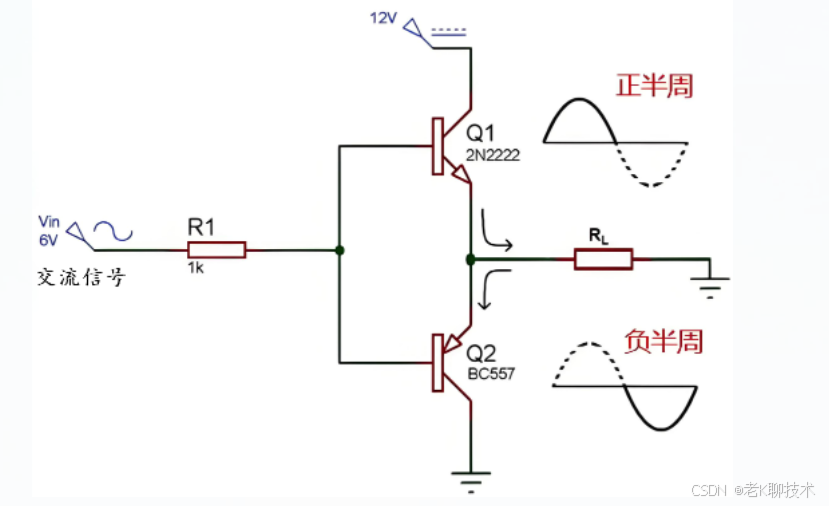

🔸推挽電路

推挽電路(push-pull)就是兩個不同極性晶體管間連接的輸出電路。推挽電路采用兩個參數相同的功率BJT管或MOSFET管,以推挽方式存在于電路中,各負責正負半周的波形放大任務,電路工作時,兩只對稱的功率開關管每次只有一個導通,所以導通損耗小效率高。推挽輸出既可以向負載灌電流,也可以從負載抽取電流,常見應用場景音頻放大器,用于放大音頻信號以驅動揚聲器。

-

工作原理

-

當輸入信號為正半周時,NPN晶體管導通,PNP晶體管截止,輸出電流流過負載。

-

當輸入信號為負半周時,NPN晶體管截止,PNP晶體管導通,輸出電流反方向流過負載。

-

這樣,兩個晶體管輪流工作,使得輸出波形接近于輸入波形,但具有更大的幅度。

在電路設計中,推挽輸出是一種很常用的輸出模式。推挽輸出有很多優點,比如更低的損耗,更安全的輸出等。“推挽”之意,即為當一個管子推出去時,另一個管子拉回來。輸入不同,交替導通。

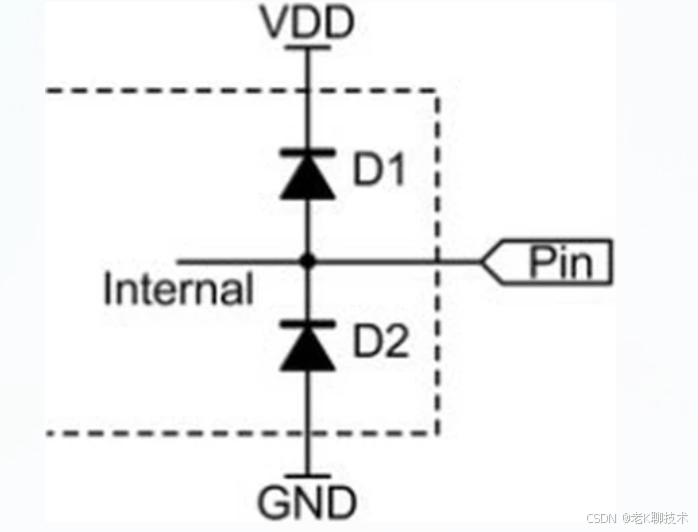

🔸鉗位二極管

鉗位二極管是指用于在電路中將某點的電位進行限制的二極管,鉗位是將某點的電位進行限制,使其不大于或者不小于參考端的值,該點的電位是可變的,是利用二極管的正向導通特性來進行鉗位。IO引腳上下兩邊兩個二極管用于防止引腳外部過高、過低的電壓輸入。當引腳電壓高于VDD時,上方的二極管導通;當引腳電壓低于VSS時,下方的二極管導通,防止不正常電壓引入芯片導致芯片燒毀。但是盡管如此,還是不能直接外接大功率器件,須加大功率及隔離電路驅動,防止燒壞芯片或者外接器件無法正常工作。

如上圖所示,有兩個保護二極管,用于保護內部電路,防止I/O引腳外部過高或者過低的電壓輸入時造成內部電路損壞。

具體來講:當引腳輸入電壓高于VDD時,上面的二極管導通,輸入點電壓被鉗位到約VDD+0.7V;當引腳輸入電壓低于VSS時,下面的二極管導通,輸入點電壓被鉗位到約VSS-0.7V,從而使輸入芯片內部的電壓出于比較穩定的值(鉗位作用)。

雖然有二極管的保護,但這樣的保護很有限,大電壓大電流的輸入很容易燒壞芯片,在實際設計中要考慮設計引腳的保護電路。

假設二極管D1和D2的正向導通壓降都是uD,反向擊穿電壓大于VDD+uD,Pin點的電位記作Upin,則:

① 當Pin點的電位Upin ≥ (VDD+uD)時,此時D1會導通而將Pin點的電位限制在VDD+uD,D2截止;

② 當Pin點的電位在范圍(GND-uD) < Upin < (VDD+uD)時,D1截止,D2截止;

③ 當Pin點的電位Upin ≤ (GND-uD)時,D1截止,D2會導通而將Pin點的電位限制在GND-uD。

綜上所述,Pin點的電位范圍會被限制在(GND-uD) ≤ Upin ≤ (VDD+uD)。若VDD=5V、GND=0V、uD=0.7V,則Pin點電位范圍被限制在 -0.7V ≤ Upin ≤ 5.7V;若忽略D1和D2的正向導通壓降,則可認為Pin點電位范圍被限制為 0V ≤ Upin ≤ 5V。

📣鉗位電路相關說明

二極管具有單向導電性,可利用這一特性對電路進行整流或鉗位。

鉗位的定義:將信號強行鉗制到某一電位上,抬高或降低信號的基準電位,但不改變原信號的波形。鉗位電路分為正向鉗位和負向鉗位電路。

當二極管負極接地時,正極端電路的電位比地高,二極管導通,電位被拉下來,即正極端電壓被鉗位到零電位或零電位以下(忽略二極管壓降)。

當二極管正極接地時,負極端電路的電位比地高,二極管截止,電位將不會受二極管影響。

(2)對 I/O 端口進行編程作為輸入時

- 輸出緩沖器被關閉

- 施密特觸發器輸入被打開

- 根據 GPIOx_PUPDR 寄存器中的值決定是否打開上拉和下拉電阻

- 輸入數據寄存器每隔 1 個 AHB1 時鐘周期對 I/O 引腳上的數據進行一次采樣

- 對輸入數據寄存器的讀訪問可獲取 I/O 狀態

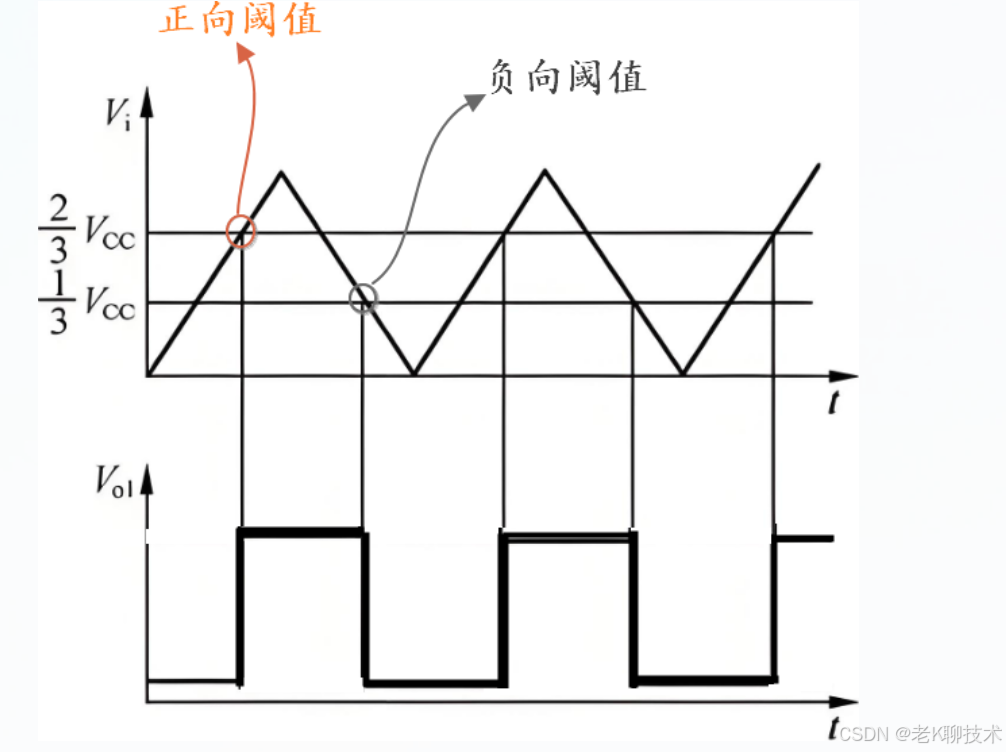

🔸施密特觸發器

在電子學中,施密特觸發器(英語:Schmitt trigger)是包含正反饋的比較器電路。

對于標準施密特觸發器,當輸入電壓高于正向閾值電壓,輸出為高;當輸入電壓低于負向閾值電壓,輸出為低;當輸入在正負向閾值電壓之間,輸出不改變,也就是說輸出由高電準位翻轉為低電準位,或是由低電準位翻轉為高電準位時所對應的閾值電壓是不同的。只有當輸入電壓發生足夠的變化時,輸出才會變化,因此將這種元件命名為觸發器。

施密特觸發器可作為波形整形電路,能將模擬信號波形整形為數字電路能夠處理的方波波形,而且由于施密特觸發器具有滯回特性,所以可用于抗干擾,其應用包括在開回路配置中用于抗擾,以及在閉回路正回授/負回授配置中用于實現多諧振蕩器。

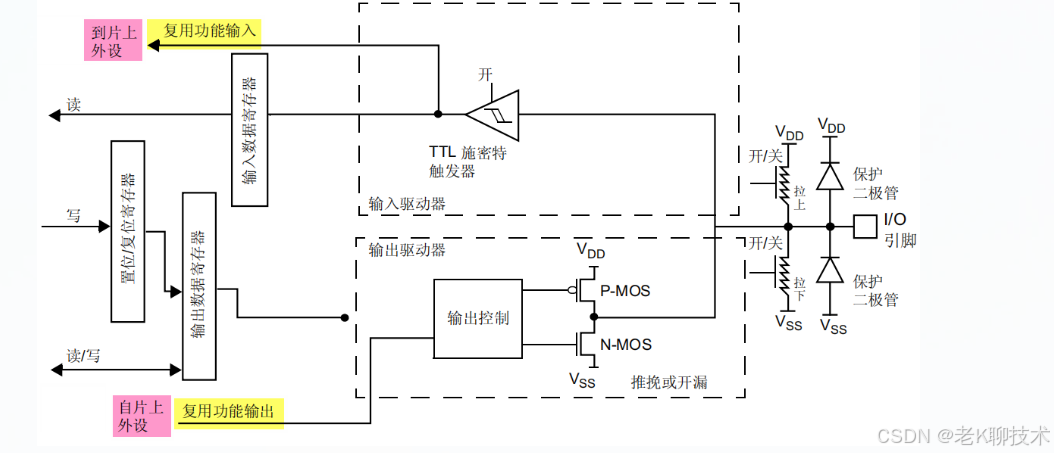

(3)對 I/O 端口進行編程作為復用功能時

- 可將輸出緩沖器配置為開漏或推挽

- 輸出緩沖器由來自外設的信號驅動(發送器使能和數據)

- 施密特觸發器輸入被打開

- 根據 GPIOx_PUPDR 寄存器中的值決定是否打開弱上拉電阻和下拉電阻

- 輸入數據寄存器每隔 1 個 AHB1 時鐘周期對 I/O 引腳上的數據進行一次采樣

- 對輸入數據寄存器的讀訪問可獲取 I/O 狀態

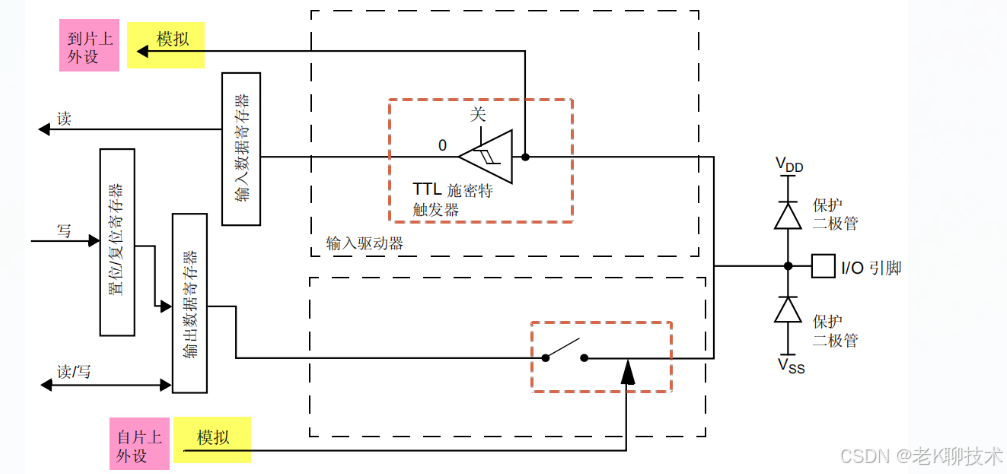

(4)對 I/O 端口進行編程作為模擬配置時

- 輸出緩沖器被禁止。

- 施密特觸發器輸入停用,I/O 引腳的每個模擬輸入的功耗變為零。施密特觸發器的輸被 強制處理為恒定值 (0)。

- 弱上拉和下拉電阻被關閉。

- 對輸入數據寄存器的讀訪問值為“0”。

在模擬配置中,I/O 引腳不能為 5 V 容忍

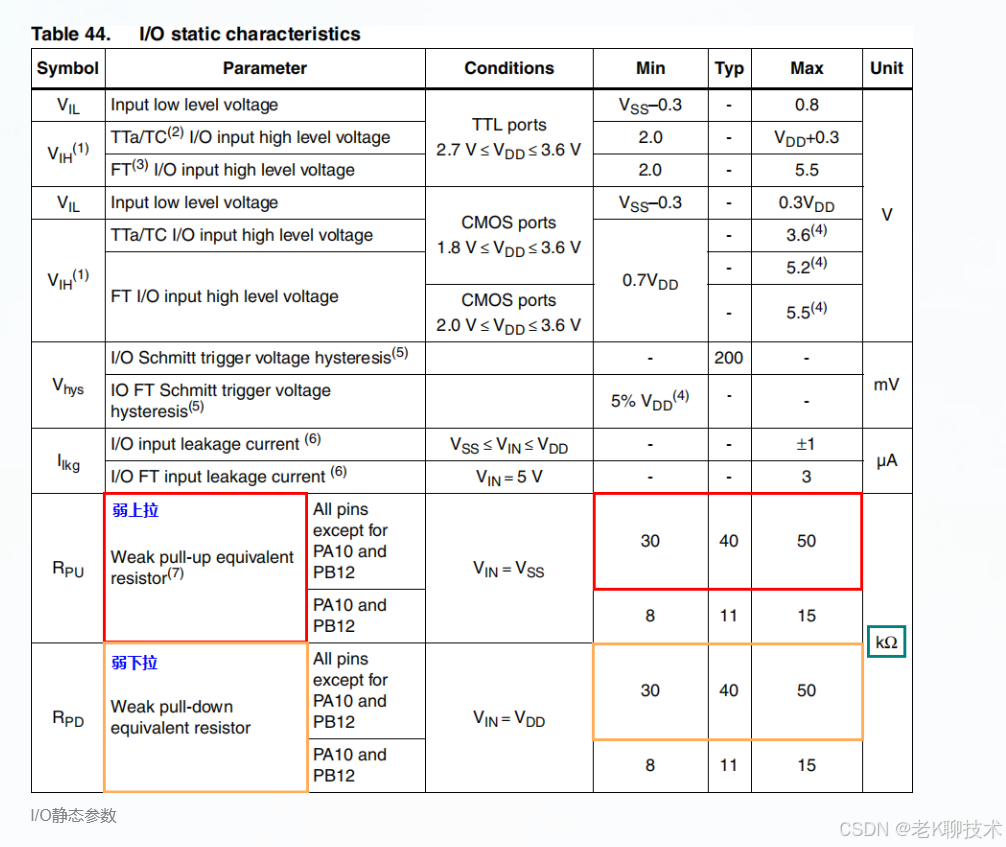

三、上下拉電阻

上下拉電阻(Pull-up 和 Pull-down Resistors)是電子電路中常用的一種組件,用于確保數字電路中的信號線在沒有其他信號源驅動時處于一個確定的狀態。它們對于防止信號線懸空(浮空)非常重要,因為在懸空狀態下,信號線可能會受到噪聲干擾,導致誤操作。

1、上拉電阻

- 將一個不確定的信號,通過一個電阻與電源VCC相連,固定在高電平;

- 上拉是對器件注入電流;灌電流;

- 當一個接有上拉電阻的IO端口設置為輸入狀態時,它的常態為高電平;

2、下拉電阻

- 將一個不確定的信號,通過一個電阻與地GND相連,固定在低電平;

- 下拉是從器件輸出電流;拉電流;

- 當一個接有下拉電阻的IO端口設置為輸入狀態時,它的常態為低電平;

![[GESP202309 六級] 2023年9月GESP C++六級上機題題解,附帶講解視頻!](http://pic.xiahunao.cn/[GESP202309 六級] 2023年9月GESP C++六級上機題題解,附帶講解視頻!)

-Hello World)

![[前端算法]排序算法](http://pic.xiahunao.cn/[前端算法]排序算法)

:Dify 的日志分析與監控)