硬件I2C和軟件I2C的區別

一、硬件I2C

1、硬件I2C的局限性及學習意義

盡管硬件I2C外設在STM32等微控制器中提供了標準化的通信支持,但在實際應用中,其穩定性可能存在問題。例如,某些情況下外設會因事件檢測異常而進入死鎖狀態,僅能通過斷電復位恢復。盡管如此,掌握硬件I2C的實現方法仍具有重要價值,不僅有助于理解I2C協議本身,還能為后續學習其他通信協議奠定基礎。

硬件I2C的工作原理

硬件I2C通過微控制器內置的專用外設實現,其功能類似于USART串口模塊。用戶僅需配置相關寄存器,外設即可自動生成符合I2C標準的時序信號。與軟件模擬不同,硬件I2C無需CPU直接干預引腳電平變化,而是通過寄存器操作控制外設完成通信流程。

軟件模擬I2C的實現方式

軟件模擬I2C依賴CPU通過GPIO手動模擬協議時序。例如,生成起始信號時,需先將SCL引腳置為高電平,隨后在SDA引腳上產生由高到低的跳變,最后拉低SCL電平。這一系列操作完全由程序控制,嚴格遵循I2C協議的時序要求。

硬件與軟件方案的對比

硬件I2C的優勢在于降低CPU負載,但其引腳分配通常受限于芯片設計,僅能使用特定功能引腳。相比之下,軟件模擬I2C具有更高的靈活性,允許任意GPIO充當SCL和SDA信號線,但會占用更多CPU資源。

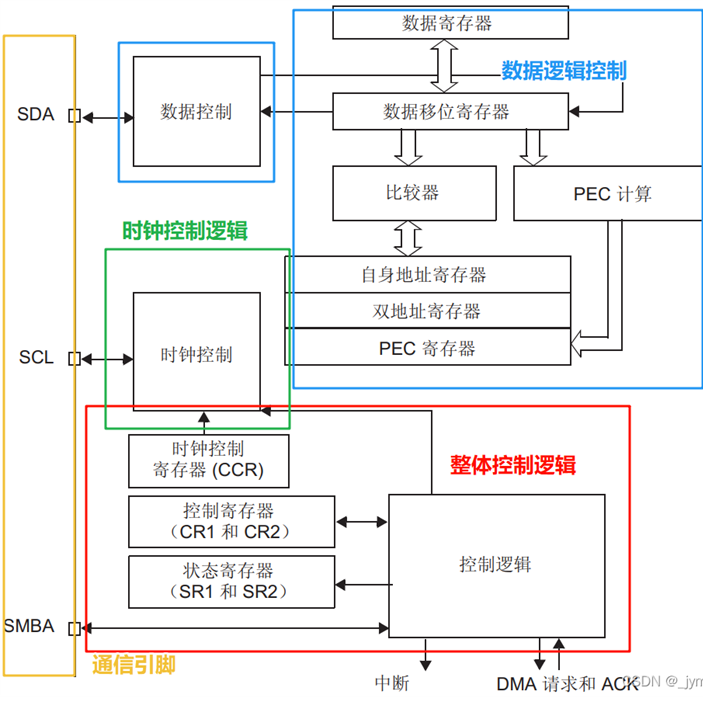

2、I2C外設功能框圖

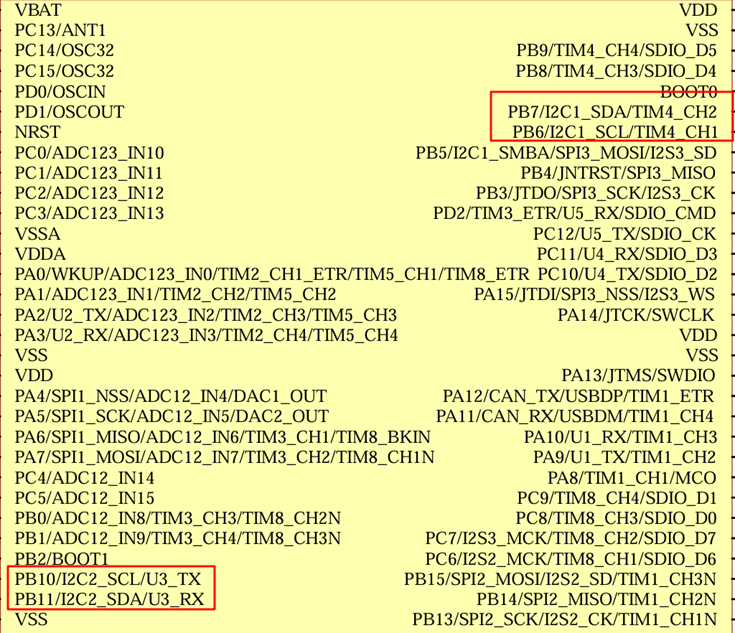

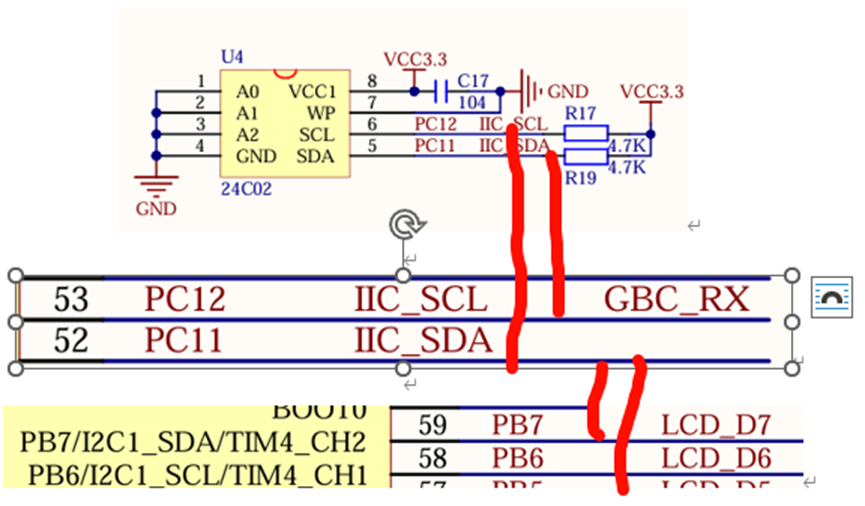

3、通信引腳

STM32中有兩個I2C外設,硬件I2C必須要使用這些引腳,因為這些引腳才連接到I2C引腳,就比如說PB6與PB7引腳就連接到芯片內部的I2C1外設。

在硬件設計中,STM32主控芯片的I2C接口默認配置為PB6(SCL)和PB7(SDA)引腳。然而,實際電路連接中,EEPROM存儲器的SCL和SDA信號線并未與這兩個引腳直接相連,而是分別接至PC12和PC11端口。為實現正常的I2C通信功能,需要通過外部飛線將PB6與PC12、PB7與PC11進行對應連接。這種跨接方式最終實現了STM32的I2C接口引腳與EEPROM器件之間的信號通路建立,從而構成完整的I2C總線系統。

4. STM32的I2C外設通信機制(核心功能解析)

4.1 I2C工作模式配置

STM32的I2C接口支持四種基本工作模式,分別是:

- 主設備發送模式(Master Transmitter)

- 主設備接收模式(Master Receiver)

- 從設備發送模式(Slave Transmitter)

- 從設備接收模式(Slave Receiver)

在默認情況下,I2C模塊初始化為從模式(Slave Mode)。工作模式會在以下兩種情況下動態切換:

- 從模式切換到主模式:當接口主動發起起始信號(Start Condition)時自動進行。

- 主模式切換回從模式:當檢測到總線仲裁失敗(Arbitration Loss)或生成停止信號(Stop Condition)時發生。這種設計支持多主設備(Multi-Master)總線架構,允許多個主設備在同一總線上進行通信。

4.2 主從模式功能定義

- **主模式(Master Mode)**:在這種模式下,STM32充當總線主機,負責發起通信并生成時鐘信號(SCL),可以作為發送端或接收端。

- **從模式(Slave Mode)**:在這種模式下,STM32作為從設備,響應主機的指令并傳輸數據。

4.3 主模式工作機制

**模式切換條件**:

I2C接口默認處于從模式,需要通過置位控制寄存器的START位來產生起始信號,從而切換至主模式。

**數據傳輸控制**:

主設備負責初始化數據傳輸,包括以下步驟:

- 產生起始條件(Start Condition)以啟動通信;

- 輸出同步時鐘(SCL);

- 發送停止條件(Stop Condition)以終止通信。

起始信號觸發后,硬件會自動將設備配置為主模式,并接管總線控制權。在主模式下,完整的通信周期必須包含起始信號與停止信號,這是確保協議時序正確性的關鍵。

**關鍵點**:

- 在主模式下,STM32必須精確控制時鐘信號(SCL)和數據信號(SDA),以符合I2C協議的要求。

- 主設備在通信過程中需要處理總線仲裁,確保在多主設備環境中能夠成功傳輸數據。

- 停止信號的生成標志著一次通信周期的結束,同時也是下一次通信的準備。

通過這些詳細的配置和控制,STM32的I2C接口能夠靈活地適應不同的通信需求,無論是作為主設備還是從設備,都能有效地進行數據傳輸。

二、EEPROM與硬件I2C的協同關系

硬件I2C與EEPROM的通信關系解析**?

1. 硬件I2C的作用**?

硬件I2C(Inter-Integrated Circuit)是STM32等微控制器內置的串行通信接口,采用**同步、半雙工**方式,通過**SCL(時鐘線)**和**SDA(數據線)**兩根信號線與外部設備通信。其核心優勢包括:?

- **硬件自動處理時序**(無需軟件模擬時鐘信號);?

- **支持標準(100kHz)、快速(400kHz)和高速(1MHz及以上)模式**;?

- **多主設備仲裁機制**,避免總線沖突。?

2. EEPROM的I2C接口特性

EEPROM(Electrically Erasable Programmable Read-Only Memory)是一種可通過I2C接口訪問的非易失性存儲器,典型型號如**AT24Cxx系列**,其關鍵特性包括:?

- **依賴I2C協議進行讀寫**:所有操作(地址尋址、數據寫入、數據讀取)均需遵循I2C時序;?

- **從設備地址固定**:通常由硬件引腳(A0~A2)設置,例如AT24C02的默認地址為**0xA0**(寫)/ **0xA1**(讀);?

- **頁寫入與單字節操作**:支持按字節或分頁(如16字節/頁)寫入,需嚴格遵循時序間隔。?

3. 硬件I2C與EEPROM的協同工作流程

1. 初始化配置

?? - STM32的I2C外設需配置為**主模式**,并設置:?

???? - 時鐘頻率(與EEPROM兼容,如100kHz);?

???? - 自身引腳(如PB6/PB7或重映射引腳)與EEPROM的SCL/SDA連接。?

2. 數據傳輸過程

?? - **寫操作**:?

???? 1. 主機(STM32)發送**起始信號(Start)**;?

???? 2. 發送EEPROM的**設備地址 + 寫標志(0)**;?

???? 3. 發送待寫入的**存儲單元地址**;?

???? 4. 發送數據字節(單字節或頁寫入);?

???? 5. 終止通信(Stop信號)。?

?? - **讀操作**:?

???? 1. 主機先發送設備地址 + 寫標志,寫入目標存儲地址;?

???? 2. 重新發送起始信號,切換為讀模式(設備地址 + 讀標志1);?

???? 3. 接收EEPROM返回的數據,最后發送NAK/Stop結束。?

3. 關鍵注意事項?

?? - **電氣兼容性**:需確保總線上拉電阻(通常4.7kΩ)正確連接;?

?? - **時序嚴格性**:EEPROM的寫入周期(如5ms)需通過延時或輪詢ACK保證;?

?? - **錯誤處理**:硬件I2C應啟用中斷/DMA,檢測總線錯誤(如仲裁丟失、無應答)。?

4. 硬件I2C對比軟件模擬的優勢**?

特性?????? ?軟件 I2C ?硬件 I2C

?實現方式?????? 通過 GPIO 引腳模擬 I2C 時序(軟件控制)? 使用 MCU 內置的硬件 I2C 外設(硬件控制)

?CPU 占用????? 高(需 CPU 持續操作 GPIO) 低(硬件自動完成時序,CPU 可處理其他任務)

?時序精度?????? 依賴軟件延時,精度較低??? 由硬件時鐘控制,精度高且穩定

?開發復雜度??? 簡單(無需配置復雜寄存器)??? 復雜(需初始化外設、處理中斷/DMA)

?靈活性??? 高(可適配任意 GPIO 引腳)?? 低(必須使用硬件 I2C 外設的固定引腳)

?速度?????? 較慢(受限于軟件延時)??? 較快(支持標準模式 100kHz、快速模式 400kHz+)

?兼容性??? 通用性強(可適配不同 MCU) 依賴具體 MCU 的硬件支持

5. 典型問題與解決方案

- **通信失敗**:?

? - 檢查SCL/SDA線路連接、上拉電阻;?

? - 確認設備地址匹配(含硬件引腳電平);?

? - 通過邏輯分析儀捕獲時序,排查協議錯誤。?

- **數據寫入異常**:?

? - 遵守EEPROM的頁寫入限制(如AT24C02每頁≤16字節);?

? - 寫入后增加足夠延時(或查詢ACK完成信號)。?

**總結**:硬件I2C為EEPROM提供了高效、穩定的訪問方式,其硬件自動化的特性顯著降低了軟件復雜度,適用于需要高可靠性的嵌入式存儲系統。

三、軟件I2C????????

通過 GPIO 手動控制 SCL 和 SDA 引腳電平,模擬 I2C 時序。

#include "stm32f10x_gpio.h"#include "stm32f10x_rcc.h"/* 宏定義(修改為PB6/PB7引腳) */#define SOFT_I2C_SCL_PIN??? GPIO_Pin_6? // PB6作為SCL#define SOFT_I2C_SDA_PIN??? GPIO_Pin_7? // PB7作為SDA#define SOFT_I2C_PORT?????? GPIOB/* 初始化函數(開漏模式+上拉) */void Soft_I2C_Init(void) {GPIO_InitTypeDef GPIO_InitStruct;// 使能GPIOB時鐘RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOB, ENABLE);// 配置SCL和SDA為開漏輸出(實際需外接上拉電阻)GPIO_InitStruct.GPIO_Pin = SOFT_I2C_SCL_PIN | SOFT_I2C_SDA_PIN;GPIO_InitStruct.GPIO_Mode = GPIO_Mode_Out_OD;? // 開漏輸出GPIO_InitStruct.GPIO_Speed = GPIO_Speed_50MHz;GPIO_Init(SOFT_I2C_PORT, &GPIO_InitStruct);// 初始狀態拉高總線GPIO_SetBits(SOFT_I2C_PORT, SOFT_I2C_SCL_PIN);GPIO_SetBits(SOFT_I2C_PORT, SOFT_I2C_SDA_PIN);}/* 精確延時(基于SysTick或NOP指令) */static void Delay_us(uint32_t us) {us *= (SystemCoreClock / 1000000) / 5;? // 根據主頻校準while(us--) __NOP();}/* 產生起始信號 */void Soft_I2C_Start(void) {GPIO_SetBits(SOFT_I2C_PORT, SOFT_I2C_SDA_PIN);GPIO_SetBits(SOFT_I2C_PORT, SOFT_I2C_SCL_PIN);Delay_us(5);GPIO_ResetBits(SOFT_I2C_PORT, SOFT_I2C_SDA_PIN);? // SDA下降沿Delay_us(5);GPIO_ResetBits(SOFT_I2C_PORT, SOFT_I2C_SCL_PIN);? // SCL拉低準備數據傳輸}/* 產生停止信號 */void Soft_I2C_Stop(void) {GPIO_ResetBits(SOFT_I2C_PORT, SOFT_I2C_SCL_PIN);GPIO_ResetBits(SOFT_I2C_PORT, SOFT_I2C_SDA_PIN);Delay_us(5);GPIO_SetBits(SOFT_I2C_PORT, SOFT_I2C_SCL_PIN);??? // SCL上升沿Delay_us(5);GPIO_SetBits(SOFT_I2C_PORT, SOFT_I2C_SDA_P

)

)

![[論文閱讀] (38)基于大模型的威脅情報分析與知識圖譜構建論文總結(讀書筆記)](http://pic.xiahunao.cn/[論文閱讀] (38)基于大模型的威脅情報分析與知識圖譜構建論文總結(讀書筆記))

)