目錄

背景

目的

操作

仿真測試

搭建仿真模型

插入損耗測試

優化設計后重新測試

思考

背景

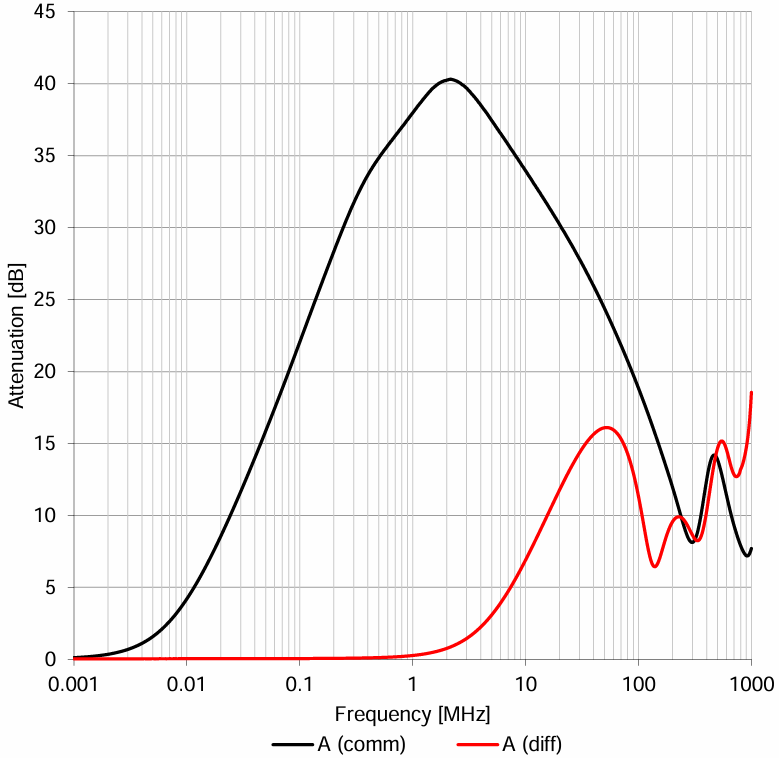

在選購共模電感時,規格書中通常會提供插損曲線或者阻抗-頻率曲線,但這些數據都是在特定條件下測試獲得的。如果將其集中在我們的樣機中性能會如何?設計前期我們可以將其加入到我們的電路仿真模型中去作為評估,這也是該系列仿真的價值所在。

準備從共模電感的共模、差模感量測試開始,然后測試與驗證共模電感的差共模插入損耗,最后基于該共模電感設計一個一級的EMC電源濾波器。

目的

設計一個一級濾波器,使其差模和共模的插損均大于80dB。

操作

仿真平臺:LTspice;

共模電感選型:WE,744821201,參數如下:

X/Y電容選型:略。

仿真測試

搭建仿真模型

參加下圖。

插入損耗測試

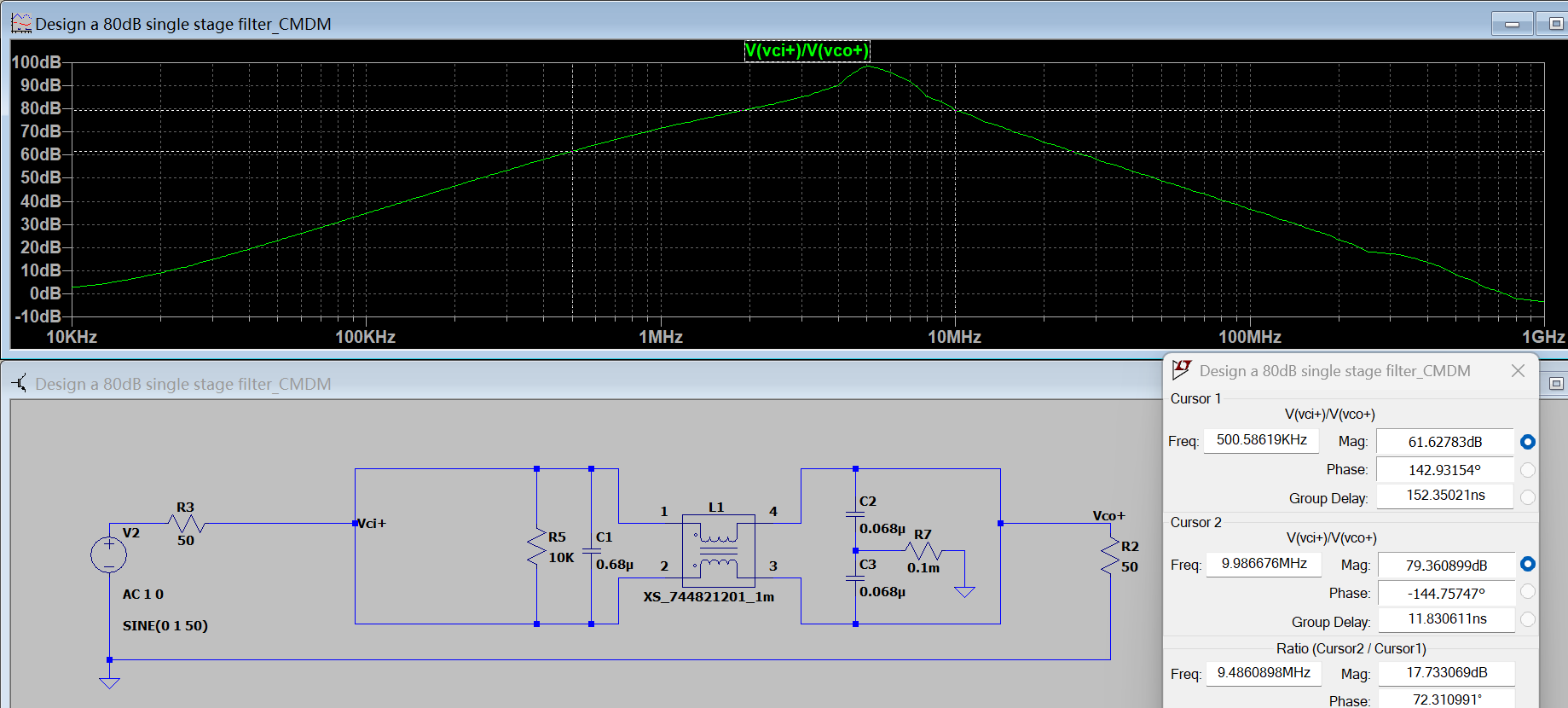

1)共模插入損耗測試:61.6dB@500kHz,79.4dB@10MHz,最大近100dB@5MHz;

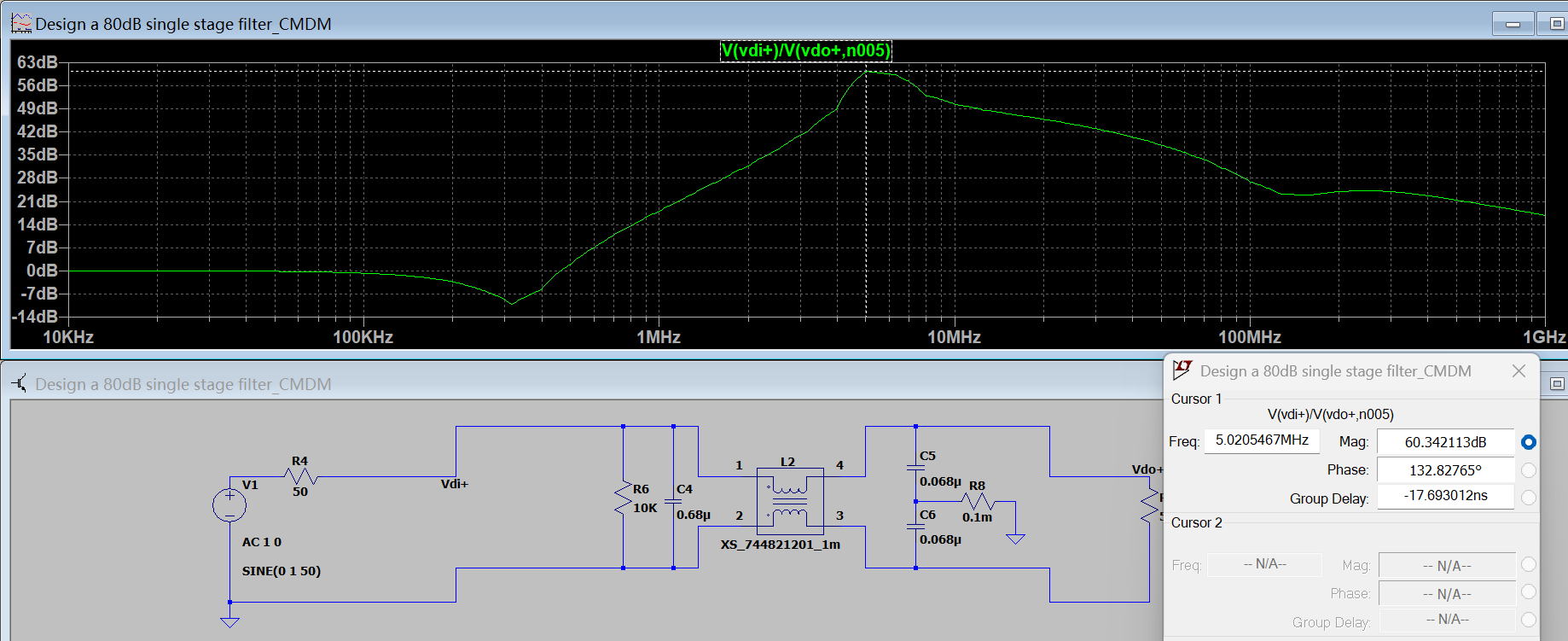

2)差模插入損耗測試:最大只有60dB@5MHz;

優化設計后重新測試

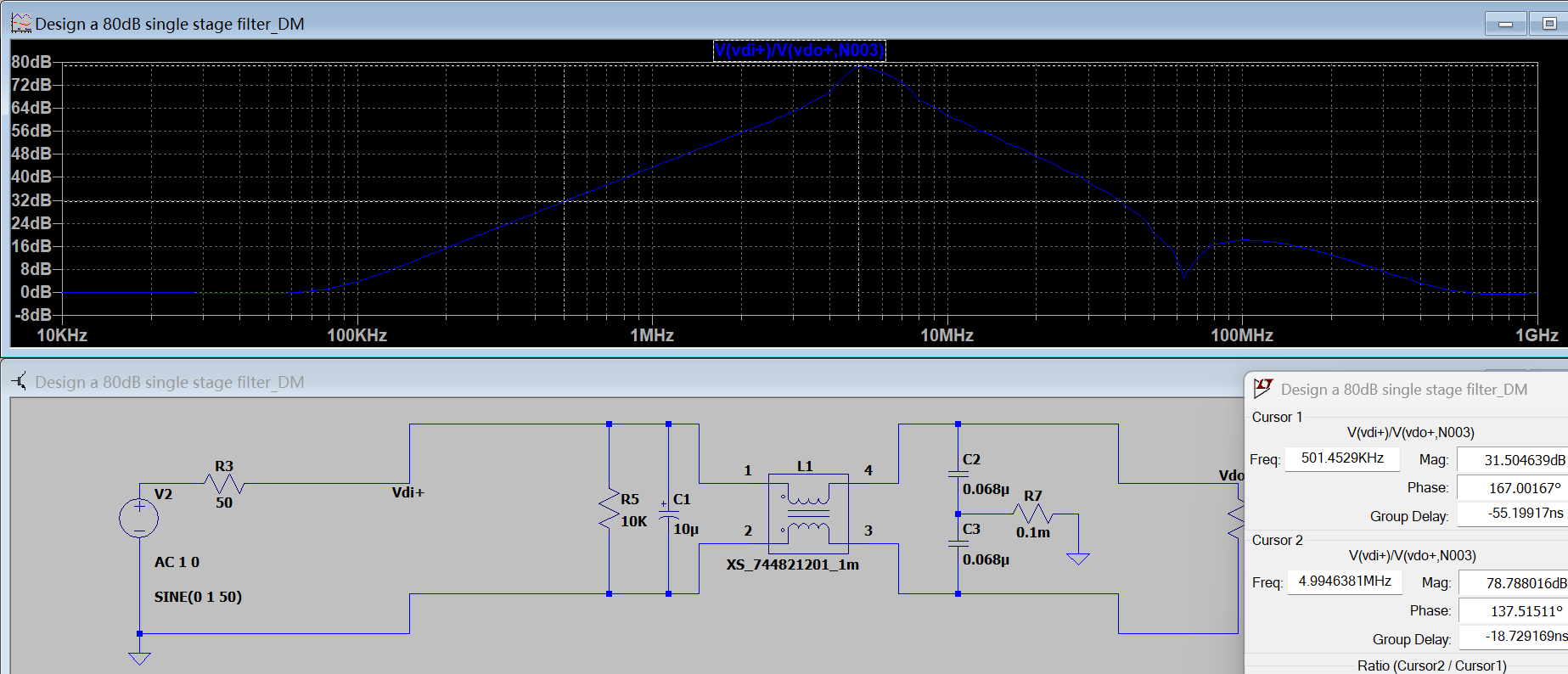

1)將差模電容增大到10uF,測得差模插入損耗最大78.8dB;

思考

1)10uF的X電容體積很大,為了實現80dB的差模插損,可以有哪些優化?歡迎評論區討論。

<完>

)

:Matplotlib 高級圖表定制 - 精雕細琢,讓你的圖表脫穎而出!)

)

)