在解析LVDS信號時,十分重要的一環就是LVDS輸入信號線在經過PCB輸入到FPGA中后,本來該嚴格對齊的信號線會出現時延,所以需要在FPGA內部對其進行延時對齊后再進行解析。

Xilinx 7系器件中用于輸入信號延時的組件為IDELAYE2可編程原語,通過可以編程的32抽頭延遲線、環繞式延遲實現信號延遲。

原語可用于組合輸入路徑、寄存器輸入路徑、FPGA邏輯直接訪問;可以對單個輸入引腳進行信號延遲。原語的抽頭延遲分辨率也就是延時精度由IDELAYCTRL原語控制。

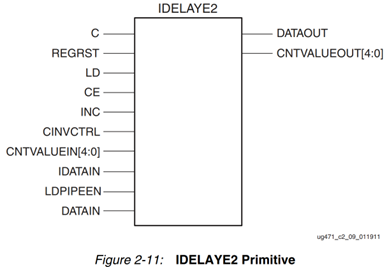

? IDELAYE2框圖:

? IDELAYE2例化:

(* IODELAY_GROUP = <iodelay_group_name> *) // Specifies group name for associated IDELAYs/ODELAYs and IDELAYCTRL

IDELAYE2 #(

.CINVCTRL_SEL(“FALSE”), // Enable dynamic clock inversion (FALSE, TRUE)

.DELAY_SRC(“IDATAIN”), // Delay input (IDATAIN, DATAIN)

.HIGH_PERFORMANCE_MODE(“FALSE”), // Reduced jitter (“TRUE”), Reduced power (“FALSE”)

.IDELAY_TYPE(“FIXED”), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

.IDELAY_VALUE(0), // Input delay tap setting (0-31)

.PIPE_SEL(“FALSE”), // Select pipelined mode, FALSE, TRUE

.REFCLK_FREQUENCY(200.0), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

.SIGNAL_PATTERN(“DATA”) // DATA, CLOCK input signal

)

IDELAYE2_inst (

.CNTVALUEOUT(CNTVALUEOUT), // 5-bit output: Counter value output

.DATAOUT(DATAOUT), // 1-bit output: Delayed data output

.C?, // 1-bit input: Clock input

.CE(CE), // 1-bit input: Active high enable increment/decrement input

.CINVCTRL(CINVCTRL), // 1-bit input: Dynamic clock inversion input

.CNTVALUEIN(CNTVALUEIN), // 5-bit input: Counter value input

.DATAIN(DATAIN), // 1-bit input: Internal delay data input

.IDATAIN(IDATAIN), // 1-bit input: Data input from the I/O

.INC(INC), // 1-bit input: Increment / Decrement tap delay input

.LD(LD), // 1-bit input: Load IDELAY_VALUE input

.LDPIPEEN(LDPIPEEN), // 1-bit input: Enable PIPELINE register to load data input

.REGRST(REGRST) // 1-bit input: Active-high reset tap-delay input

);

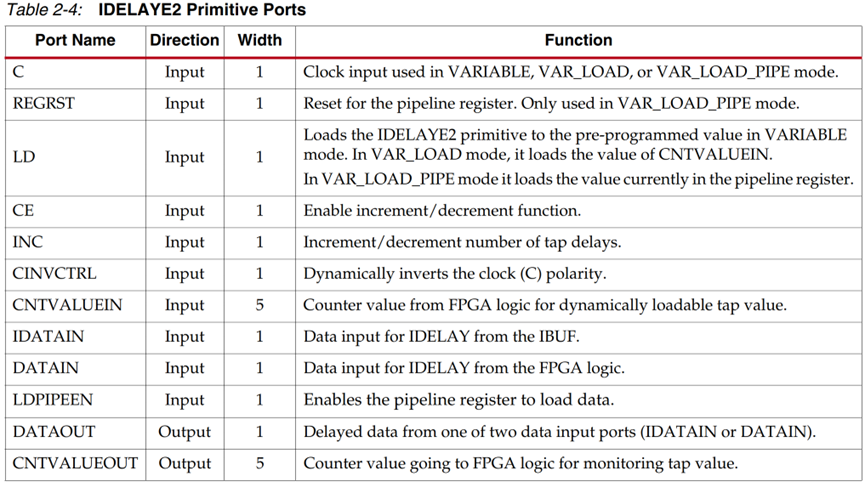

? IDELAYE2例化端口:

端口列表如上圖:

C:時鐘輸入,原語的所有控制輸入(如REGRST、LD、CE、INC)都與該時鐘輸入同步。當該原語配置為VARIABLE, VAR_LOAD和VAR_LOAD_PIPE模式時,該端口必須連接有效時鐘。且該時鐘必須由全局或區域時鐘緩沖器提供。

REGRST:寄存器同步復位信號,當復位置1時,將原語內部流水線寄存器置0,僅在

VAR_LOAD_PIPE模式下使用。

LD:加載抽頭值,LD端口置1有效,且與輸入時鐘C同步;

在VARIABLE模式下,IDELAY置高LD端口會加載IDELAY_VALUE參數端口設置的抽頭值作為新的延時值,此時LD端口可當作IDELAY的復位信號,拉高LD后延時抽頭值將設置為IDELAY_VALUE參數的值。

在VAR_LOAD模式下,IDELAY會加載由CNTVALUEIN端口設置的抽頭值作為新的延時值。

在VAR_LOAD_PIPE模式下,IDELAY會加載當前在流水線寄存器中的抽頭值作為新的延時值。

CE:控制INC端口作為抽頭值增量或減量的使能,就是CE有效,INC端口的值才能生效。且該端口只在VARIABLE, VAR_LOAD, VAR_LOAD_PIPE這三個模式下使用。

INC:抽頭延遲的增量減量,搭配CE使用,只有當CE為高時,INC才有效,當CE為低時INC值不起作用,其中INC=1時抽頭值遞增,INC=0時抽頭值遞減,且INC和CE都與時鐘C同步,且當CE保持高,每個C的時鐘周期,根據INC的值設置,抽頭值會在下一個時鐘C的上升沿開始進行抽頭值的遞增遞減操作;

IDELAYE2原語的可編程延遲抽頭會執行環繞操作,原語的延遲抽頭值為0~31共32個數,環繞是指當抽頭值當前到達邊界,如0或31,在0時如果遞減,抽頭值將變為31,在31時如果遞增,抽頭值將變為0;

且信號的延時也只有32個選項,例如對一個信號從延時抽頭值0開始一直做INC遞增的延時操作,當抽頭值到達31,遞增1后,抽頭值到0,此時這個抽頭值0的信號延時與最開始抽頭值初始為0的延時是相同的,而不是指從31遞增到0后,信號延時在延時抽頭值31的延時基礎上又往后延遲了一個抽頭的延時,這就是該原語的環繞操作。

CINVCTRL:動態控制輸入時鐘C的極性,且在切換極性時,兩個時鐘周期內不要控制IDLEAY原語的控制端口。

CNTVALUEIN:用于動態切換加載的抽頭值。

IDATAIN:IDATAIN端口輸入來自IOB,該輸入數據由IOB中的IBUF驅動,也就是FPGA的管腳輸入的信號,對FPGA的外部輸入信號作延時。

DATAIN:DATAIN端口輸入來自FPGA邏輯,該端口為內部邏輯提供了可訪問的延遲線。

LDPIPEEN:流水線寄存器加載,當該端口為1時,會把當前CNTVALUEIN引腳上的抽頭值加載到管道寄存器中。

DATAOUT:來自兩個數據輸入端口的延遲數據,延時后的輸出數據線可以連接到ILOGIC、ISERDES組件或是FPGA邏輯。

CNTVALUEOUT:該端口用于報告此時輸出的延遲數據加載的延遲抽頭值。

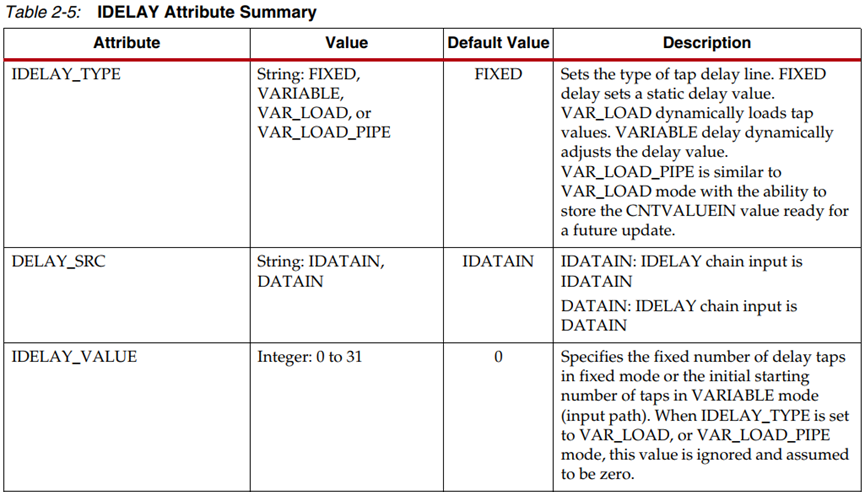

? IDELAYE2例化參數:

上圖為原語的例化參數:

IDELAY_TYPE:設置IDELAY原語的延遲的工作模式,有FIXED, VARIABLE, VAR_LOAD,

VAR_LOAD_PIPE四種可選模式;

設置為FIXED模式時,抽頭延遲值由參數IDELAY_VALUE的值確定,且該值是預設的,配置后無法更改;

設置為VARIABLE模式時,抽頭延遲可選,設置CE=1和INC=1增加抽頭延遲,設置CE=1和INC=0減少抽頭延遲,遞增遞減操作與C時鐘同步;

設置為VAR_LOAD模式時,置高LD端口,原語將立即加載CNTVALUEIN端口的值作為新的抽頭延遲值,同時支持CE和INC協同的遞增遞減操作;

設置為VAR_LOAD_PIPE模式時,置高LDPIPEEN端口,原語將立即將CNTVALUEIN端口的值加載到原語內部的流水線寄存器中暫存,當置高LD端口,原語將立即加載流水線寄存器中的抽頭值作為新的抽頭延遲值(該模式一般用于多通道同步修改延遲的情況,同步性強,優化時序),同時支持CE和INC協同的遞增遞減操作。

DELAY_SRC:選擇原語的輸入數據源端口,可選值為IDATAIN和DATAIN,設置為IDATAIN時原語使用IDATAIN端口作為輸入數據,數據來自IO引腳,設置為DATAIN時原語使用DATAIN端口作為輸入數據,數據來自FPGA內部邏輯。

IDELAY_VALUE:指定了初始的抽頭延遲數量,默認為0,可設置為0~31之間任意整數;

FIXED模式下,IDELAY_VALUE參數指定原語的抽頭延時值;

VARIABLE模式下,IDELAY_VALUE值將作為延遲線的初始延時值,LD置高將會將原語的延遲重置為IDELAY_VALUE的值;

VAR_LOAD和VAR_LOAD_PIPE模式下,IDELAY_VALUE參數不被使用。

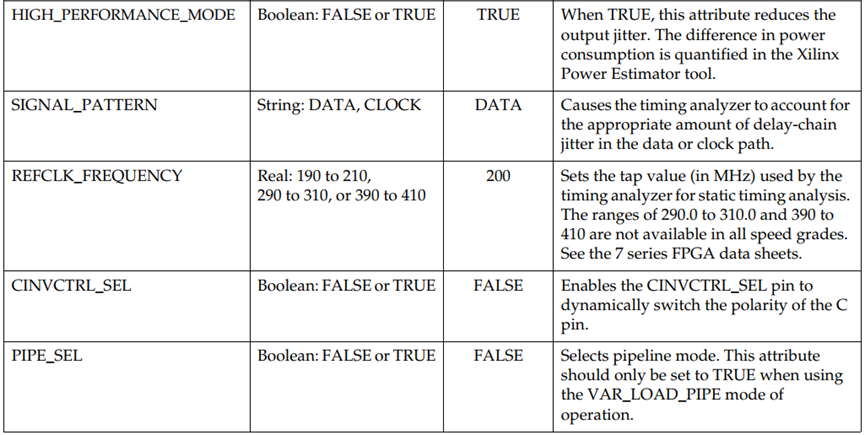

HIGH_PERFORMANCE_MODE:高性能模式選擇參數,可選值為TRUE和FALSE,

TRUE模式降低抖動,降低抖動將會略微增加功耗,適用于高速場景,

FALSE降低功耗但抖動增加,適用于低速場景。

SIGNAL_PATTERN:數據輸入的信號類型,可選值為DATA和CLOCK,由于時鐘信號和數據信號有不同的電器特性,時鐘信號具有周期性,而數據信號是隨機的,兩者在延遲鏈中積累的抖動量也不同,所以選擇DATA(輸入數據為數據信號)和CLOCK(輸入數據為時鐘信號),原語將會根據時鐘和數據的電氣特性的不同執行不同的抖動優化策略。

REFCLK_FREQUENCY:參考時鐘頻率,與IDELAYCTRL原語參考時鐘需嚴格匹配,否則將會校準失敗,范圍為(190.0-210.0, 290.0-310.0),默認使用200.0,設置為200MHZ即可。

CINVCTRL_SEL:時鐘動態反相的使能,輸入時鐘端口C是否可以反相,改參數搭配CINVCTRL端口使用,當參數設置為TRUE的同時將CINVCTRL端口置1可以將時鐘C反相,當參數設置為FALSE時,時鐘不會反相,CINVCTRL端口也將無法使用。

PIPE_SEL:僅在VAR_LOAD_PIPE模式下工作,控制流水線寄存器是否使用,設置為TRUE時啟用流水線寄存器,FALSE時不啟用流水線寄存器。

? 例化約束:

Vivado的例化模板中IDELAYE2原語還有一行約束:

(* IODELAY_GROUP = <iodelay_group_name> *)

該約束可以定義IDELAYE2原語的組,可以將多個IDELAYE2和ODELAYE2原語與一個IDELAYCTRL原語綁定,確保它們共享同一個參考時鐘并物理相鄰,減少時鐘偏差;

使用時同一組的IDELAYE2和ODELAYE2和IDELAYCTRL原語都約束指定為一個相同的組名即可。

? IDELAY工作模式:

IDELAY_TYPE參數設置工作模式,有FIXED, VARIABLE, VAR_LOAD,VAR_LOAD_PIPE:

FIXED固定延遲模式:

IDELAY_VALUE參數值將配置為延時值,配置后無法更改;

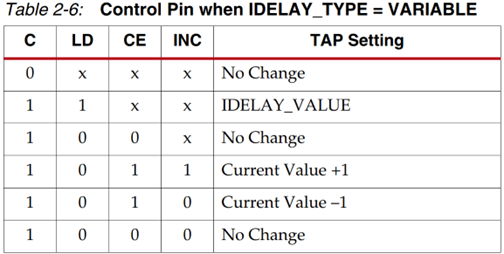

VARIABLE可變延遲模式:

由上表,該模式下,LD置1將加載IDELAY_VALUE參數值作為延時值;

CE和INC搭配執行當前延時值的遞增遞減操作,CE=1,INC=1遞增,CE=1,INC=0遞減;

其他輸入延時值保持不變;

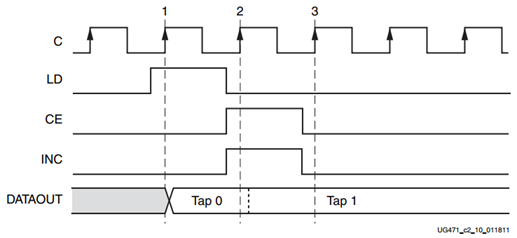

上圖為VARIABLE模式下,IDELAY_VALUE參數值為0的時序:

時刻1,LD置1,原語加載為IDELAY_VALUE參數值,延時值DATAOUT變為tap0,

時刻2,CE=1,INC=1,延時值從0遞增到1,從tap0變為tap1;

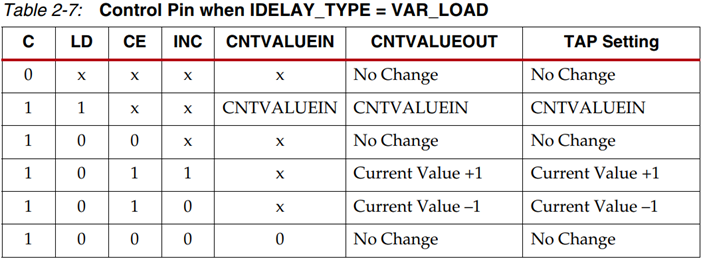

VAR_LOAD可加載變量延遲模式:

由上表,該模式下,

CE和INC搭配執行當前延時值的遞增遞減操作,同上條;

此時LD置1將加載CNTVALUEIN端口值作為延時值;

其他輸入延時值保持不變;

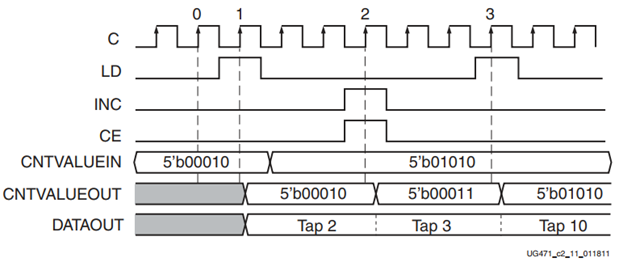

上圖為VAR_LOAD模式下的時序,

時刻1,LD置1,加載CNTVALUEIN端口的值2,延時值DATAOUT變為tap2,

時刻2,CE=1,INC=1,延時值從2遞增到3,從tap2變為tap3,

時刻3,LD置1,加載CNTVALUEIN端口的值10,延時值DATAOUT變為tap10,

VAR_LOAD_PIPE可加載變量流水線寄存延遲模式:

該模式與VAR_LOAD模式類似,

CE和INC執行遞增遞減;

不同的是LD的操作,該模式下LD置1將加載內部流水線寄存器值作為延時值,

流水線寄存器則是在LDPIPEEN端口置1時,將CNTVALUEIN端口的值加載到寄存器中;

下節講解IDELAYCTRL原語和IDELAYE2的搭配使用;

本文章由威三學社出品

對課程感興趣可以私信聯系

)

)

)

)