目錄

1. 簡介

2. 界面展示

2.1 啟動

2.1.1 C Simulation Dialog

2.1.2 C Synthesis

2.1.3 C/RTL Co-simulation

2.1.4 Implementation

2.1.5 Package

3. C Synthesis 詳解

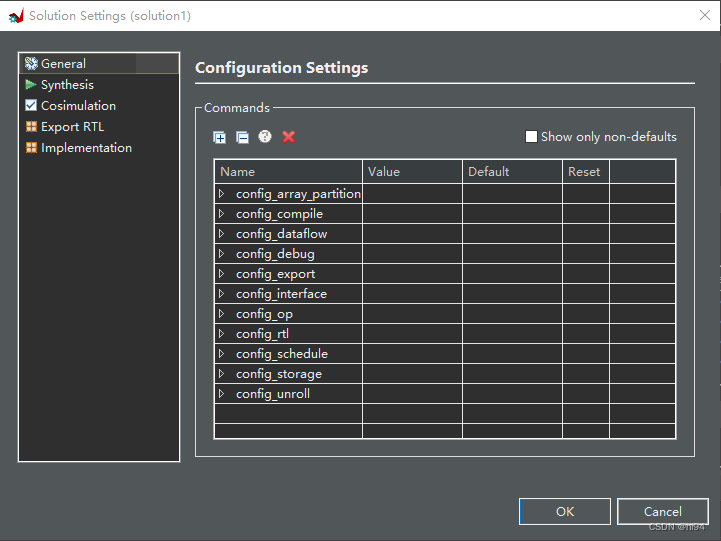

3.1 Classic Configuration Settings

3.1.1 config_array_partition

3.1.2 config_compile

3.1.3 config_dataflow

3.1.4 config_debug

3.1.5 config_export

3.1.6 config_interface

3.1.7 config_op

3.1.8 config_rtl

3.1.9 config_schedule

3.1.10 config_storage

3.1.11 config_unroll

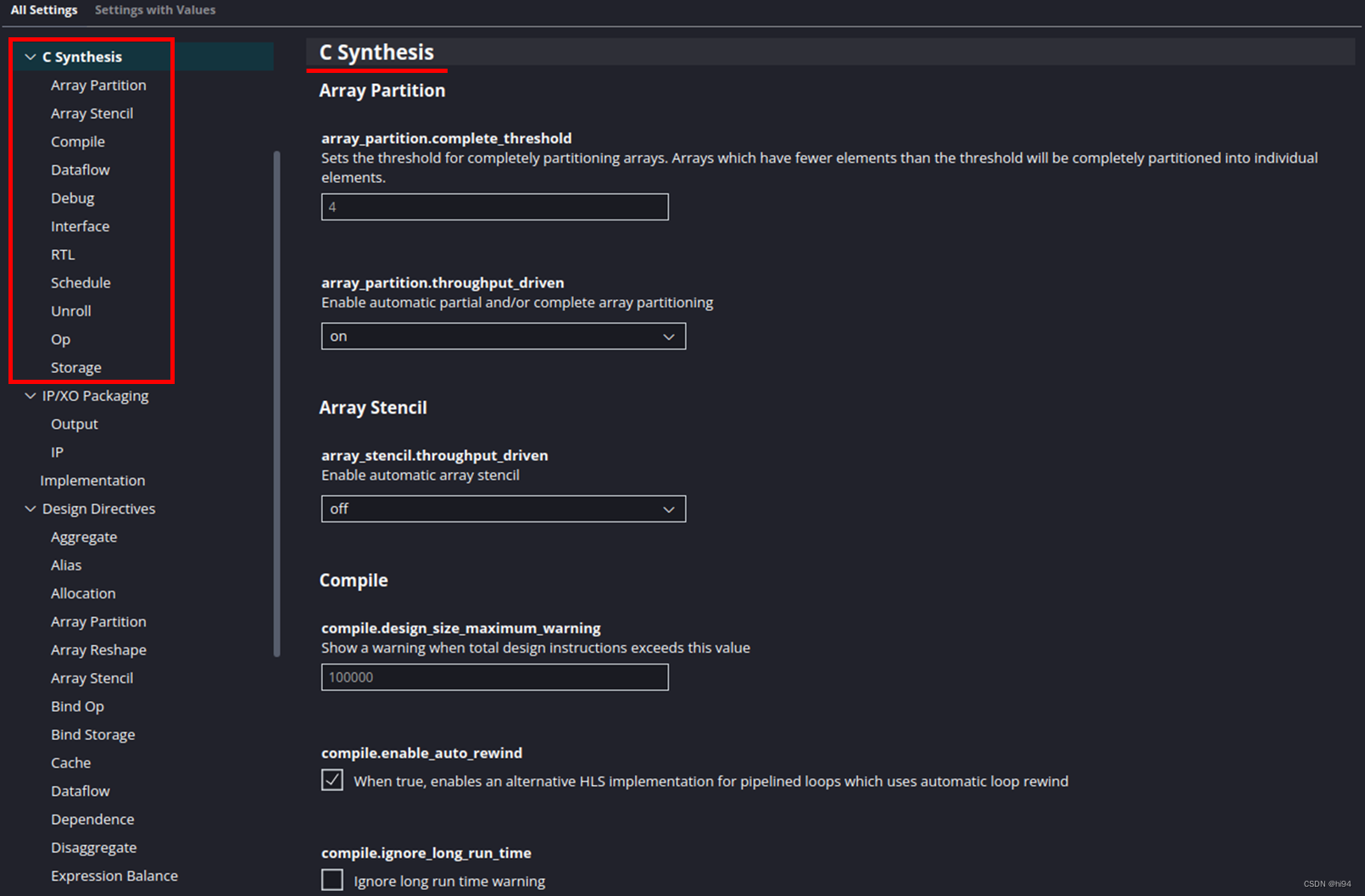

3.2 New?Configuration Settings

3.2.1?Array Partition

3.2.2 Array Stencil

3.2.3?Compile

3.2.4 Dataflow

3.2.5 Debug

3.2.6 interface

3.2.7 RTL

3.2.8 Schedule

3.2.9 Unroll

3.2.10 Op

3.2.11 Storage

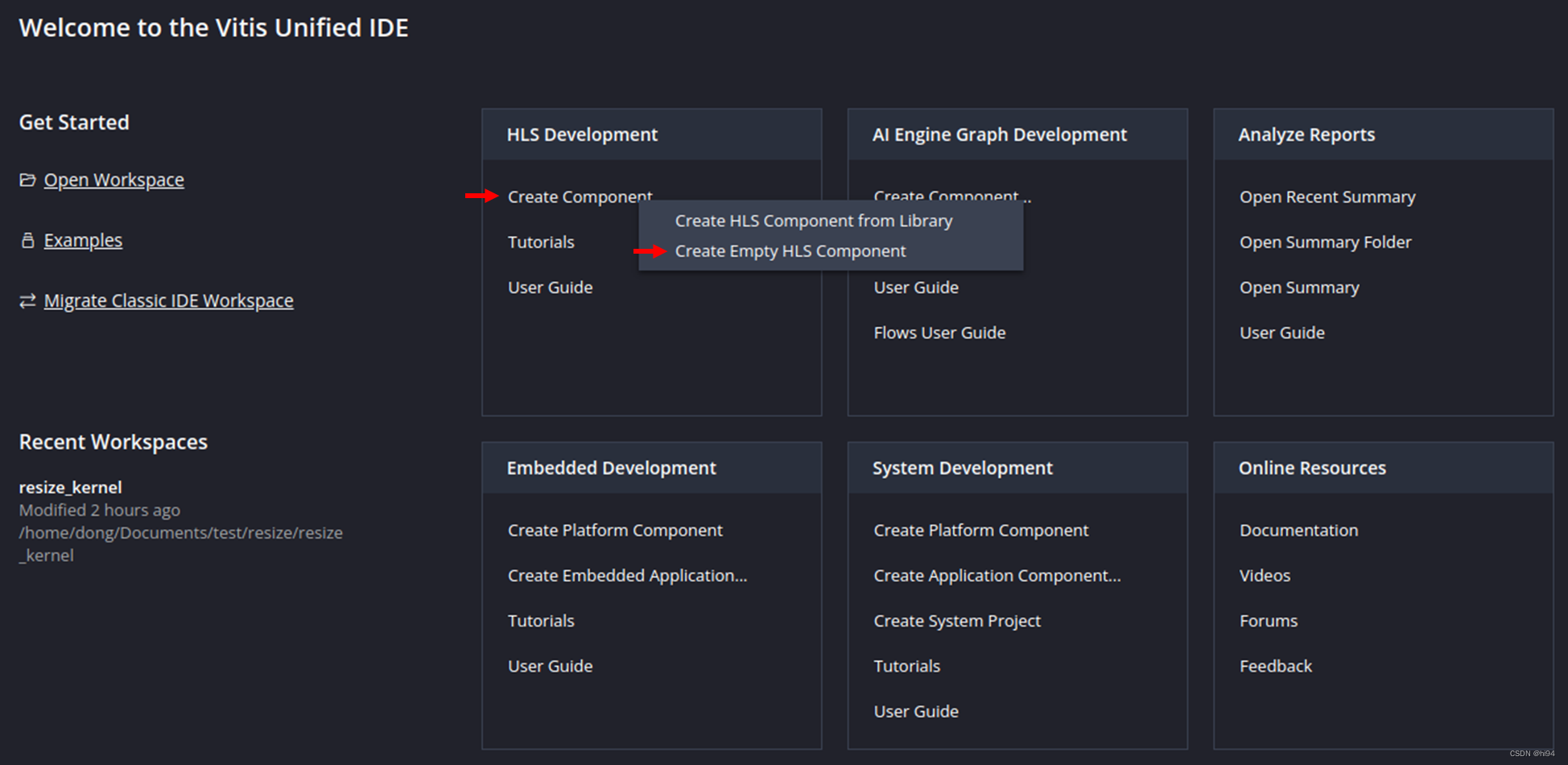

4. 創建?HLS 工程

4.1 選擇 HLS 組件

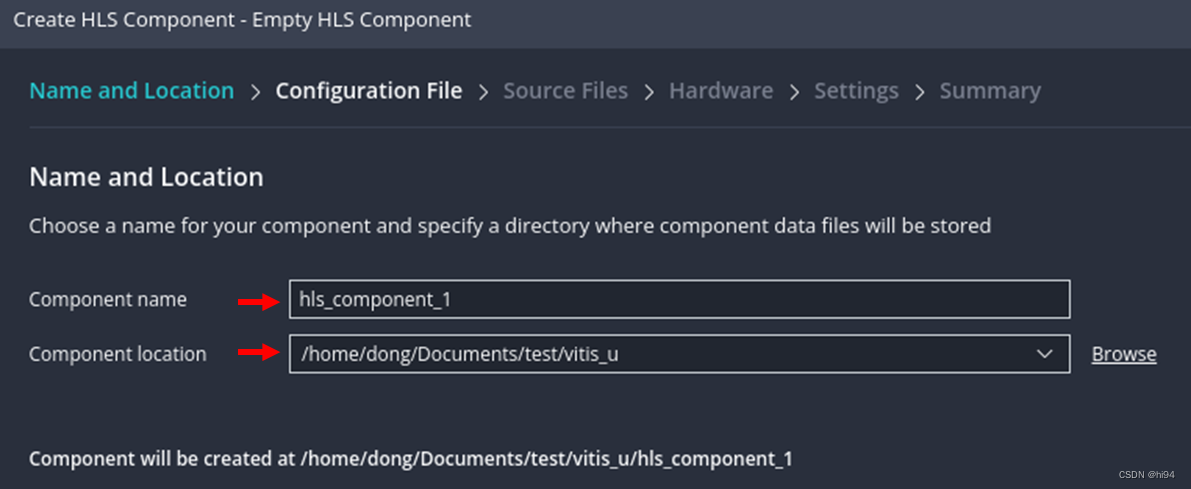

4.2 名稱和路徑

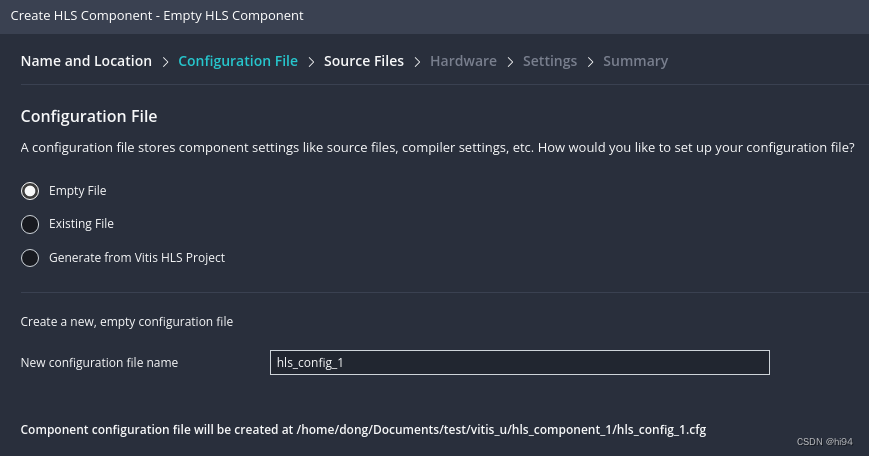

4.3 創建配置文件

4.4 選擇綜合源文件和TestBench

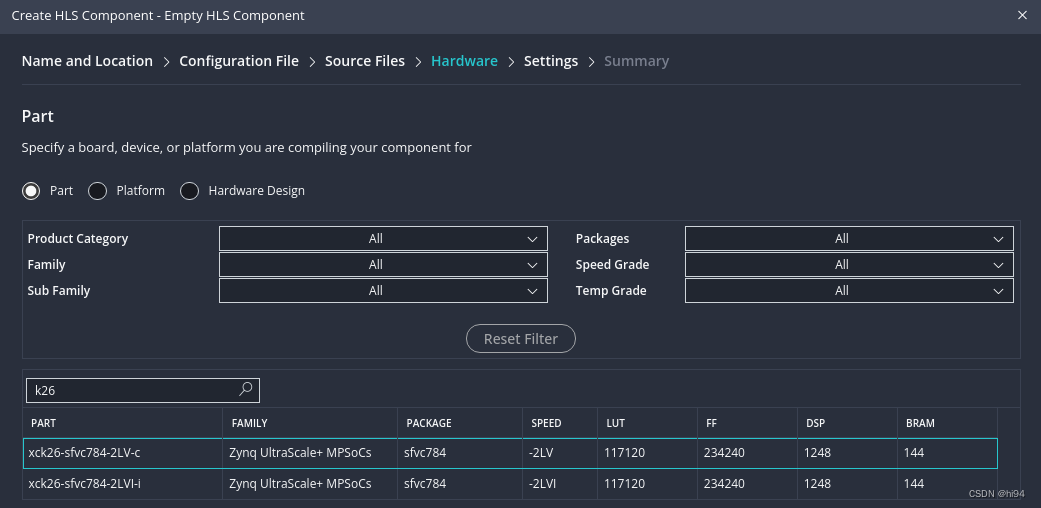

4.5 選擇硬件平臺

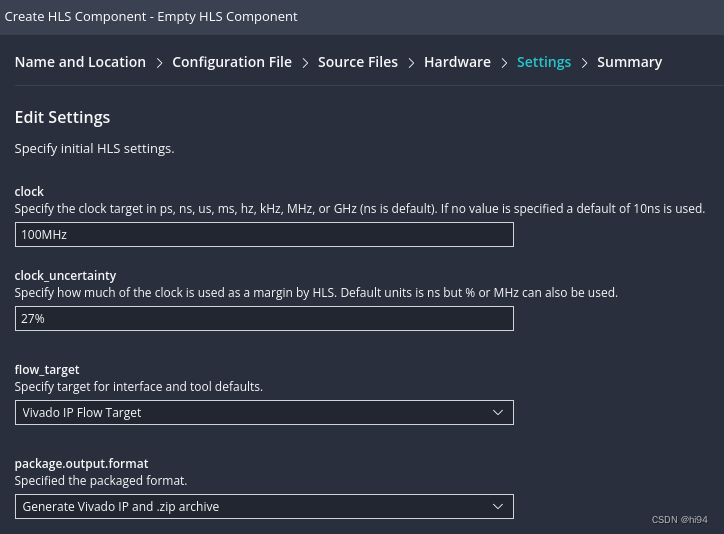

4.6 配置Clock和Flow

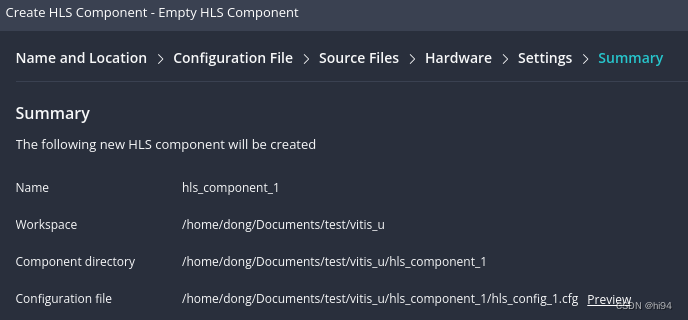

4.7 查看摘要

4.8 新建組件完畢

5. 總結

1. 簡介

Vitis 2024.1 已經完全不支持傳統界面了,新版軟件提供一個更加統一和現代化的用戶界面。

傳統的 Vitis GUI 像是一位老朋友,我們熟悉它的每一個角落,每一個命令,就像回到自己溫馨的家。新的統一軟件界面卻像是搬進了一個未知的新城市,盡管它充滿了現代化的便利和先進的功能,但那份親切感和熟悉度卻需要時間來建立。

命令行選項的變更、菜單結構的重組、工具鏈的整合,每一個細節都需要重新學習。筆者不得不告別那些熟悉的命令行快捷方式,轉而學習新的操作方法。

比如運行 vitis -w <workspace> 將直接進入新的界面,不在提供進入傳統 SDK 的模式。

這個過程中,我們可能會感到迷茫,甚至有些挫敗。

但正如所有的成長過程一樣,適應是必經之路。隨著時間的推移,我們將逐漸掌握新界面的奧秘,發現它帶來的高效和便捷。新的統一軟件界面不僅僅是一個工具的更新,它是我們作為開發者進步的象征,是我們與時俱進的證明。

據說從2023.2版本開始,Vitis統一IDE整合了多個工具,以便在Vitis、Vitis AIE編譯器/仿真器和Vitis HLS中提供一致的圖形用戶界面。

本文將探索這種變換的一角,開啟筆者適應新GUI的過程。

Vitis IDE的新特性簡述如下:

- 用戶界面友好:Flow Navigator助力工作流程管理,模板樣本啟迪新手,多任務并行執行提升效率。

- AI引擎優化:軟件仿真在x86環境下加快迭代,AI引擎的流水線和微代碼視圖得到多核支持和篩選功能增強。

- 界面現代化:提供明亮和暗色兩種主題,自定義快捷鍵簡化操作,命令選用板更加人性化,C++語法高亮和智能提示功能。

- 靈活切換:GUI和CLI模式無縫轉換,結合兩者優勢,配置文件實時展示,CLI構建項目,GUI用于調試和核心分析,操作記錄可用于批處理。

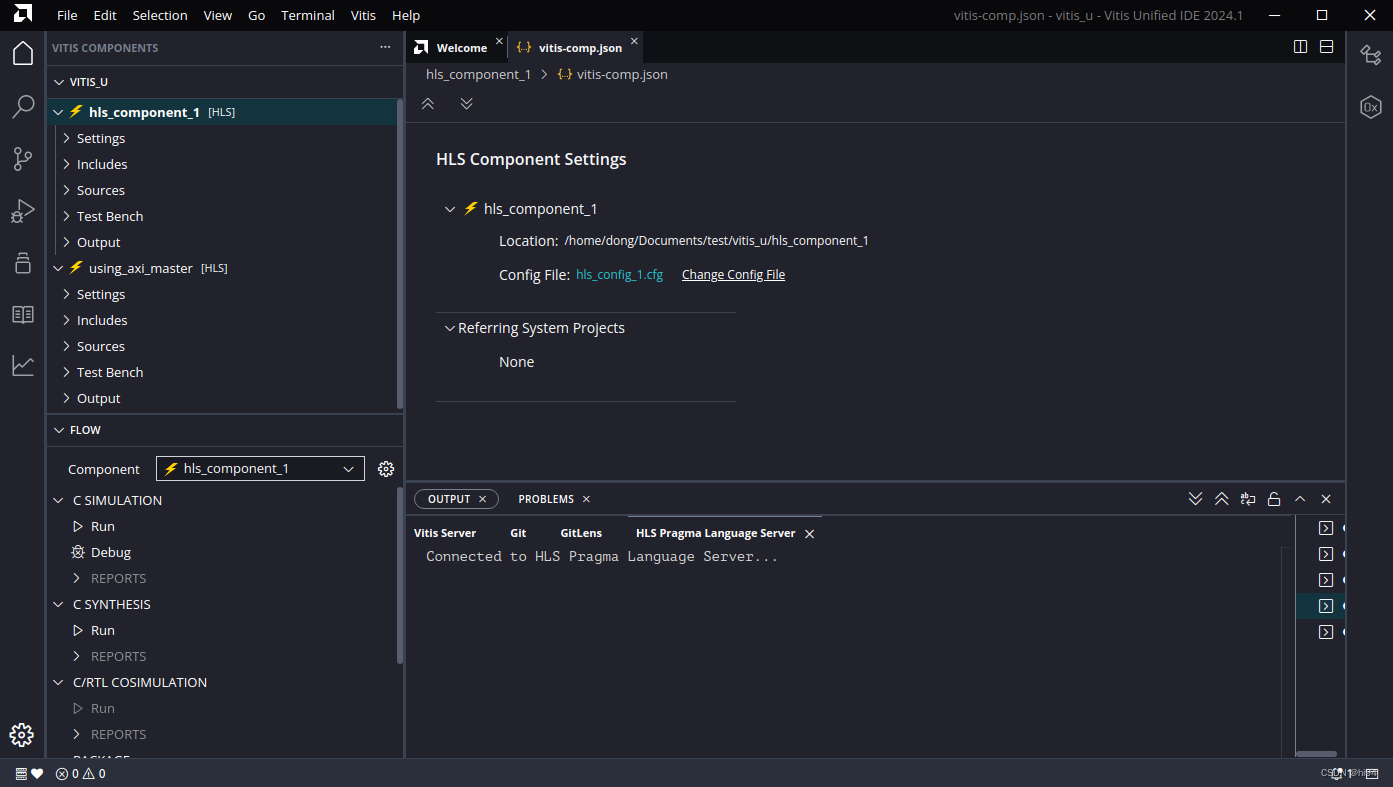

2. 界面展示

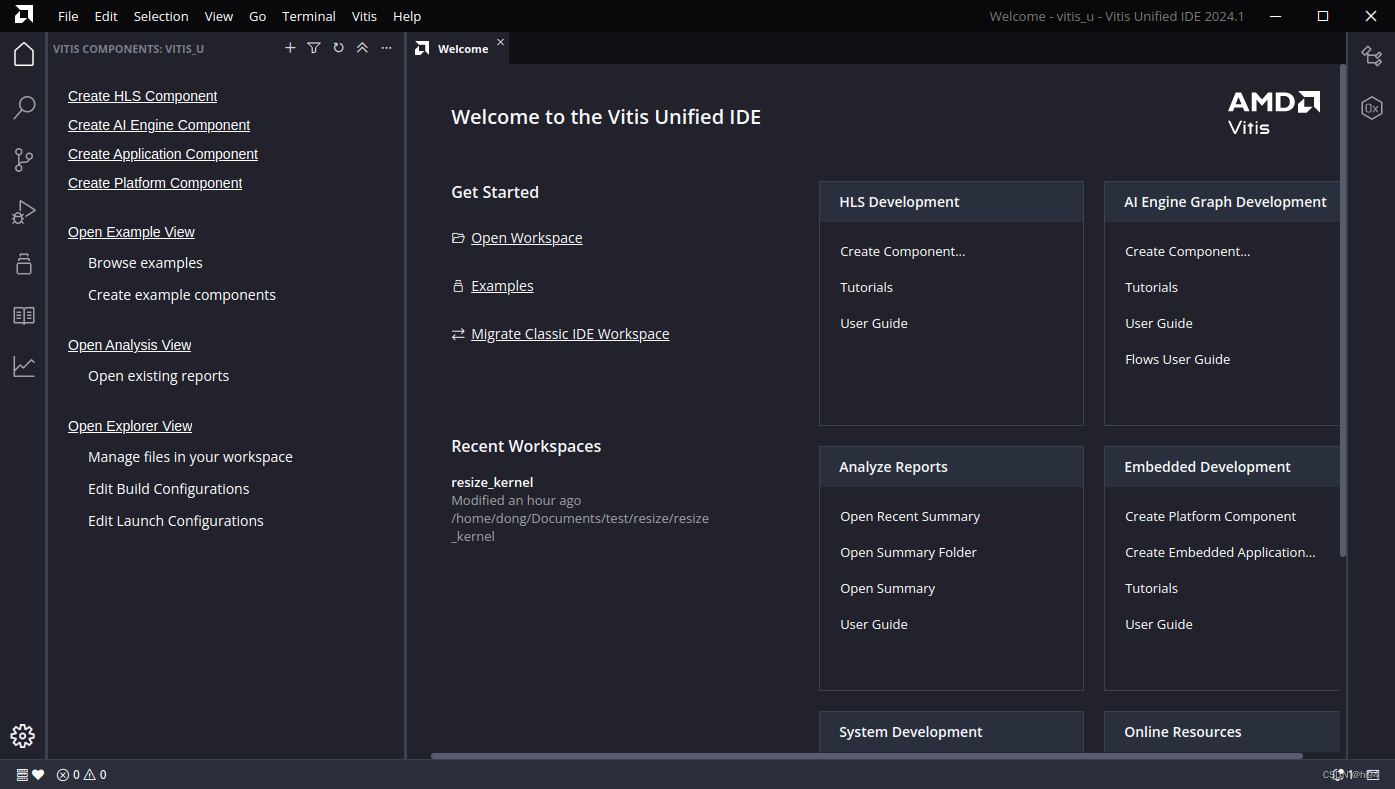

2.1 啟動

Vitis Unified 把 Vitis HLS 和 SDK 合并了。

啟動 Vitis Unified IDE:

vitis -w <workspace>workspace 是一個文件夾,用于保存設計的各種組件和項目。?

?

?

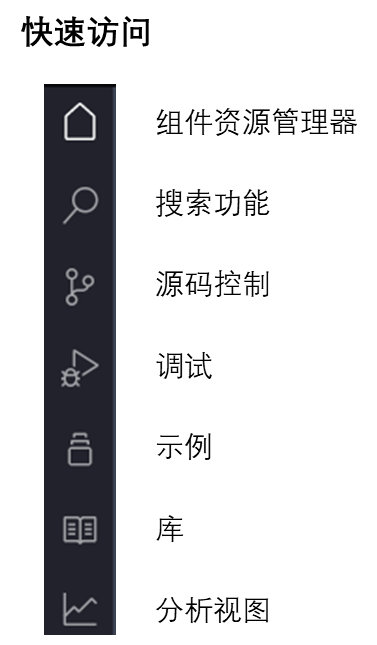

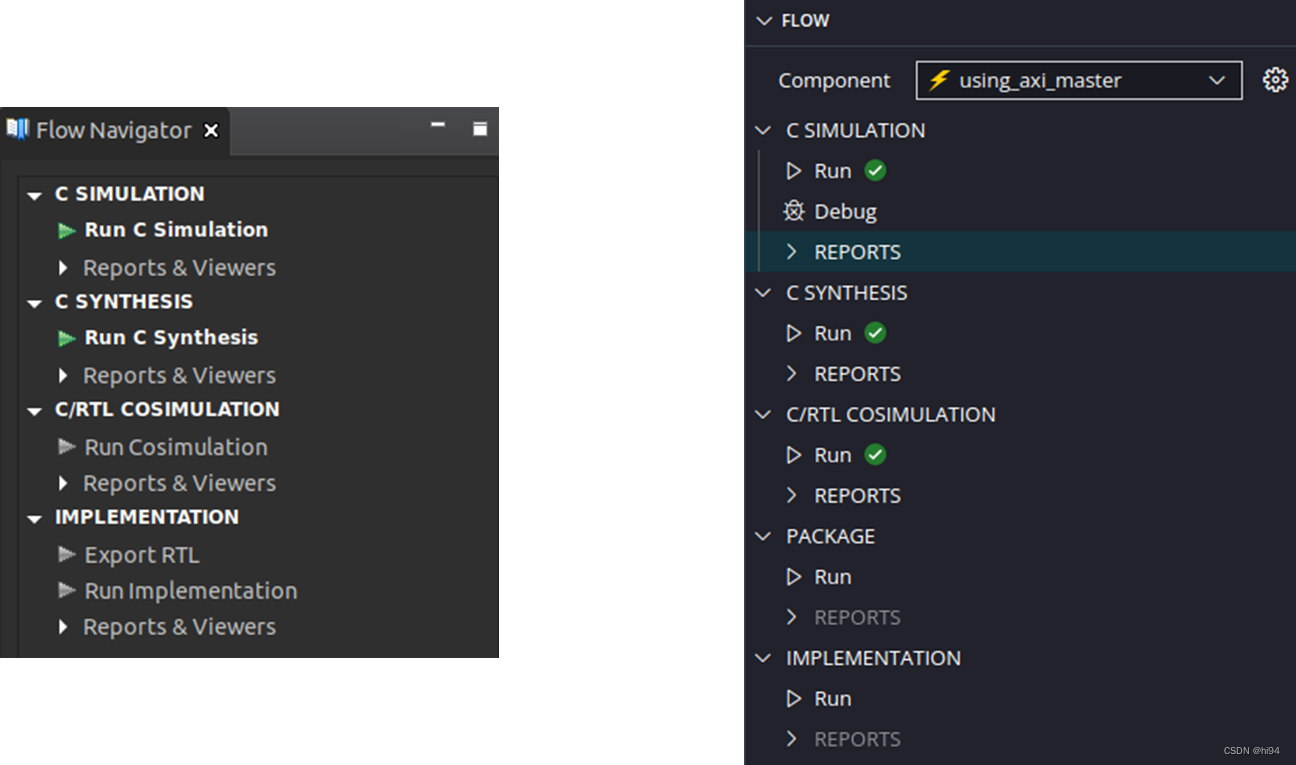

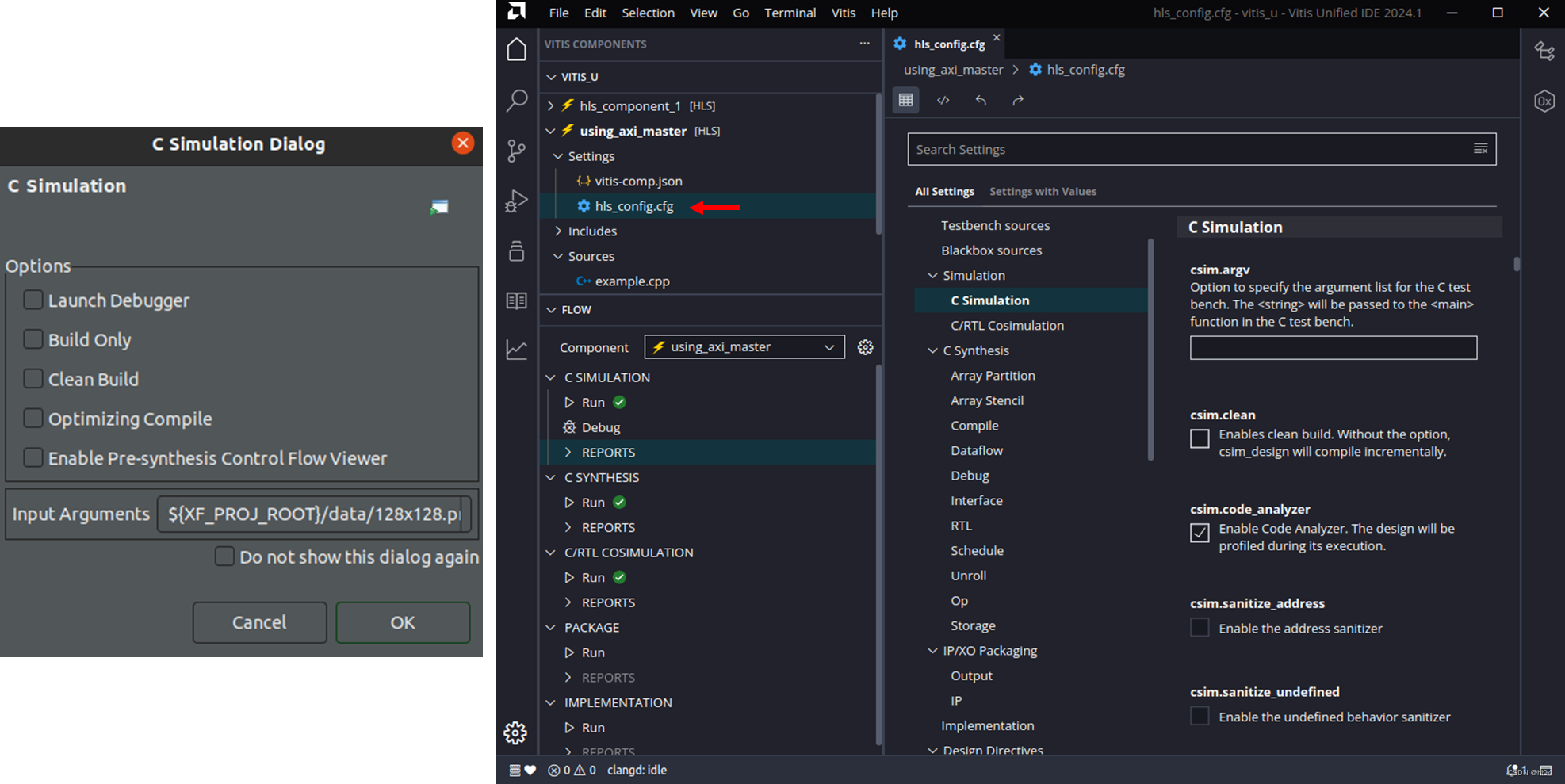

2.2 Flow Navigator

傳統 Vitis IDE 啟動每個 Flow,都會彈出配置對話框。新 Vitis Unified IDE,全部都在 Vitis Component下的 Settings 下進行設置,啟動每個 Flow 則會直接運行。?

2.1.1 C Simulation Dialog

Vitis Unified IDE

csim.clean:啟用清理構建。如果不選擇此選項,csim_design將進行增量編譯。

csim.code_analyzer:啟用代碼分析器。設計在執行過程中將被分析。

csim.sanitize_address:啟用地址檢查器

csim.sanitize_undefined:啟用未定義行為檢查器

csim.setup:當指定此選項時,C仿真二進制文件將被創建在當前解決方案的'csim'目錄中,但不會執行仿真。

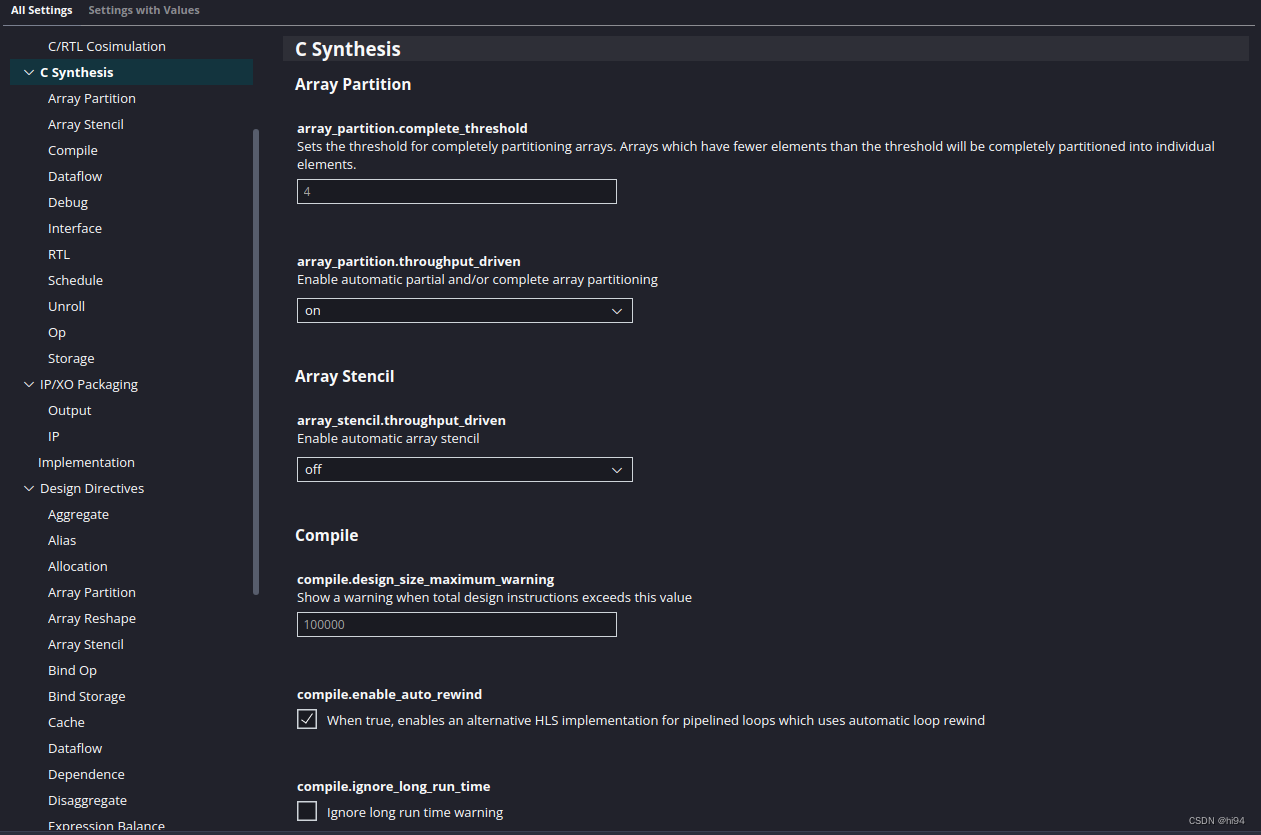

2.1.2 C Synthesis

Vitis IDE

Vitis Unified IDE

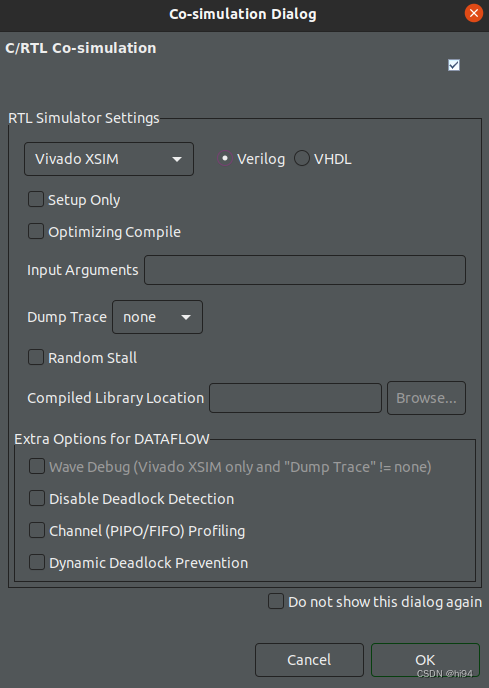

2.1.3 C/RTL Co-simulation

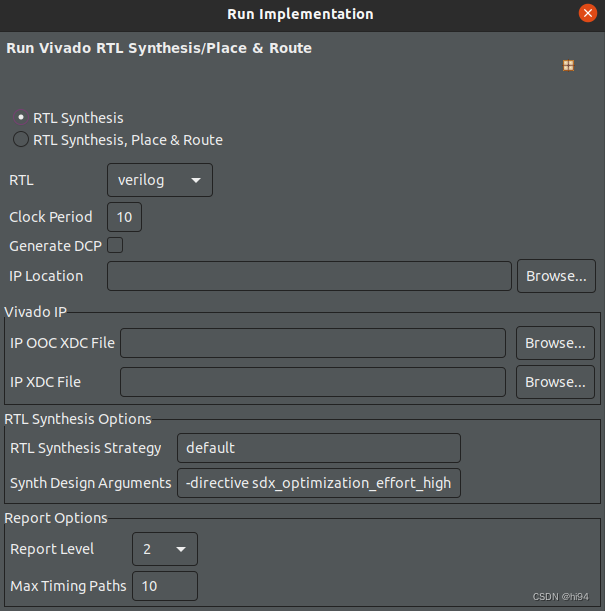

2.1.4 Implementation

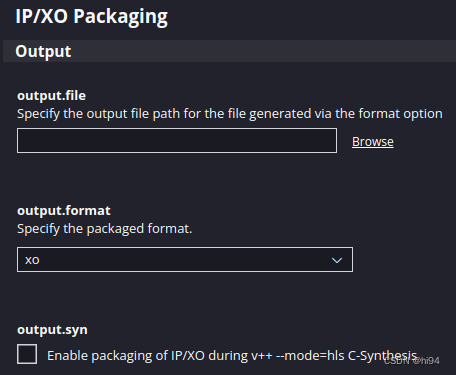

2.1.5 Package

在 Vitis Unified IDE 中獨有。

3. C Synthesis 詳解

在 Vivado IP Flow Target 流程中。

3.1 Classic Configuration Settings

3.1.1 config_array_partition

- complete_threshold, defalt=4

- throughput_driven, default=auto, (auto/off)

3.1.2 config_compile

- enable_auto_rewind, default=true

- ignore_long_run_time, default=false

- name_max_length, default=80

- no_signed_zeros, default=false

- pipeline_loops, default=64

- pipeline_style, default=frp, (stp/flp/frp)

- pragma_strict_mode, default=false

- pre_tcl

- unsafe_math_optimizations, default=false

3.1.3 config_dataflow

- default_channel, default=pingpong, (fifo/pingpong)

- disable_fifo_sizing_opt, default=false

- fifo_depth, default=2

- override_user_fifo_depth, default=0

- scalar_fifo_depth, default=2

- start_fifo_depth, default=2

- strict_mode, default=warning, (off/warning/error)

- strict_stable_sync, default=false

- task_level_fifo_depth, default=2

3.1.4 config_debug

- directory, default=.debug

- enable, default=false

3.1.5 config_export

3.1.6 config_interface

3.1.7 config_op

3.1.8 config_rtl

3.1.9 config_schedule

- enable_dsp_full_reg, default=true

3.1.10 config_storage

- fifo impl, default=autosrl, (bram/lutram/ram/memory/srl)

- fifo auto_srl_max_bits, default=1024

- fifo auto_srl_max_depth, default=2

3.1.11 config_unroll

- tripcount_threshold, default=0

3.2 New?Configuration Settings

3.2.1?Array Partition

- array_partition.complete_threshold: 設置完全分區數組的閾值。具有少于閾值元素的數組將被完全分區為單獨的元素。

- array_partition.throughput_driven: 啟用自動部分和/或完全數組分區。

3.2.2 Array Stencil

- array_stencil.throughput_driven: 啟用自動數組模板

3.2.3?Compile

- compile.design_size_maximum_warning: 當總設計指令超過此值時顯示警告

- compile.enable_auto_rewind: 當為真時,啟用用于流水線循環的替代 HLS 實現,該實現使用自動循環回繞

- compile.ignore_long_run_time: 忽略長運行時間警告

- compile.name_max_length: name_max_length 選項將指定函數名稱的最大長度。如果長度超過閾值,名稱的最后部分將被截斷。

- compile.no_signed_zeros: no_signed_zeros 選項將忽略浮點零的符號,以便編譯器可以對浮點操作進行最大程度的優化。

- compile.pipeline_flush_in_task: 啟用數據流程中的非回繞流水線默認刷新。

- compile.pipeline_loops: 循環的迭代次數大于此值將自動進行流水線處理。

- compile.pipeline_style: 設置默認流水線樣式,這是一種偏好而不是硬性約束。

- compile.pragma_strict_mode: 啟用錯誤而不是警告,用于舊的和不正確的編譯指示語法檢查。

- compile.unsafe_math_optimizations: unsafe_math_optimizations 選項將忽略浮點零的符號,并啟用浮點操作的結合性,以便編譯器可以對浮點操作進行激進的優化。

3.2.4 Dataflow

- dataflow.default_channel: 默認情況下,在使用數據流流水線時,將以ping-pong方式配置的RAM內存用于在函數或循環之間緩沖數據。當使用流式數據(其中數據總是按順序讀取和寫入)時,FIFO內存將更有效,并可以選擇為默認內存類型。請注意,必須使用 set_directive_array_stream 命令將數組設置為流式,以便執行FIFO訪問。

- dataflow.disable_fifo_sizing_opt: 禁用增加資源使用量并可能提高性能并減少死鎖的FIFO大小優化。

- dataflow.fifo_depth: 指定FIFO的默認深度的整數值。當使用ping-pong方式的存儲器時,此選項不起作用。如果未指定,通道中使用的FIFO將設置為最大生產者或消費者的大小(以較大者為準)。在某些情況下,這可能過于保守,引入比實際所需更大的FIFO。當用戶知道FIFO比所需更大時,可以使用此選項。在使用此選項時要小心,因為不正確的使用可能導致設計無法正確運行。

- dataflow.override_user_fifo_depth: 設置設計中所有FIFO的深度,除非深度已經大于覆蓋值。

- dataflow.scalar_fifo_depth: 指定標量值傳播FIFO的最小深度的整數值。如果未指定,最小值為 fifo_depth 選項的值(如果指定),否則為2。這些FIFO用于將數據流區域的標量參數值傳播到區域內具有前驅的處理過程。它們不影響功能正確性,但自動計算的大小不足可能導致性能損失甚至死鎖。粗略來說,最佳深度是發出標量的處理過程在最后讀取它的處理過程實際啟動前的平均次數。

- dataflow.start_fifo_depth: 指定啟動傳播FIFO的最小深度的整數值。如果未指定,最小值為 fifo_depth 選項的值(如果指定),否則為2。這些FIFO用于將 ap_start 握手信號轉發到區域內具有前驅的處理過程。它們不影響功能正確性,但自動計算的大小不足可能導致性能損失。粗略來說,最佳深度是處理過程應該被允許提前啟動的預期平均次數。

- dataflow.strict_mode: 設置數據流規范形式消息的嚴重程度。

- dataflow.strict_stable_sync: 穩定端口強制與 done 同步。

- dataflow.task_level_fifo_depth: 默認任務級FIFO深度(用于自動創建的用于在處理過程之間傳輸標量的FIFO)。

3.2.5 Debug

- debug.directory: 相對于 solution 方案目錄的輸出目錄名稱

- debug.enable: 啟用調試文件生成

- debug.enable_verbose_report: 啟用覆蓋率報告

3.2.6 interface

3.2.7 RTL

3.2.8 Schedule

- schedule.enable_dsp_full_reg: 啟用完整的 dsp48 寄存器利用率

3.2.9 Unroll

- unroll.tripcount_threshold: 自動展開循環,其迭代次數少于此閾值。

3.2.10 Op

- hls.syn.op: 配置不同運算符的默認實現樣式和延遲。

3.2.11 Storage

- hls.syn.storage: 配置不同類型存儲元素的默認實現樣式和延遲。

4. 創建?HLS 工程

在 Vitis Unified IDE 中,PL 內核被創建為 HLS 組件,你可以在 C/C++ 源代碼上運行 C 仿真,使用編譯指示或指令優化設計,綜合和分析結果,并將設計導出為 Vivado IP 與 Vivado Design Suite 一起使用,或作為 Vitis 內核 ( .xo ) 文件在更高級別的系統項目中使用。

4.1 選擇 HLS 組件

4.2 名稱和路徑

4.3 創建配置文件

4.4 選擇綜合源文件和TestBench

這里我們先跳過,后續再添加。

編寫良好的測試平臺可以極大地提高工作效率,因為 C 函數的執行速度比 RTL 仿真快幾個數量級。在綜合之前使用 C 來開發和驗證算法比開發和調試 RTL 代碼要快得多。?

4.5 選擇硬件平臺

4.6 配置Clock和Flow

當未指定時鐘不確定度時,默認時鐘不確定性為時鐘周期的 27%。?

4.7 查看摘要

4.8 新建組件完畢

5. 總結

在Vitis 2024.1版本中,傳統的Vitis GUI已經被全新的統一軟件界面所取代。這個變化雖然初看令人生疏,但它實際上為開發者們帶來了更加高效和現代化的工作環境。新界面的Flow Navigator、多任務并行執行、AI引擎優化、以及界面的現代化設計,都極大地提升了工作流程的管理和執行效率。此外,新的統一軟件界面還提供了GUI和CLI模式的無縫轉換,使得項目構建和調試更加靈活。雖然適應新界面需要時間,但隨著熟悉度的提升,開發者們將能夠充分利用這些新特性,以更快的速度迭代和優化他們的工程。總的來說,Vitis的這次更新不僅僅是界面上的改變,更是開發者與時俱進、不斷進步的體現。

)

DroneCAN 適配器節點(二))

![AI論文速讀 | 2024[KDD]自適應時空圖神經網絡中圖中獎彩票的預訓練識別](http://pic.xiahunao.cn/AI論文速讀 | 2024[KDD]自適應時空圖神經網絡中圖中獎彩票的預訓練識別)

)