目錄

1.單片機啟動流程

2.看門狗

3.最小系統

4.ROM、RAM、Flash

5.EPROM、EEPROM

6.Bootloader與OTA

7.NAND FLASH 和NOR FLASH

相同點

區別

適用場景

8.CPU、MPU、MCU、SOC、SOPC

9.交叉編譯

10.寄存器

寄存器的作用

寄存器與內存的區別

11.Cortex-M3寄存器組

通用寄存器

特殊功能寄存器

12.保存、恢復現場的詳細操作

13.ARM Cortex-M3和M4的區別

14.異常和中斷

15.中斷和DMA的區別

16.DMA

17.中斷響應執行流程

1.單片機啟動流程

單片機的啟動流程是指從上電或復位開始到應用用戶主程序執行的一系列自動操作過程,不同架構的單片機流程略有差異,但核心邏輯相似。

首先,當單片機接通電源或收到復位信號(如外部復位引腳觸發、看門狗超時、軟件復位指令等),硬件電路會先進行復位操作,讓內部所有寄存器回到初始狀態,確保系統從已知的初始條件開始運行。

接下來,單片機通常會執行一段固化在芯片內部的 “啟動代碼”(也叫引導程序或啟動程序),這段代碼由芯片廠商預先編寫,存放在只讀存儲器(ROM 或 Flash 的特定區域)中,用戶無法修改。啟動代碼的主要任務包括初始化關鍵硬件,比如配置系統時鐘(從默認的低速內部時鐘切換到高速外部時鐘或 PLL 鎖相環,以滿足運行速度需求)、設置堆棧指針(為后續程序運行分配棧空間,用于函數調用和局部變量存儲)、初始化數據段和 BSS 段(將程序中的全局變量和靜態變量從 Flash 加載到 RAM 中,并對未初始化的變量清零)。

完成這些初始化后,啟動代碼會尋找用戶程序的入口點(通常是 main 函數的地址),并跳轉到該地址,此時單片機開始執行用戶編寫的主程序,啟動流程結束。

對于一些支持程序下載或在線編程的單片機,啟動流程中可能還會包含一段引導加載程序(Bootloader),用于檢測是否需要從外部存儲(如串口、SPI Flash)加載新的程序,如果不需要則繼續執行上述常規啟動步驟,這使得單片機可以方便地更新固件而無需專用編程器。

2.看門狗

在單片機系統中,看門狗(Watchdog Timer,簡稱 WDT)是一種用于監控程序運行狀態、防止程序 “死機” 或進入無限循環的硬件定時器,本質上是一套保障系統可靠性的 “程序異常自救機制”。單片機在運行過程中,可能會因為電磁干擾、硬件臨時故障、代碼漏洞(比如數組越界導致的邏輯混亂、意外觸發的死循環等),使得程序脫離預設的正常執行流程,陷入 “假死” 狀態,無法完成原本的控制、采集等功能,而看門狗的核心作用就是在這種情況下,強制讓失控的系統重啟,恢復到初始運行狀態,避免長時間 “死機” 帶來的設備失效或功能異常。

看門狗的工作原理圍繞 “定時器計時” 和 “超時觸發復位” 展開,其中關鍵操作是 “喂狗”。具體來說,程序啟動后首先需要初始化看門狗,設定一個合適的 “超時時間”(比如幾十毫秒到幾秒,根據單片機型號和實際需求確定),初始化完成后,看門狗定時器會開始從 0 向上計數(或從預設值向下遞減)。如果程序正常運行,就需要在定時器計數達到設定的超時時間之前,通過代碼向看門狗的特定寄存器寫入預設的 “喂狗指令”(比如某些單片機要求連續寫入 0x55 和 0xAA),寫入指令后,定時器會立即清零并重新開始計時,從而避免觸發復位;但如果程序因為故障陷入失控狀態,就無法按時執行 “喂狗” 操作,此時看門狗定時器會一直計數直到達到超時時間,隨后會自動觸發單片機的系統復位信號,強制單片機重新上電啟動,讓程序從初始狀態重新運行,脫離失控困境。

單片機的看門狗主要分為內置和外置兩種類型,內置看門狗是集成在單片機芯片內部的硬件模塊,像 51 單片機、STM32、AVR 等主流型號基本都自帶,它無需額外添加硬件,成本較低,且能通過軟件靈活調整超時時間,適合消費電子、智能家居等大多數常規場景;外置看門狗則是獨立的外部芯片(如 MAX813L、X5045 等),需要通過單片機的 I/O 口或專用引腳進行 “喂狗”,雖然會額外占用 PCB 空間和增加成本,但獨立性更強,即便單片機內部核心硬件(如時鐘模塊)出現故障,仍能正常觸發復位,因此更適合工業控制、汽車電子、醫療設備等對可靠性要求極高的場景。

3.最小系統

STM32 的最小系統是指能讓 STM32 單片機正常工作的最基礎電路組成。它通常由 STM32 主芯片、電源電路、復位電路、時鐘電路和下載調試接口這幾部分構成。

電源電路負責提供穩定的工作電壓(一般為 3.3V),通過穩壓芯片將外部輸入的電壓(如 5V)轉換為單片機所需的穩定電壓,同時包含濾波電容以濾除電源噪聲。

復位電路用于讓單片機在需要時回到初始狀態,通常由復位按鍵、電阻和電容組成,按下按鍵時產生復位信號,松開后單片機重新啟動。

時鐘電路為單片機提供工作時序,包括外部高速時鐘(如 8MHz 晶振配合兩個電容)和內部 RC 振蕩器,外部晶振能提供更高精度的時鐘信號,滿足精確計時或高速外設的需求。

下載調試接口(如 SWD 接口,由 SWCLK 和 SWDIO 兩根線組成)用于程序的下載和在線調試,方便開發者將編寫好的程序燒錄到單片機中,并進行運行狀態的調試。

這些部分共同協作,確保 STM32 單片機能夠正常上電、啟動、運行程序并支持開發調試,是構建任何基于 STM32 的電子系統的基礎。

4.ROM、RAM、Flash

在單片機(如 STM32)及各類電子系統中,ROM、RAM、Flash 都是核心存儲部件,但它們的存儲特性、用途和工作原理差異很大,分別對應不同的功能需求。

ROM(只讀存儲器,Read-Only Memory)是一種斷電后數據不會丟失的 “非易失性存儲”,早期的 ROM 數據由廠商在生產時固化,用戶無法修改,主要用來存放單片機的啟動代碼、基礎驅動程序等固定不變的內容,比如早期 51 單片機里的引導程序就存在 ROM 中。不過現在常見的是 “可擦寫 ROM”(如 EPROM、EEPROM),用戶可以通過專用工具修改數據,但擦寫次數有限(通常上萬次),且擦寫速度較慢,所以更多用于存儲少量需要長期保存、很少修改的信息,比如設備參數、校準數據等。

RAM(隨機存取存儲器,Random Access Memory)則是 “易失性存儲”,斷電后數據會立即丟失,它的特點是讀寫速度極快,能高效配合 CPU 進行數據交換,主要用途是臨時存放程序運行時的動態數據 —— 比如程序中的局部變量、函數調用時的棧數據、實時采集的傳感器數據等。CPU 在執行程序時,會把需要頻繁操作的數據從 Flash 或 ROM 加載到 RAM 中,因為 RAM 的讀寫速度遠快于非易失性存儲,能大幅提升程序運行效率,但由于斷電失數據的特性,它無法長期保存信息,每次上電后都需要重新從其他存儲中加載數據。

Flash(閃存)是目前單片機中最常用的 “非易失性存儲”,兼具了 ROM 的斷電保數據特性和接近 RAM 的讀寫便捷性(但速度仍慢于 RAM),它的擦寫次數比 EEPROM 更多(通常可達 10 萬次以上),且存儲容量更大,成本相對較低。在 STM32 等現代單片機中,Flash 主要用來存放用戶編寫的應用程序(比如控制邏輯、算法代碼),單片機上電后會從 Flash 中讀取程序指令并執行;同時,Flash 也能用來存儲需要長期保存、偶爾修改的大量數據,比如日志信息、配置文件等。不過 Flash 的擦寫有 “按塊擦除” 的特點(不能像 RAM 那樣單個字節隨意修改),所以在寫入數據時需要配合特定的驅動程序來管理擦寫操作。

簡單來說,三者的核心區別可以概括為:ROM(含 EEPROM)適合存少量、長期不變或極少修改的數據;RAM 適合存程序運行時臨時用、高速讀寫的數據;Flash 則適合存大量的程序代碼和需要長期保存、偶爾修改的數據,三者協同工作,共同支撐單片機的正常運行。

5.EPROM、EEPROM

EPROM(可擦除可編程只讀存儲器)和 EEPROM(電可擦除可編程只讀存儲器)都是可擦寫的非易失性存儲設備,斷電后數據不會丟失,常用于存儲需要長期保存且可能偶爾修改的信息,但兩者在擦除方式、操作便捷性和應用場景上有明顯區別。

EPROM 的擦除需要通過紫外線照射芯片表面的透明窗口來完成,整個過程通常需要幾分鐘,且擦除時必須將芯片從電路板上取下,操作繁瑣,適合早期對存儲修改需求較少的場景,比如早期單片機中的固定程序存儲。

EEPROM 則改進了擦除方式,可通過電信號直接擦除和改寫數據,無需物理拆卸芯片,甚至能在系統運行中在線修改(即 “在系統編程”),擦寫速度也更快(毫秒級),雖然存儲容量通常小于 EPROM,且擦寫次數相對有限(一般幾萬到幾十萬次),但因其操作便捷性,在現代電子設備中應用更廣泛,比如用于存儲設備參數、校準數據、用戶設置等需要靈活修改的少量信息,像智能儀表的配置參數、汽車電子中的故障碼存儲等場景常能見到它的身影。

6.Bootloader與OTA

Bootloader 是嵌入式系統中在應用程序運行之前執行的一段引導程序,相當于系統的 “啟動管家”,主要負責初始化硬件、準備運行環境,并最終將控制權轉交給用戶應用程序。在 STM32 等單片機中,Bootloader 通常分為兩種:一種是芯片出廠時固化在系統存儲器中的 “內置 Bootloader”,由芯片廠商(如 ST 公司)編寫,用戶無法修改,它支持通過串口、SPI、I2C 等外設接口接收程序數據,實現對主 Flash 的編程(即 ISP 下載),方便用戶在沒有專用編程器的情況下更新固件;另一種是用戶自定義的 Bootloader,由開發者根據需求編寫并燒錄到主 Flash 的特定區域,這類 Bootloader 可以實現更靈活的功能,比如從 SD 卡、以太網或無線模塊讀取程序鏡像進行升級(即 OTA 升級),或者對應用程序進行校驗、加密保護等。

Bootloader 的工作流程通常包括幾個階段:

- 首先進行最基礎的硬件初始化,如配置時鐘、初始化關鍵外設(如用于通信的串口)和設置堆棧;

- 然后根據預設的觸發條件(如特定按鍵按下、收到升級指令)判斷是否需要執行升級操作,若需要則通過相應接口接收新的程序數據并寫入 Flash;

- 若無需升級,則跳轉到用戶應用程序的起始地址,將系統控制權移交,之后 Bootloader 的使命完成,應用程序開始運行。

這種分層啟動的設計,既保證了系統能夠可靠啟動,又為程序更新和功能擴展提供了便利,是嵌入式系統中實現固件升級和系統管理的重要機制。

OTA 是一種具體的程序更新方式,指通過無線通信(如 Wi-Fi、藍牙、蜂窩網絡等)遠程傳輸新的固件鏡像,讓設備無需物理連接(如用數據線接電腦)就能完成升級。

在實際應用中,OTA 的實現依賴于 Bootloader:設備運行時,應用程序若收到遠程的 OTA 升級指令,會將新固件暫時存放在存儲區(如 Flash 的特定分區),然后觸發系統復位;復位后 Bootloader 啟動,檢測到存儲區有新固件,便執行擦除舊程序、寫入新程序的操作,完成后再跳轉到新程序運行。這里的 Bootloader 需要被設計為支持從存儲區讀取新固件并處理升級邏輯,而 OTA 則解決了 “如何將新固件傳到設備” 的問題,兩者結合讓嵌入式設備(如物聯網傳感器、智能家居設備)的遠程升級成為可能,大幅降低了維護成本。

7.NAND FLASH 和NOR FLASH

Flash分為NAND flash和NOR flash兩種。它們的核心功能都是斷電后保留數據。NOR的特點是芯片內執行(XIP, eXecute In Place),這樣應用程序可以直接在flash閃存內運行,不必再把代碼讀到系統RAM中。NOR的傳輸效率很高,但是很低的寫入和擦除速度大大影響了它的性能。而NAND則是高數據存儲密度的理想解決方案。NAND的寫入和擦除速度更快,且存儲容量更大,但是用戶不能直接運行NAND Flash上的代碼。

相同點

- 非易失性:兩者均為非易失性存儲,斷電后數據不會丟失,這是相對于 RAM(隨機存取存儲器)的核心優勢。

- 基于浮柵晶體管:存儲原理均依賴 “浮柵晶體管”(Floating Gate Transistor),通過在浮柵中捕獲電荷來表示數據(0/1)。

- 可擦除重寫:支持數據的擦除和重寫(需按塊 / 扇區操作,不能直接修改單個字節)。

區別

| 對比維度 | NAND Flash | NOR Flash |

|---|---|---|

| 存儲結構 | 以 “塊(Block)” 為單位組織,塊內包含頁(Page),類似硬盤結構 | 以 “扇區(Sector)” 為單位,支持隨機地址訪問,類似內存結構 |

| 讀取方式 | 需通過頁地址順序讀取,不支持隨機地址直接訪問(類似硬盤) | 支持隨機地址讀取(直接訪問任意地址),速度快 |

| 寫入 / 擦除特性 | 寫入前需先擦除塊(塊級擦除),擦除速度快(毫秒級) | 寫入前需先擦除扇區(扇區級擦除),擦除速度慢(秒級) |

| 容量與成本 | 容量大(可達 TB 級),單位存儲成本低 | 容量小(通常幾十 MB 到幾百 MB),單位存儲成本高 |

| 數據總線寬度 | 多為 8 位或 16 位總線,并行讀取效率高 | 多為 1 位或 8 位總線,適合小數據量讀取 |

| 壞塊管理 | 存在天然壞塊,需通過固件 / 軟件進行壞塊管理 | 幾乎無壞塊,無需復雜管理 |

| 可靠性與壽命 | 擦寫次數相對較低(SLC 約 10 萬次,MLC 約 1 萬次) | 擦寫次數較高(SLC 可達 10 萬次以上) |

| 典型應用場景 | 大容量數據存儲(U 盤、SSD、存儲卡、嵌入式系統數據區) | 代碼存儲(嵌入式系統的程序區、BIOS、固件) |

適用場景

-

選 NOR Flash:

當需要存儲程序代碼并直接運行(如嵌入式系統的 Bootloader、BIOS、小型固件),或需要頻繁隨機讀取小數據時(如配置信息),優先選擇 NOR。例如:路由器的啟動程序、汽車電子的控制固件。 -

選 NAND Flash:

當需要大容量數據存儲(如文件、圖像、日志),或需要高寫入 / 擦除效率時,優先選擇 NAND。例如:U 盤、SD 卡、固態硬盤(SSD)、智能手機的存儲芯片。

8.CPU、MPU、MCU、SOC、SOPC

CPU(Central Processing Unit),是一臺計算機的運算核心和控制核心。CPU由運算器、控制器和寄存器及實現它們之間聯系的數據、控制及狀態的總線構成。差不多所有的CPU的運作原理可分為四個階 段:提取(Fetch)、解碼(Decode)、執行(Execute)和寫回(Writeback)。 CPU從存儲器或高速緩沖存儲器中取出指令,放入指令寄存器,并對指令譯碼,并執行指令。所謂的計算機的可編程性主要是指對CPU的編程。

MPU(Micro Processor Unit)微處理器(不是微控制器),通常代表一個功能強大的CPU(可理解為增強版的CPU),但不是為任何已有的特定計算目的而設計的芯片。這種芯片往往是個人計算機和高端工作站的核心CPU。最常見的微處理器是Motorola的68K系列和Intel的X86系列。

MCU(Micro Control Unit)微控制器,是指將計算機的 CPU、RAM、ROM、定時計數器和多種I/O接口集成在一片芯片上形成的芯片,比如51,avr這些芯片,內部除了CPU外還有RAM、ROM,直接加簡單的外圍器件(電阻,電容)就可以運行代碼了。而MPU如x86這些就不能直接放代碼了,它只不過是增強版的CPU,所以得添加RAM、ROM。MCU,MPU最主要的區別就是能否直接運行代碼。

SOC(System on Chip)片上系統,MCU只是芯片級的芯片,而SOC是系統級的芯片,它既像MCU(51,avr)那樣有內置RAM、ROM,同時又像MPU那樣強大,不單單是放簡單的代碼,可以放系統級的代碼,也就是說可以運行操作系統(將MCU的集成化與MPU的強處理力的優點二合一)。

SOPC(System On a Programmable Chip)可編程片上系統(FPGA),上面4點的硬件配置是固化的,就是說51單片機就是51單片機,不能變為avr,而avr就是avr不是51單片機,他們的硬件是一次性成型的,能改的只有軟件配置,也就是改代碼。而SOPC則是硬件配置,軟件配置都可以修改。硬件是可以自己構建的,也就是說這個芯片是自己構造出來的,這顆芯片我們叫“白片”,什么芯片都不是,把硬件配置信息下載進去了,他就是相應的芯片了,可以讓他變成51,也可以是avr,甚至arm。同時SOPC是在SOC基礎上來的,所以他也是系統級的芯片。記得當把他變成arm時還得加外圍ROM,RAM之類的,不然就是MPU了。

9.交叉編譯

交叉編譯指在一臺計算機(通常稱為主機,如 PC 機)上編譯出能在另一種不同架構的目標設備(如單片機、嵌入式處理器)上運行的程序。由于主機和目標設備的硬件架構、指令集不同(比如 PC 機常用 x86 架構,而 STM32 單片機采用 ARM 架構),直接在主機上用本地編譯器生成的程序無法在目標設備上運行,因此需要專門的交叉編譯工具鏈。

交叉編譯的核心是使用針對目標架構的編譯器、匯編器和鏈接器,這些工具能將源代碼轉換為目標設備可識別的機器碼。例如,開發 STM32 程序時,開發者在 Windows 或 Linux 系統(主機)上使用 arm-none-eabi-gcc 等交叉編譯工具,將 C/C++ 代碼編譯成 ARM 架構的二進制文件,再通過下載工具燒錄到單片機中運行。

這種方式的優勢在于充分利用主機的強大計算能力和便捷的開發環境,同時滿足目標設備的運行需求,尤其適合資源有限的嵌入式設備 —— 這些設備通常無法直接在自身上安裝編譯器或運行復雜的編譯過程。交叉編譯過程中需要正確配置目標設備的架構、處理器型號、內存布局等參數,以確保生成的程序能在目標硬件上正常運行,是嵌入式開發中連接開發環境與目標設備的關鍵環節。

10.寄存器

寄存器(Register)是CPU內部集成的高速存儲單元,用于用于臨時存放數據、指令和地址,是 CPU 與內存、外設之間數據交互的 “中轉站”。它的核心特點是速度極快(納秒級,比內存快 1-2 個數量級),但容量極小(通常以字節或字為單位,整個 CPU 的寄存器總量一般在幾十到幾百字節)。

寄存器的作用

寄存器是 CPU 運行的 “臨時工作臺”,主要功能包括:

- 暫存數據:存儲 CPU 正在運算的數據(如加法運算中的兩個操作數和中間結果)。

- 存放指令:存儲即將執行的指令(或指令的地址)。

- 記錄狀態:存儲 CPU 的運行狀態(如是否產生進位、是否發生中斷等)。

- 控制操作:部分寄存器可通過設置特定位,控制 CPU 的工作模式(如中斷開關、特權級切換)。

寄存器與內存的區別

寄存器和內存都是存儲設備,但定位完全不同,核心差異如下:

| 對比維度 | 寄存器(Register) | 內存(Memory,如 DRAM) |

|---|---|---|

| 物理位置 | 集成在 CPU 內部 | 位于 CPU 外部(通過總線連接) |

| 速度 | 極快(納秒級,與 CPU 主頻匹配) | 較慢(幾十納秒,需通過總線傳輸) |

| 容量 | 極小(通常幾十到幾百字節) | 較大(GB 級,如 8GB、16GB) |

| 用途 | 臨時存放 CPU 正在處理的數據 / 指令 | 長期存放程序和數據(斷電丟失) |

| 訪問方式 | 直接通過指令操作(如MOV R0, #5) | 通過地址總線和數據總線訪問 |

例如,要控制 GPIO 引腳輸出高低電平,需向對應的 GPIO 口的輸出數據寄存器寫入特定值;要設置串口的波特率,需配置串口的波特率寄存器;而通過讀取狀態寄存器,可以知道外設當前是否處于忙碌、完成或出錯狀態。

每個寄存器都有唯一的地址,CPU 通過訪問這些地址來讀寫寄存器的值,進而實現對硬件的控制。不同外設(如定時器、ADC、SPI 等)都有各自對應的寄存器組,開發者需要根據芯片手冊了解每個寄存器的功能、位定義及合法值,通過編寫代碼配置這些寄存器,才能讓硬件按照預期工作。這種直接操作寄存器的方式能精確控制硬件行為,是嵌入式開發的底層基礎,盡管許多開發中會使用庫函數封裝寄存器操作。

11.Cortex-M3寄存器組

Cortex-M3 處理器采用 32 位架構,其寄存器組可分為通用寄存器、特殊功能寄存器和程序狀態寄存器三類,以下是詳細說明:

通用寄存器

Cortex-M3 有 16 個 32 位通用寄存器(R0-R15),其中 R0-R12 為純通用寄存器,R13-R15 有特殊用途:

| 寄存器 | 名稱 / 用途 | 說明 |

|---|---|---|

| R0 | 通用寄存器 | 用于臨時數據存儲,支持所有數據操作指令 |

| R1 | 通用寄存器 | 同上 |

| ... | ... | (R2-R12 功能相同,均為通用寄存器,無特殊用途) |

| R12 | 通用寄存器(IP) | 通常用作函數調用的中間結果寄存器(Intra-Procedure Call Register) |

| R13 | 棧指針(SP) | 分為?MSP(主棧指針,默認用于操作系統和異常處理)和?PSP(進程棧指針,用于用戶任務),由?CONTROL?寄存器選擇當前使用的 SP |

| R14 | 鏈接寄存器(LR) | 存儲函數調用的返回地址,函數返回時通過?BX LR?指令跳轉回調用處 |

| R15 | 程序計數器(PC) | 存儲下一條要執行的指令地址,自動遞增(Thumb 指令集下每次 + 2,32 位指令下 + 4) |

特殊功能寄存器

特殊功能寄存器用于 Cortex-M3 的核心核心控制和狀態,只能通過特定指令(如?MRS/MSR)訪問,主要包括:

| 寄存器 | 名稱 | 功能說明 |

|---|---|---|

| xPSR | 程序狀態寄存器組合 | 由三個子寄存器組成: 1.? APSR(應用程序狀態寄存器):存儲條件標志位(N/Z/C/V)、Q 標志(DSP 相關)、GE位(大于等于標志)2.? IPSR(中斷程序狀態寄存器):存儲當前活躍的異常編號(0-255,0 表示無異常)3.? EPSR(執行程序狀態寄存器):存儲 Thumb 狀態位(T 位,Cortex-M3 始終為 1,因僅支持 Thumb-2 指令集) |

| PRIMASK | 主屏蔽寄存器 | 1 位寄存器,置 1 時屏蔽所有可屏蔽中斷(僅 NMI 和硬 fault 可響應) |

| FAULTMASK | fault 屏蔽寄存器 | 1 位寄存器,置 1 時屏蔽所有異常(僅 NMI 可響應),優先級高于 PRIMASK |

| BASEPRI | 基礎優先級寄存器 | 8 位寄存器,屏蔽優先級低于設定值的中斷(僅響應更高優先級的中斷) |

| CONTROL | 控制寄存器 | 2 位寄存器: - bit0:選擇棧指針(0=MSP,1=PSP) - bit1:選擇特權級(0 = 特權級,1 = 用戶級) |

Cortex-M3 的寄存器組設計兼顧了高效性和實時性:

- 通用寄存器(R0-R15)滿足日常數據處理需求,特殊用途寄存器(SP/LR/PC)簡化了函數調用和棧管理;

- 特殊功能寄存器(xPSR、PRIMASK 等)提供了對中斷、特權級和異常的精細控制,適配嵌入式實時系統的嚴苛要求。

12.保存、恢復現場的詳細操作

保存和恢復現場的本質是“狀態的完整備份與還原”,核心流程為:

- 保存:中斷 / 切換發生時,將寄存器、狀態等壓入棧或專用存儲區(硬件 + 軟件協同);

- 處理:執行中斷服務程序或切換到目標任務;

- 恢復:按相反順序從存儲區彈出狀態,回到中斷前的執行點。

對ARM Cortex-M3\M4具體而言:

“現場”:指程序執行到某一時刻的全部運行狀態,包括:

- CPU 通用寄存器的值(如 R0-R15);

- 程序狀態寄存器(如 xPSR,記錄標志位、中斷狀態等);

- 棧指針(SP)、程序計數器(PC)等專用寄存器;

- (部分場景)內存中臨時變量、外設狀態等。

保存現場:在程序被中斷(如中斷請求、任務切換)時,將當前 “現場” 完整存儲到安全區域(通常是棧或專用存儲區),防止狀態丟失。

恢復現場:當中斷處理完成或任務重新調度時,將保存的 “現場” 從存儲區讀回寄存器,使程序恢復到中斷前的狀態繼續執行。

13.ARM Cortex-M3和M4的區別

| 特性 | Cortex-M3 | Cortex-M4 |

|---|---|---|

| 核心定位 | 通用嵌入式處理器,側重控制類應用 | 增強型處理器,支持控制 + 信號處理 |

| 核心功能 | 基礎控制能力,無硬件 DSP 和浮點單元 | 集成硬件 DSP 指令和可選 FPU(浮點運算),支持硬件浮點運算 |

| 典型應用場景 | 工業控制、智能家居、低端嵌入式設備 | 電機控制、音頻處理、傳感器融合、物聯網網關等需要信號處理的場景 |

- 若僅需基礎控制功能(如 GPIO 控制、簡單通信協議),對成本和功耗敏感 → 選 Cortex-M3(如 STM32F1 系列);

- 若需信號處理(如音頻濾波、電機矢量控制)或浮點運算(如傳感器融合算法) → 選 Cortex-M4(如 STM32F4 系列、TI Tiva C 系列)。

Cortex-M4 完全兼容 Cortex-M3 的軟件生態,是 Cortex-M3 的 “增強版”。

14.異常和中斷

-

中斷(外部事件):

由CPU 外部設備(如定時器、按鍵、傳感器、串口)主動觸發的請求,目的是通知 CPU “外部有事件需要處理”(如按鍵被按下、數據接收完成)。

本質是 “外部異步事件”,與 CPU 執行的指令流無關,隨時可能發生。 -

異常(內部錯誤):

由CPU 內部事件觸發(如程序執行錯誤、調試請求),是 CPU 在執行指令過程中 “自身遇到的特殊情況”(如除以零、訪問無效內存、執行斷點指令)。

本質是 “內部同步事件”,與當前執行的指令直接相關,通常在特定指令執行時發生。

| 對比維度 | 中斷(Interrupt) | 異常(Exception) |

|---|---|---|

| 觸發源 | CPU 外部設備(定時器、GPIO、UART 等) | CPU 內部(程序錯誤、調試、指令執行異常等) |

| 同步性 | 異步(與程序執行流程無關,意味著中斷隨時可能到來) | 同步(與當前執行的指令相關,確定發生,與時鐘是同步的) |

| 典型場景 | 按鍵輸入、定時器超時、串口數據到達 | 除以零、空指針訪問、斷點調試、系統調用 |

| 處理優先級 | 通常可配置優先級(支持嵌套) | 固定優先級(部分可配置,如故障異常) |

| 響應延遲 | 需快速響應(如實時控制系統要求微秒級) | 需立即處理(如內存錯誤不處理會導致崩潰) |

| ARM Cortex-M 舉例 | 外部中斷(EXTI)、定時器中斷(TIM) | 硬故障(HardFault)、內存管理故障(MemManage)、調試異常(DebugMonitor) |

15.中斷和DMA的區別

DMA是一種無須CPU的參與,就可以讓外設與系統內存之間進行雙向數據傳輸的硬件機制,使用 DMA可以使系統CPU從實際的I/O數據傳輸過程中擺脫出來,從而大大提高系統的吞吐率。

中斷:是指CPU在執行程序的過程中,出現了某些突發事件時,CPU必須暫停執行當前的程序,轉去處理突發事件,處理完畢后CPU又返回源程序被中斷的位置并繼續執行。

所以中斷和DMA的區別就是:DMA不需CPU參與,而中斷是需要CPU參與的。

16.DMA

在沒有 DMA 的系統中,外設與內存之間的數據傳輸需要 CPU 全程介入(例如:CPU 從外設寄存器讀取數據,再寫入內存),這會占用大量 CPU 時間,尤其在傳輸大數據量時(如視頻、音頻流),會導致 CPU 無法處理其他任務。

DMA 的出現解決了這一問題:它通過DMA 控制器(獨立于 CPU 的硬件模塊)直接管理外設與內存之間的數據傳輸,CPU 只需在傳輸開始前進行初始化配置,傳輸過程中可完全脫離,僅在傳輸完成或出錯時通過中斷通知 CPU。

流程:

-

初始化配置(CPU 介入)

CPU 向 DMA 控制器發送指令,設置關鍵參數:- 數據源地址(如外設的數據寄存器地址,如 UART 接收緩沖區);

- 目標地址(如內存中的數據緩沖區地址);

- 傳輸數據量(如 1024 字節);

- 傳輸方向(外設→內存、內存→外設、內存→內存);

- 傳輸模式(單次傳輸、循環傳輸等)。

-

數據傳輸(DMA 獨立完成)

CPU 配置完成后,DMA 控制器接管總線(數據總線、地址總線),直接執行數據搬運:- 從數據源讀取數據,寫入目標地址;

- 自動更新源地址、目標地址和剩余傳輸量;

- 傳輸過程中,CPU 可執行其他任務(如運算、響應中斷等),無需參與。

-

傳輸結束(通知 CPU)

當數據傳輸完成或發生錯誤時,DMA 控制器觸發中斷,通知 CPU:- CPU 響應中斷,處理后續工作(如校驗數據、啟動下一次傳輸);

- 整個過程中,CPU 僅在初始化和結束階段參與,中間傳輸完全由 DMA 完成。

優勢:

-

提高系統效率

大數據量傳輸時(如攝像頭采集圖像、SD 卡讀寫),DMA 避免了 CPU 頻繁搬運數據的開銷,讓 CPU 專注于更復雜的任務(如算法處理、邏輯決策)。 -

降低 CPU 負載

無需 CPU 參與數據傳輸,減少了 CPU 的占用時間,尤其適合嵌入式系統、實時系統等資源有限的場景。 -

提升傳輸速度

DMA 控制器直接操作總線,傳輸速度僅受總線帶寬限制,比 CPU 通過指令搬運數據更快(尤其在高頻傳輸場景)。

典型應用場景

- 外設數據采集:ADC(模數轉換器)連續采樣傳感器數據,通過 DMA 直接寫入內存,CPU 無需每次采樣都介入;

- 通信數據傳輸:UART、SPI、I2C 等接口接收 / 發送大數據包時,用 DMA 自動完成,避免 CPU 被頻繁中斷;

- 存儲設備讀寫:硬盤、SD 卡、Flash 等存儲設備與內存之間的文件傳輸(如計算機中的硬盤 DMA 模式);

- 音頻 / 視頻處理:音頻 Codec、攝像頭模塊與內存之間的實時數據流傳輸,保證數據連續性。

17.中斷響應執行流程

中斷響應執行流程是指 CPU 從檢測到中斷請求到完成中斷處理并返回原程序的完整過程,這一流程需要硬件與軟件協同工作,確保中斷能被快速響應且程序能正確恢復執行。

中斷響應流程可概括為:

外設請求(中斷觸發) → 優先級仲裁(控制器比較當前請求的優先級與正在處理的中斷優先級) → 硬件保存現場(自動保存關鍵寄存器到棧中) → 跳轉ISR(CPU 從中斷向量表中找到當前中斷對應的服務程序地址) → 軟件處理(執行中斷服務程序并清除中斷標志) → 恢復現場(從棧中彈出之前自動保存的寄存器) → 返回原程序

18.中斷和輪詢哪個效率高?怎樣決定是采用中斷方式還是采用輪詢方式去實現驅動?

中斷是CPU處于被動狀態下來接受設備的信號,而輪詢是CPU主動去查詢該設備是否有請求。

凡事都是兩面性,所以,看效率不能簡單的說那個效率高。如果是請求設備是一個頻繁請求cpu的設備,或者有大量數據請求的網絡設備,那么輪詢的效率是比中斷高。如果是一般設備,并且該設備請求 cpu的頻率比較低,則用中斷效率要高一些。主要是看請求頻率。

19.什么是輪詢?

輪詢是計算機系統中CPU 主動查詢外設狀態以處理事件的一種基礎機制,核心邏輯是 “CPU 周期性詢問、外設被動響應”,無需外設主動向 CPU 發送信號。

具體如下:

- 發起查詢:CPU 按固定周期(如每 10ms)主動訪問外設的 “狀態寄存器”,讀取外設當前狀態(例如 “是否有數據待讀取”“操作是否完成”“是否發生錯誤”)。

- 狀態判斷:CPU 對比讀取到的狀態值與預設的 “事件觸發條件”(如 “狀態寄存器第 0 位為 1 表示有數據”):

- 若未滿足觸發條件(如無數據):CPU 不處理該外設,繼續執行其他任務(或進入下一次查詢循環);

- 若滿足觸發條件(如有數據):CPU 執行對應的處理邏輯(如讀取數據、發送控制指令)。

- 循環重復:處理完成后,CPU 回到 “查詢” 步驟,繼續周期性詢問外設狀態,直到系統停止或外設斷開。

在事件頻繁規律、硬件資源有限的場景下,是比中斷更合適的解決方案。在實際系統中,也常出現 “中斷 + 輪詢” 的混合策略(如中斷通知 “有事件”,輪詢批量處理數據),以平衡效率與資源消耗。

20.狀態機

系統在任一時刻僅處于一個確定的狀態,當外部事件(輸入)觸發時,會按照預設規則從當前狀態 “跳轉” 到另一個狀態,并可能執行對應狀態的動作。

任何狀態機都由 4 個基本部分構成,缺少任一要素都無法形成完整的邏輯閉環:

-

狀態(State)

系統在某一時刻的行為模式或運行狀態,分為兩種關鍵類型:- 初始狀態(Initial State):系統啟動時的默認狀態(僅 1 個)。

- 常規狀態 / 終止狀態:常規狀態是系統運行中的中間狀態(如 “設備待機”“數據傳輸中”);終止狀態是系統邏輯結束的狀態(可選,如 “任務完成”)。

-

事件(Event)

觸發狀態切換的外部輸入或內部條件,是狀態變化的 “驅動力”。

示例:按鍵按下(外部事件)、定時器超時(內部事件)、數據接收完成(硬件事件)。 -

轉移(Transition)

系統從 “當前狀態” 在某個 “事件” 觸發下,切換到 “目標狀態” 的規則。

注意:轉移是有條件的—— 同一事件在不同當前狀態下,可能觸發不同轉移(如 “按鍵按下” 在 “待機狀態” 下觸發 “啟動”,在 “運行狀態” 下觸發 “暫停”)。 -

動作(Action)

狀態切換時或狀態存續期間執行的具體操作。

分為兩種場景:- 進入動作:進入某個狀態時執行(如進入 “數據傳輸狀態” 時,初始化串口)。

- 離開動作:離開某個狀態時執行(如離開 “數據傳輸狀態” 時,關閉串口)。

優點:

- 邏輯清晰,易維護:將復雜流程拆分為 “狀態 - 事件 - 轉移”,避免

if-else嵌套,新邏輯只需新增狀態 / 表項,無需修改原有代碼。 - 行為可預測:任一時刻狀態唯一,給定事件后轉移結果確定,調試時可快速定位 “狀態異常” 問題。

- 資源占用低:裸機中狀態機通常用枚舉、數組實現,無額外內存開銷,適合 MCU 等資源受限場景。

- 復用性強:同一狀態機邏輯(如按鍵處理、協議解析)可移植到不同項目,只需調整 “動作函數”。

21.當一個異常出現以后,ARM微處理器會執行哪幾步操作?

- 將下一條指令的地址存入相應鏈接寄存器LR,以便程序在處理異常返回時能從正確的位置重新開始執行。若異常是從ARM狀態進入,則LR寄存器中保存的是下一條指令的地址(當前PC+4或PC+ 8,與異常的類型有關);若異常是從Thumb狀態進入,則在LR寄存器中保存當前PC的偏移量,這樣,異常處理程序就不需要確定異常是從何種狀態進入的。例如:在軟件中斷異常SWI,指令MOV PC,R14_svc總是返回到下一條指令,不管SWI是在ARM狀態執行,還是在Thumb狀態執行。

- 將CPSR復制到相應的SPSR中。

- 根據異常類型,強制設置CPSR的運行模式位。

- 強制PC從相關的異常向量地址取下一條指令執行,從而跳轉到相應的異常處理程序處

注意:

CPSR: 程序狀態寄存器(當前程序狀態寄存器),在任何處理器模式下被訪問

SPSR:程序狀態保存寄存器(saved programstatus register),每一種處理器模式下都有一個狀態寄存器SPSR,SPSR用于保存CPSR的狀態,以便異常返回后恢復異常發生時的工作狀態

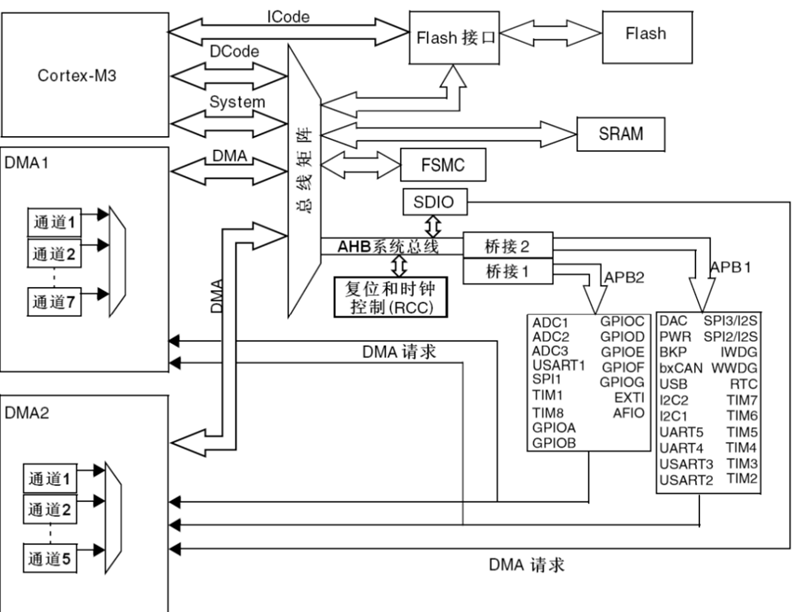

22.ARM內核架構

1. ICode總線:ICode 中的 I 表示 Instruction,即指令。我們寫好的程序編譯之后都是一條條指令,存放在 FLASH 中,內核要讀取這些指令來執行程序就必須通過 ICode 總線,它幾乎每時每刻 都需要被使用,它是專門用來取指的。

2.DCode總線:DCode 中的 D 表示 Data,即數據,那說明這條總線是用來取數的。我們在寫程序的時候,數據有常量和變量兩種,常量就是固定不變的,用 C 語言中的 const 關鍵字修飾,是放到內部的 FLASH 當中的,變量是可變的,不管是全局變量還是局部變量都放在內部的 SRAM。因為數據可以被 Dcode 總線和 DMA 總線訪問,所以為了避免訪問沖突,在取數的時候需要經過一個總線矩陣來仲裁,決定哪個總線在取數。

3.系統總線:系統總線主要是訪問外設的寄存器,我們通常說的寄存器編程,即讀寫寄存器都是通 過這根系統總線來完成的

(1)FSMC的英文全稱是 Flexible static memory controller,叫靈活的靜態的存儲器控制器, 是 STM32F10xx 中一個很有特色的外設,通過 FSMC,我們可以擴展內存,如外部的 SRAM,NANDFLASH 和 NORFLASH。

(2)內部的閃存存儲器即 FLASH,我們編寫好的程序就放在這個地方。內核通過 ICode 總 線來取里面的指令。

(3)DMA總線(Direct Memory Access)即直接存儲器訪問。主要用來傳輸數據,這個數據可以是某個外設的數據寄存存器,可以在SRAM,可以在內部的FLASH。

(4)AHB到APB的橋。AHB(Advanced High performance Bus)系統總線高級高性能總線

APB(Advance Peripheral BUS)外圍總線。

(5)看門狗模塊(watchdog timer):定期查看芯片內部的情況,一旦發生錯誤向芯片發出重啟信號。看門狗命令在程序的中斷中擁有最高的優先級。

23.STM32是大端還是小端?

小端模式。

24.SysTick

SysTick(系統滴答定時器)是 ARM Cortex-M 系列內核內置的24 位向下計數定時器,專為操作系統(如 RTOS)提供 “系統節拍”(定時中斷),也可用于普通定時、延時等場景。無需占用外部定時器資源。

- 硬件集成:屬于 Cortex-M 內核外設,所有 Cortex-M 系列 MCU(如 M0/M3/M4/M7)均標配,接口和功能統一,移植性極強。

- 計數特性:24 位遞減計數器,最大計數值為

22?-1=16,777,215,計數到 0 后自動重載(從LOAD寄存器值重新開始)。 - 時鐘源:可選擇兩種時鐘源(由內核外設

Sys_cfg配置):- 內核時鐘(HCLK)的 1/8(默認,適合低功耗);

- 內核時鐘(HCLK)本身(高頻,適合高精度定時)。

- 中斷觸發:計數到 0 時可觸發

SysTick_handler中斷,用于實現定時中斷(如 RTOS 的任務調度、延時函數)。

25.什么是哈佛結構和馮諾依曼結構?

馮諾依曼結構主要用于通用計算機領域,需要對存儲器中的代碼和數據頻繁的進行修改,統一編址有利于節約資源。

哈佛結構主要用于嵌入式計算機,程序固化在硬件中,有較高的可靠性、運算速度和較大的吞吐。

)

—— SLS 接入與設置自動化)

—— Nginx反向代理與負載均衡實戰指南)

:人工智能、機器學習與深度學習)

![[網絡入侵AI檢測] 純卷積神經網絡(CNN)模型 | CNN處理數據](http://pic.xiahunao.cn/[網絡入侵AI檢測] 純卷積神經網絡(CNN)模型 | CNN處理數據)

:用戶界面及系統管理界面布局)