26考研 | 王道 | 計算機組成原理 | 三、存儲系統

文章目錄

- 26考研 | 王道 | 計算機組成原理 | 三、存儲系統

- 3.1 存儲系統基本概念

- 3.2 主存儲器

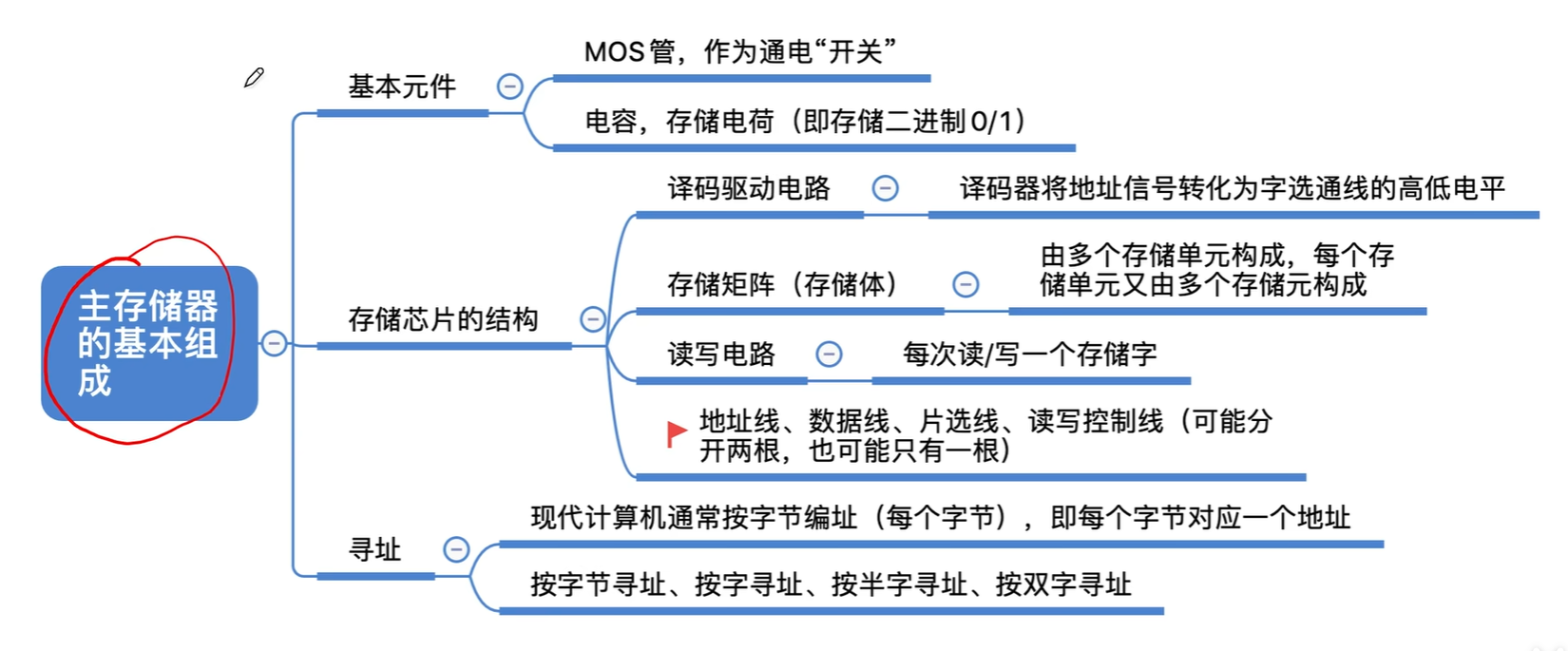

- 1. 主存儲器的基本組成

- 2. SRAM與DRAM

- 1.DRAM和SRAM對比

- 2.DRAM的刷新

- 3.DRAM的地址線復用技術

- 3. 只讀存儲器ROM

- 4.雙端口RAM和多模塊存儲器

- 3.3 主存儲器與CPU的連接

- 1.位擴展

- 2.字擴展

- 3.字位同時擴展

- 3.4 外部存儲器

- 1. 磁盤存儲器

- 磁盤陣列

- 2. 固態硬盤SSD

- 3.5 高速緩沖存儲器

- 1.基本原理

- 2.Cache和主存間的映射方式

- 3. Cache的替換算法

- 4. Cache寫策略

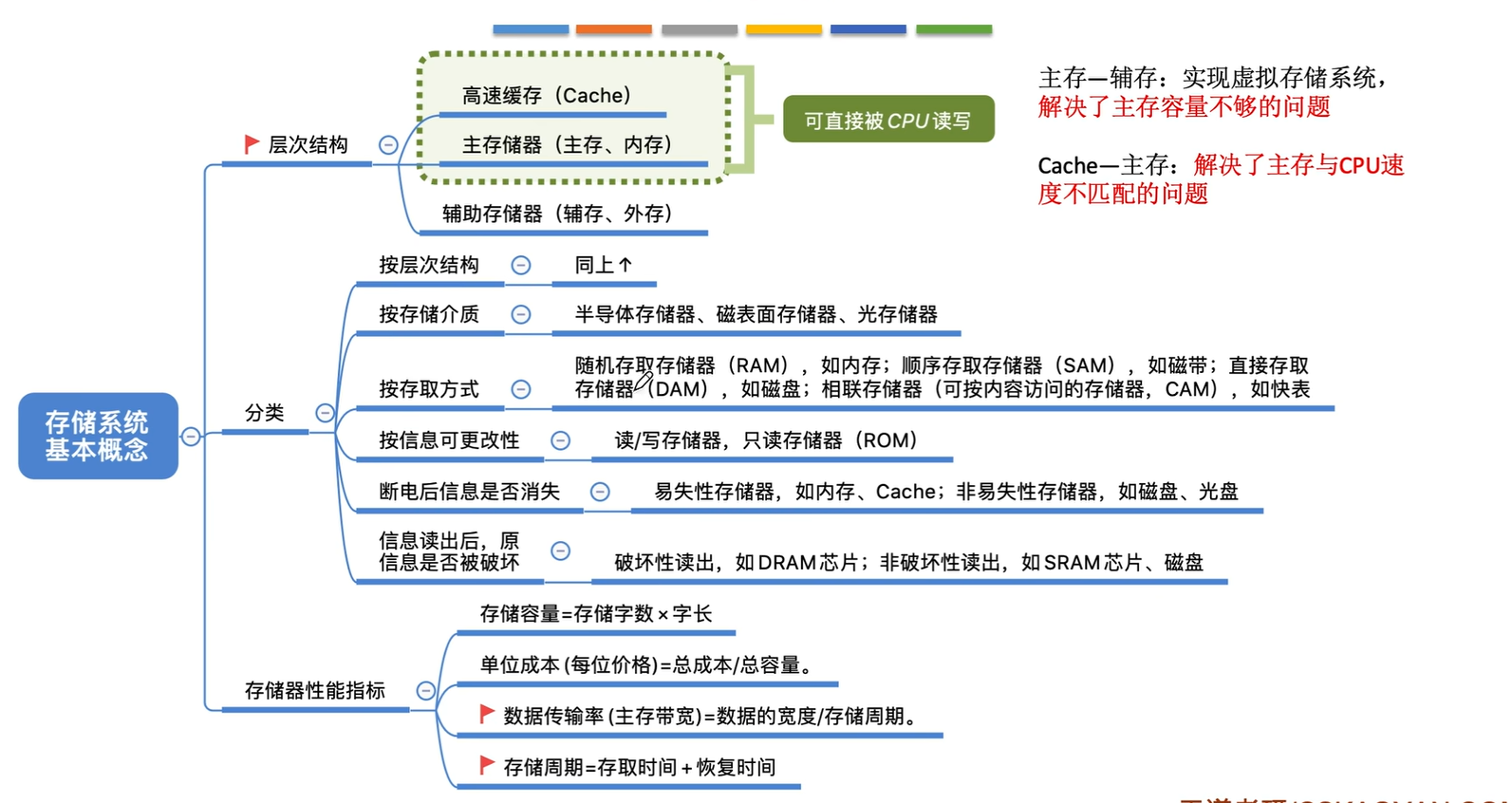

3.1 存儲系統基本概念

相聯存儲器的基本原理是指把存儲單元所存的內容的某一部分作為檢索項去檢索該存儲器,并把存儲器中與該檢索項符號的存儲單元內容進行讀出和寫入。所以是按內容或者地址進行尋址的,價格比較昂貴

一般用來制作TLB,相聯Cache等

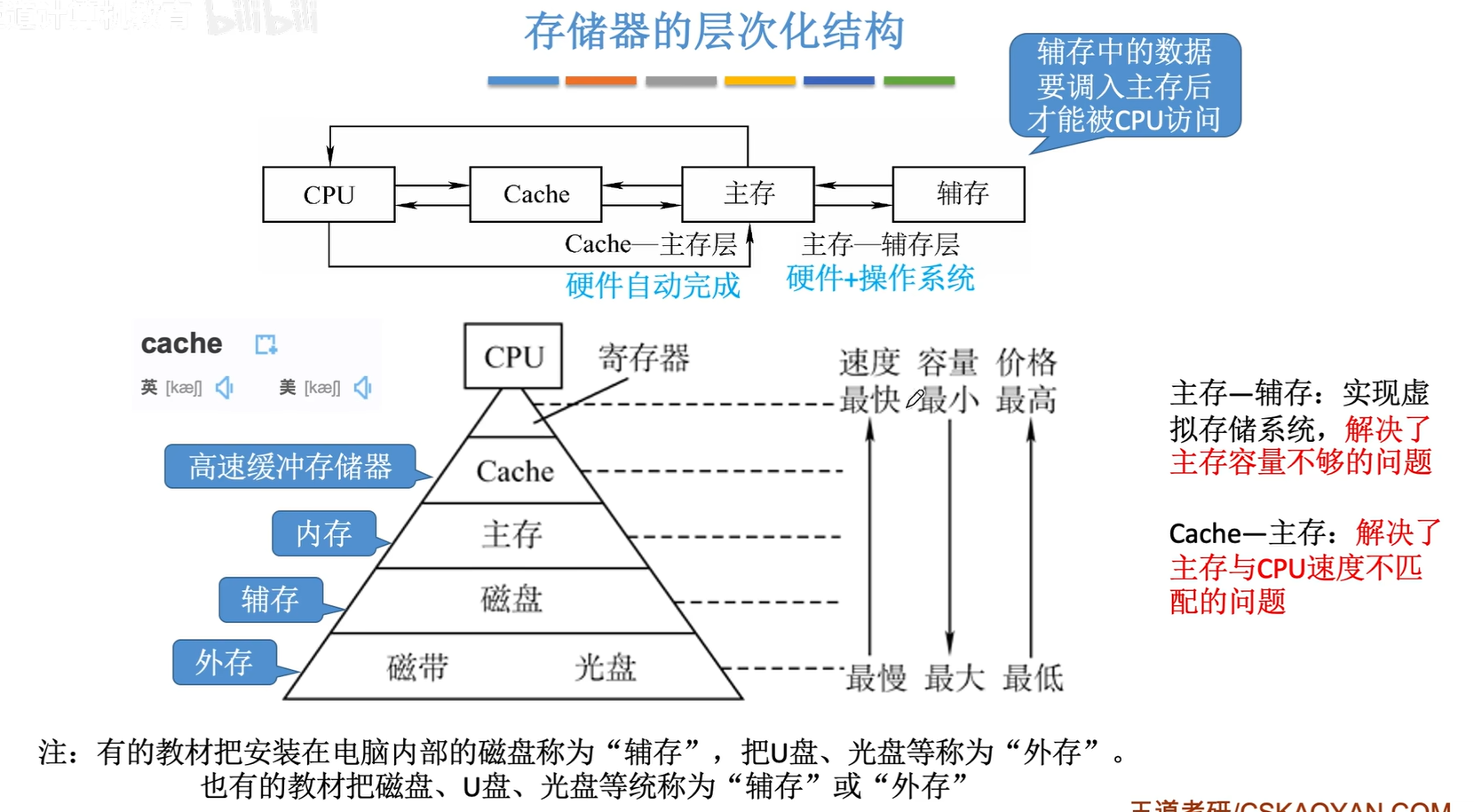

存儲器的層次化結構

主存和輔存之間的數據調動是由硬件和操作系統共同完成的,僅對應用級程序員透明

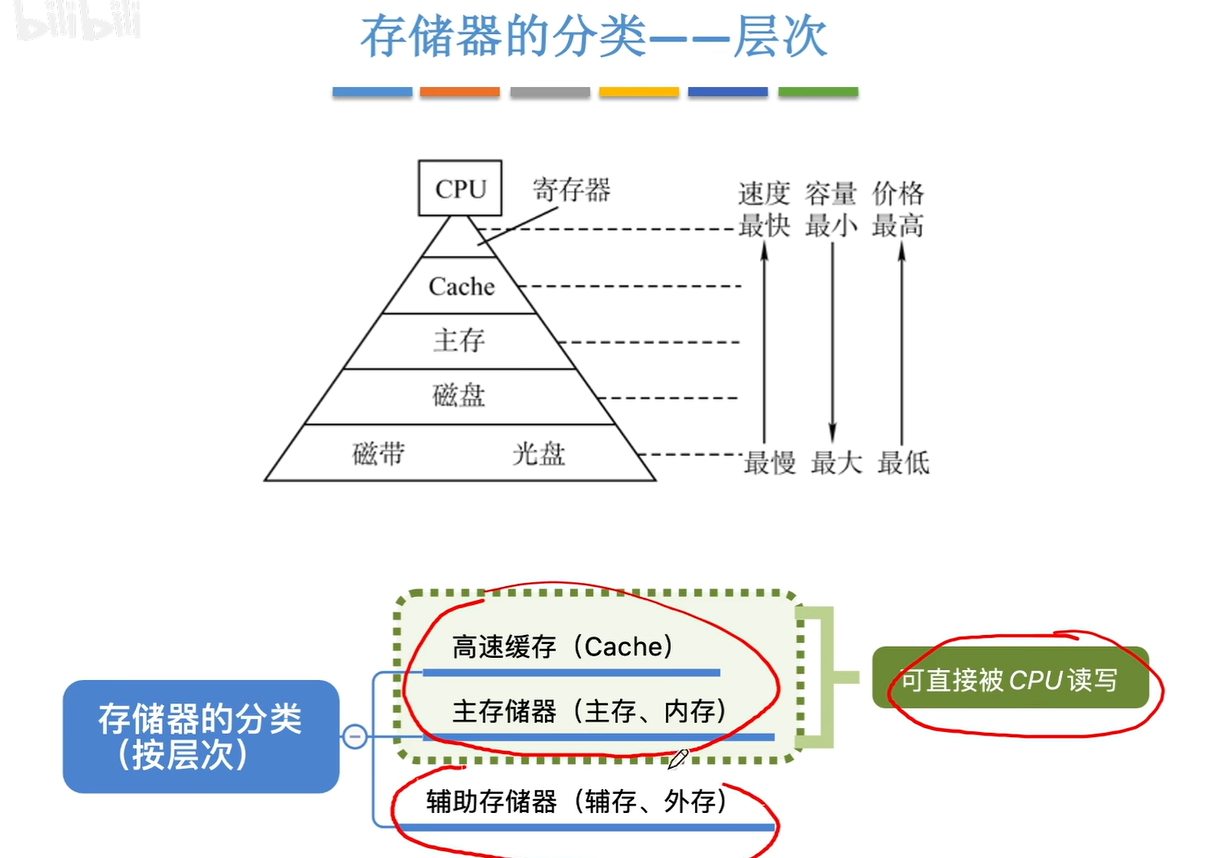

存儲器的分類–層次

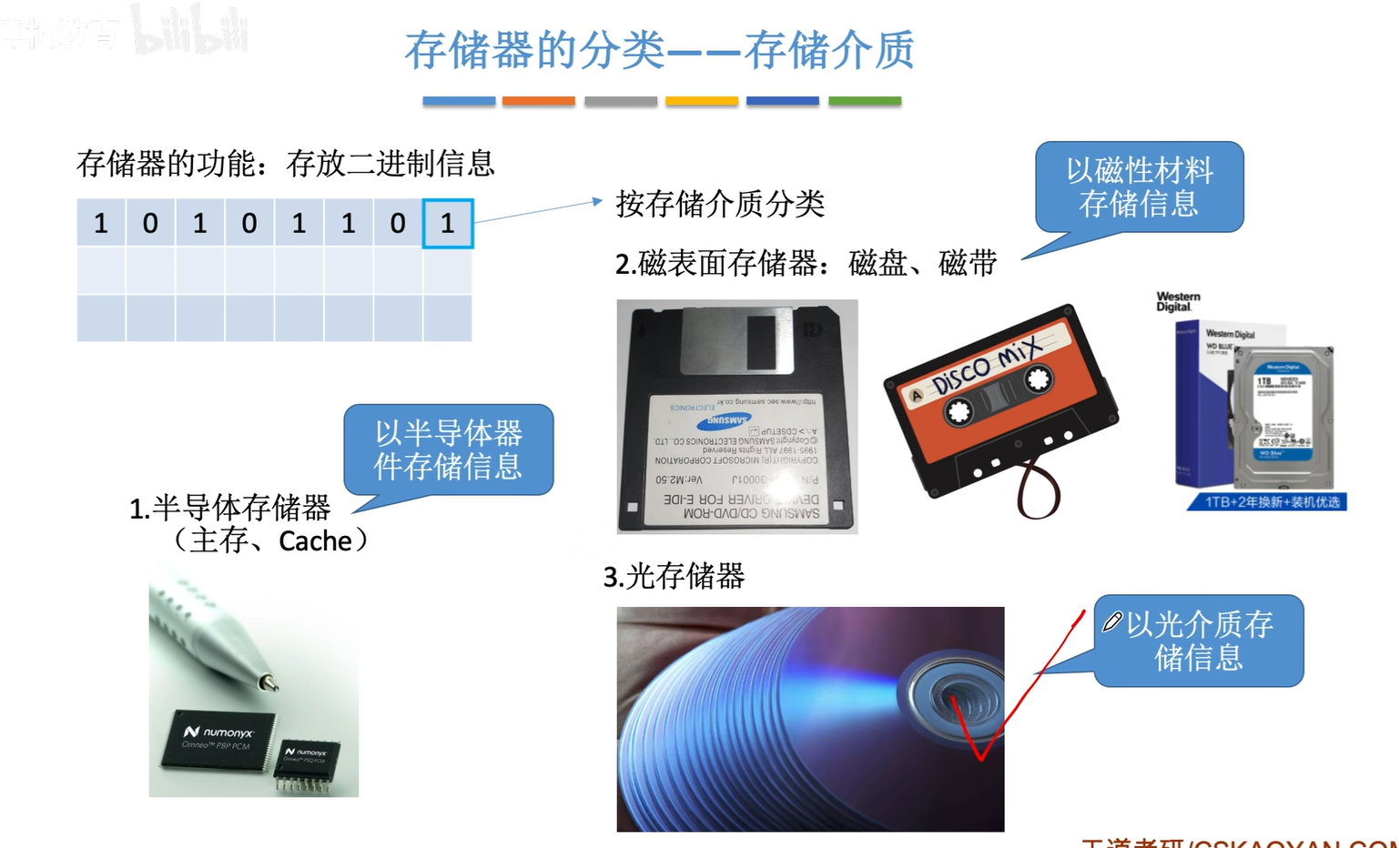

存儲器的分類–存儲介質

- 半導體存儲器:主存、Cache

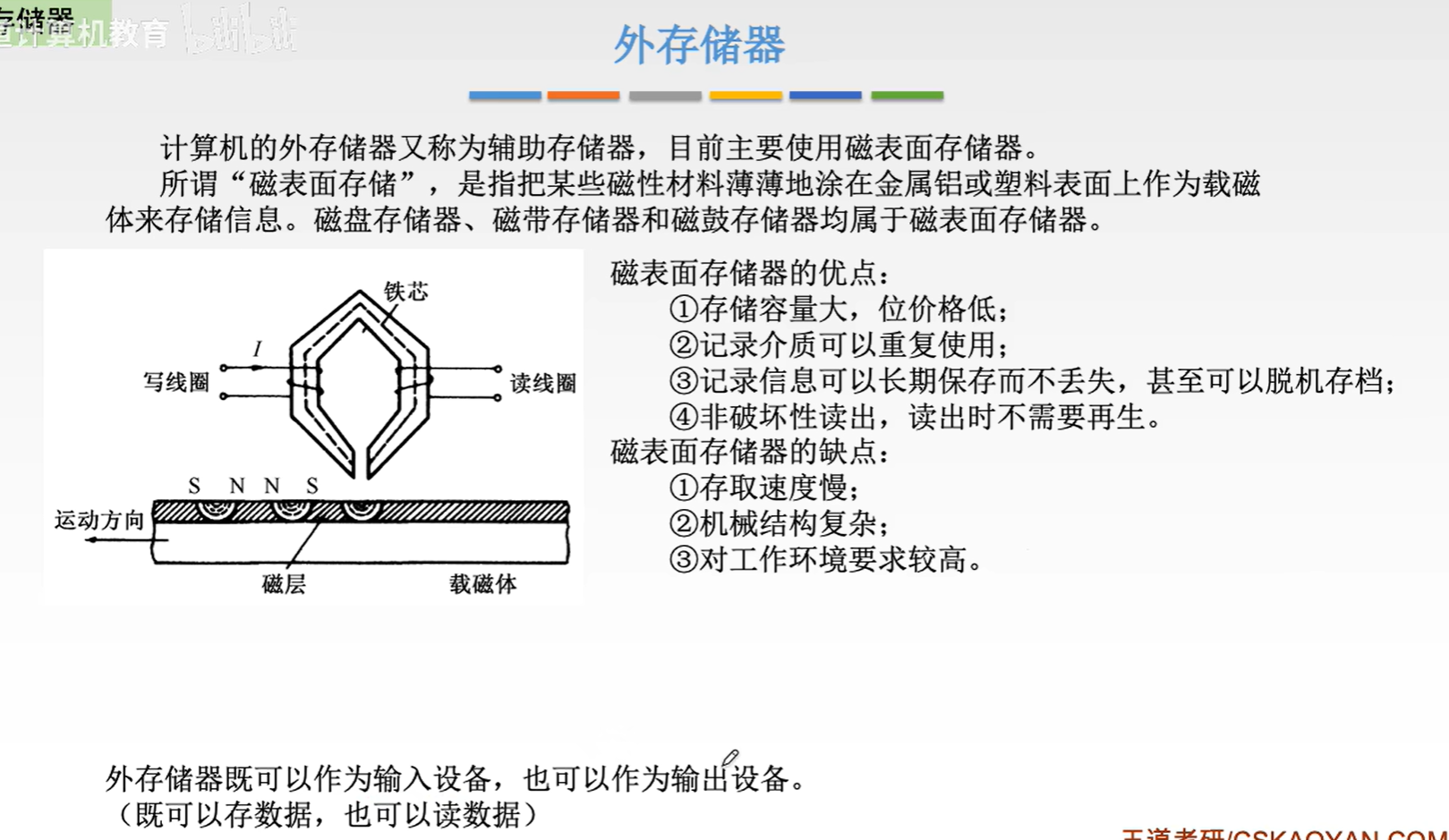

- 磁表面存儲器:磁盤、磁帶(以磁性材料存儲信息)

- 光存儲器:光盤(以光介質存儲信息)

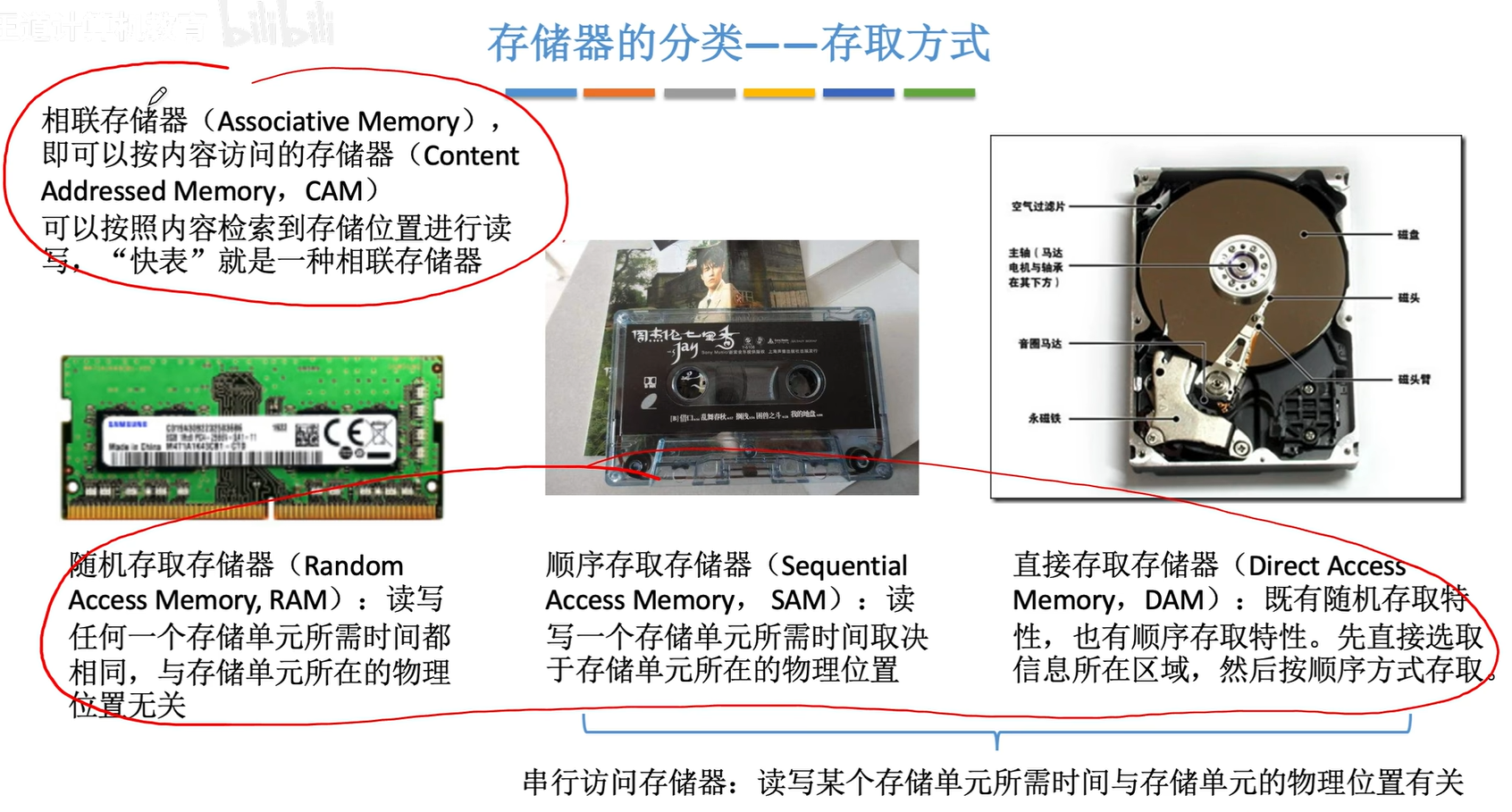

存儲器的分類–存取方式

相聯存儲器既可以按地址又可以按內容尋址。

存儲器的分類–信息的可更改性

CD-ROM是只讀型光盤存儲器,不屬于只讀存儲器ROM

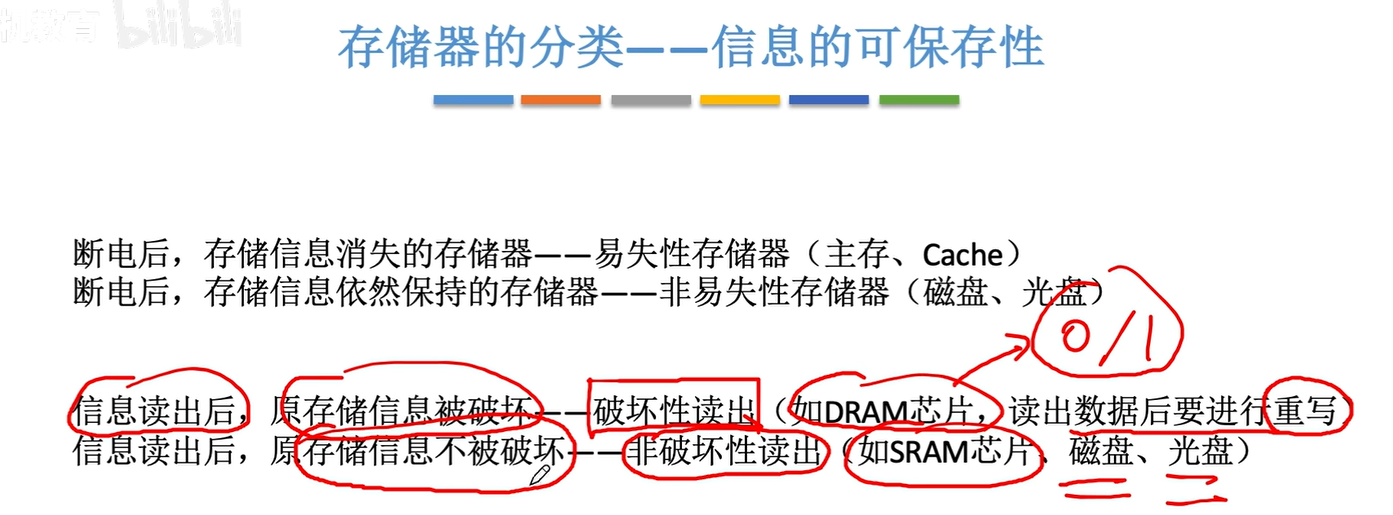

存儲器的分類–信息的可保存性

RAM都是易失性存儲器;

ROM都是非易失性存儲器;

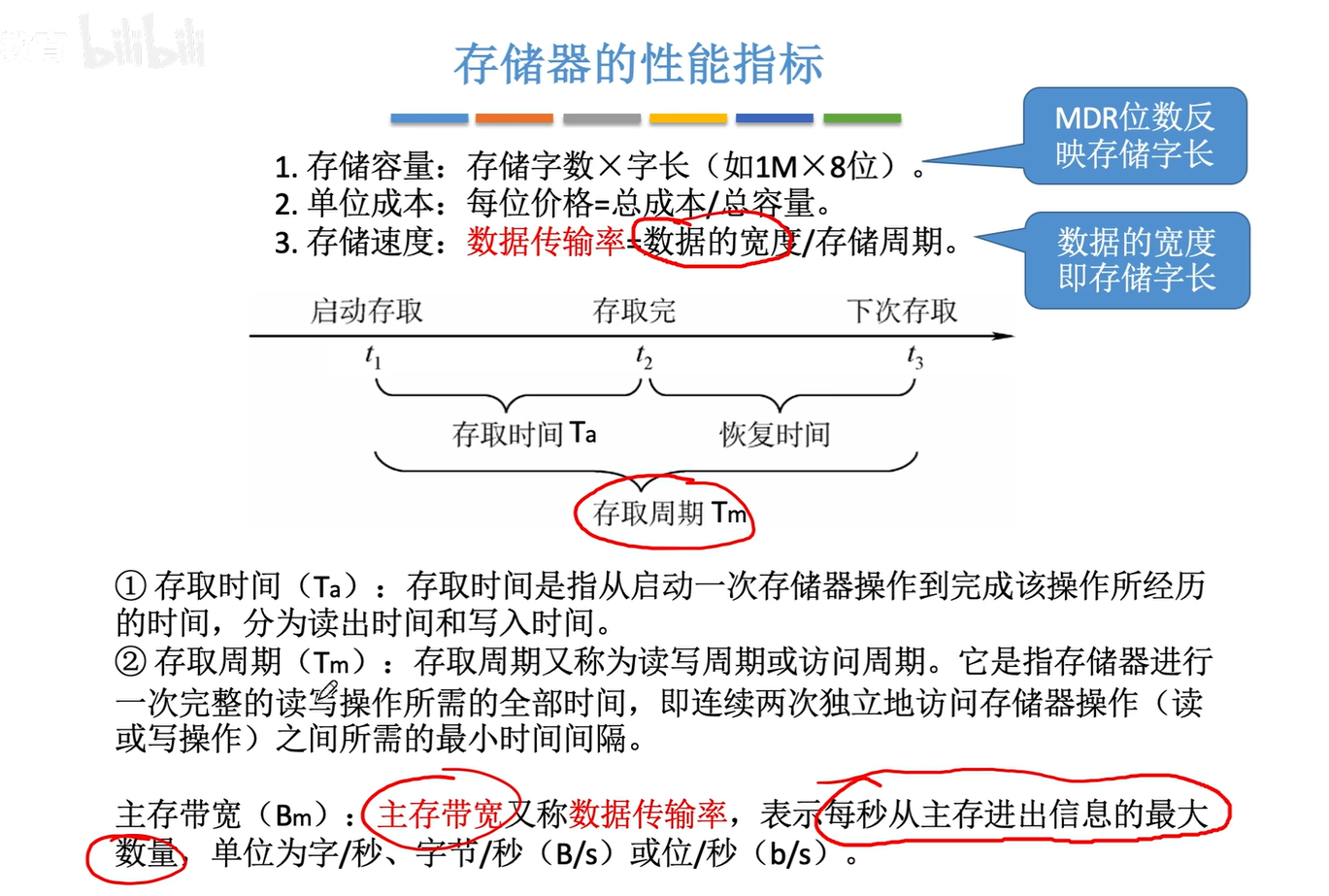

存儲器的性能指標

3.2 主存儲器

1. 主存儲器的基本組成

基本的半導體元件及原理

注:MOS管可理解為一種電控開關,輸入電壓達到某個閾值時,MOS管就可以接通。

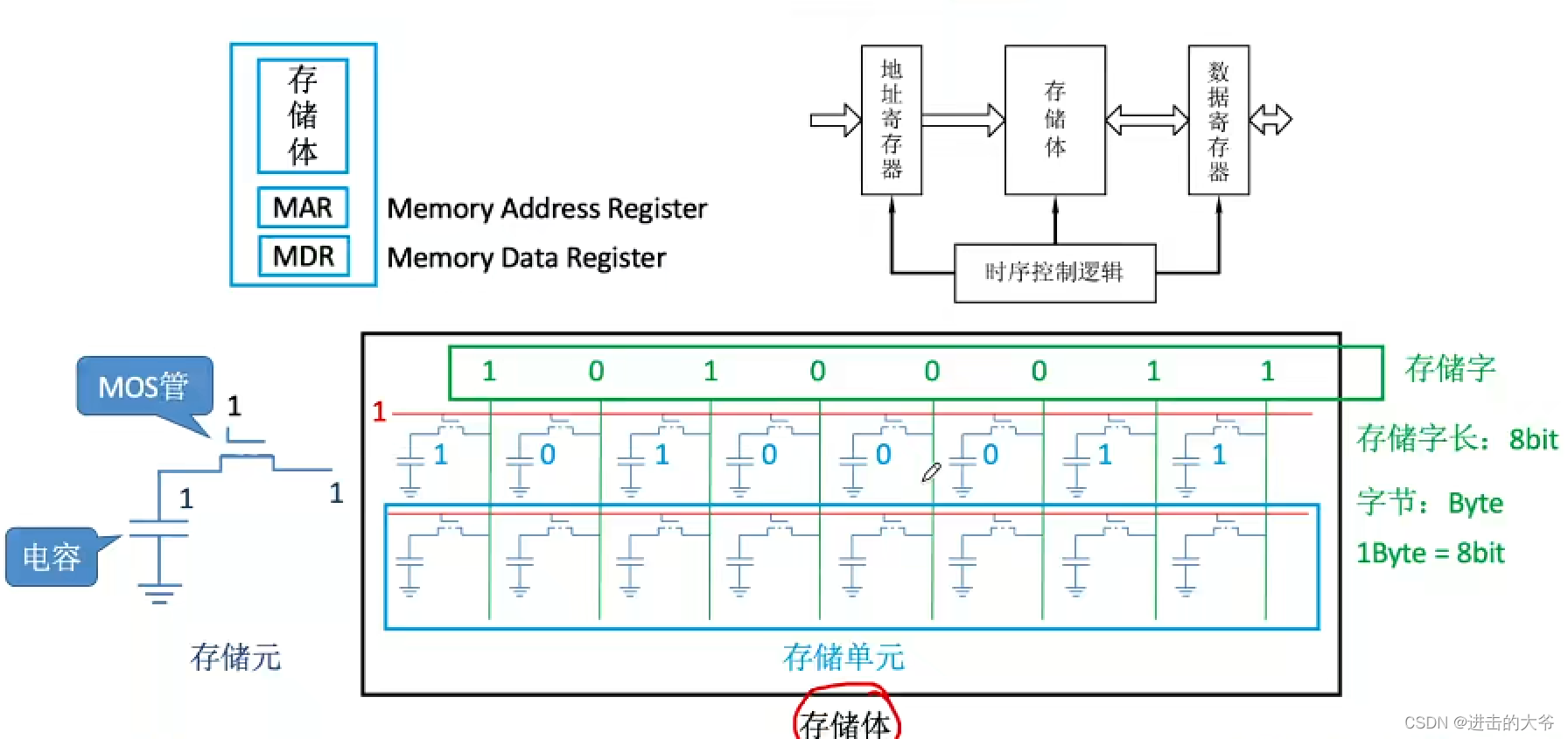

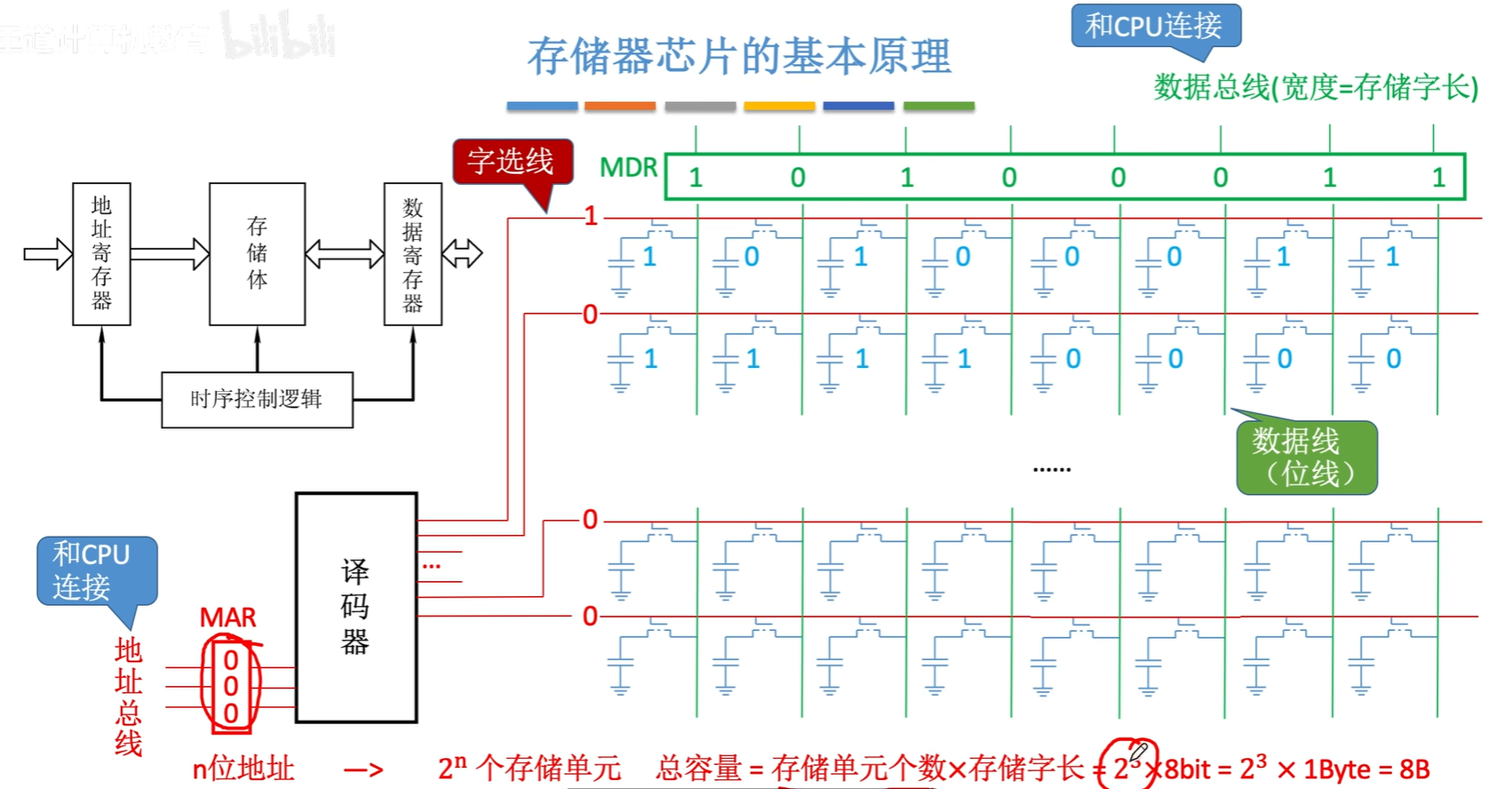

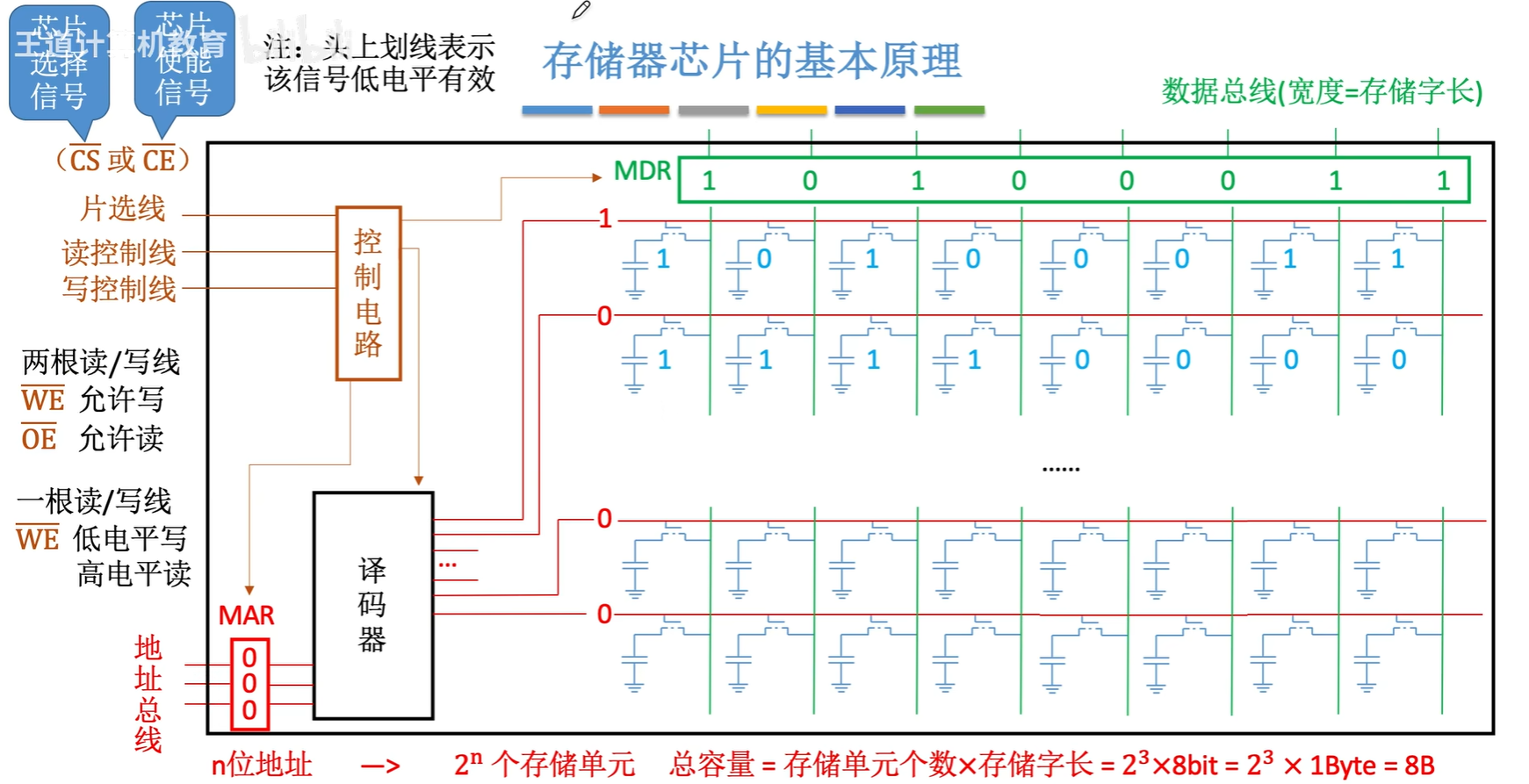

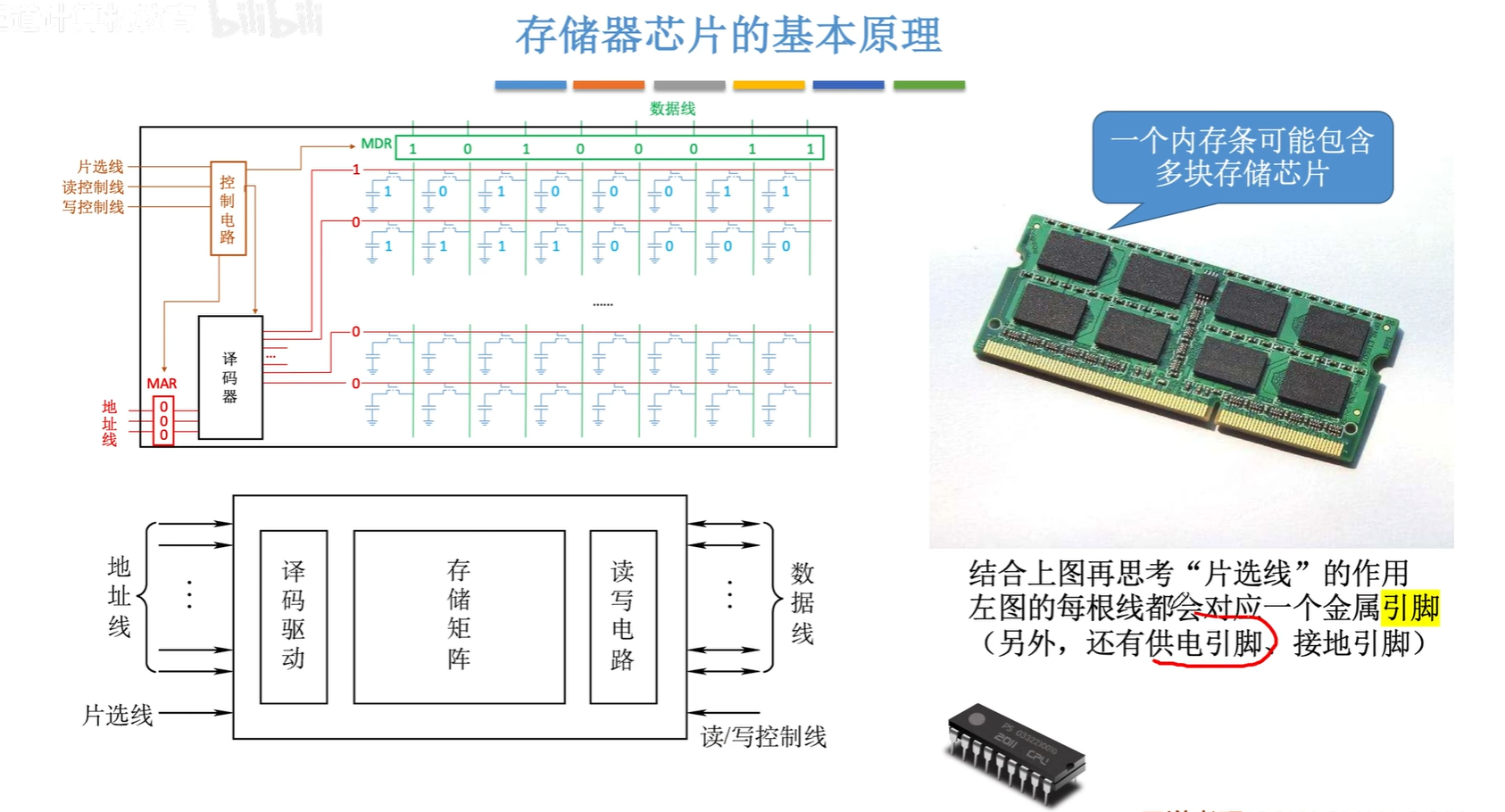

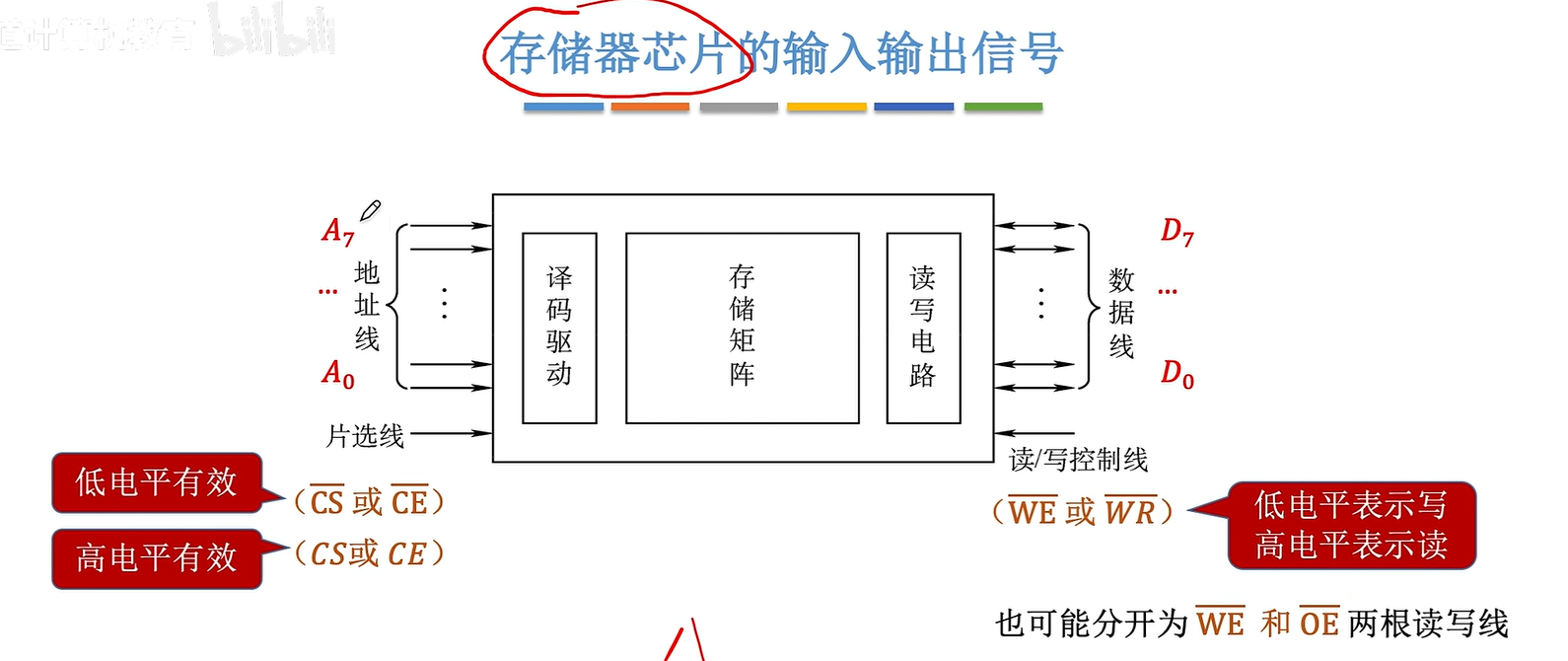

存儲器芯片的基本原理

片選線作用:一個內存條可能包含多塊存儲芯片,比如一共8塊,而我們想要的數據存在第5塊芯片里面,那么我們拿數據的時候就要讓第5塊芯片工作而其他的不工作。CS給予低電平,其他芯片為高電平。

譯碼驅動:其實就是在譯碼器和存儲矩陣中間加了一個驅動,讓譯碼器傳過來的電信號更加穩定的

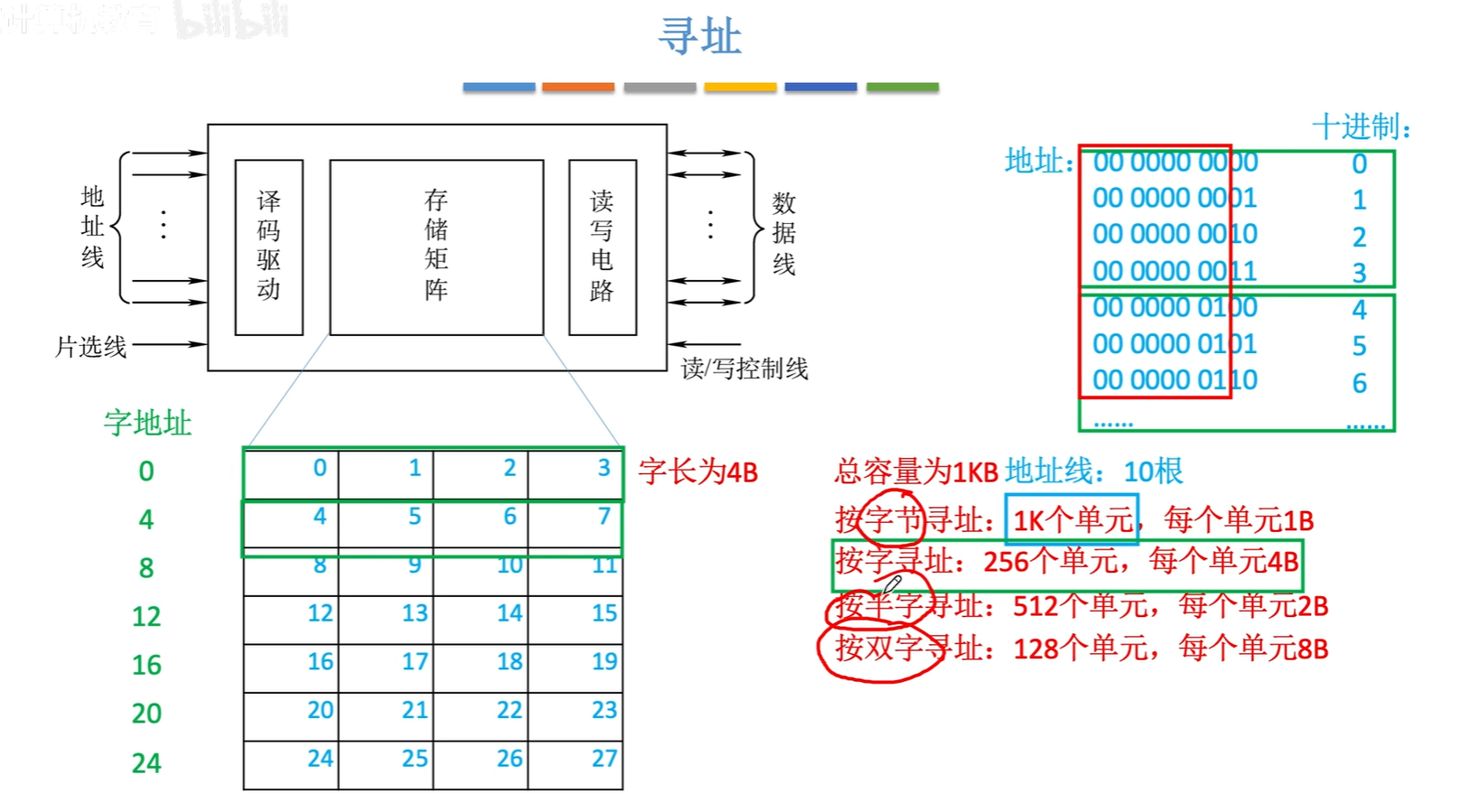

尋址

字節地址左移兩位就是對應的字的地址

比如1號字節是 1,左移兩位就是100,就是4,而按字尋址的編號2對應的就是字節尋址的編號4

2. SRAM與DRAM

SDRAM依舊是DRAM,所以依舊要刷新的

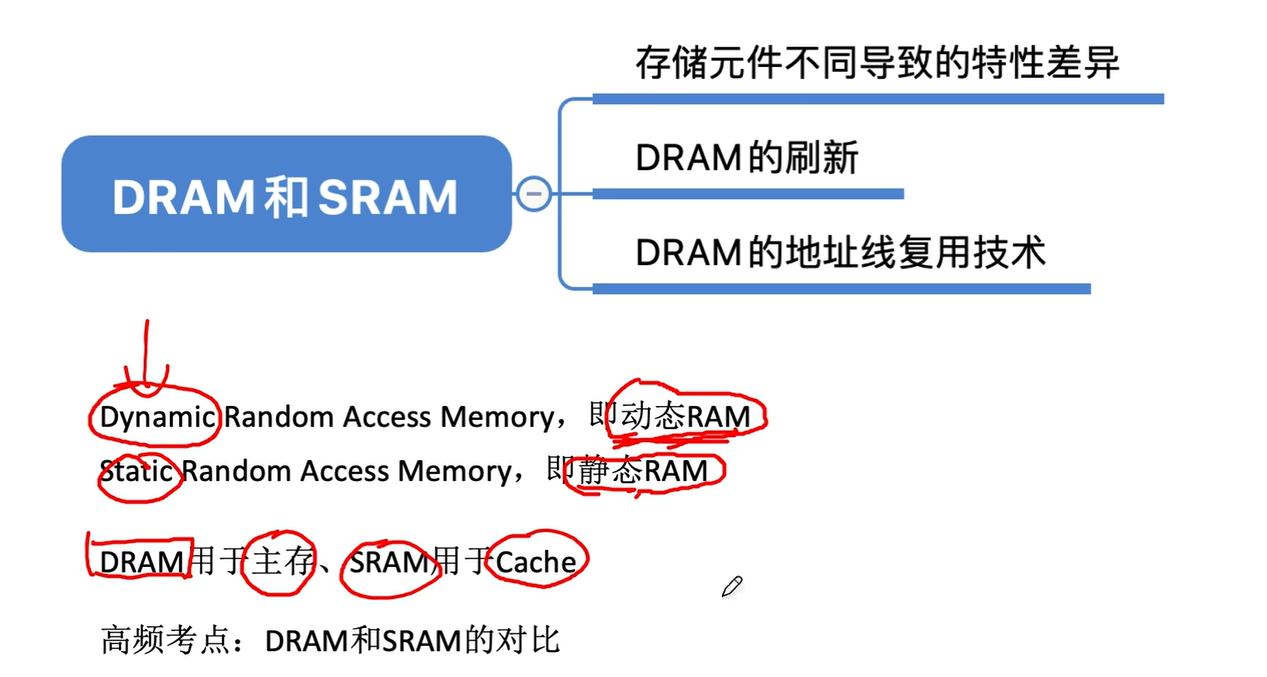

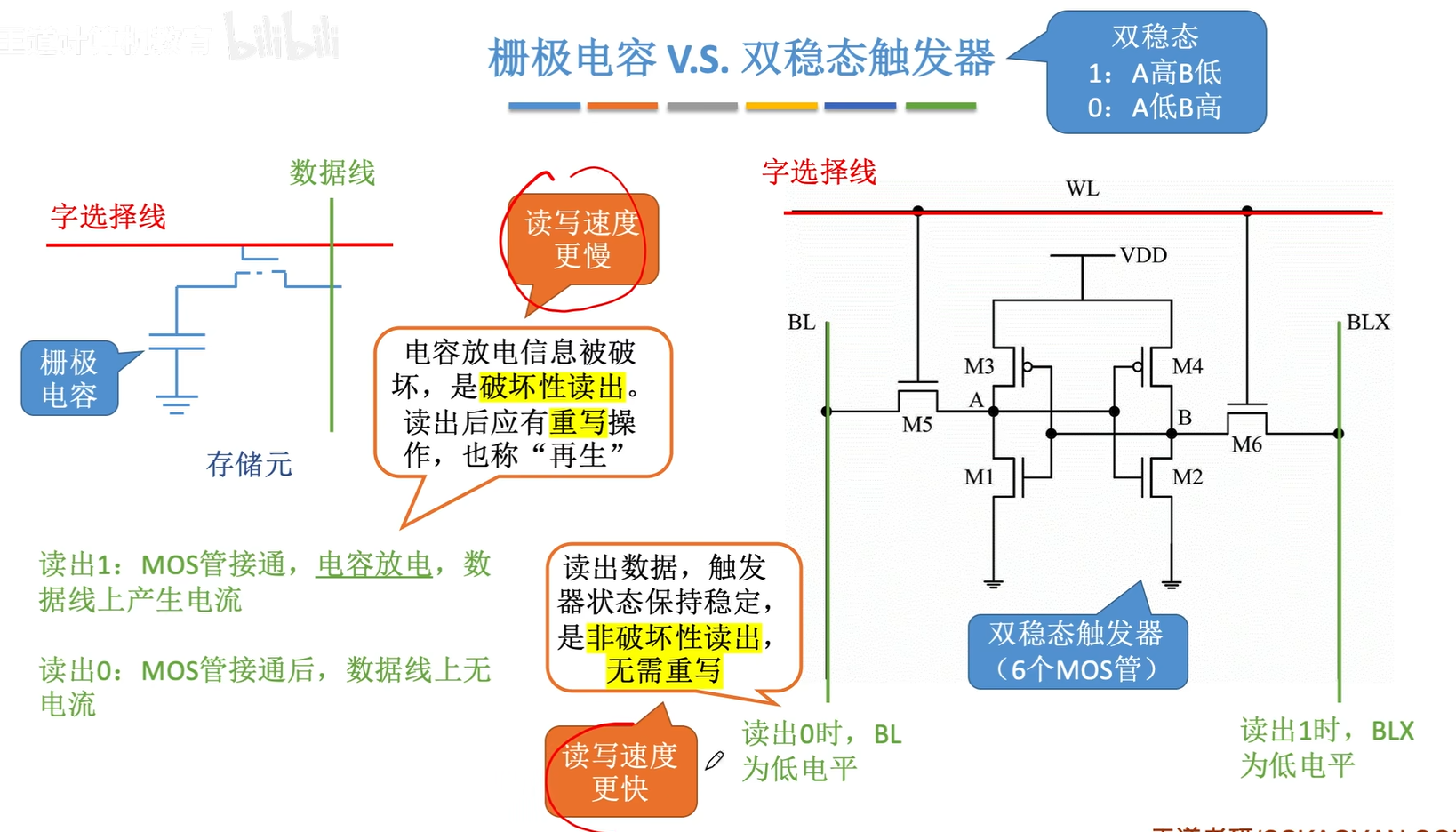

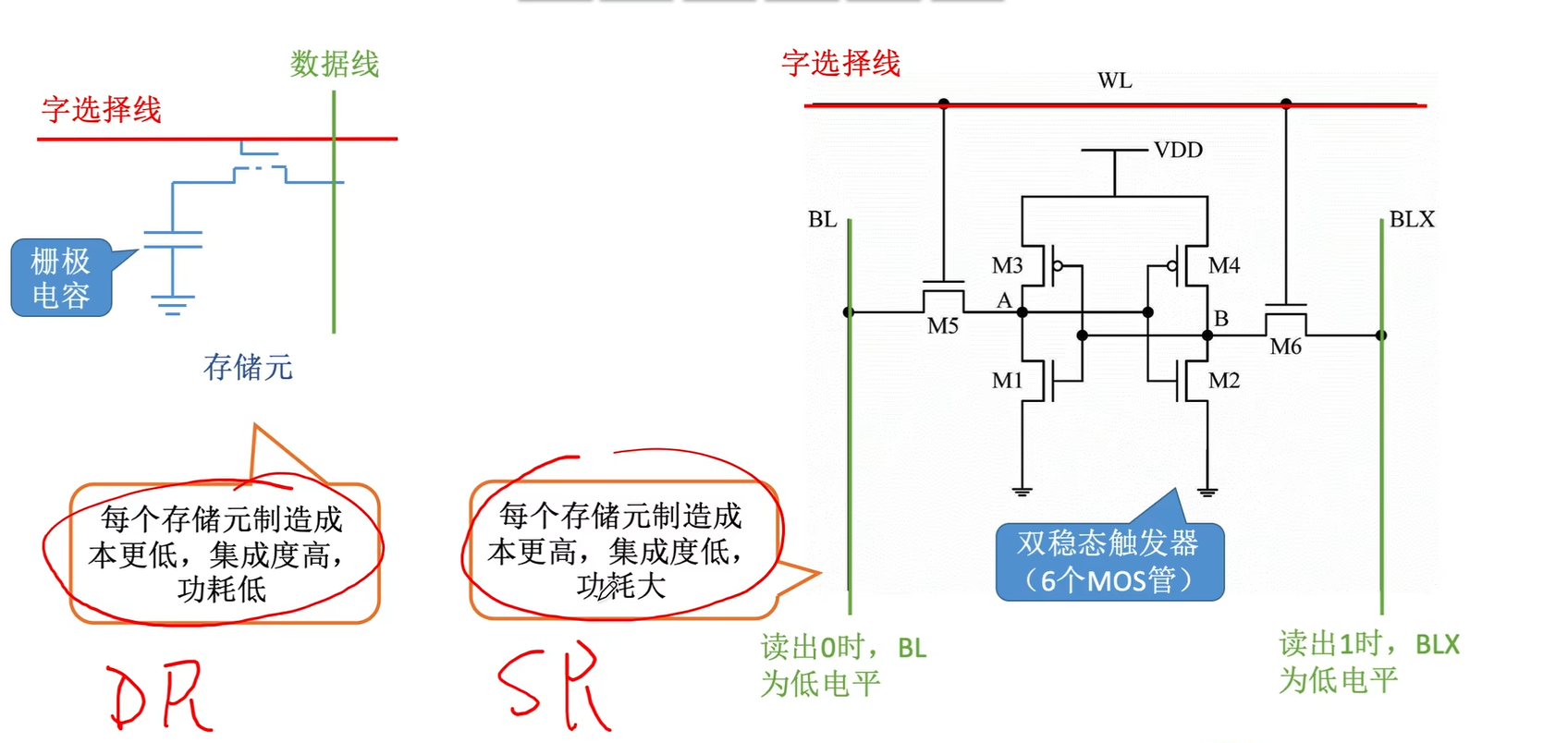

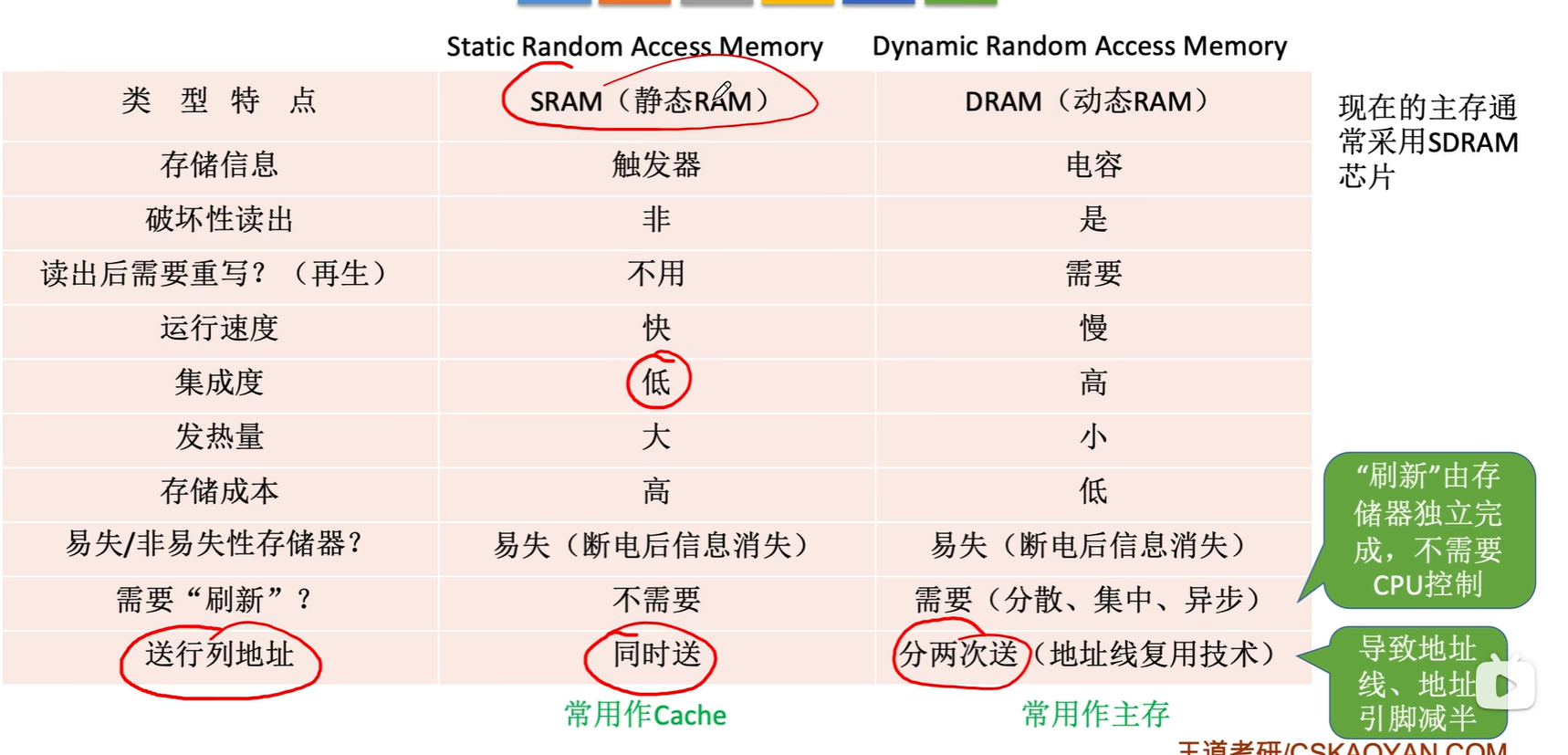

1.DRAM和SRAM對比

3.2.1 的主存儲器的基本組成部分就是那DRAM舉例子的,可以回看一下

RAM屬于易失性半導體,SRAM和DRAM區別在于是否需要動態刷新

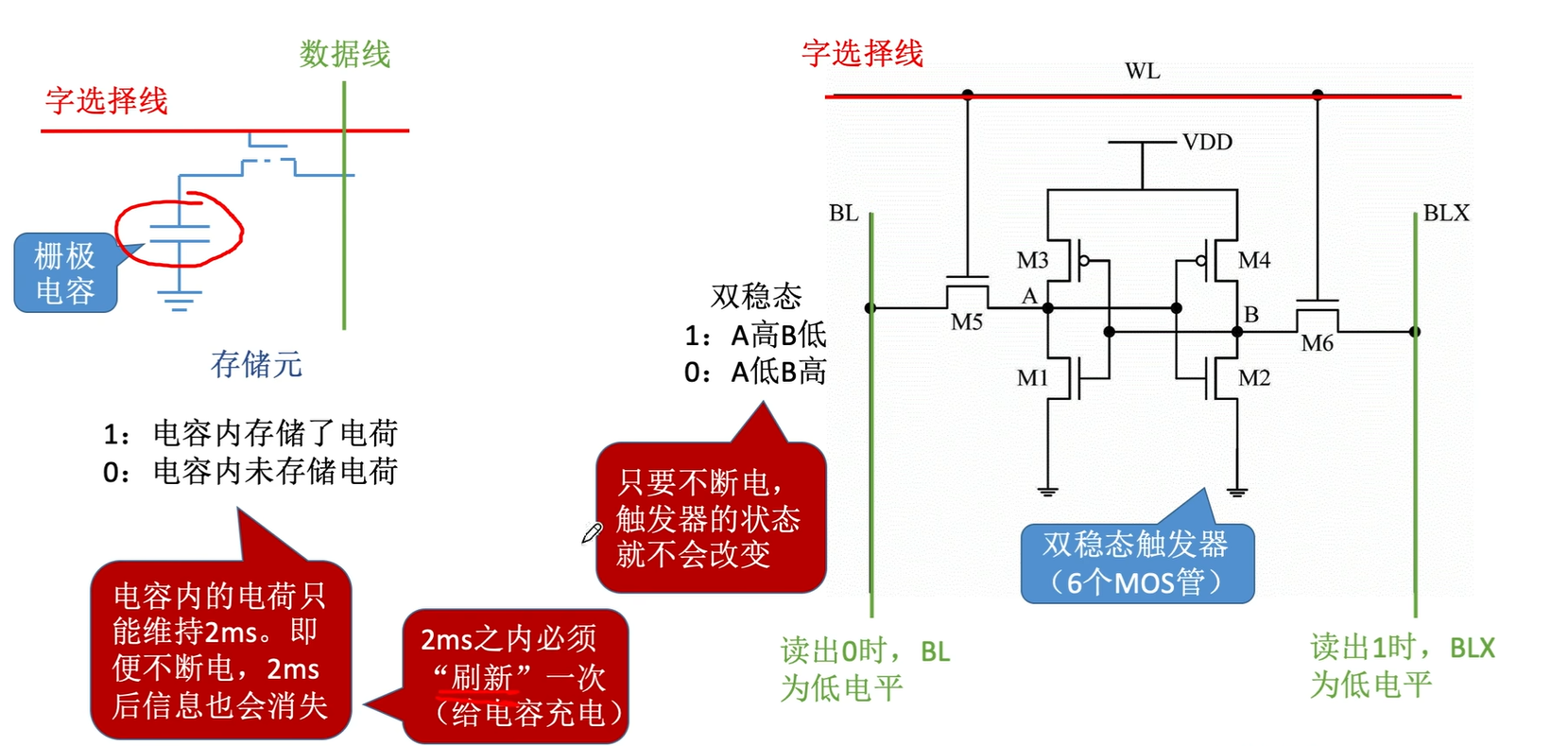

DRAM芯片:使用柵極電容存儲信息

SRAM芯片:使用雙穩態觸發器存儲信息

雙穩態觸發器這個圖做個了解就行

SDRAM是同步DRAM芯片,與傳統的異步DRAM不同。SDRAM與CPU的數據交換同步與時鐘信號,并且以CPU-主存總線的最高速度運行,而不需要等待插入狀態

而傳統的DRAM中,CPU將地址和控制信號送入存儲器后,需要經過一段延遲時間數據才能讀出或者寫入。在此期間,CPU不斷采樣DRAM的完成信號,在讀寫完成前,CPU不能干別的,降低了CPU的執行速度

而SDRAM在系統時鐘控制下進行數據的讀出和寫入,它將CPU發出的地址和控制信號鎖存起來,經過指定的時鐘周期后再響應,此時CPU可以執行別的操作

2.DRAM的刷新

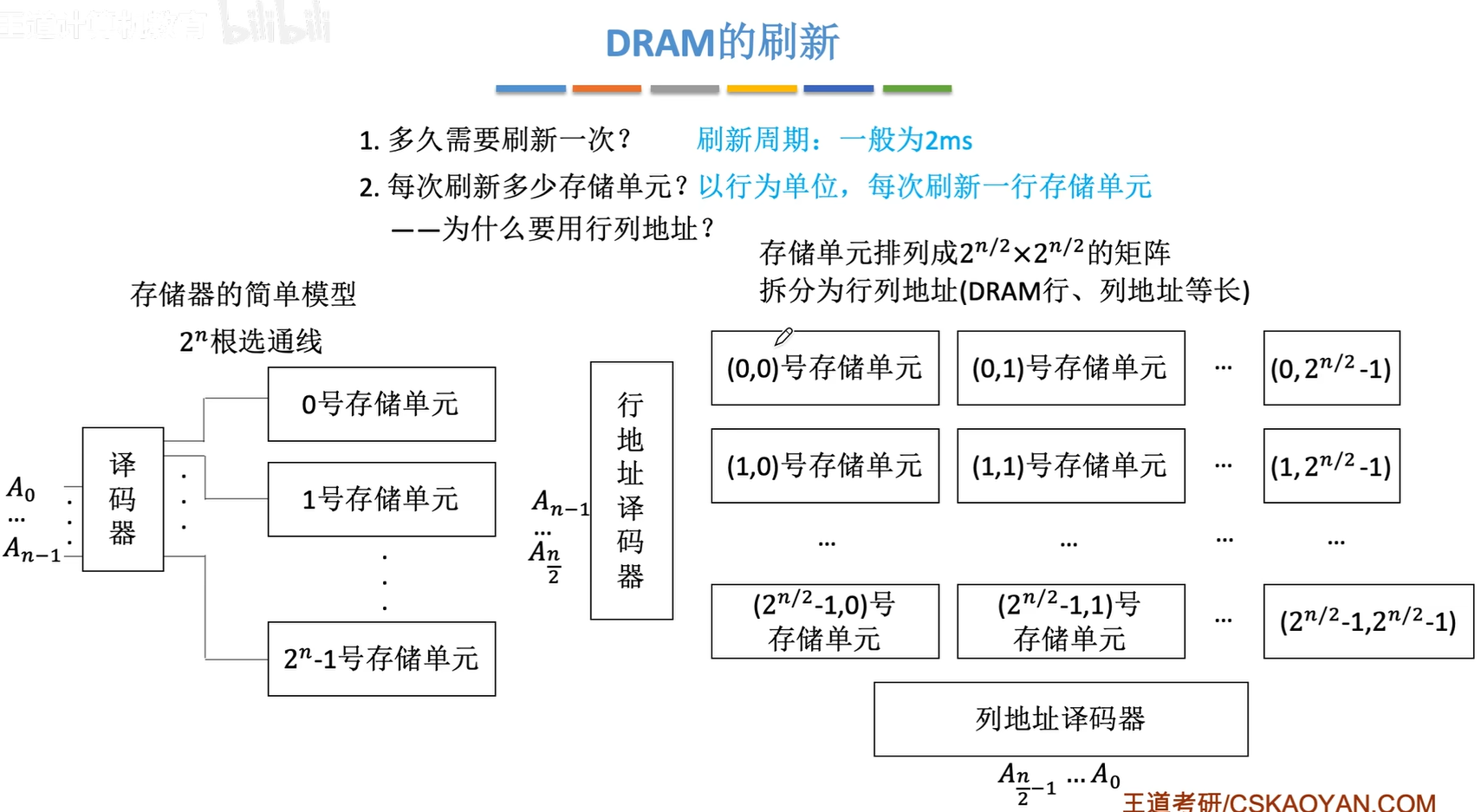

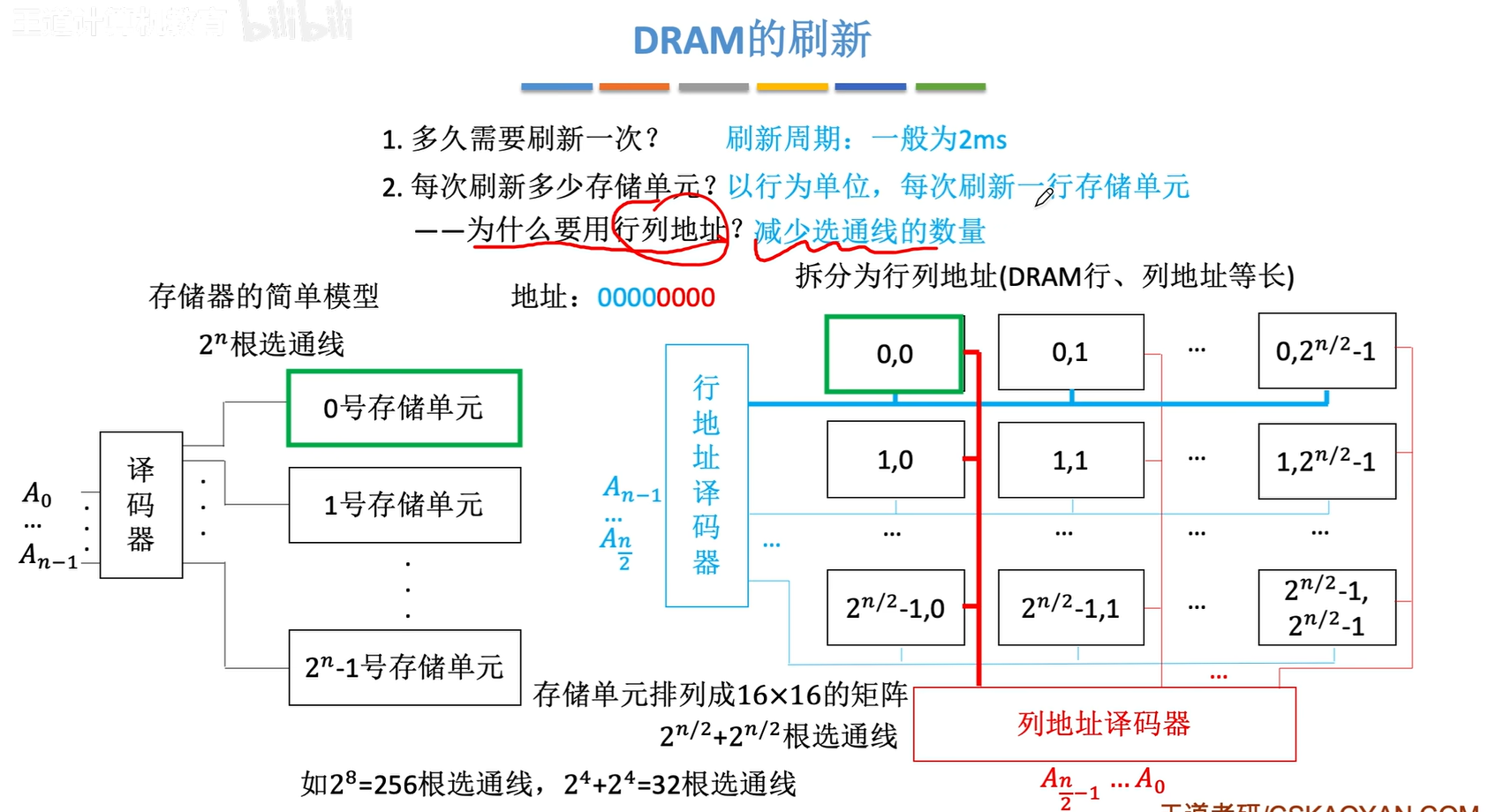

為什么要用行列地址(二維)?而不是用行地址或者列地址(一維)?

如果是一維的話,加入地址線有20位,那就需要220這么多個選通線才能連接到對應的存儲單元

但如果是二維的話,即有行和列來確定一個存儲單元,那行和列分別只需要210個選通線即可

即可以減少選通線的數量,使得電路變得簡單和清晰

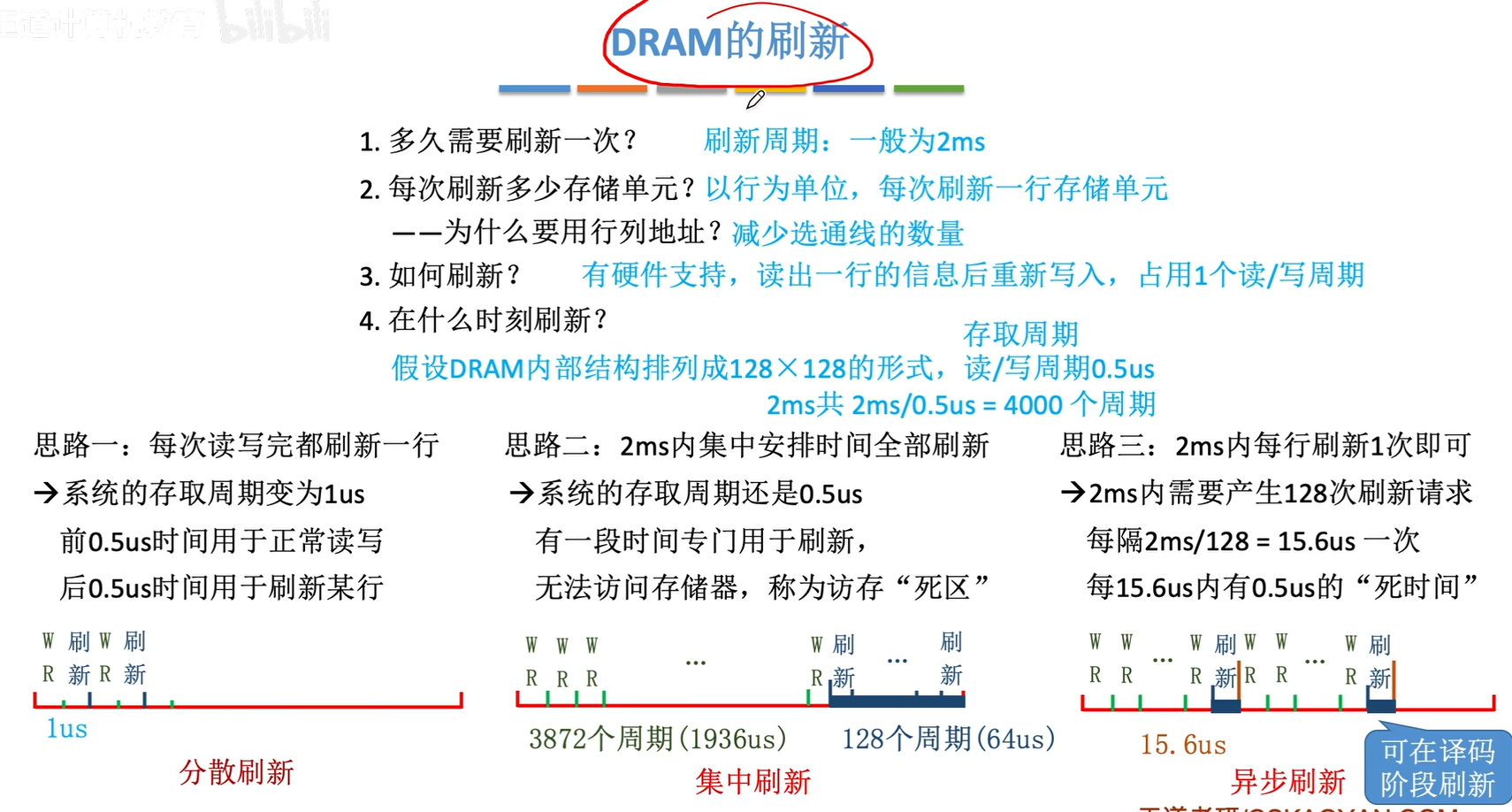

分散刷新不存在死區,因為把刷新時間算到存取周期里面去了,所以存取周期會變長。

異步刷新雖然縮短了死時間,但是死時間依然存在

CPU可以在死區時間的時候去做運算(比如譯碼階段),然后不是死區的時間來讀寫

一次完整的刷新過程只需要占用一個存取周期(書上P93頁15題)

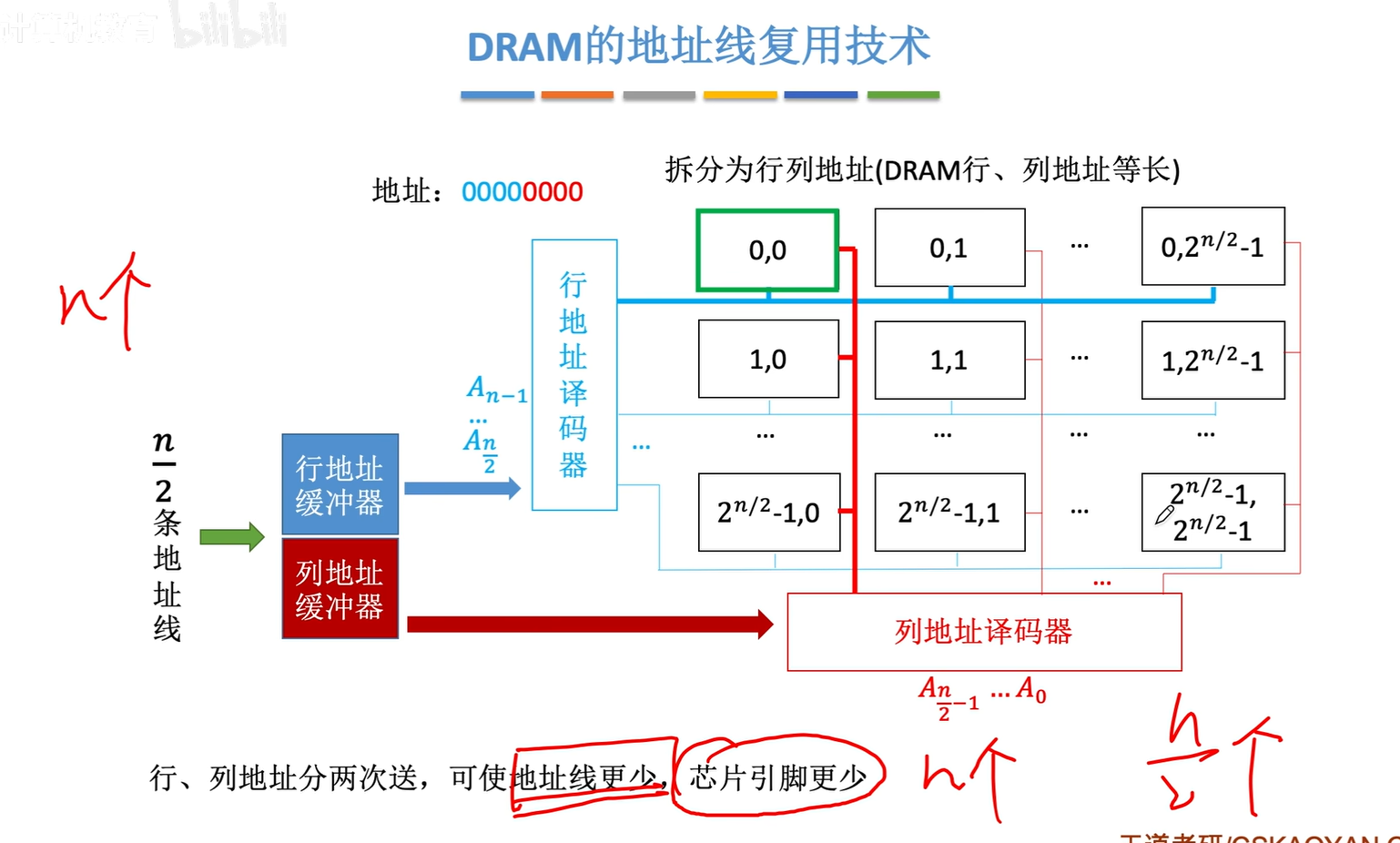

3.DRAM的地址線復用技術

行/列緩沖器通常使用SRAM實現

同時送行列地址,需要8根地址線。兩次送只需要4根地址線。

地址線復用技術:地址線是原來的1/2(行和列相等)且地址線分行、列兩次傳送。第一次送行地址到行地址緩沖器,第二次送列地址到列地址緩沖器,然后分別送到對應的譯碼器。

突發傳輸方式:在尋址階段給出數據的首地址,在傳輸階段可傳送多個連續存儲單元的數據

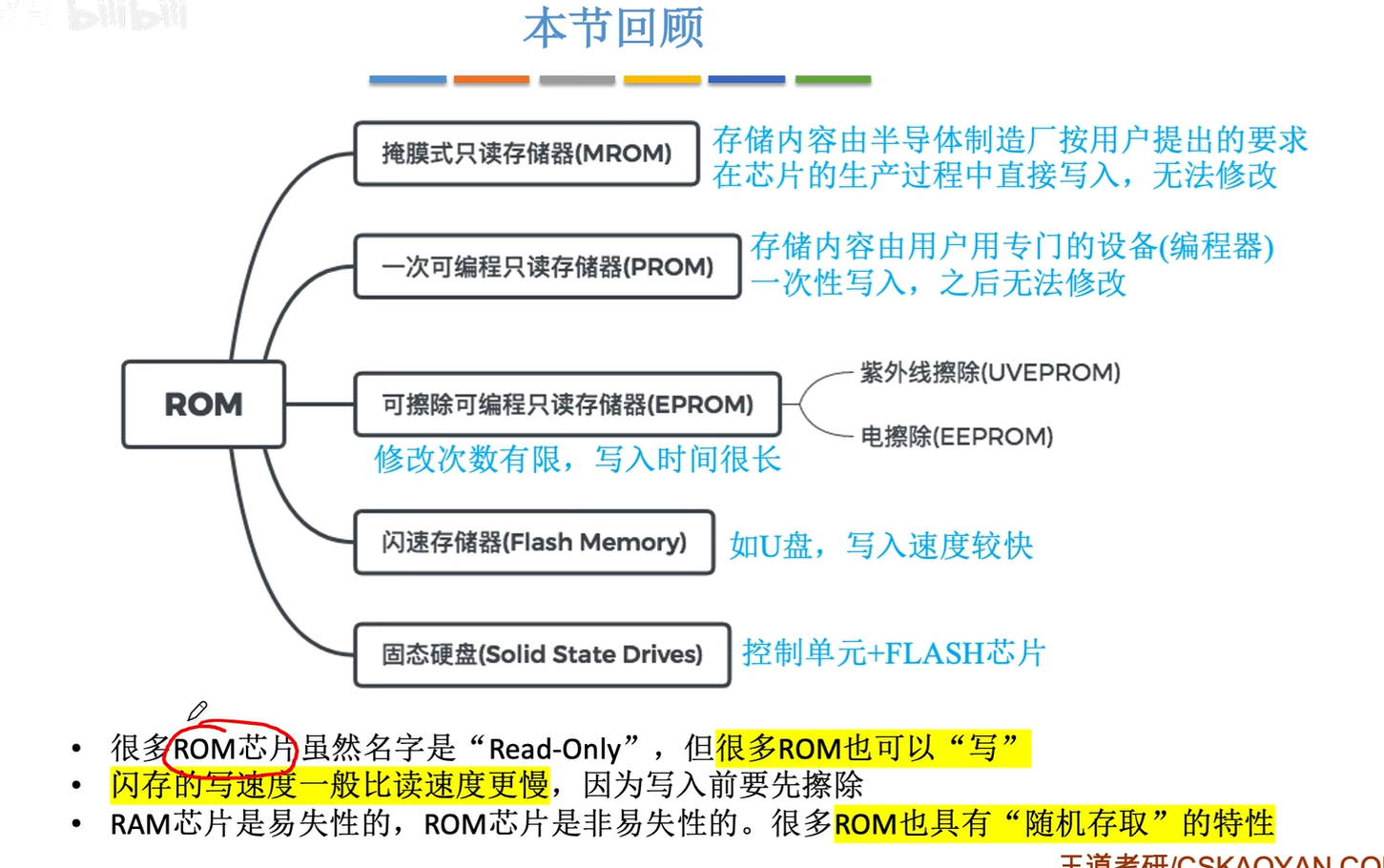

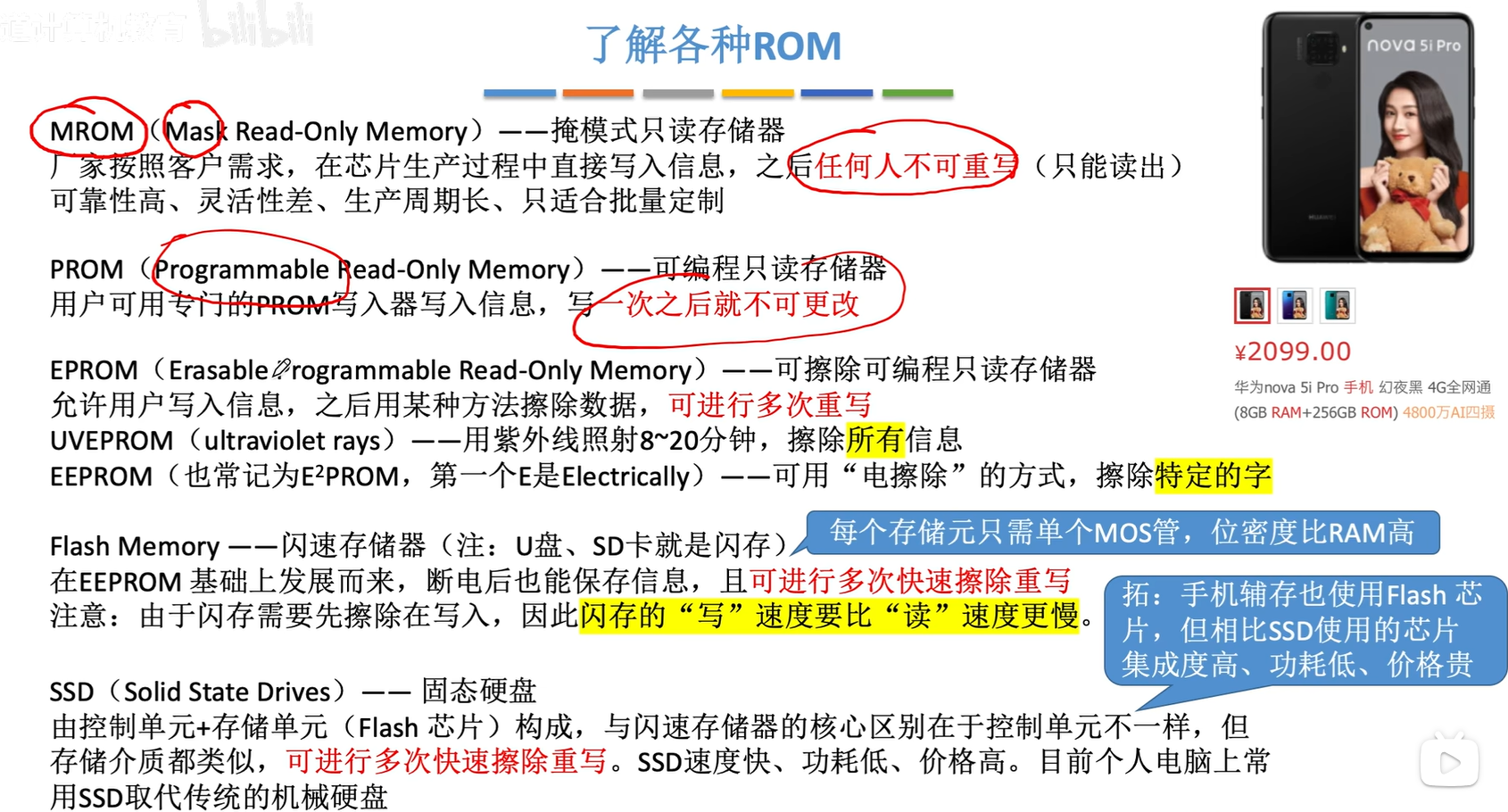

3. 只讀存儲器ROM

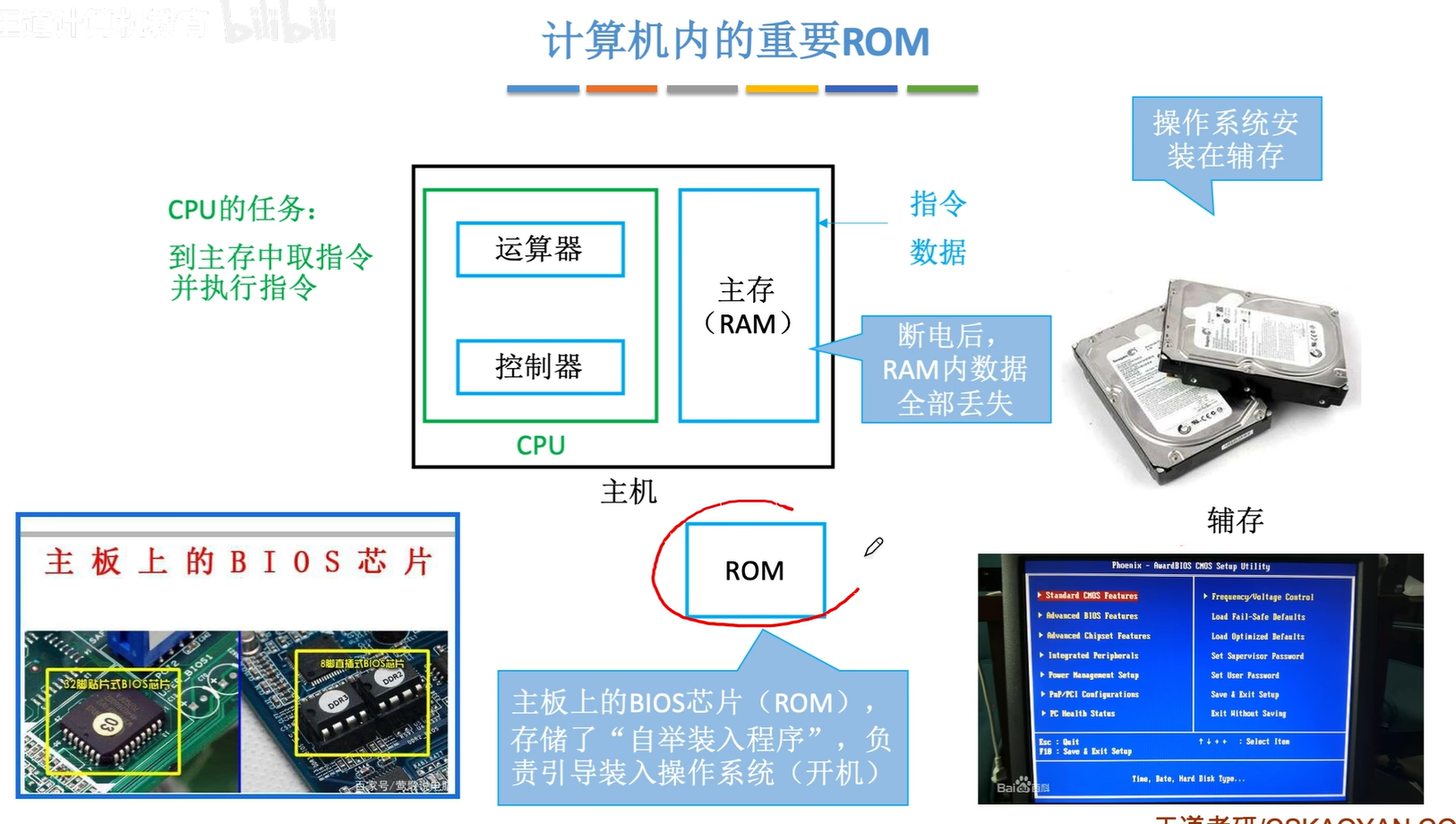

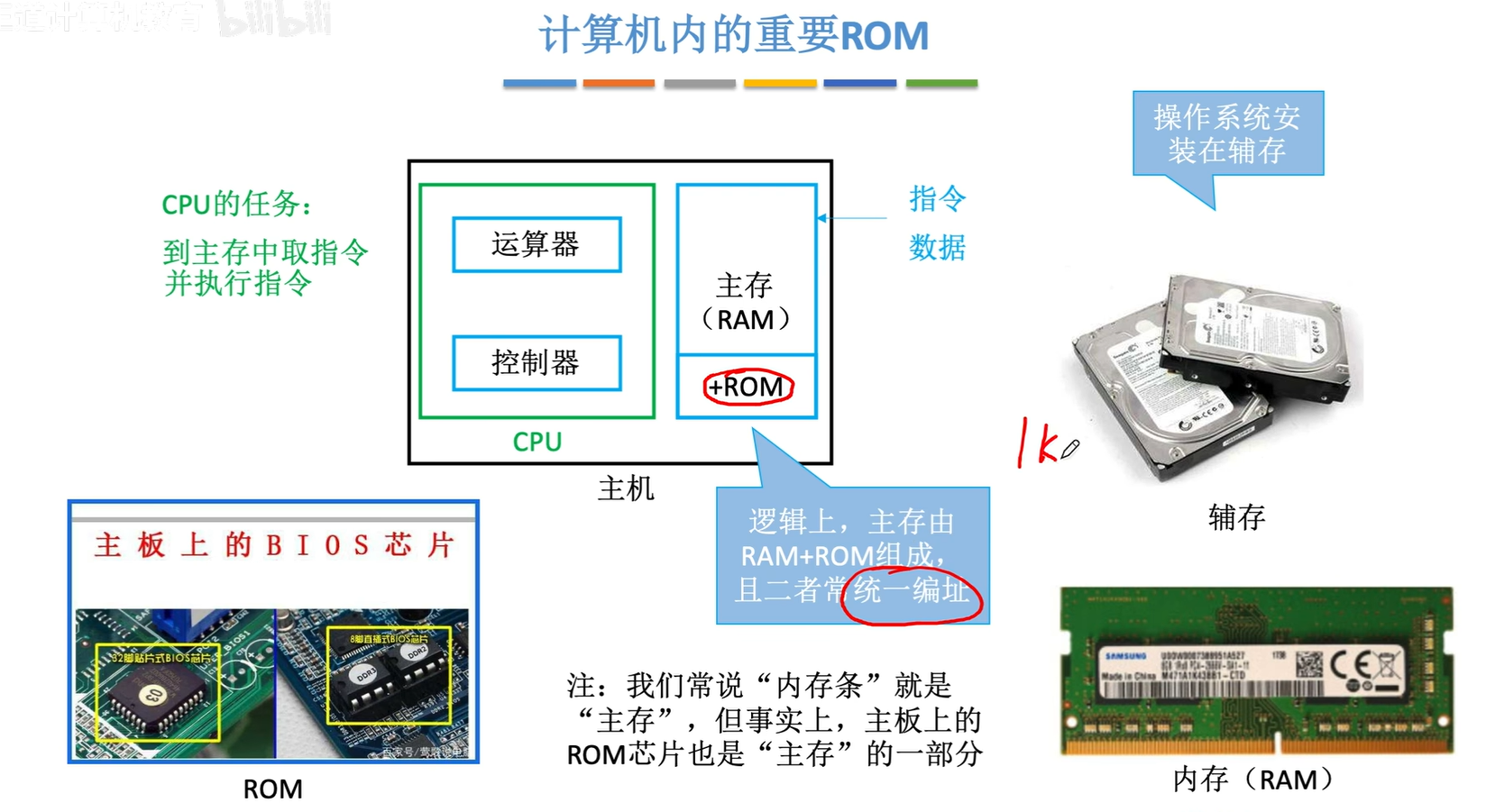

RAM和ROM可以統一編址。比如主存就是

易失性說的是斷電后數據會消失

EPROM不能作為隨機存儲器。

UVEPROM要擦除只能選擇全部擦除或者不擦除,不能擦一部分剩下的不擦除

閃存存儲元件由MOS管組成,是一種半導體存儲器,采用隨機訪問方式,可替代計算機外部存儲器

說主存不是光有內存條這個RAM,還有主板上的ROM芯片,也是主存的一部分

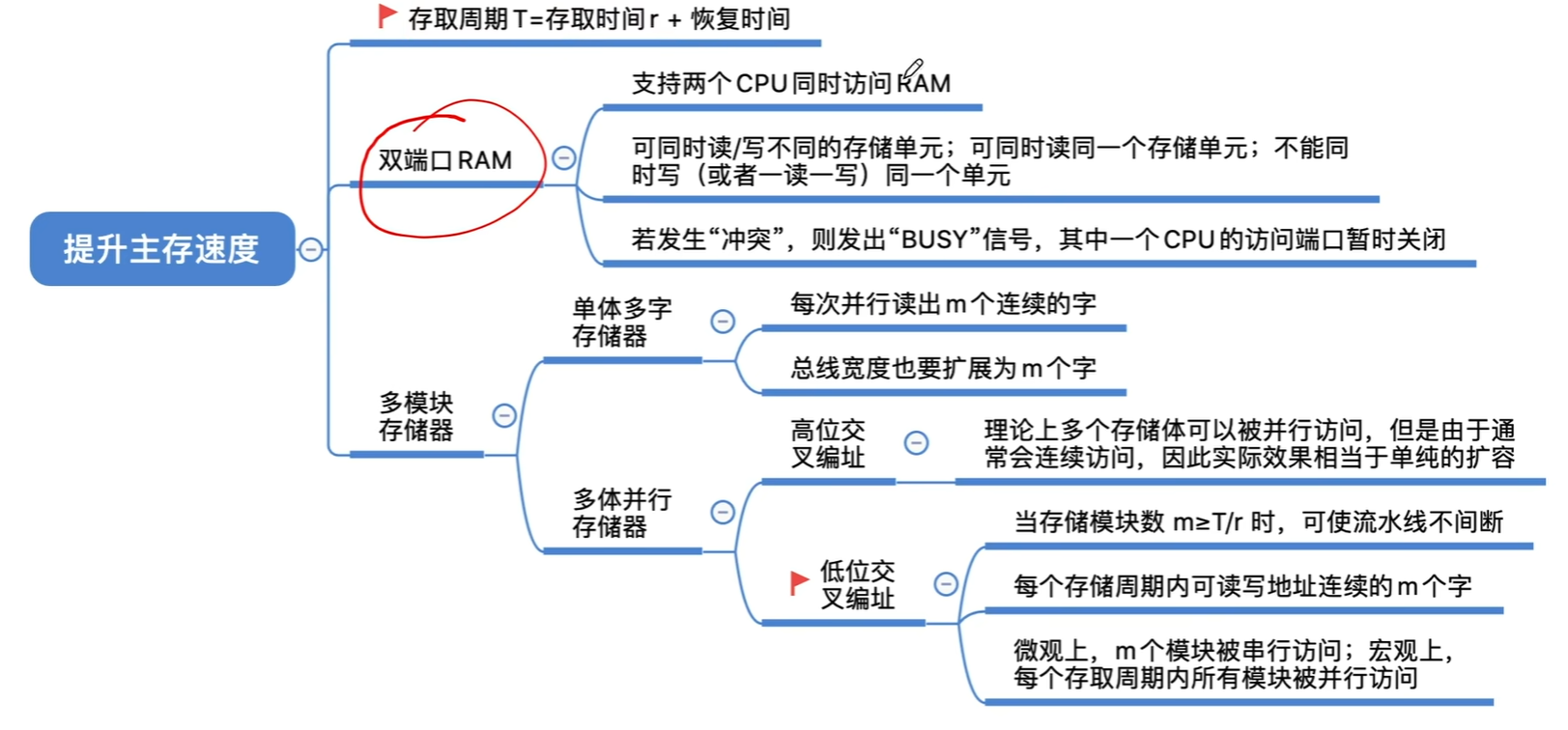

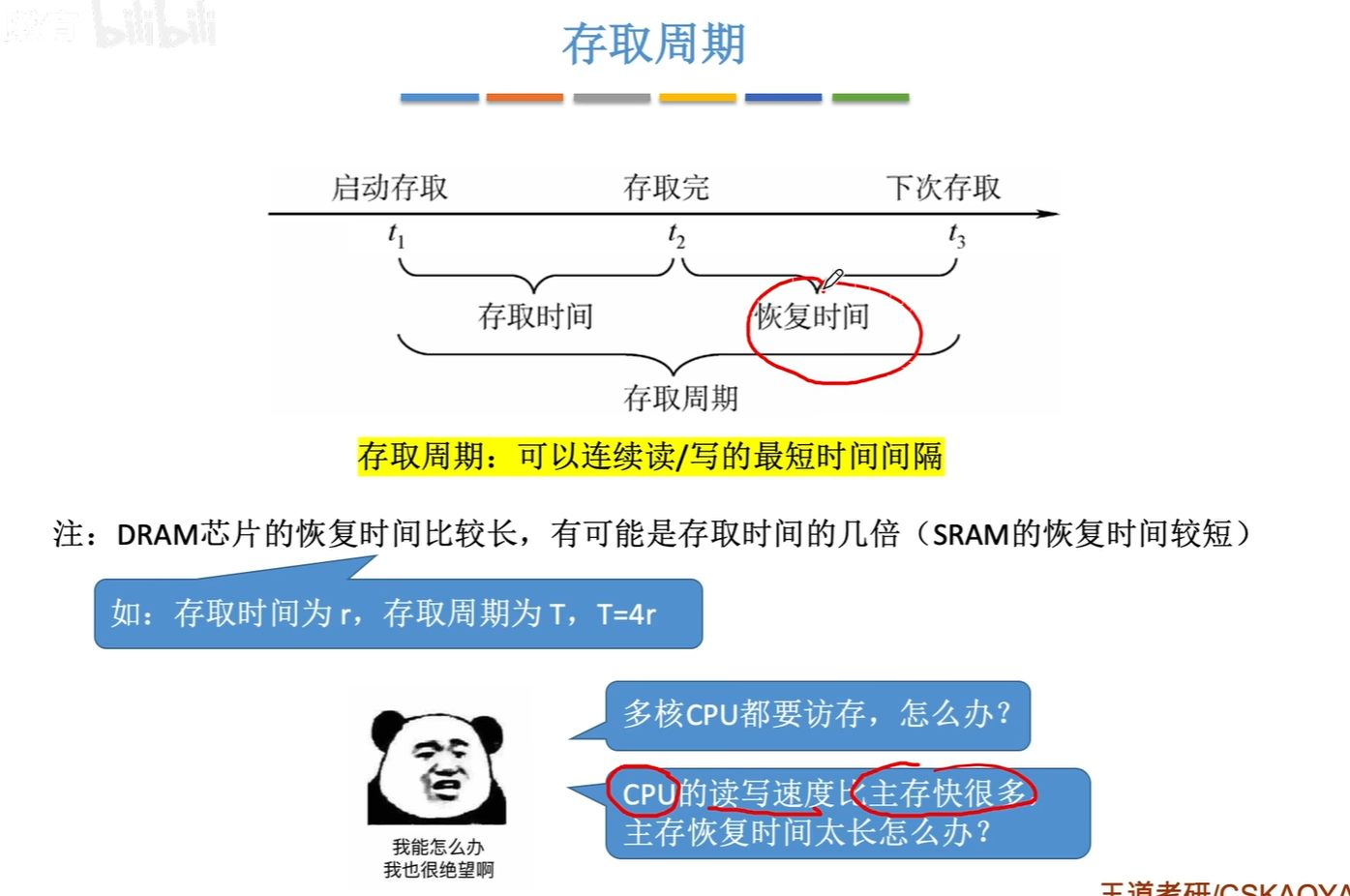

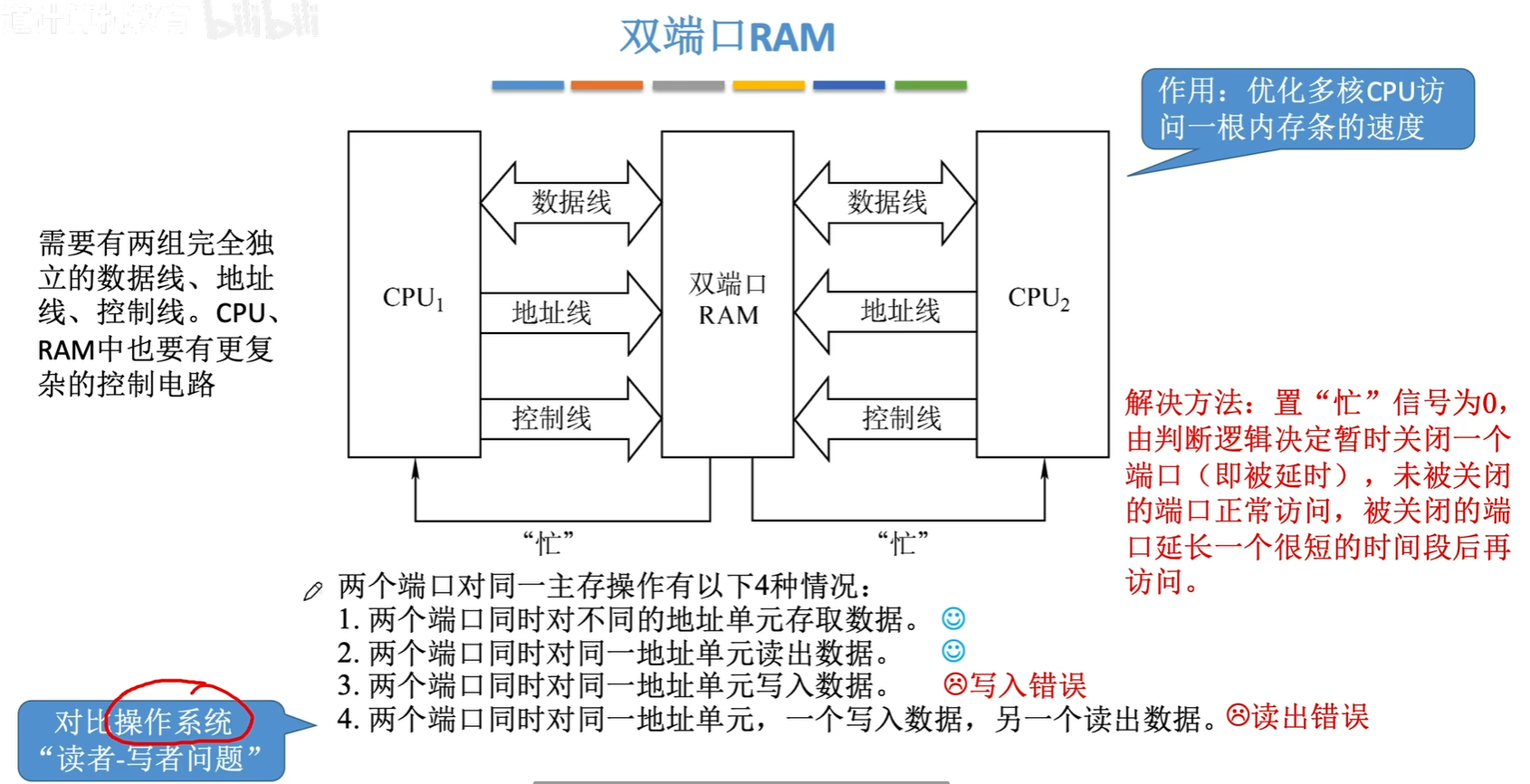

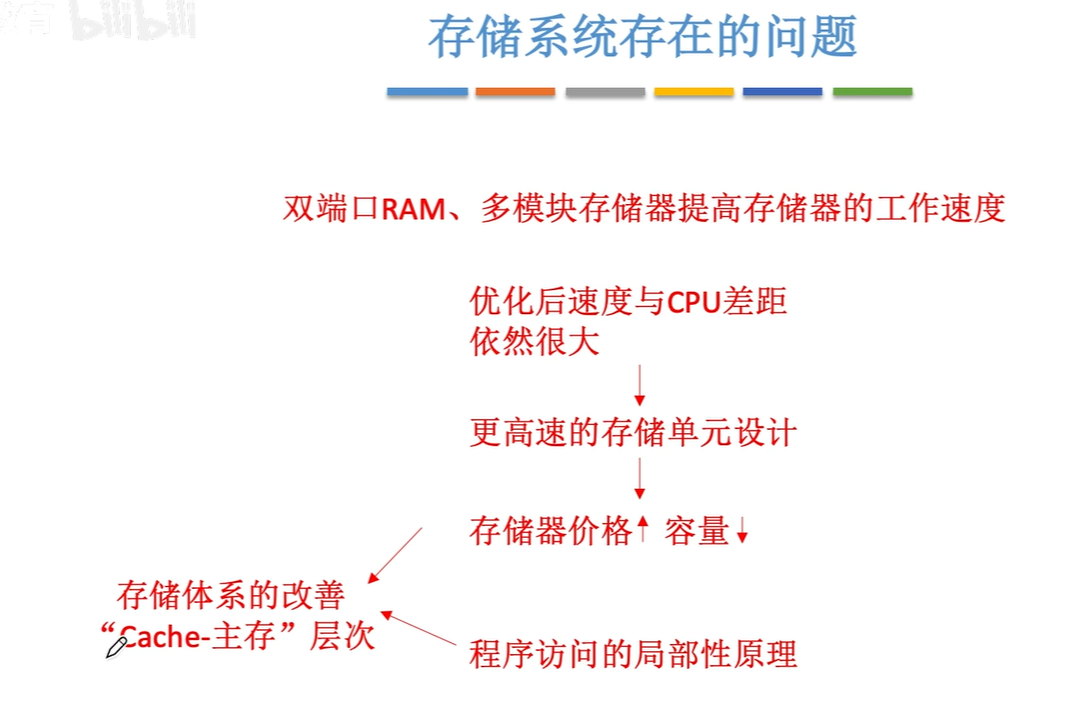

4.雙端口RAM和多模塊存儲器

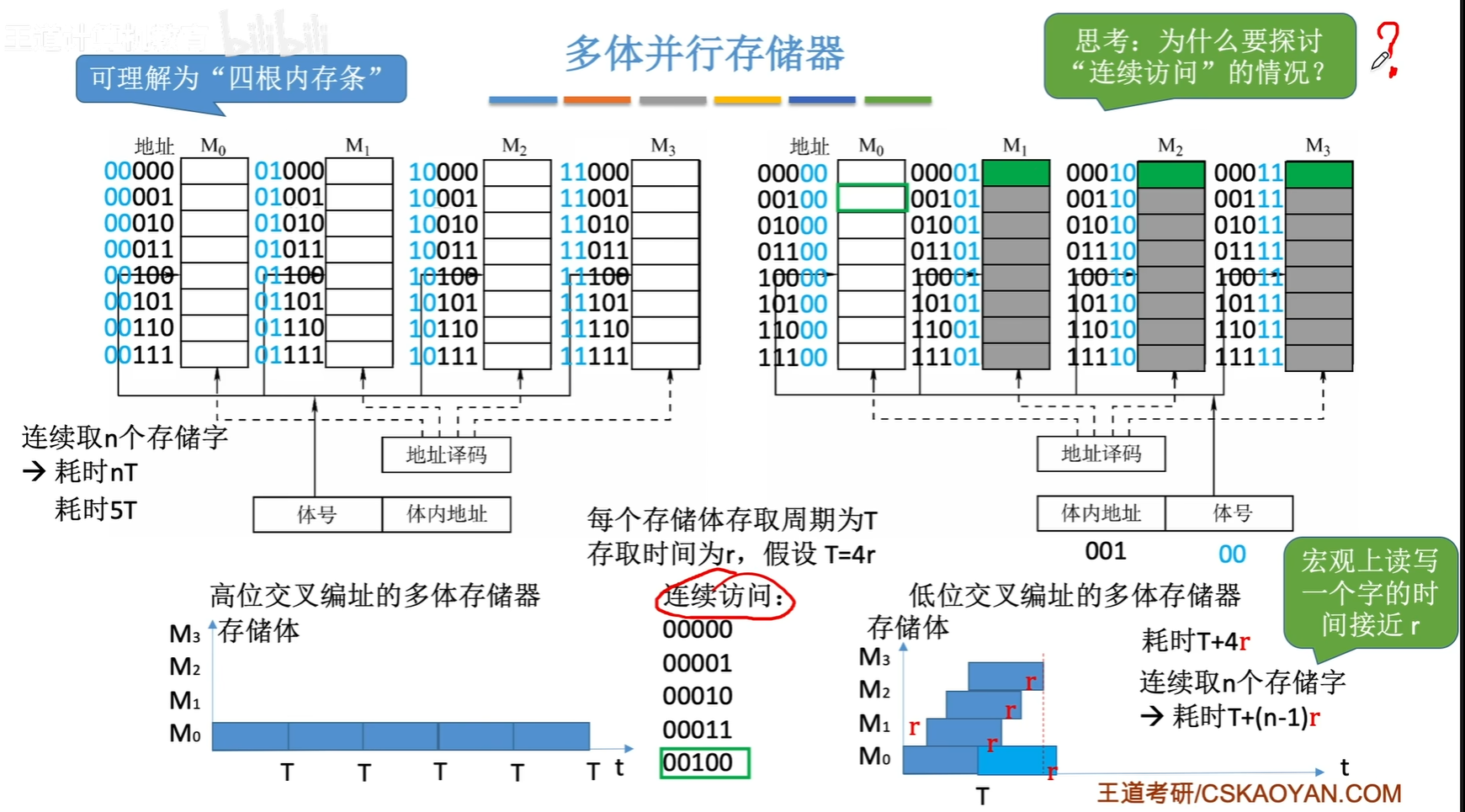

單純的擴容的意思是說,高位交叉編制沒有加快訪存的速度,即CPU在恢復時間內不能訪問正在恢復的內存條的情況沒有被改善,而低位卻有效改善了這個問題,加快了訪存速度

連續訪問者五個地址的數,分別是編號0,1,2,3,4

對于高位編址來說,這五個數據都在M0內存條上,而讀或寫完一個數據以后就要等待恢復時間,所以花費的時間就長很多

而對于低位編址來說,0在M0,1在M1,2在M2,3在M3,4在M1。那我們花r的時間讀完M0上面的0就可以立馬去讀M1上的1,而不需要等M0恢復,從而節省了很多的時間。

為什么討論的是連續訪問(連續地址)的情況?因為很多情況下就是訪問連續的地址比如數組

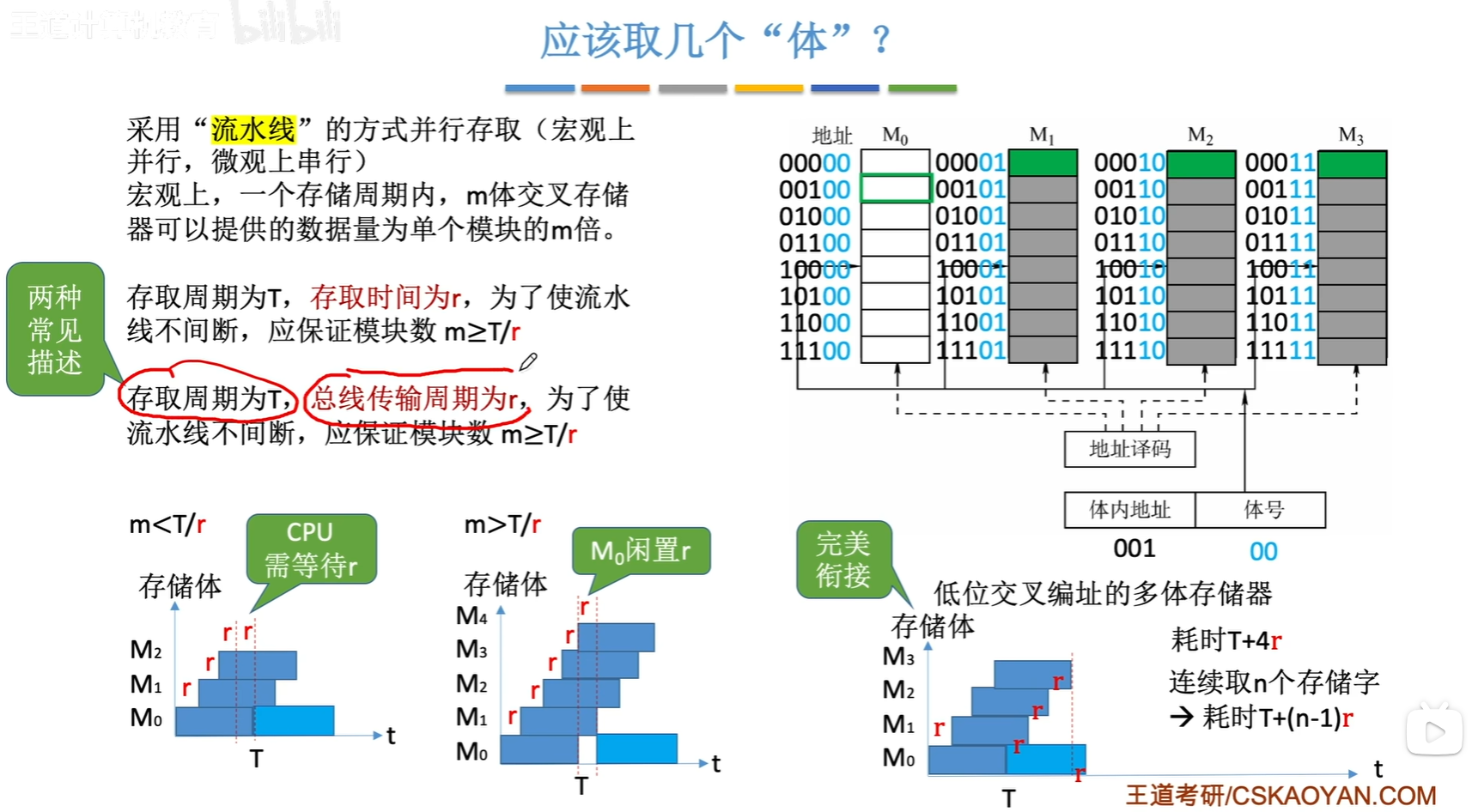

m=T/r的時候就是完美銜接,這個時候就是最好的情況,沒有閑置也不用等待,而且存儲體的個數也最少,成本就低

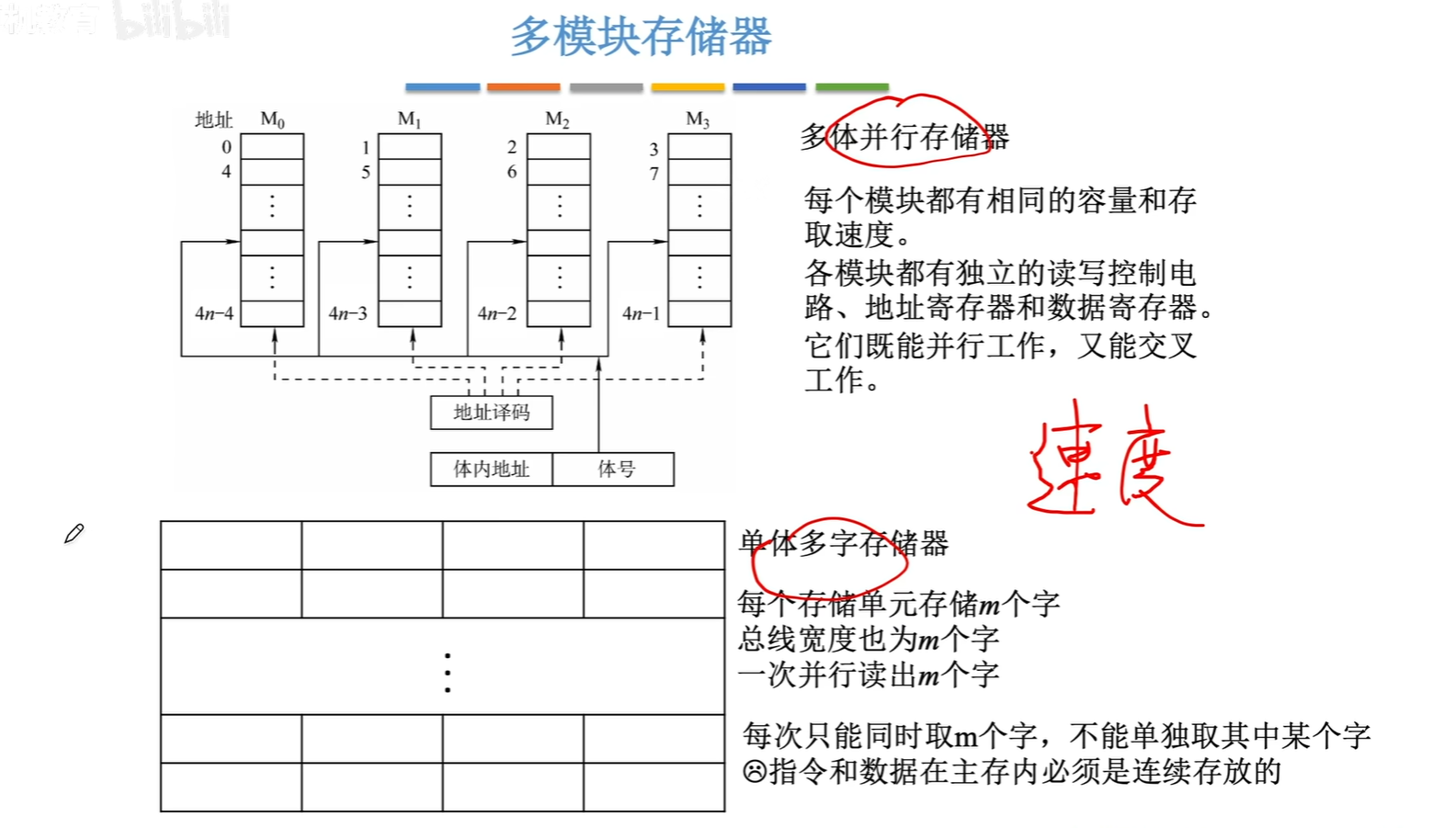

對于靈活性來說,多體比單體好一些,比如讀取,2,3,4,5這四個存儲單元的數據

多體會直接讀取這四個,而單體就會把第一行和第二行全給讀下來,那么0,1,6,7這四個就是多讀的,其實不太需要這四個

對于速度而言,兩者相差不大

對于上面的多體,有m個存儲體,而m=T/r的時候最好,在一個存取周期T內也是讀出m個字

對于下面的單體,每個存儲單元有m個字,在一個存取周期T內一次也是讀出m個字

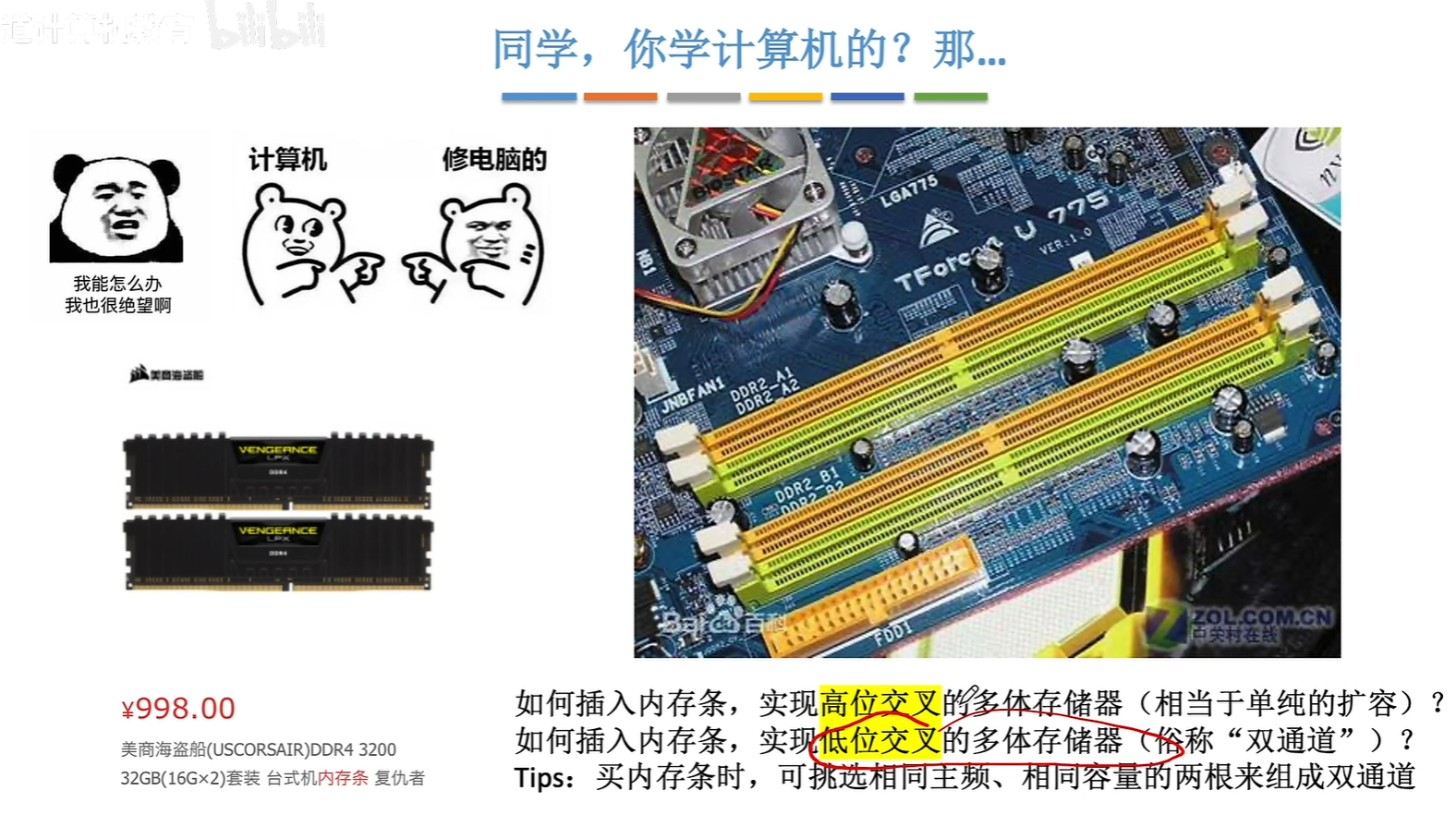

相同主頻:主頻不一樣的話,高的主頻會向下兼容,和低的主頻保持一致,這樣其實就相當于白花了很多錢

相同容量:在兩者容量相同的地方,還是雙通道,但是在低容量沒有了的地方,而高容量內存條還有內存的地方,那其實就相當于單通道了。用游戲來說的話,如果正好放在了低地址的地方,即雙通道的地方,那運行速度就快,但是如果不巧被放到了高地址的地方,那就還是單通道,性能會很不穩定

如圖:左邊只有三個存儲單元,右邊有8個,就會出現上面的情況

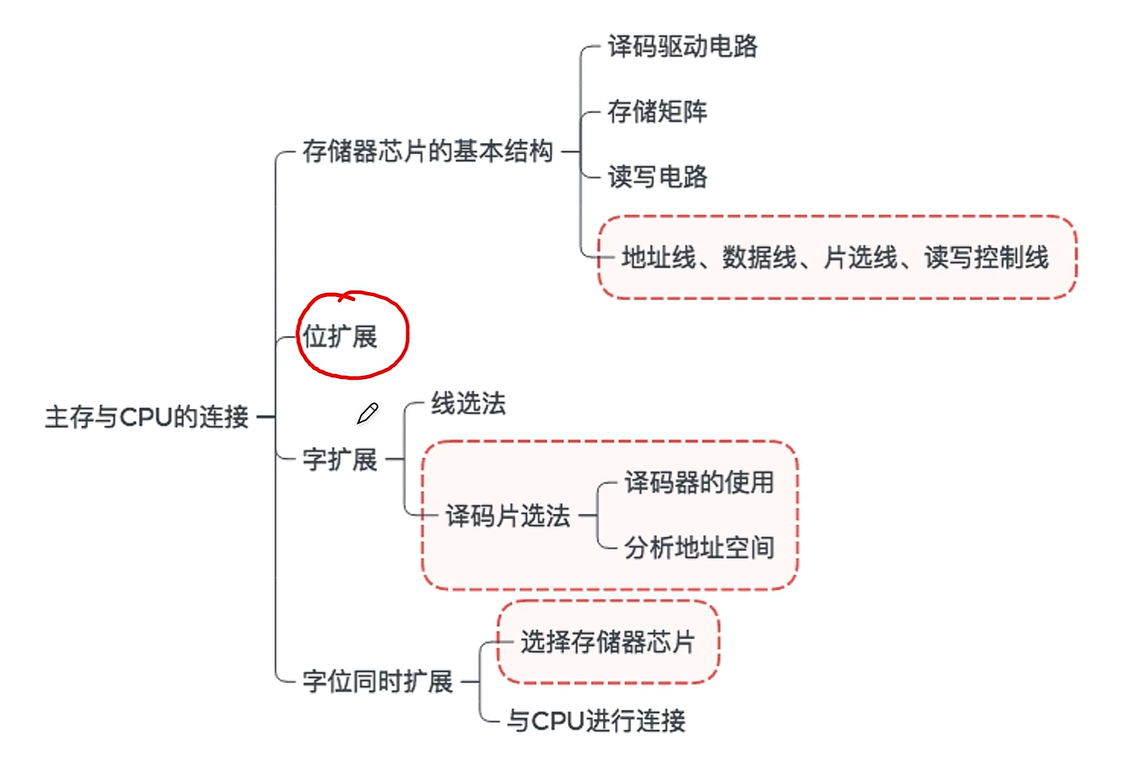

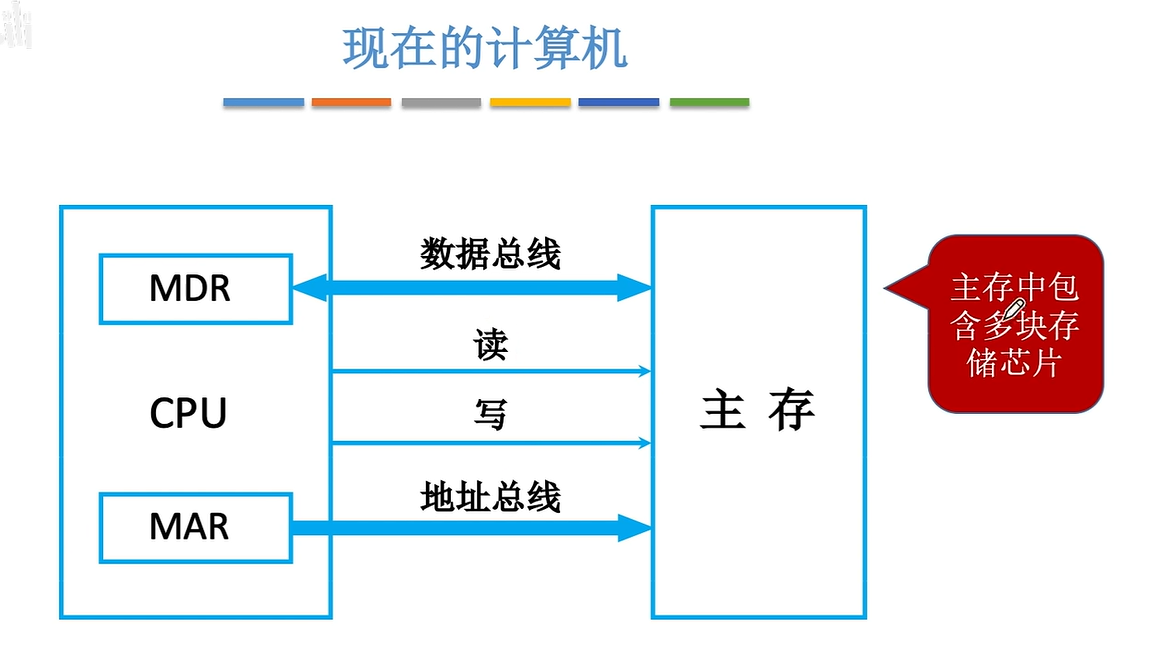

3.3 主存儲器與CPU的連接

現在的計算機MAR、MDR都在CPU中,而不再主存中

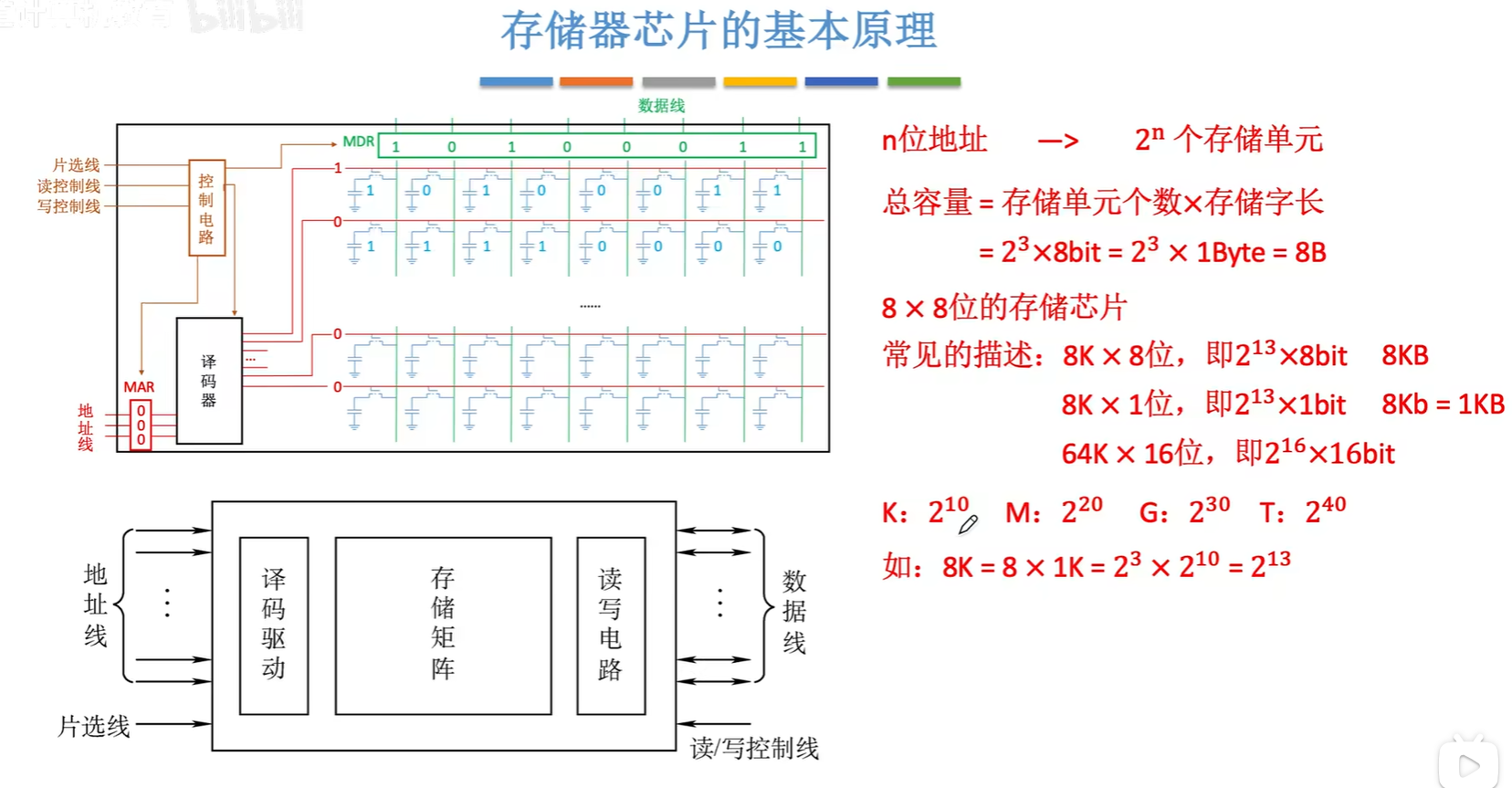

8K*8位含義

8K是存儲單元數量,是213,需要13根地址線

8位是每個存儲單元存儲的bit位數

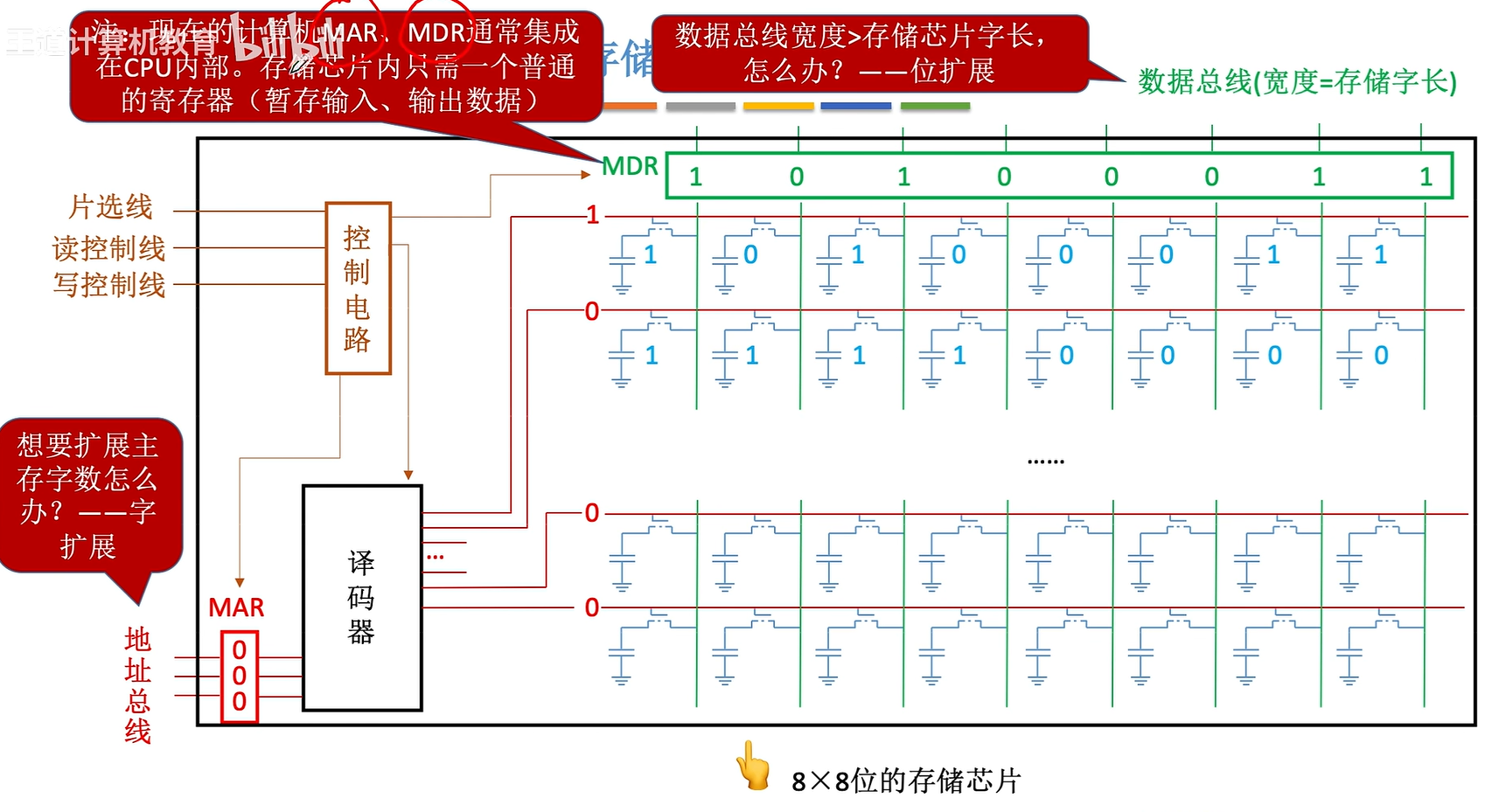

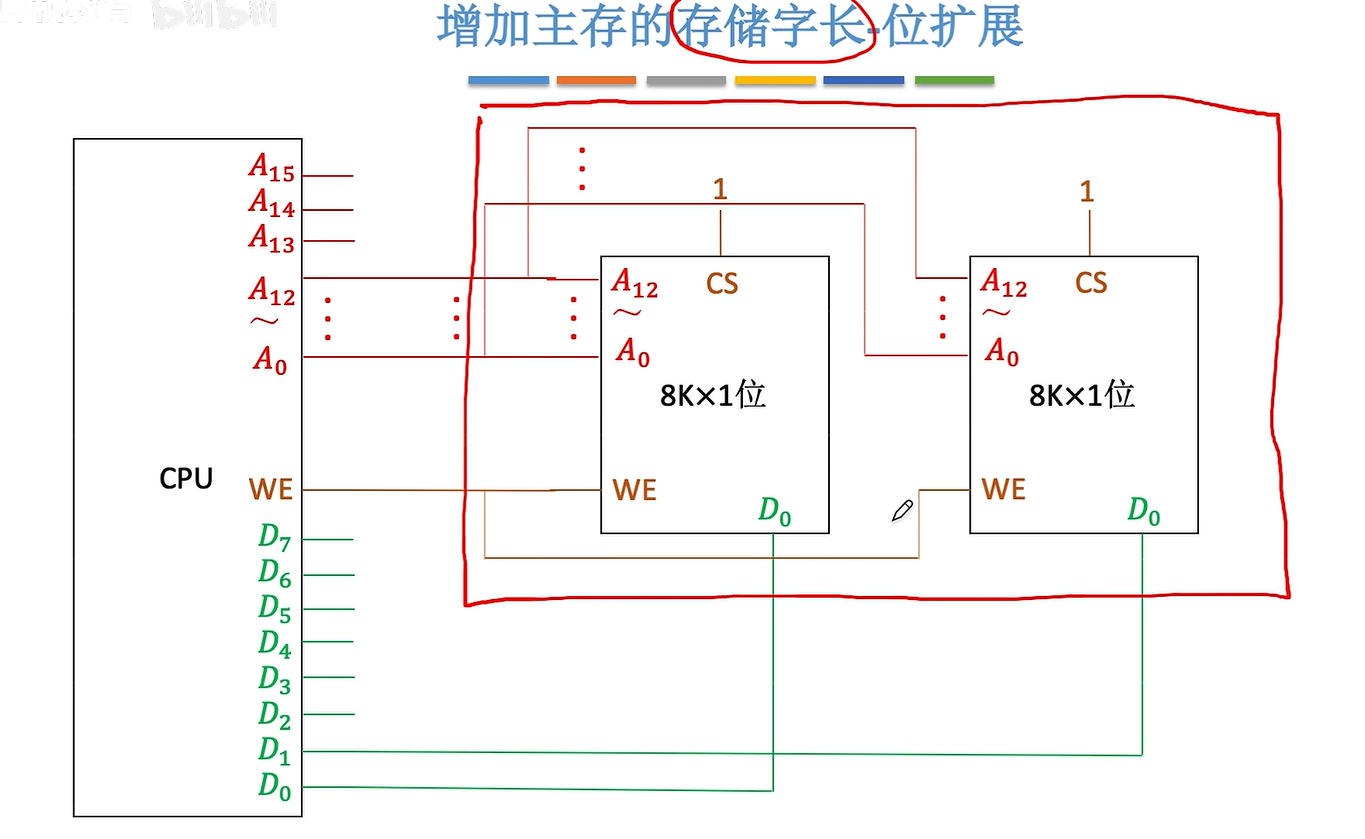

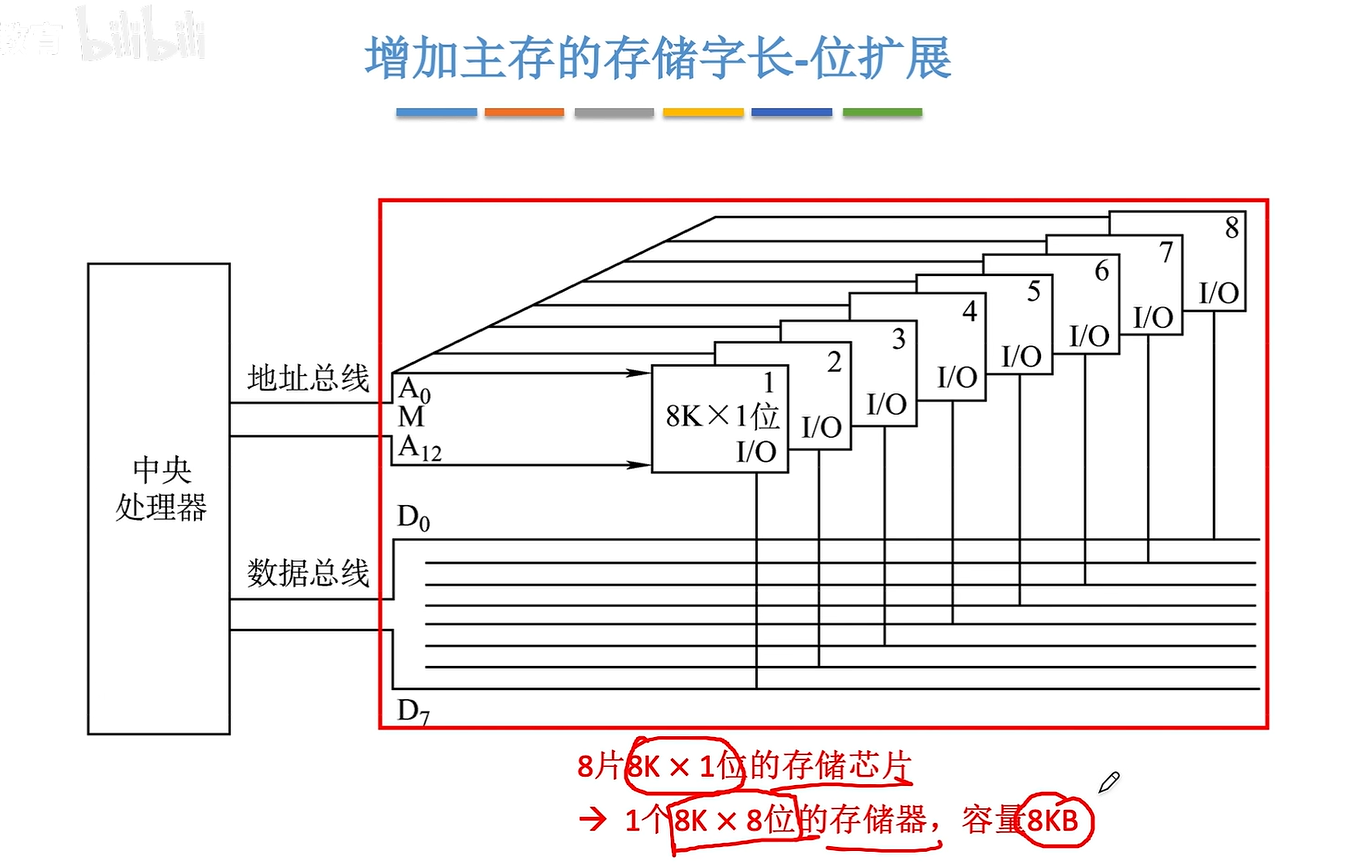

1.位擴展

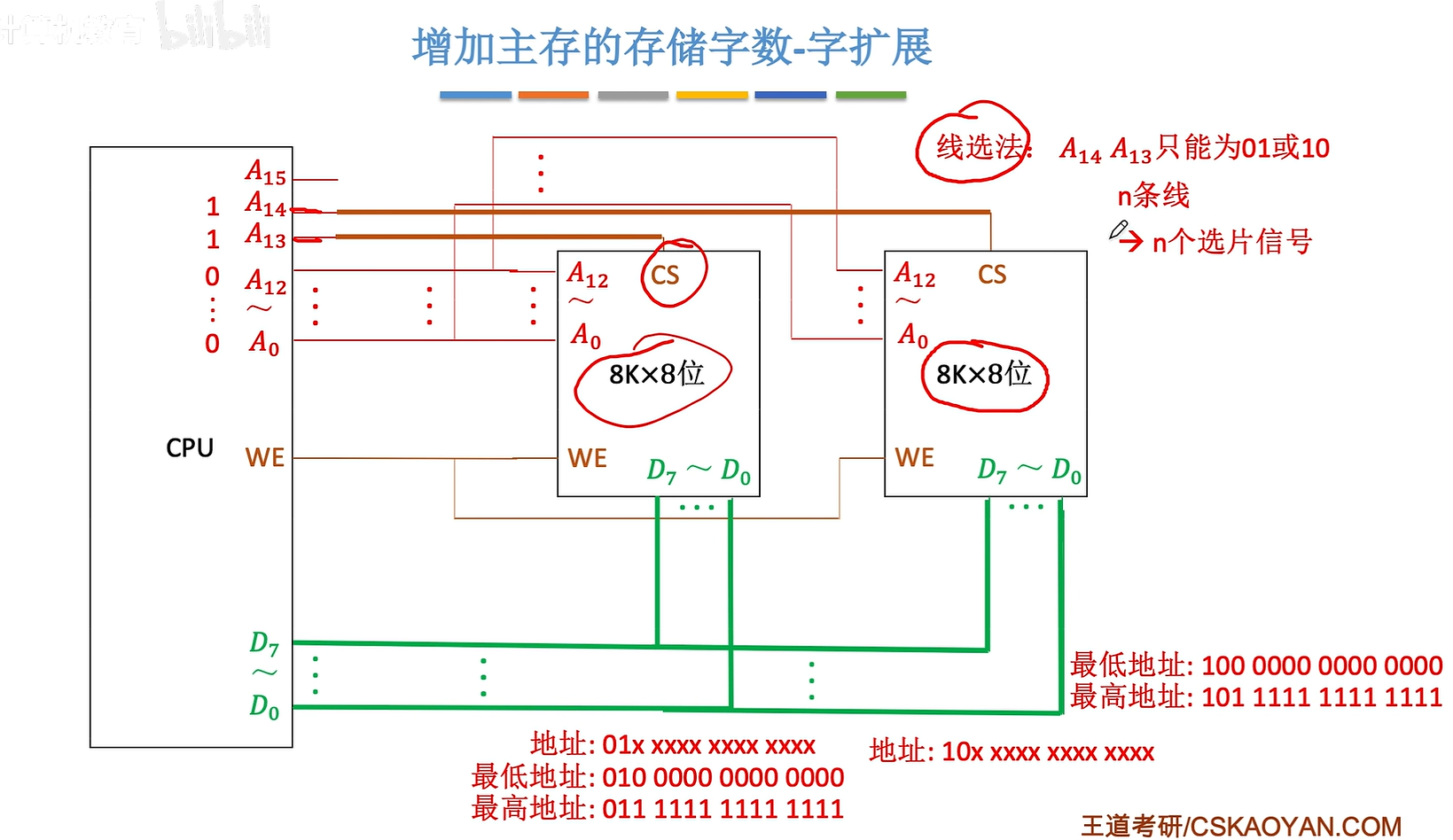

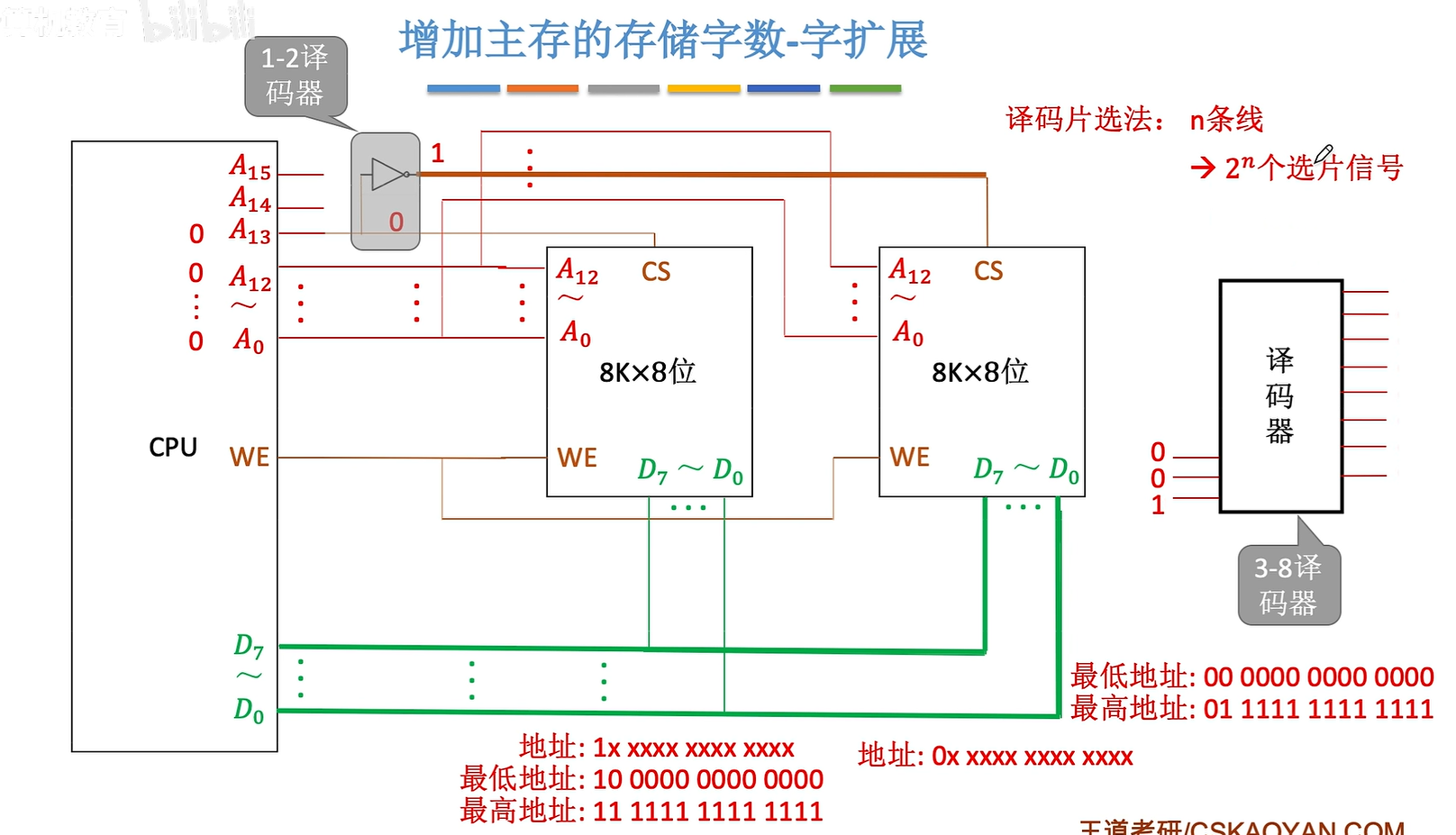

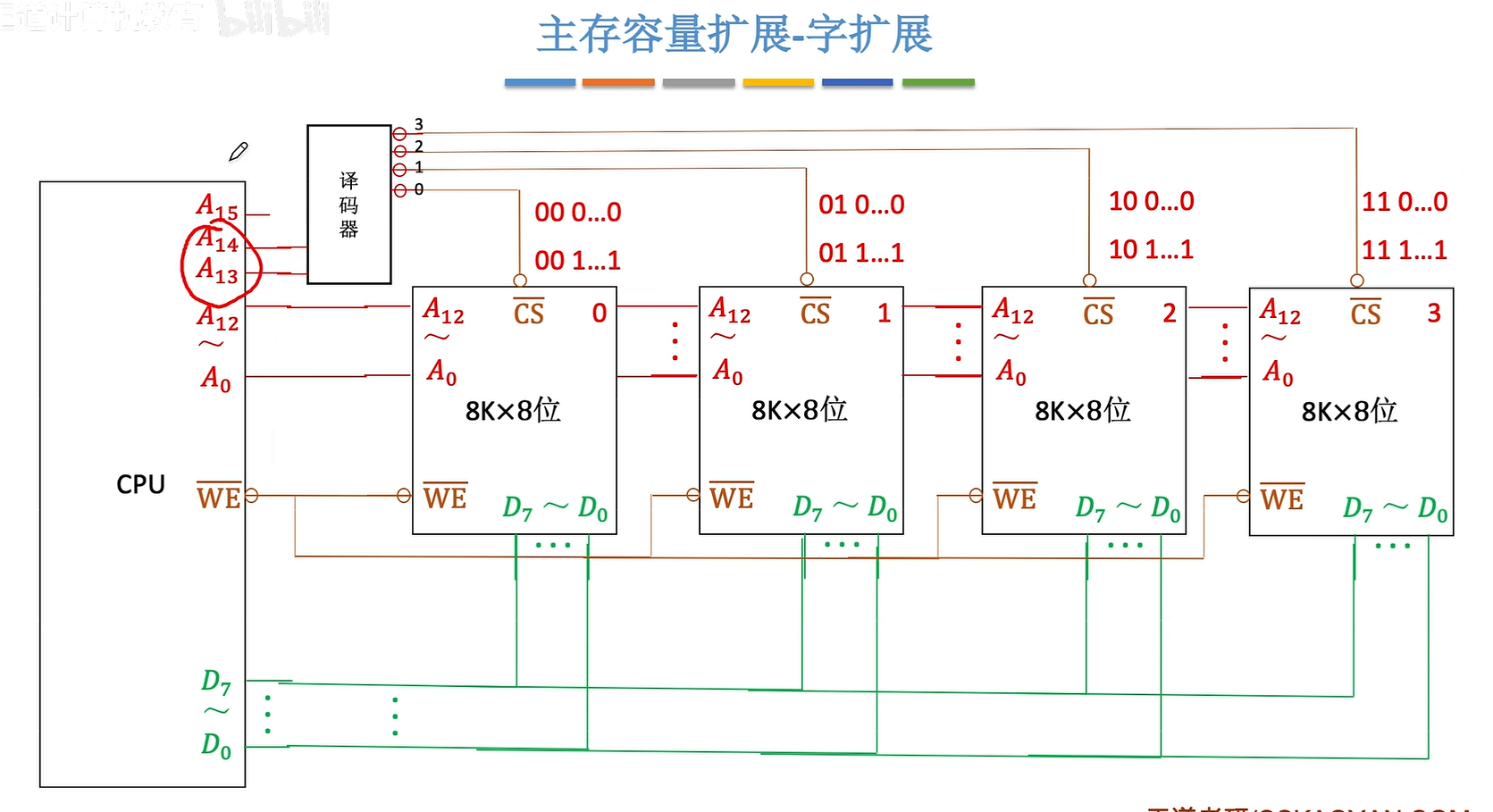

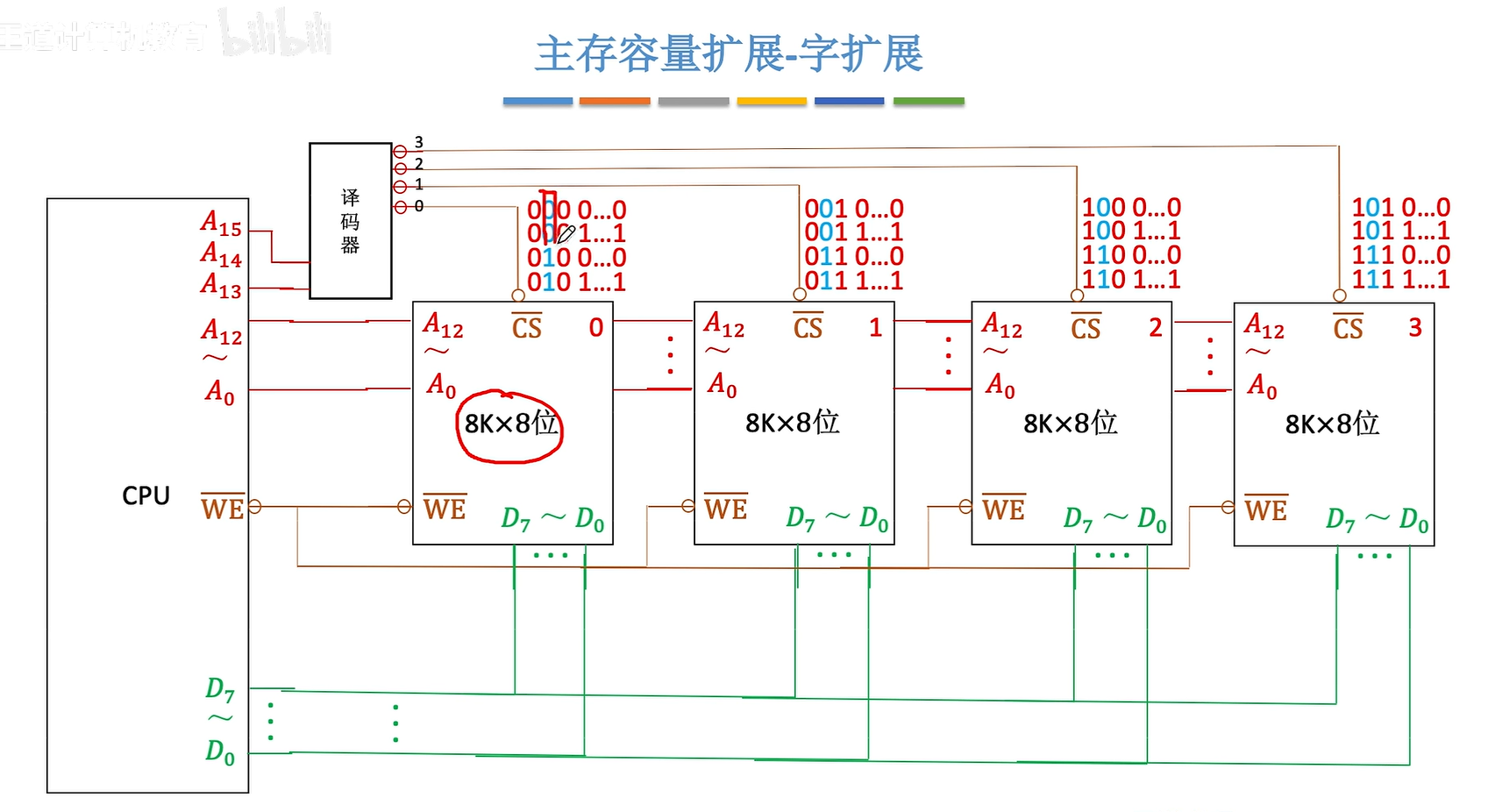

2.字擴展

用這種方法,CPU有n條多余的地址線,只能有n個片選信號

并且把兩塊芯片看做一個整體的話,那么開頭的地址只能為01或者10,不能用00或者11

可以做如下的優化(譯碼片選法),就是在第二塊的片選線上加個非門,這樣的話地址空間就是連續的了,從全0到全1都可以用了

考試可能不選A13和A14這兩個連著的,可能選A13和A15作為譯碼器的輸入,那么A14是多少就無關緊要了

那么就會發現多出來了一倍的地址,全都映射到這四塊芯片中了,而四塊芯片肯定裝不下,所以實際中不可能用這種設計

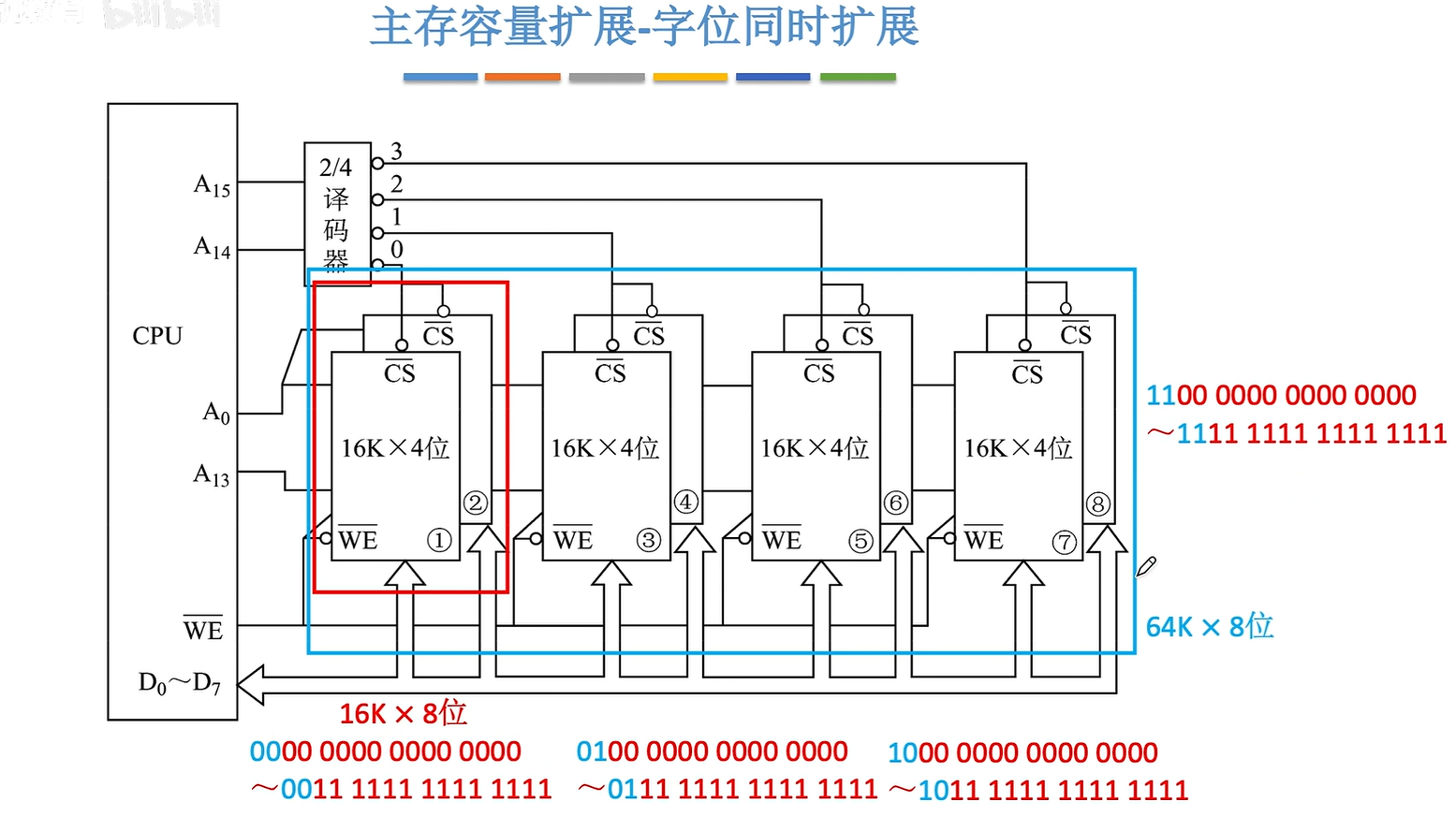

3.字位同時擴展

一共四組芯片,一組2個芯片。

1.原來是一塊芯片,16K*4位

2.位擴展得到每組的芯片個數,就是目標位數除以單個芯片的位數,8/4=2,所以每組是2個新盤

經過位擴展后,變成一組芯片,16K*8位

3.字擴展得到一共要幾組,就是目標存儲單元數量除以一組的單元數量,64K/16K=4,那么一共需要4組

經過字擴展后,把16K*8位變成64K*8位的

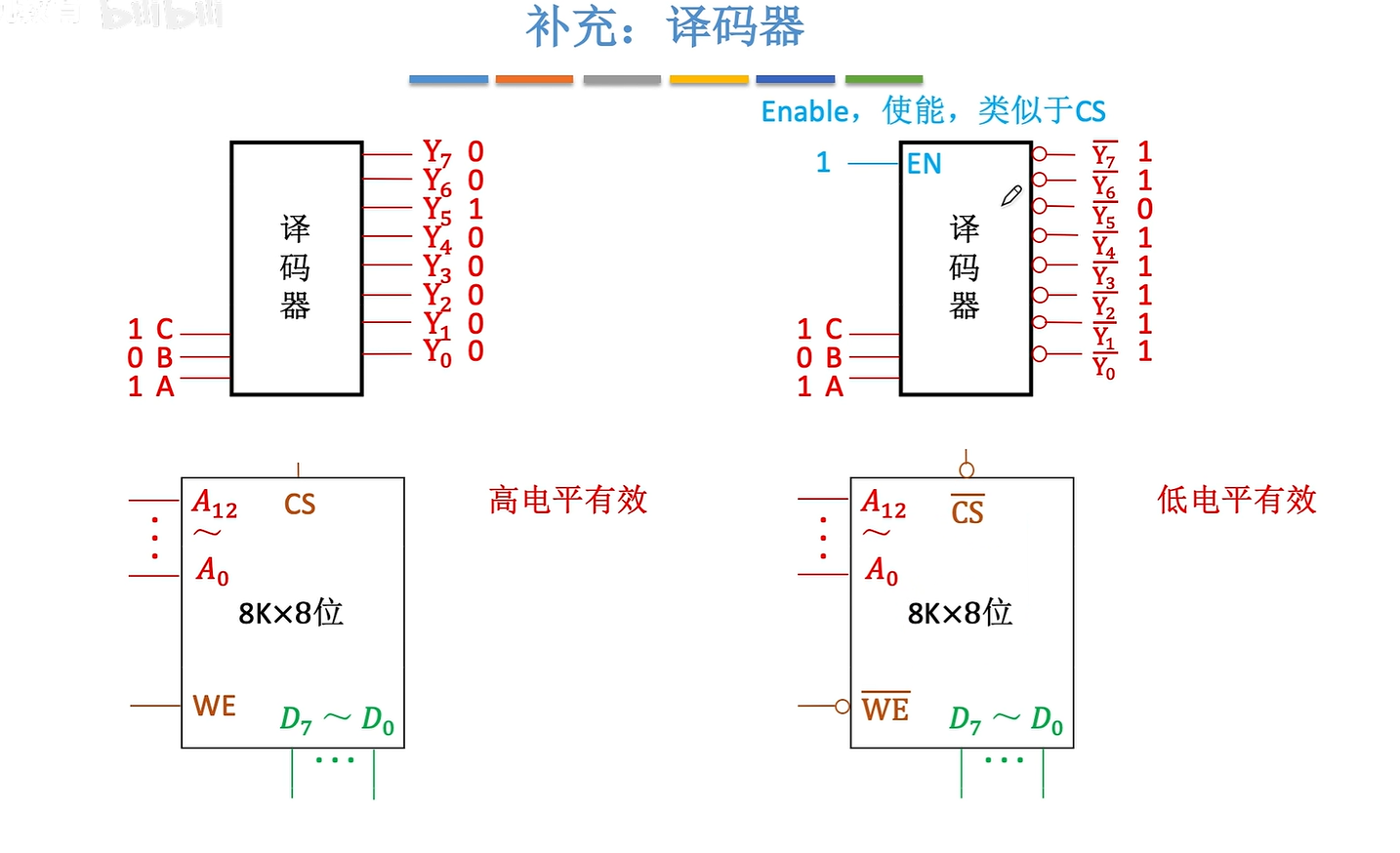

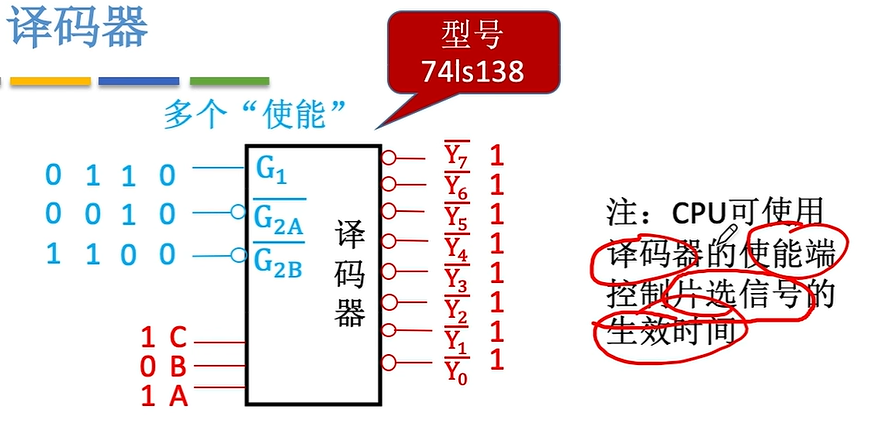

有3個使能信號,那么必須同時滿足才可以工作,有一個不滿足就不可以工作

也就是只有100才會正常工作,而其他的001,101之類的都是非法信號,會讓所有的結果都為0,再取反那就都是1然后輸出出去了

這樣可以讓CPU使用使能端控制片選信號的生效時間

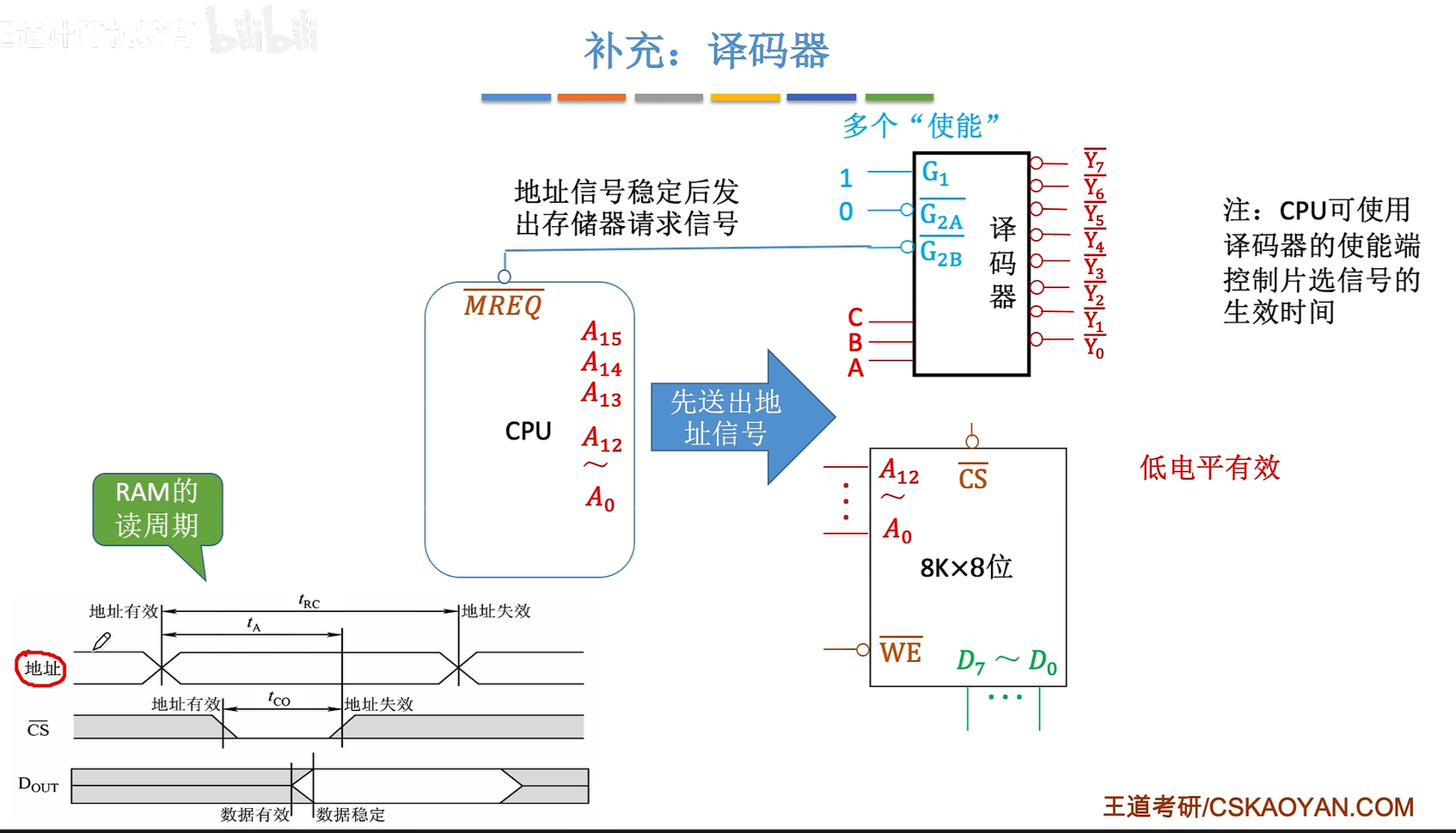

MREQ,低電平有效,主存請求信號, 當CPU想要訪問主存的時候就會讓它有效

它有效才會讓譯碼器使能,也就是讓譯碼器有效

CPU訪存是這樣的:

1.先發送出去地址信號,由于地址信號都是電信號,所以要先等一下讓它穩定

2.等到地址信號穩定以后讓MREQ有效,然后片選線才會有效

這樣保證了主存收到的地址信號一定是穩定的

對于左下角的圖,中間有上上下下的,那說明傳過去的電信號有1有0,就是有高電平也有低電平

上面提到,發送出去地址信號以后會等一段時間。所以圖中地址有效的時候CS并不是立馬開始有效,而是中間間隔了一段時間才開始有效,這中間這段時間就是等待的時間。然后在地址有效時間Tco內把數據輸出出去。

注:灰色的部分是無效的地方,白色的地方才是有效的地方

3.4 外部存儲器

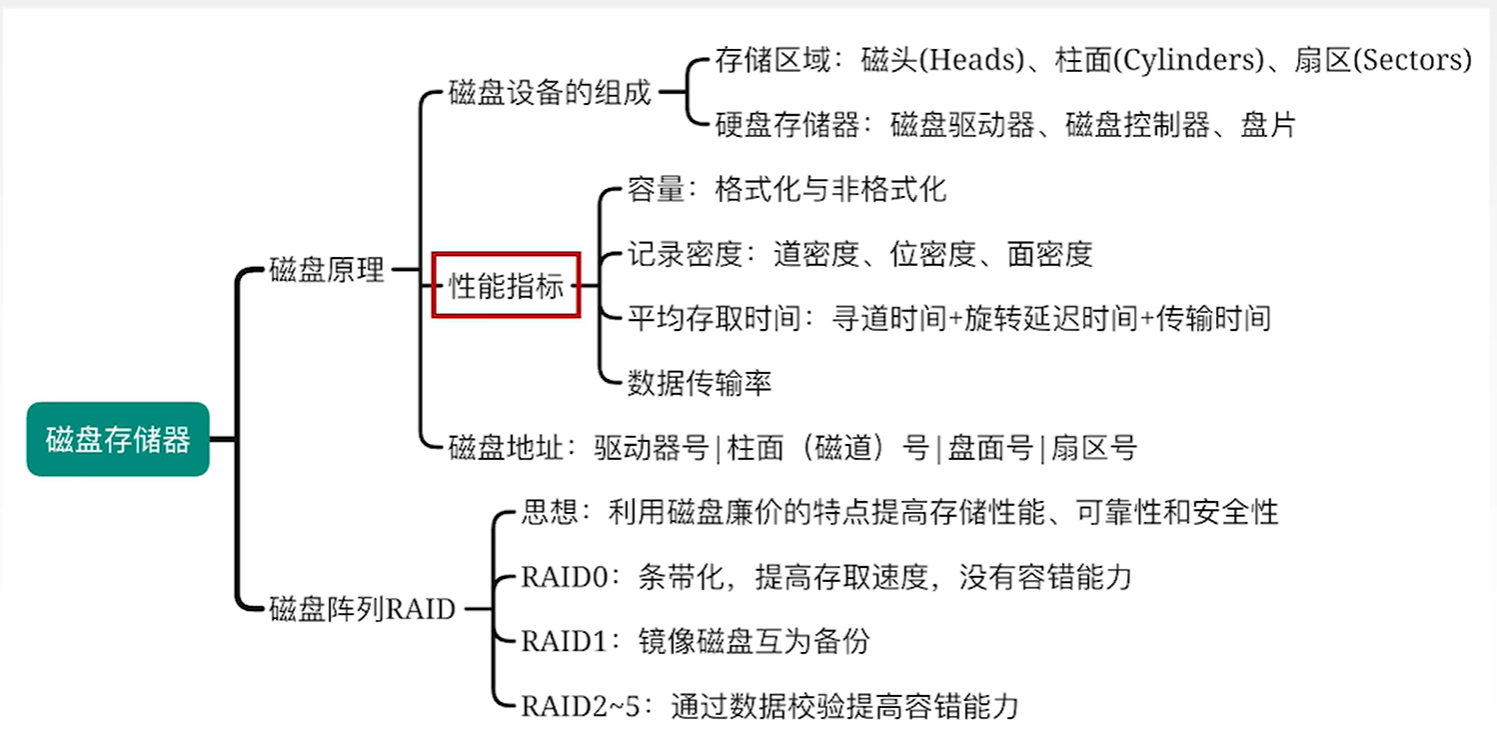

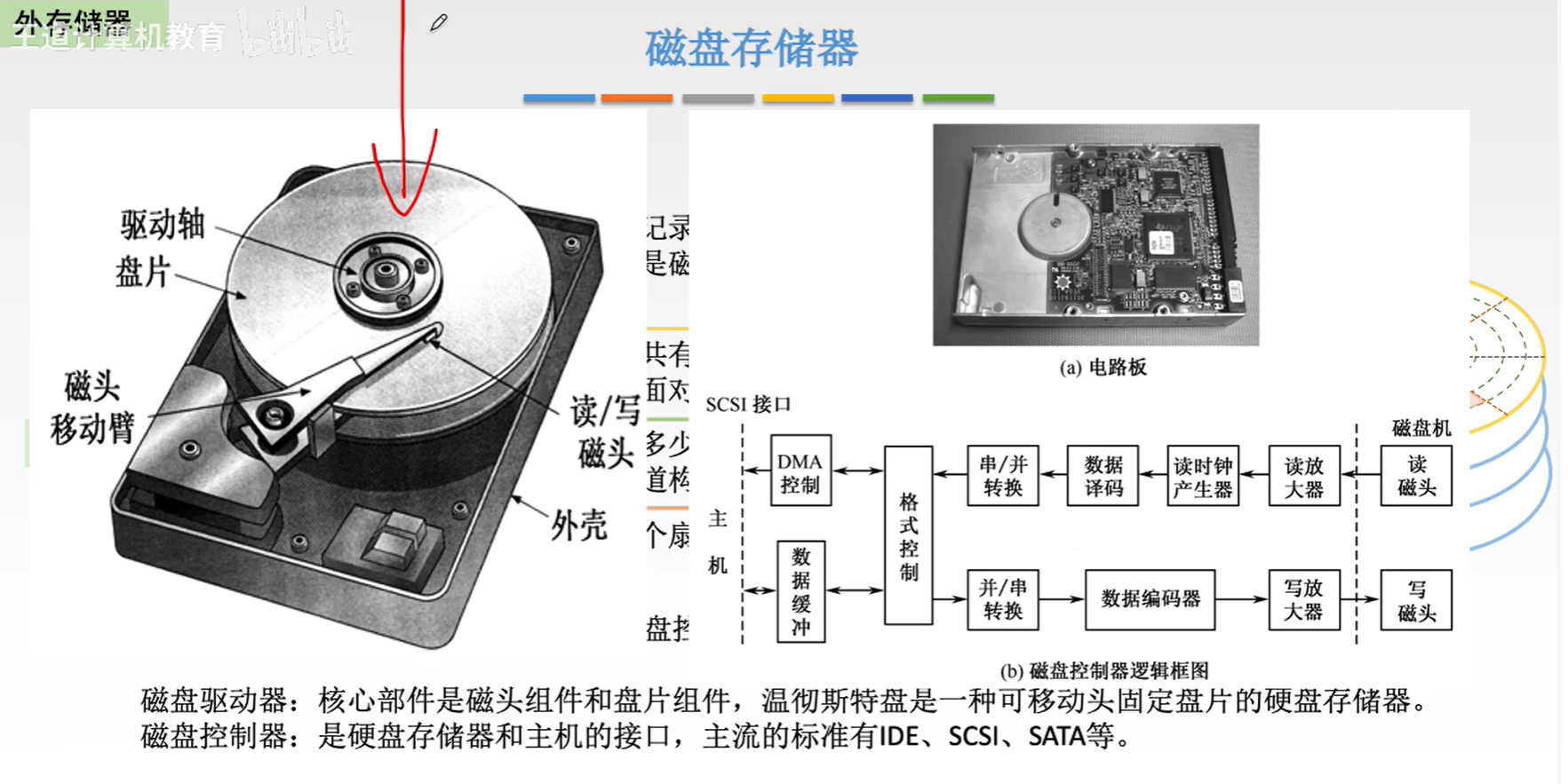

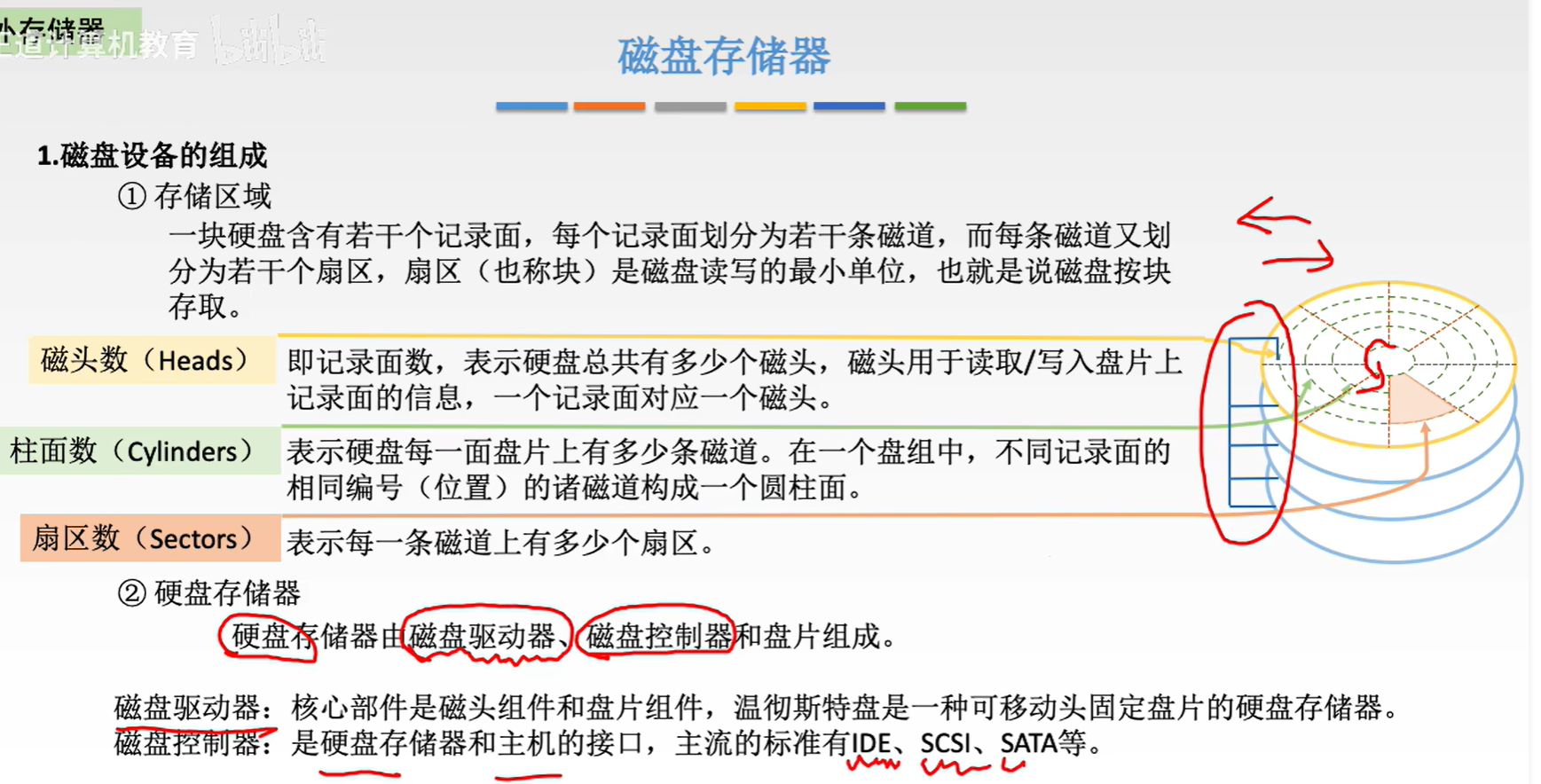

1. 磁盤存儲器

1、磁盤設備的組成

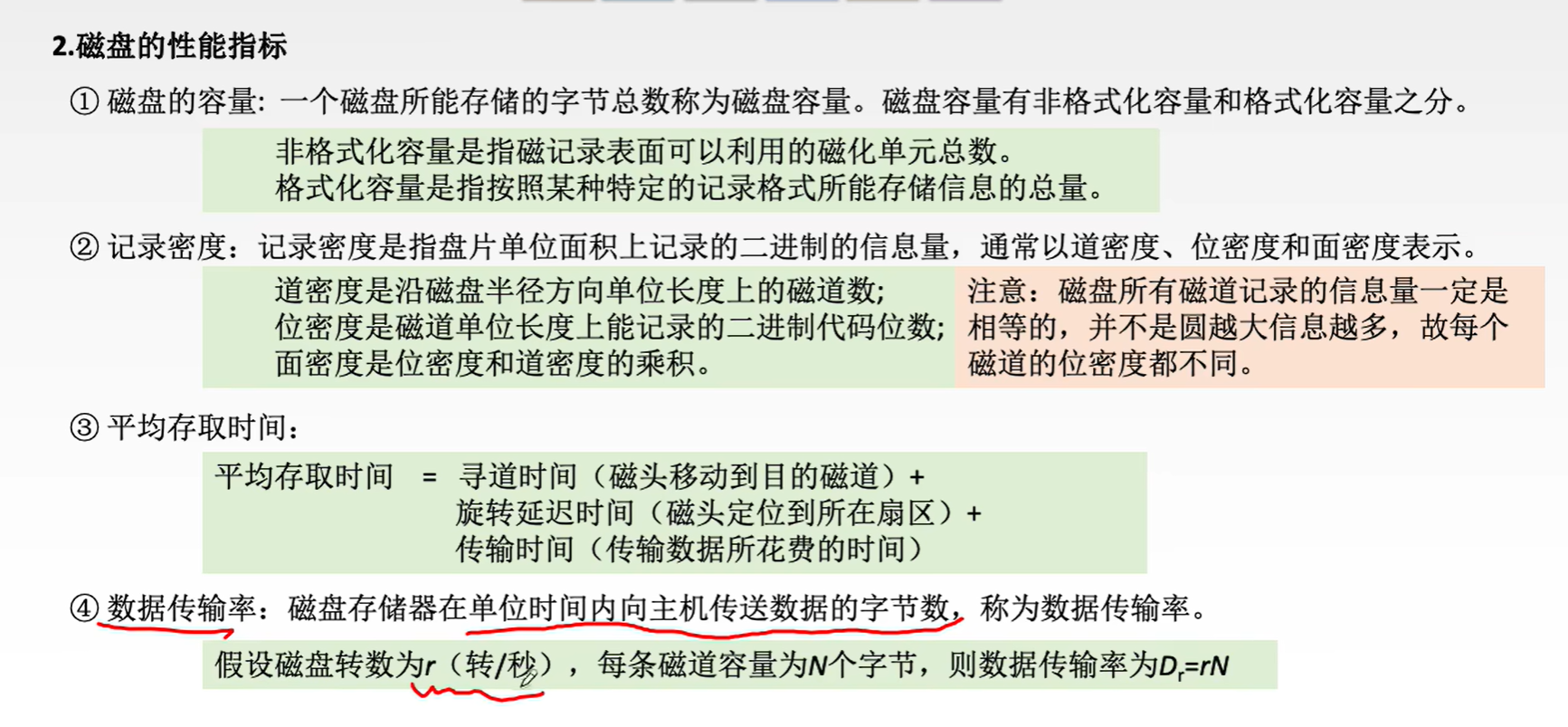

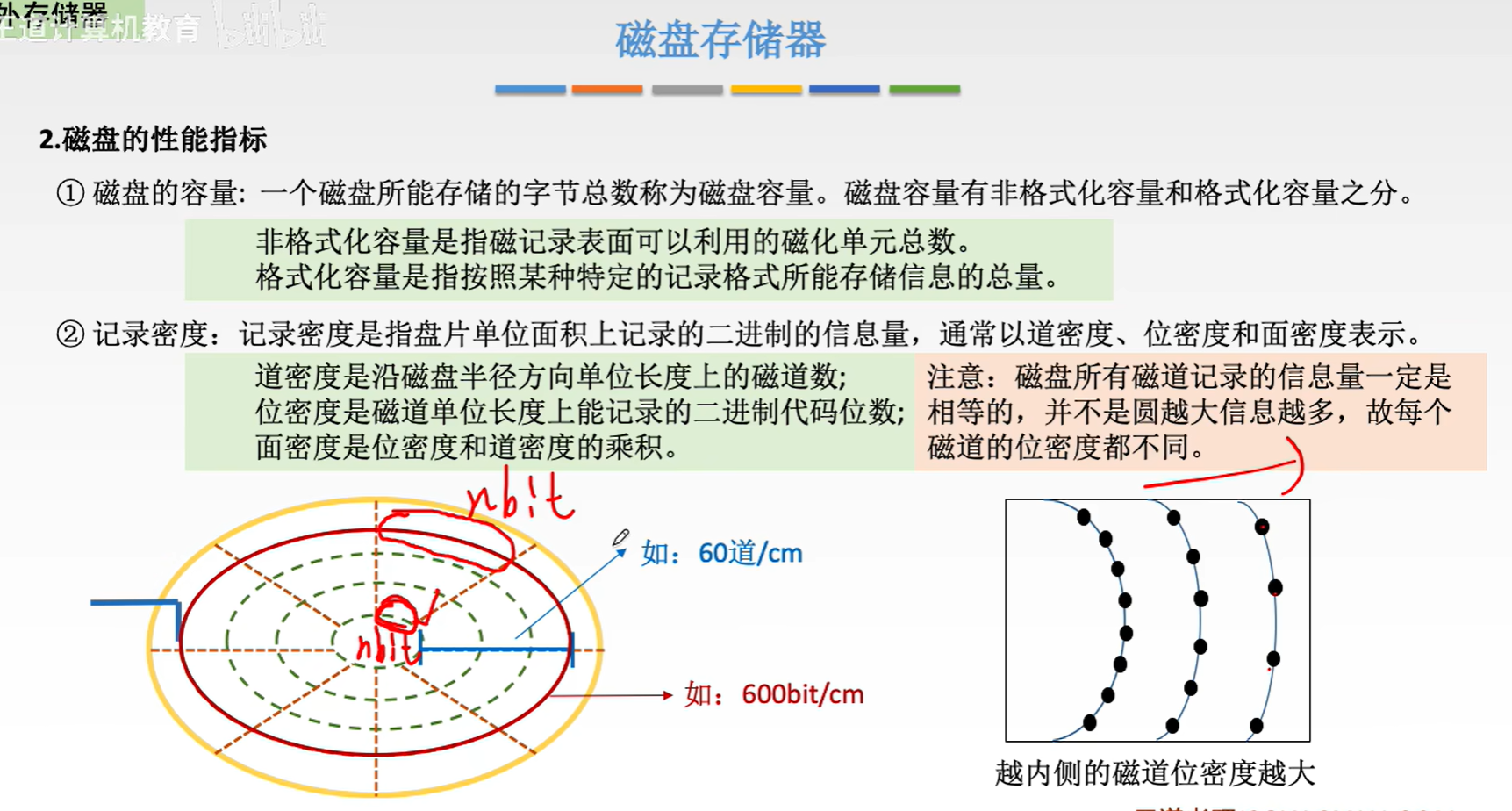

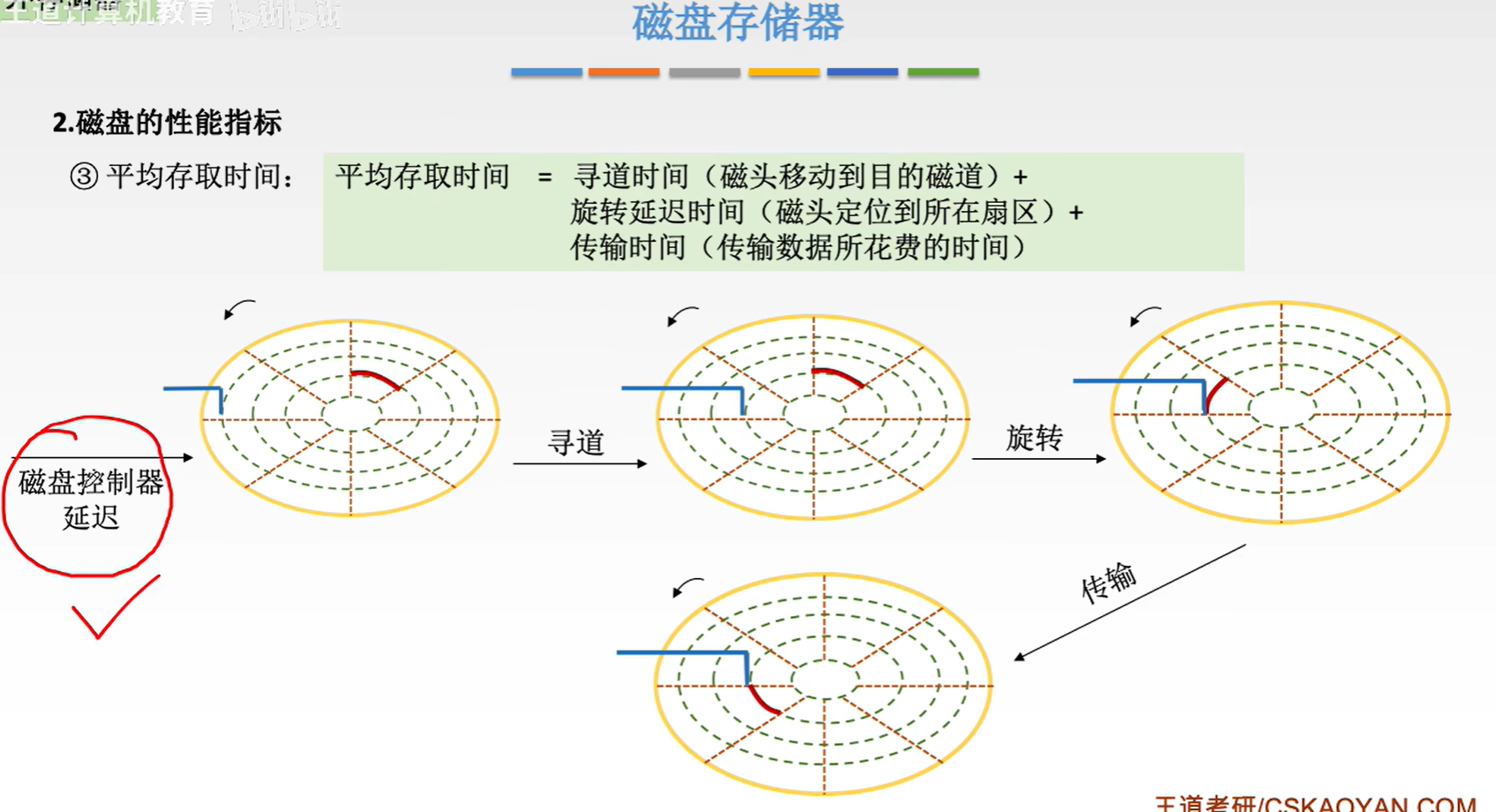

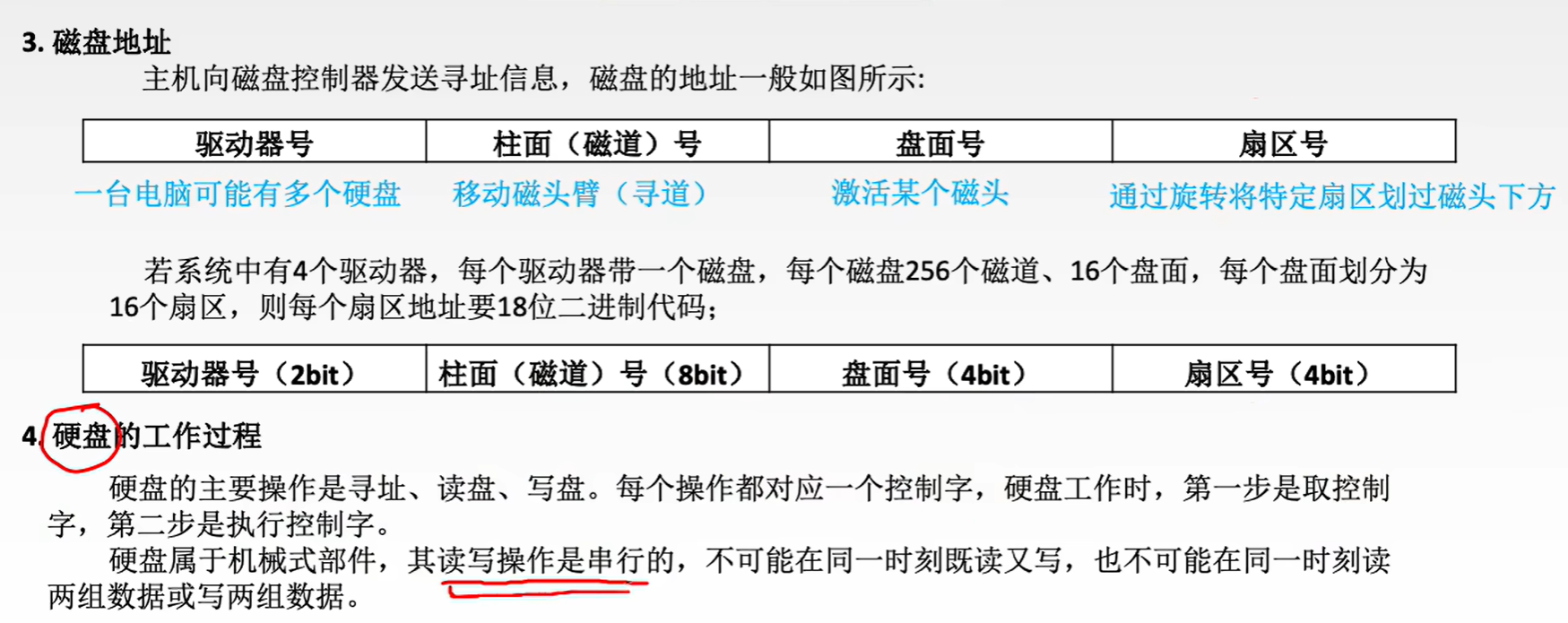

2、磁盤的性能指標

rN是一個理論最大值

格式化容量會有一部分容量用于別的用途,而非格式化容量是該磁盤的二進制bit存儲上限,所以格式化容量比非格式化容量要小

每個磁道記錄信息的信息量是相同的,并不是圓的半徑越大信息量越多

磁盤控制器延遲:(有的題有,有的題沒有)電子部件接收主機信號,然后向磁盤發出讀寫信號的時間

如果數據是并行傳給磁盤的,那在這之前還要經過一個串并行轉換電路才行,因為磁盤只能串行的工作

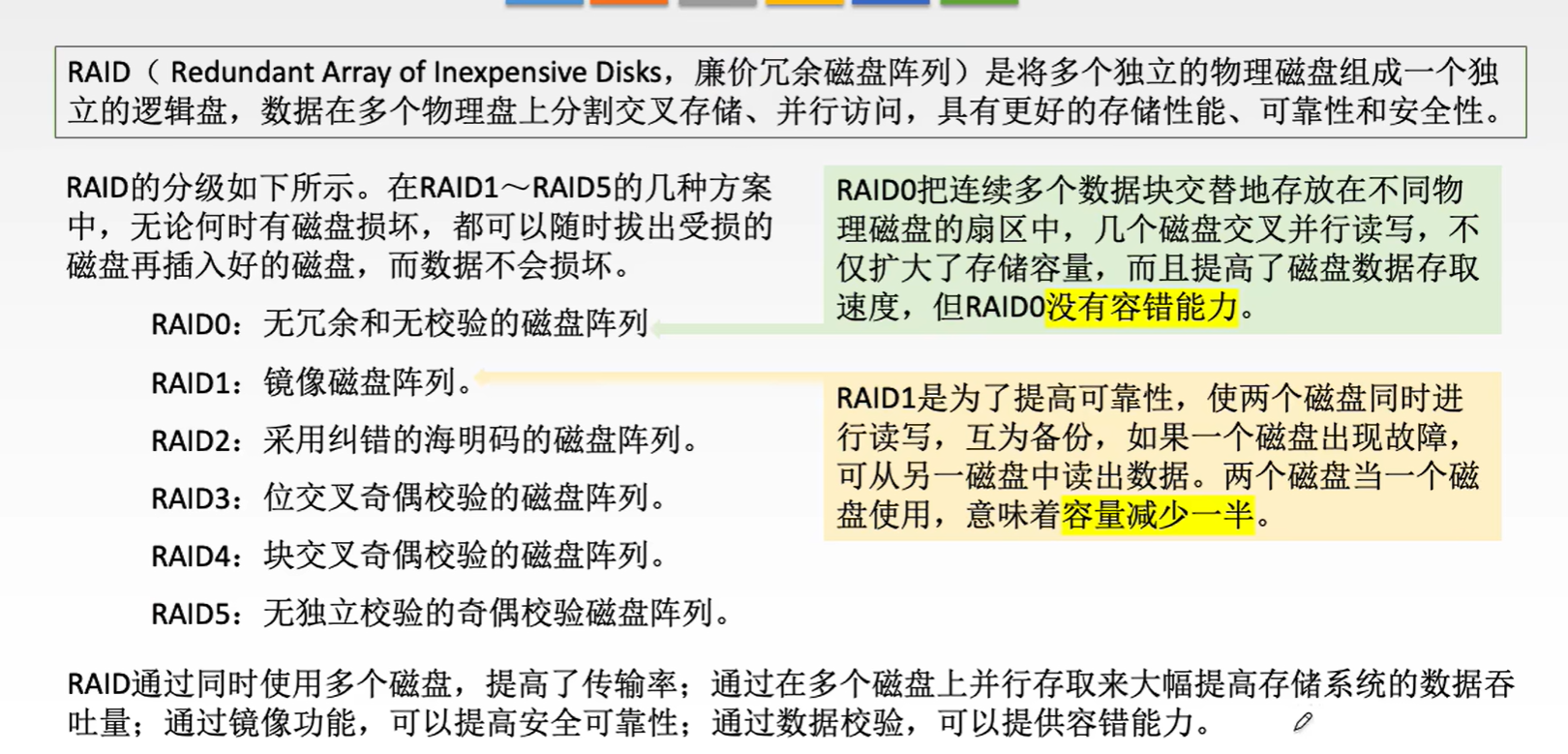

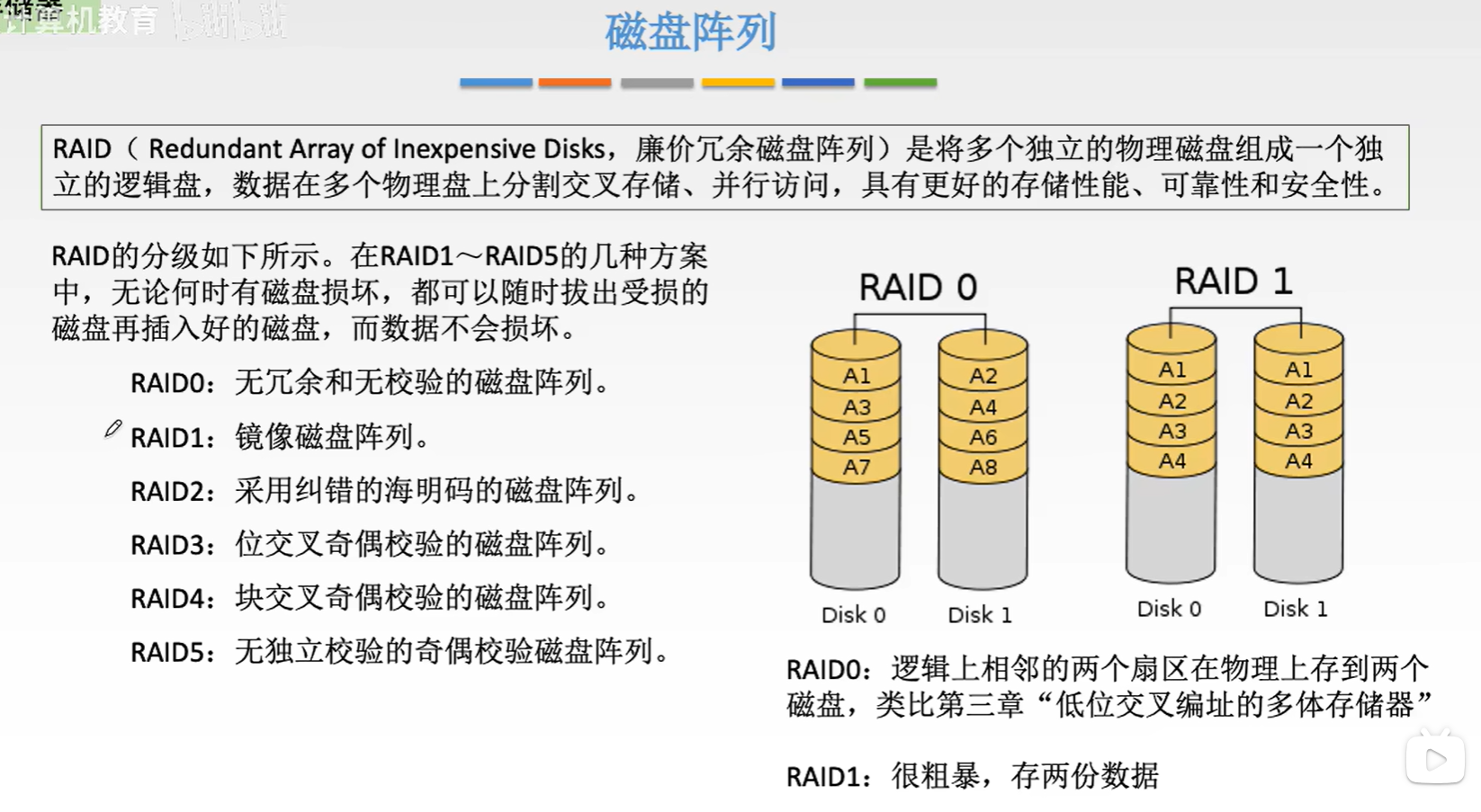

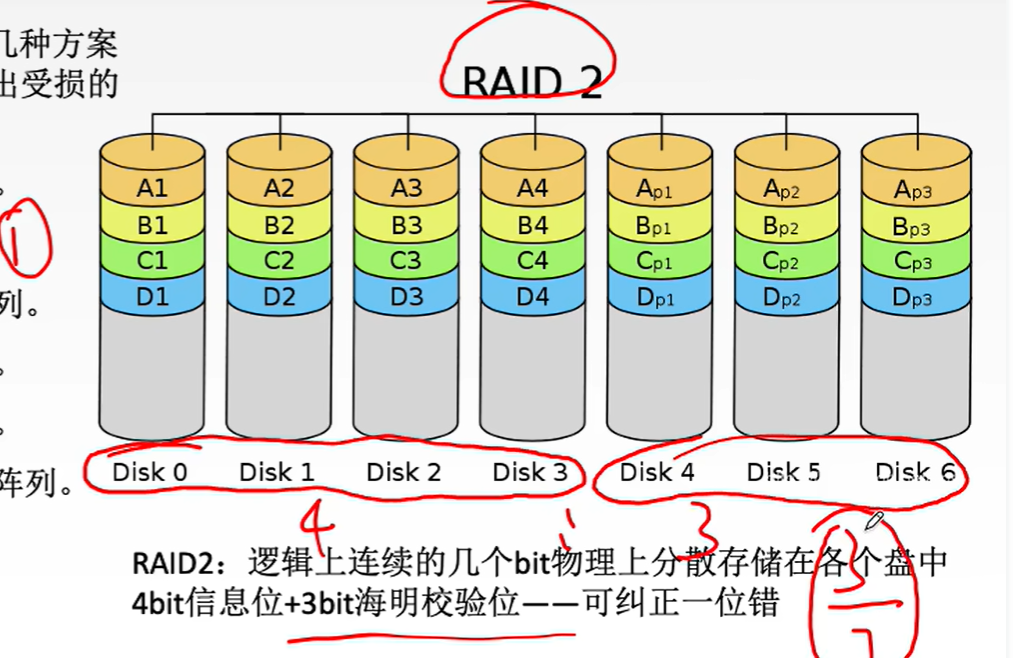

磁盤陣列

越后面的磁盤陣列信息冗余越少,安全性和可靠性越高,成本也越低

RAID0:就是RAID0是一個邏輯盤,是通過磁盤1和磁盤2映射而來,比如RAID0的第一個存儲單元的數據存放在磁盤1的第一個單元和磁盤2第一個單元,那我們讀取邏輯盤的時候就相當于有兩個磁盤同時為我們工作,可以實現并行訪問,提高速度

但如果物理磁盤有比特跳變之類的錯誤的話,RAID0也發現不了

RAID1:存了兩份一樣的數據,那就是有冗余了,兩份可以對比著看,有錯誤可以發現,所以是有校驗的。也實現了并行訪問,但是存儲空間有些浪費

0-3只存儲比特數據,4-6存儲校驗數據

這樣的話浪費的空間沒有RAID1那么多

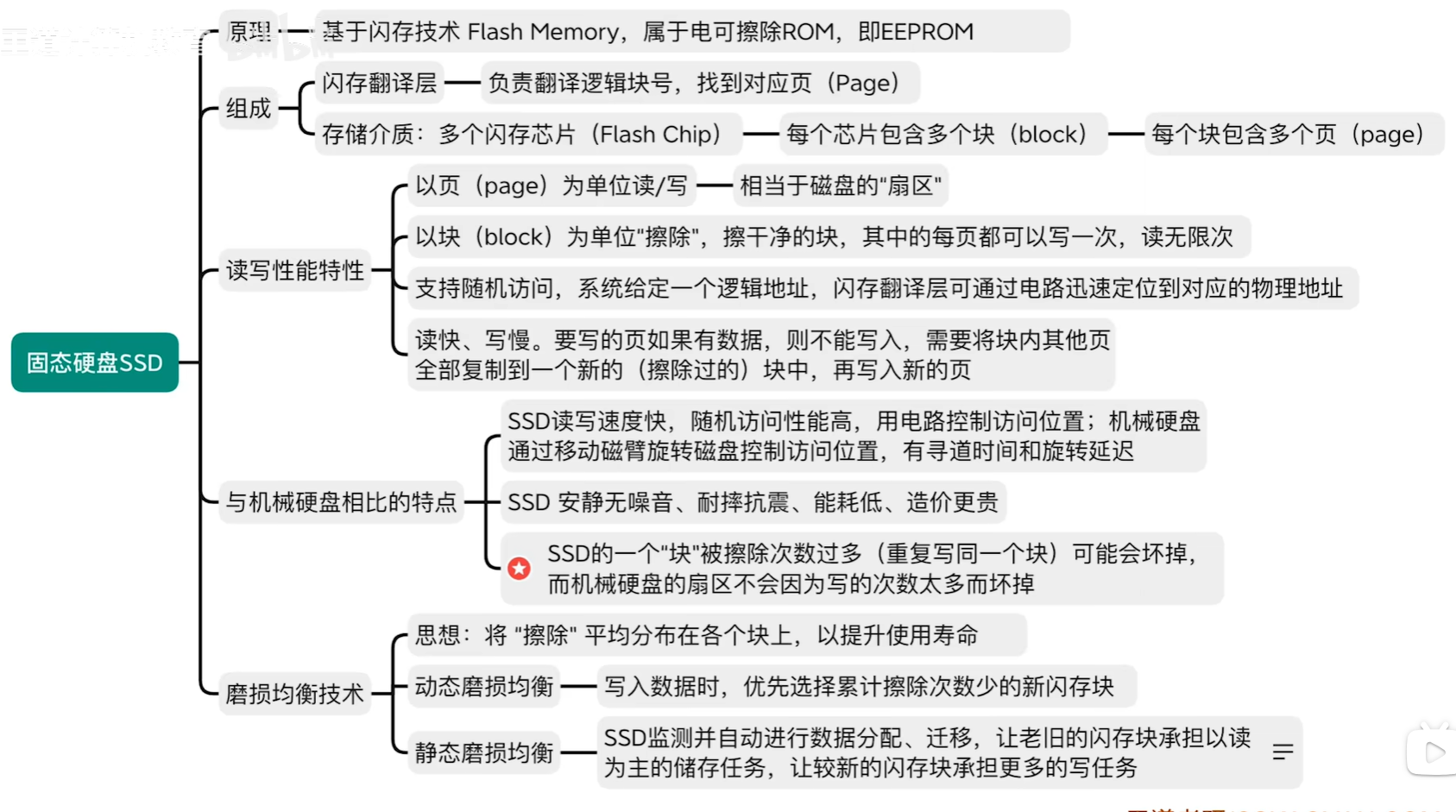

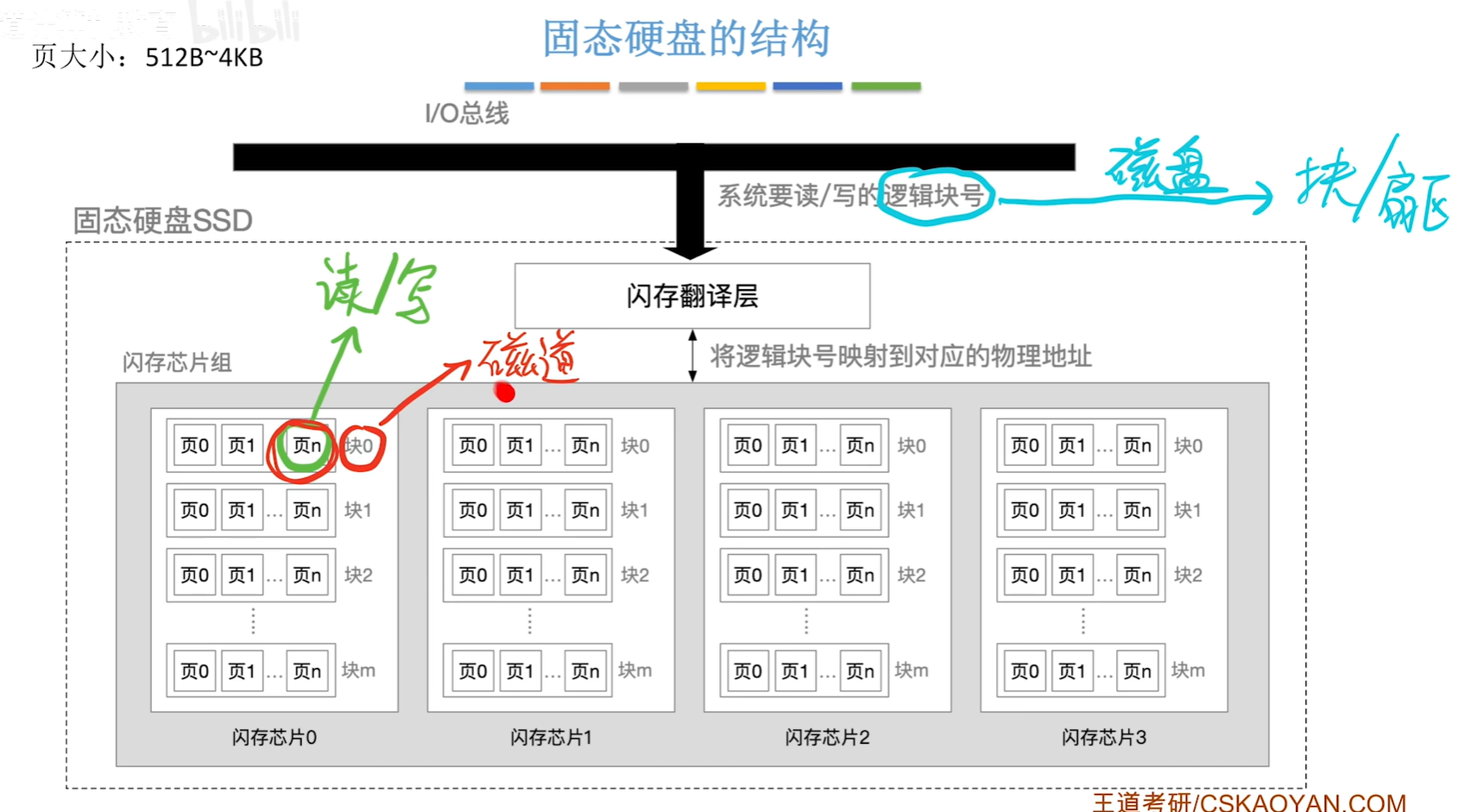

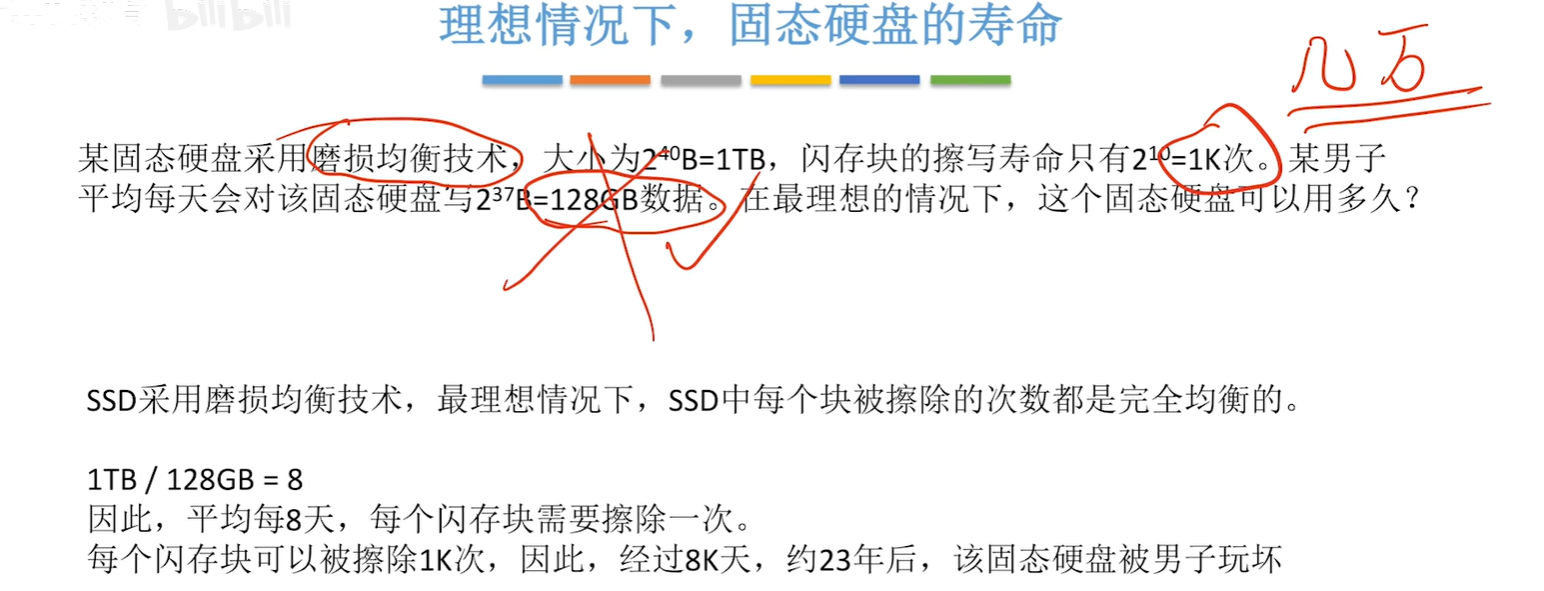

2. 固態硬盤SSD

閃存芯片可以分為很多塊,每個塊可以分為很多頁

每個塊相當于磁盤中的磁道,每個頁相當于磁盤中的塊/扇區

也就是說SSD的讀寫的基本單位是頁也不是塊

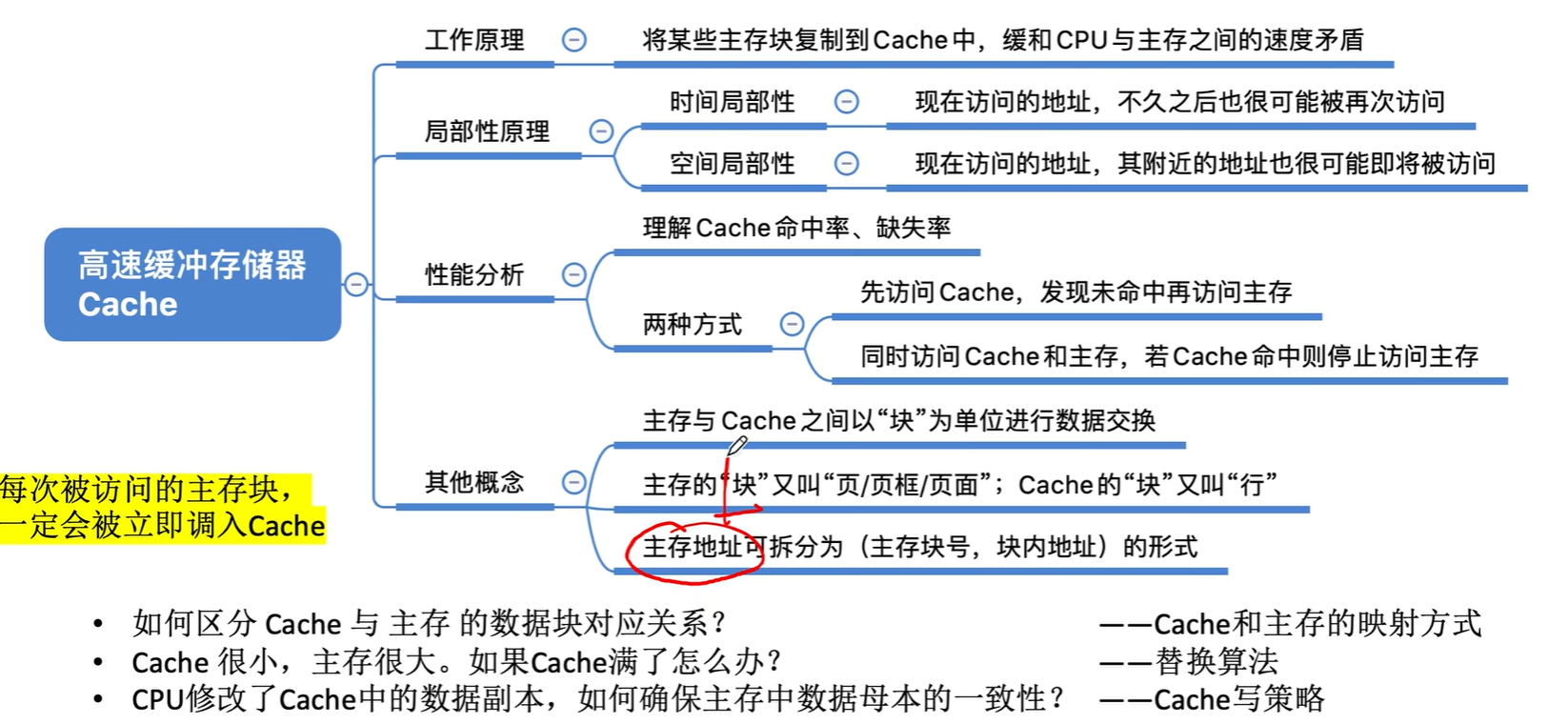

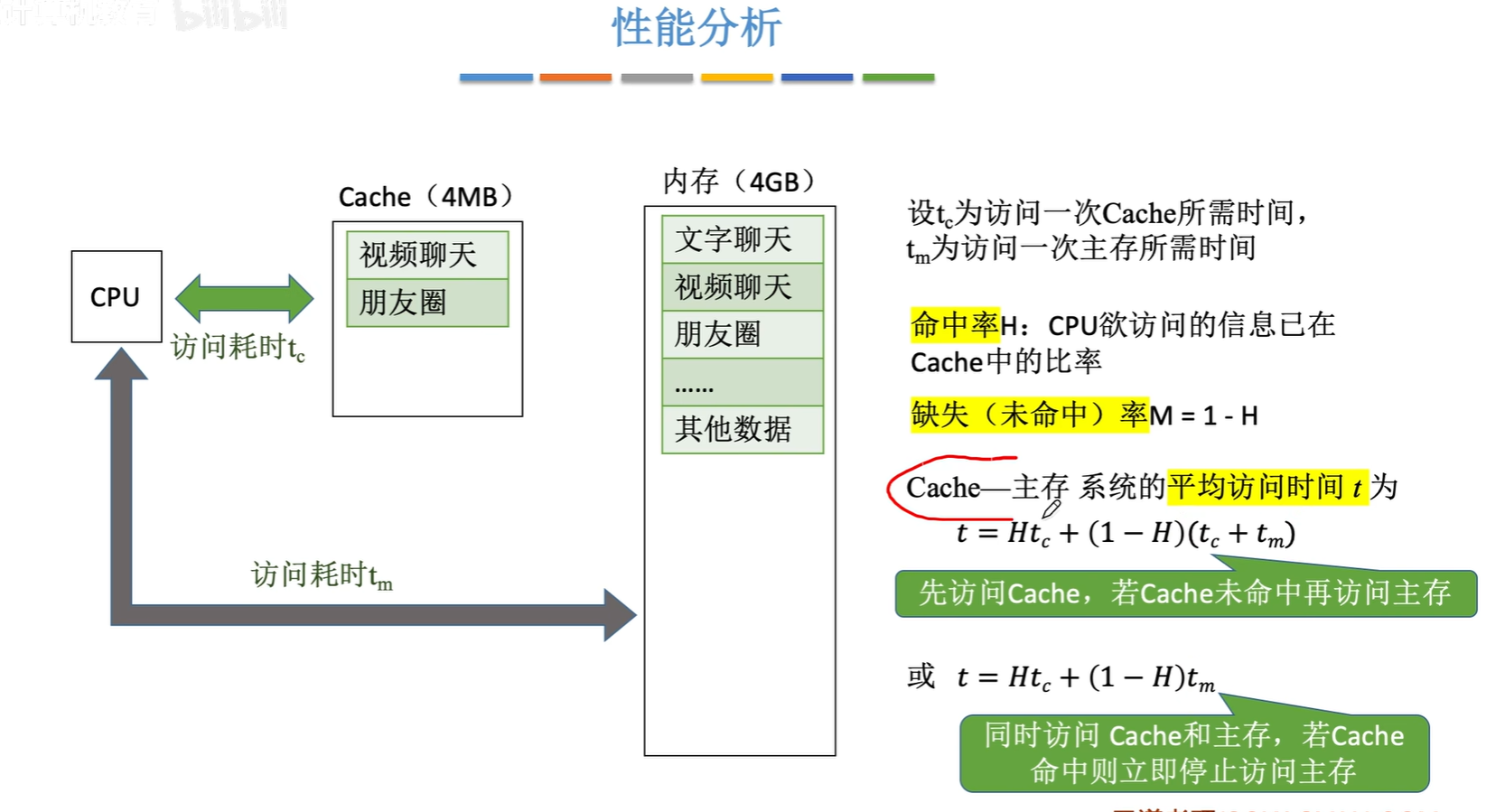

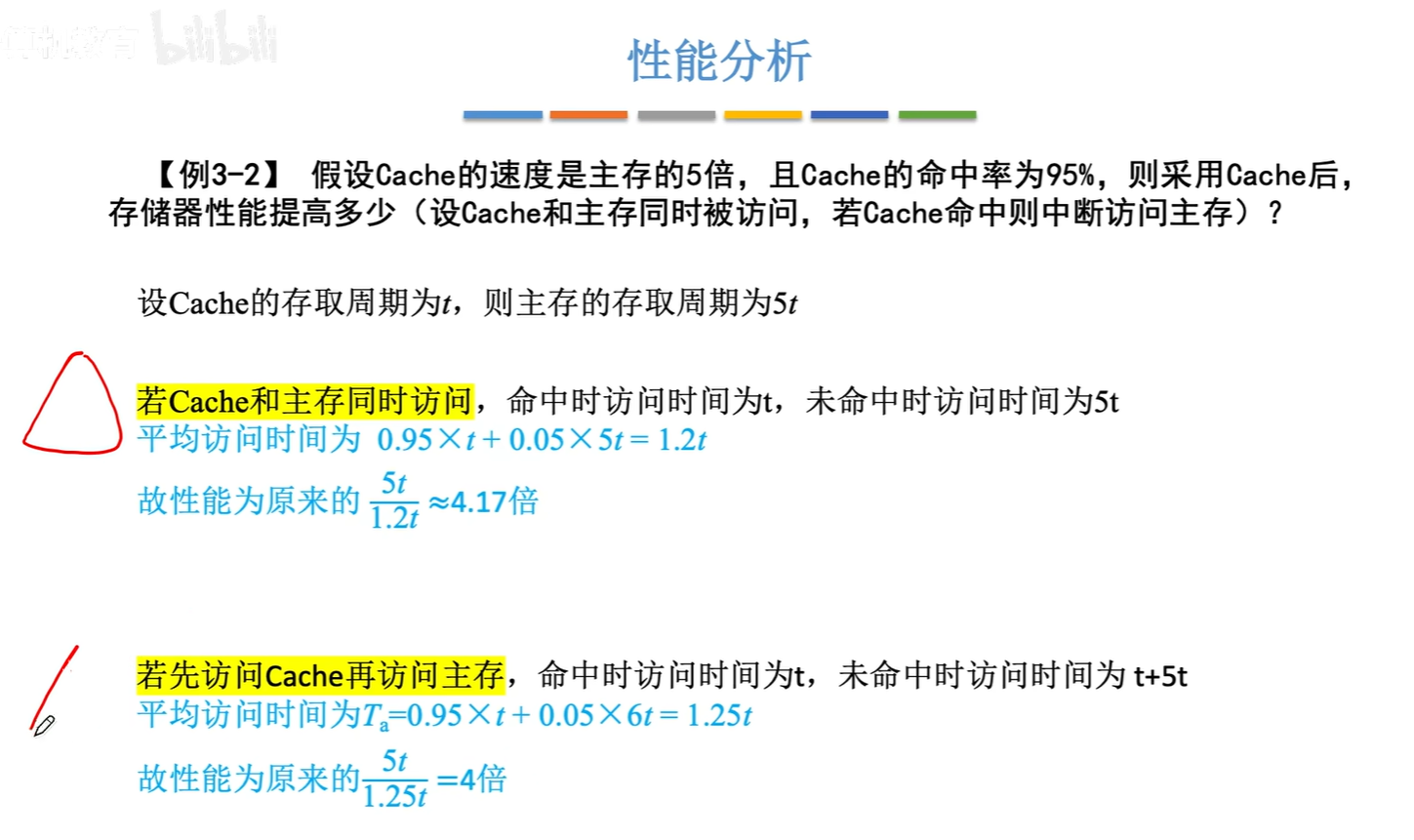

3.5 高速緩沖存儲器

1.Cache里面存儲的是主存的副本。所以如果Cache有40KB,主存有200MB

那存儲系統的容量還是200MB,而不是200MB+40KB,因為Cache存的僅僅是副本而已

2.Cache訪問失效的時候,通常不僅要像CPU傳遞消息,還要將信息寫入Cache,傳遞消息的數據寬度是字,寫入信息的數據寬度是塊。

CPU與cache或者主存信息信息交互的單位是字,而Cache與主存間信息交互的單位是塊

3.Cache的功能全部由硬件實現

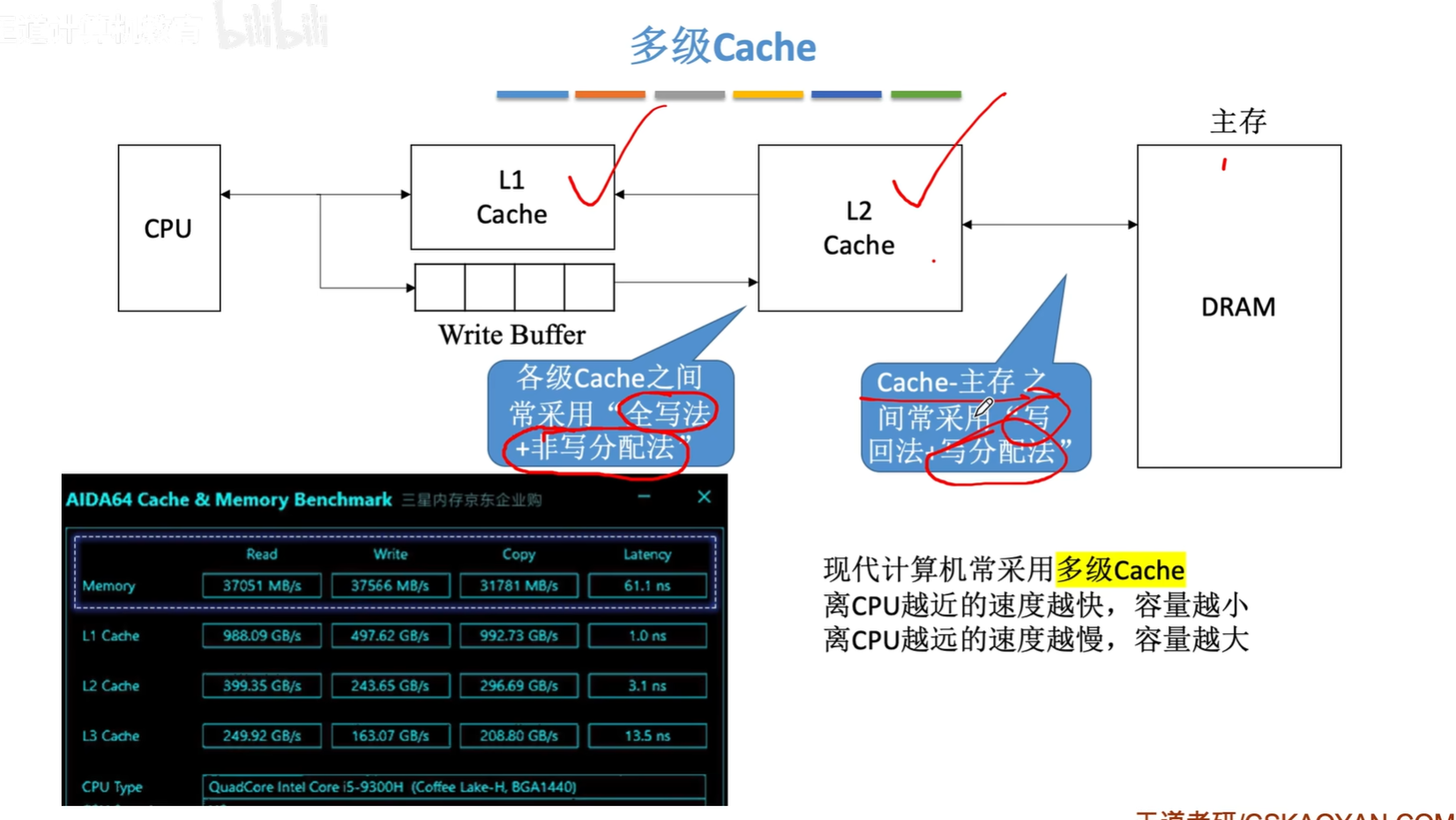

4.多級cache中,算缺失率的時候,只需要看到最低一級的cache的時候還有多少沒有命中

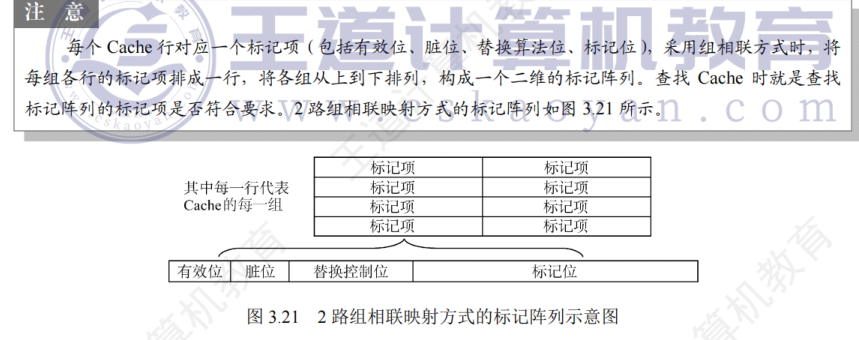

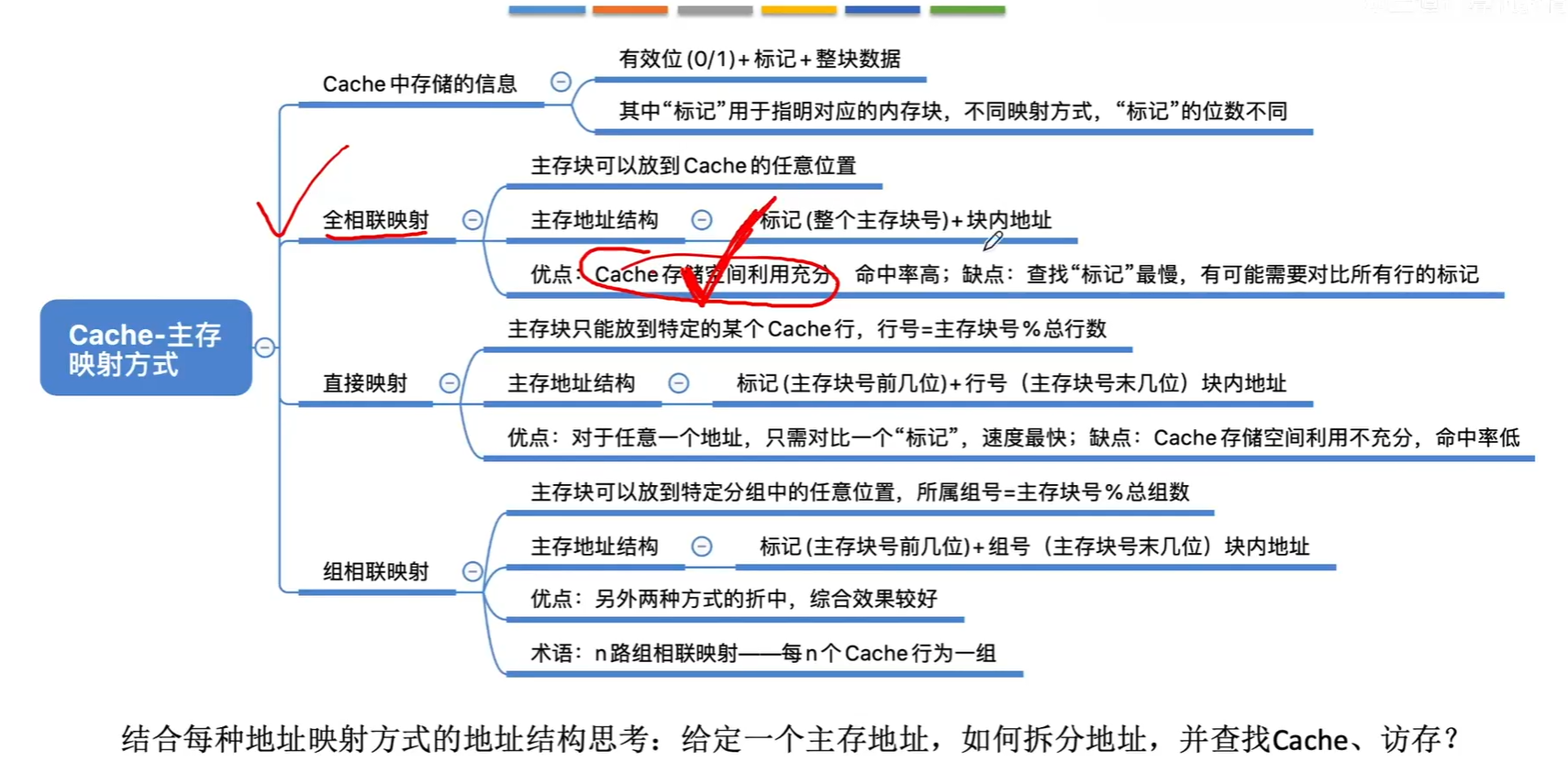

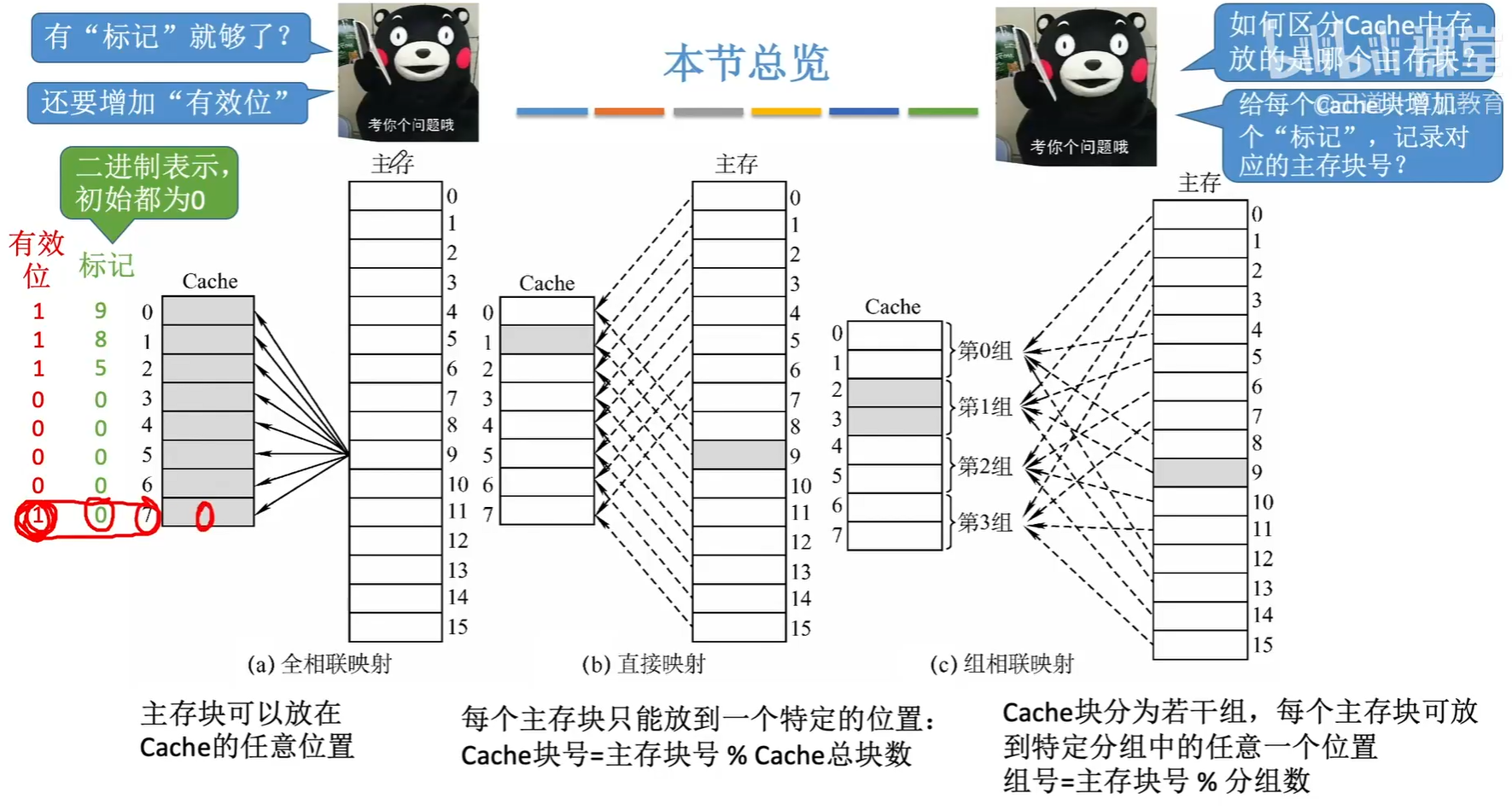

5.Cache中地址映射表的大小就是(有效位+標記位)*塊數

6.邏輯地址的頁和物理地址的塊對應,映射的話就是邏輯的頁映射到物理的塊上面去

7.對于有高速緩存,主存,硬盤構成的三級存儲體系,CPU直接根據主存物理地址進行訪問

8.

標記位前面可能還有有效位、臟位、替換控制位,通過這四個位來算Cache除了數據部分還有得有多少的容量

不管什么方法都會有有效位,寫回法一定會有臟a位。替換控制位很少見

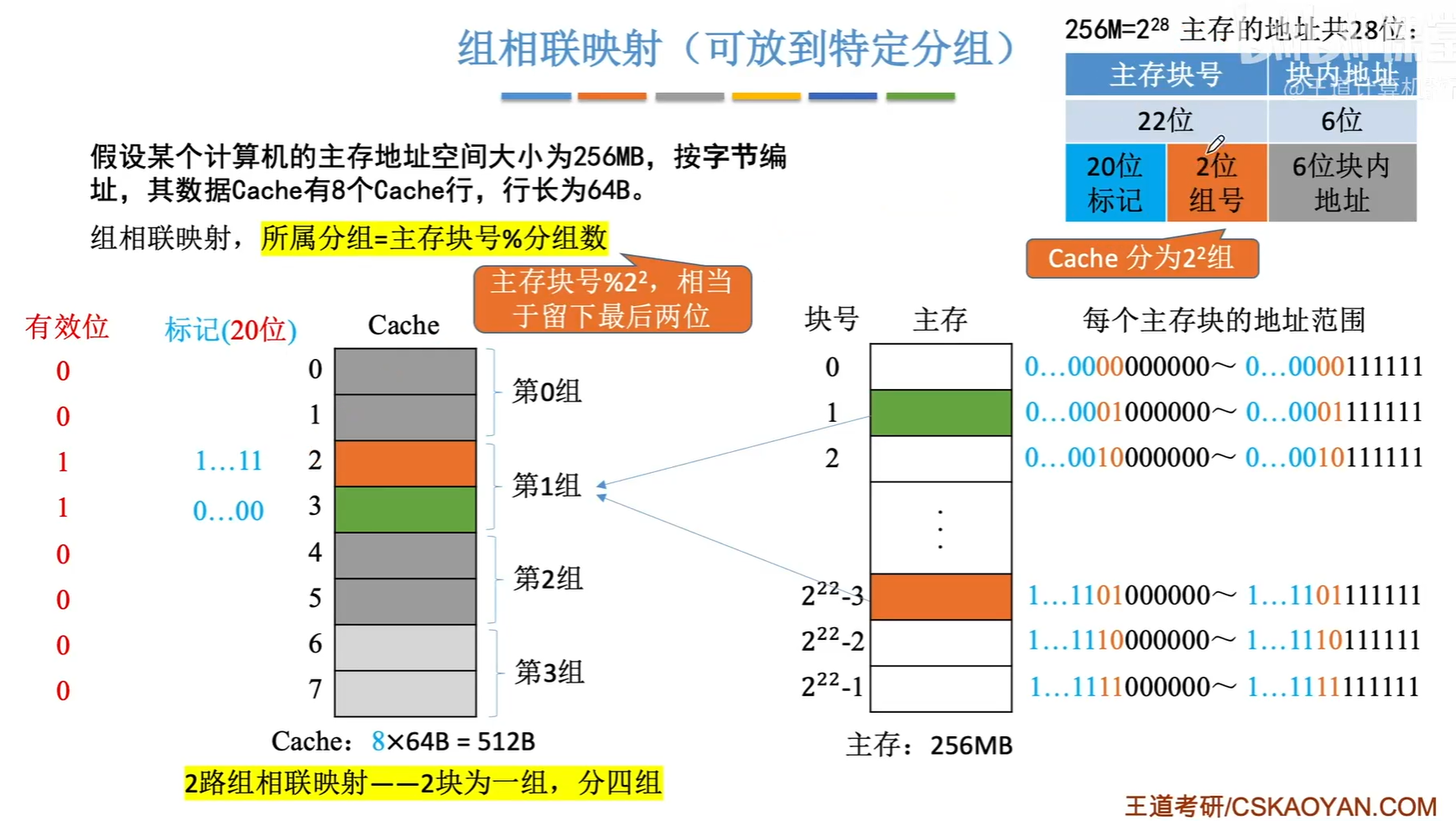

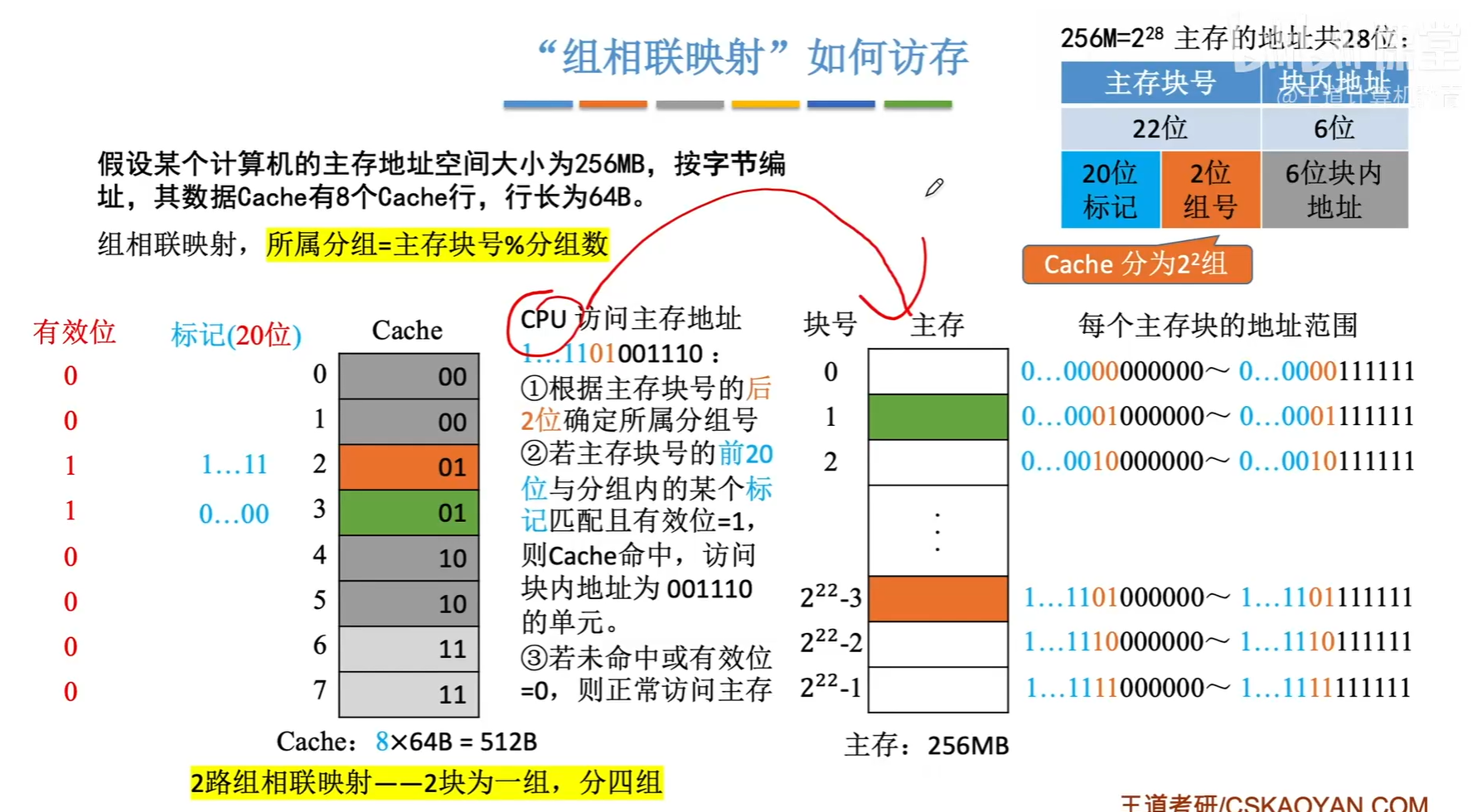

9.組相聯映射中,是幾路組相聯就有幾個比較器。這個比較器是來看給出的主存地址具體在組內的哪個塊

所以 比較器里面存的就是標記位(不包含組號),因為一組有 的塊數和路數相同,所以比較器的個數就是和路數相同的,一共要比較的次數也和路數一樣

1.基本原理

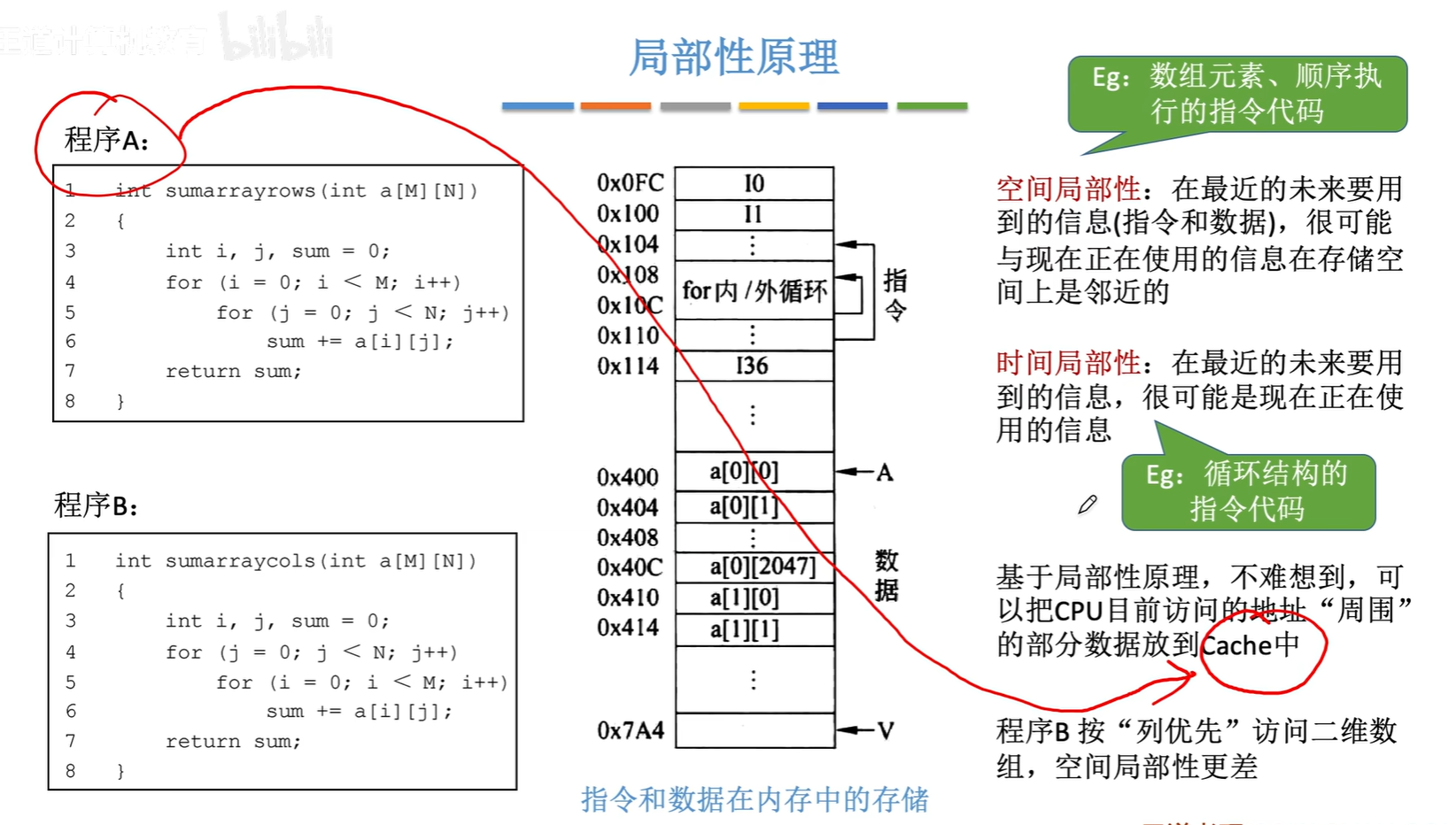

按照行優先存儲的,如果循環體按照列優先進行訪問的話,那么會比按照行優先進行訪問的慢很多,因為按照行優先會有很多地址可以映射到cache中

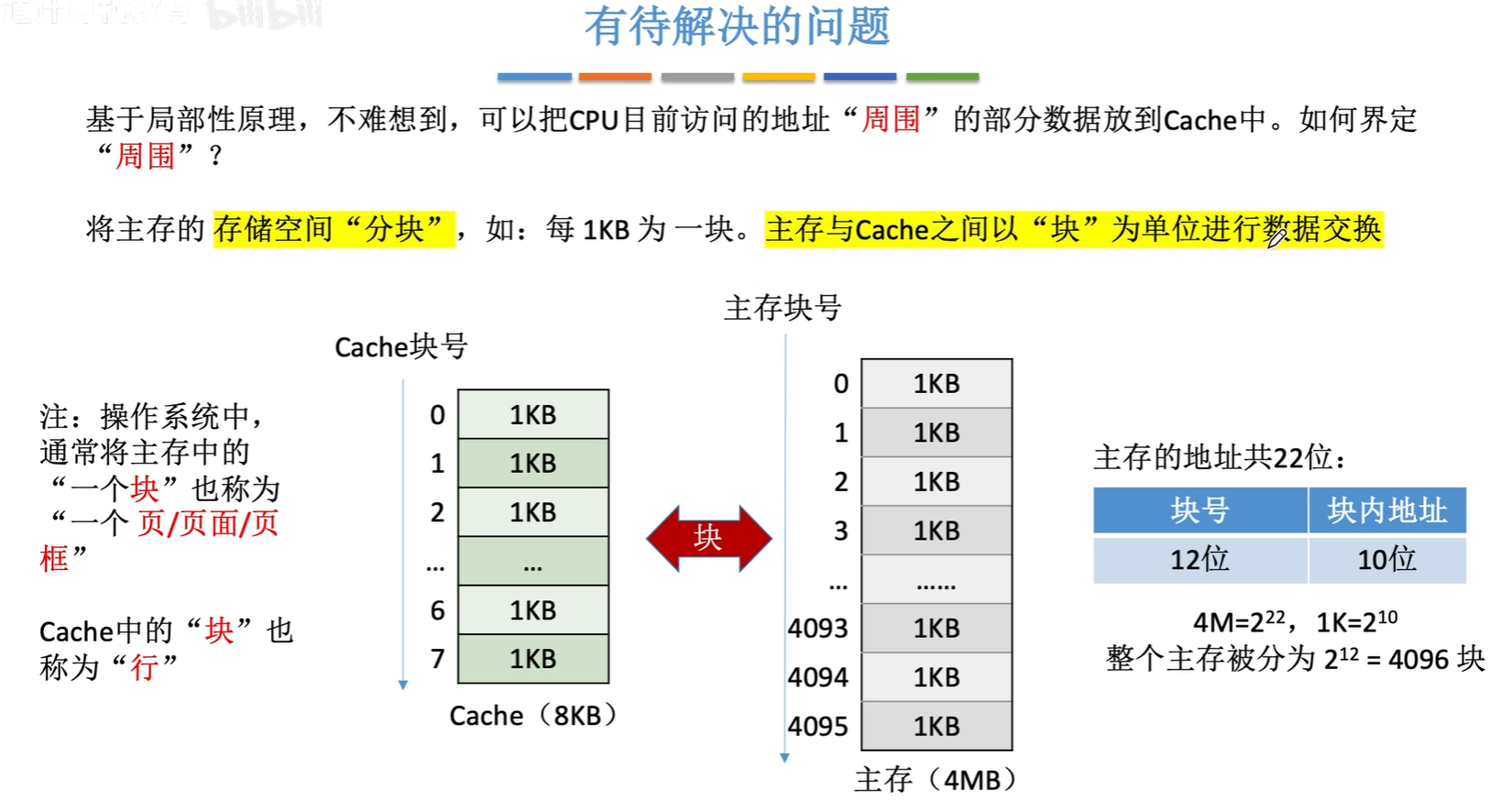

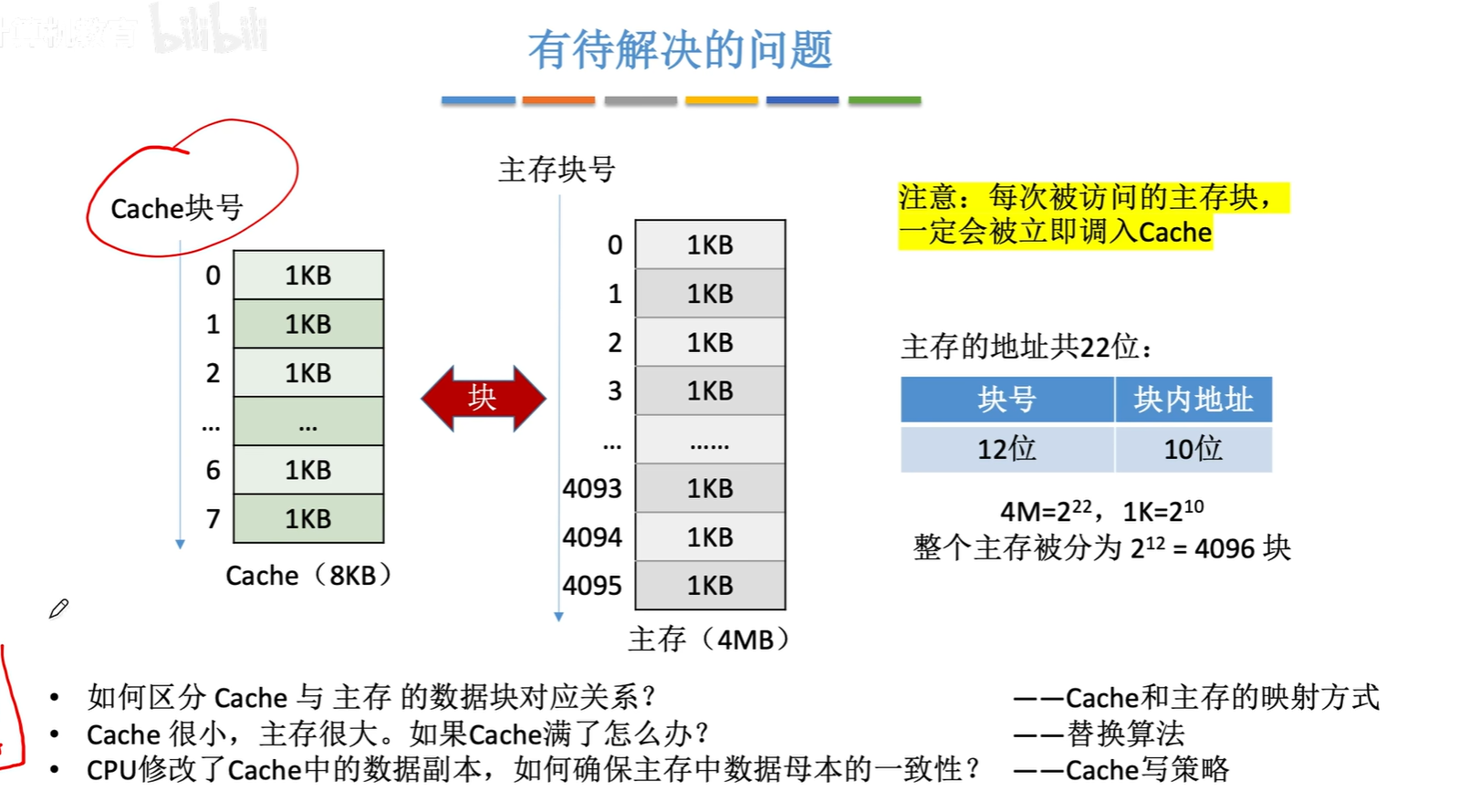

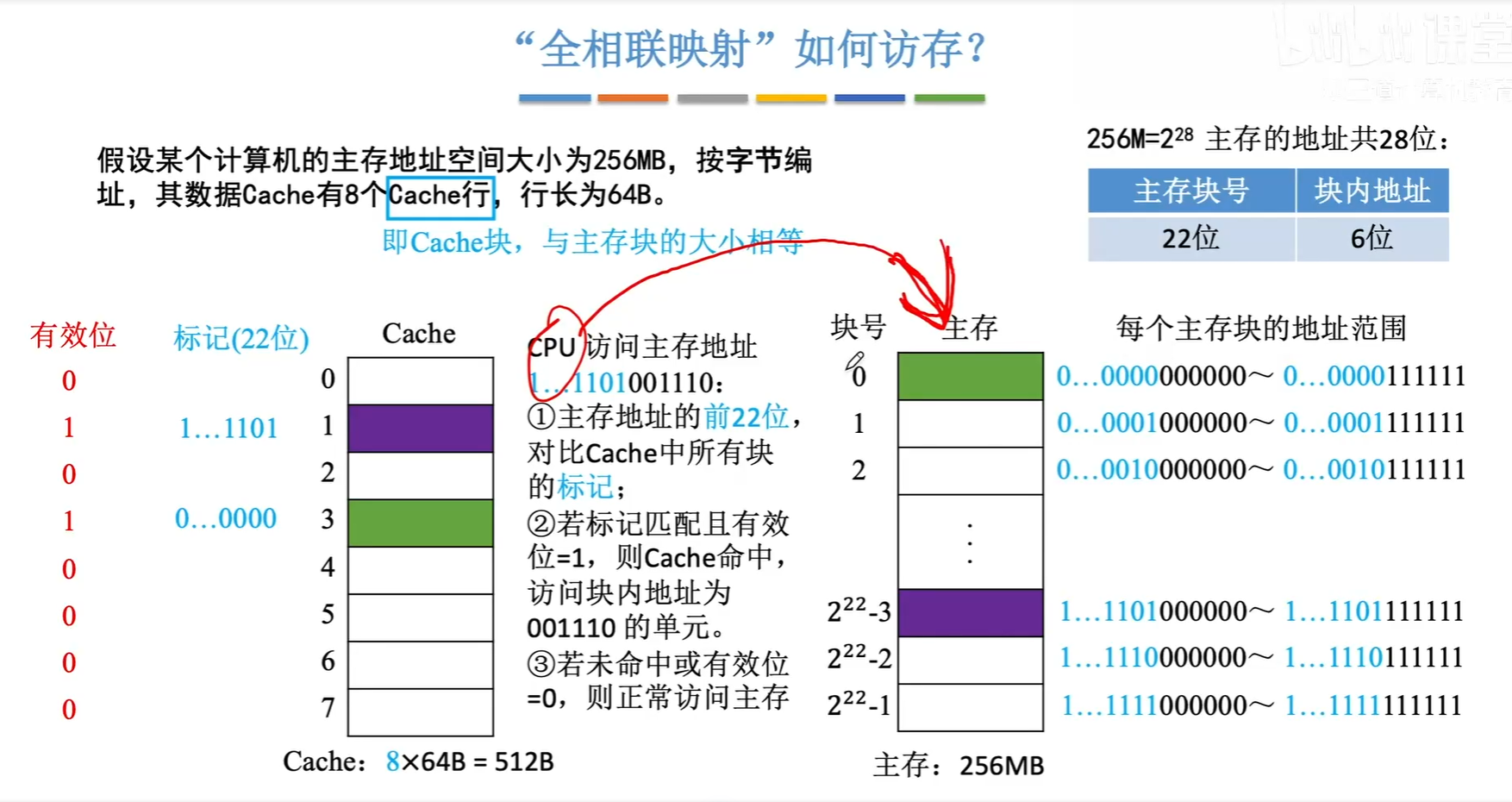

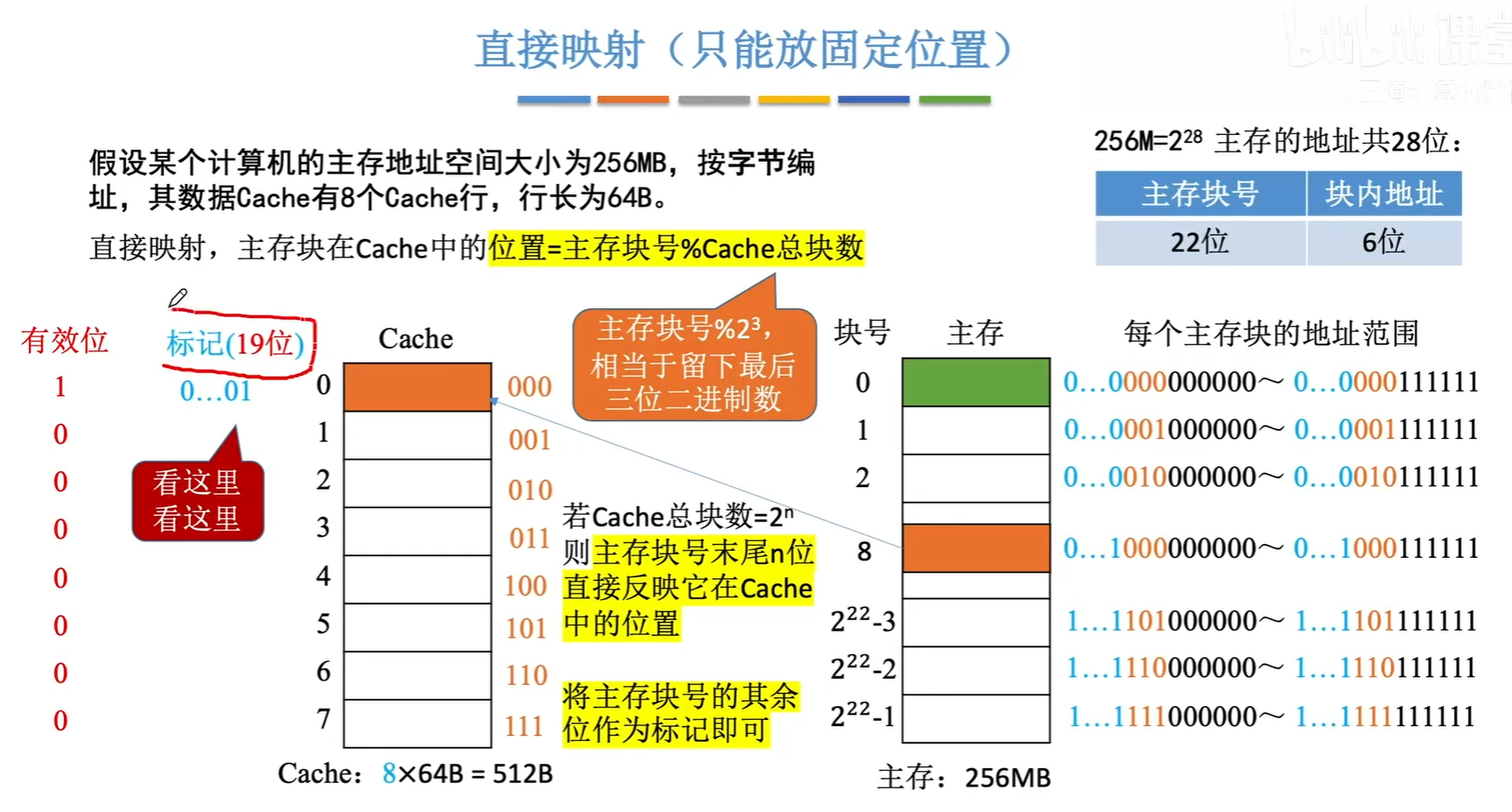

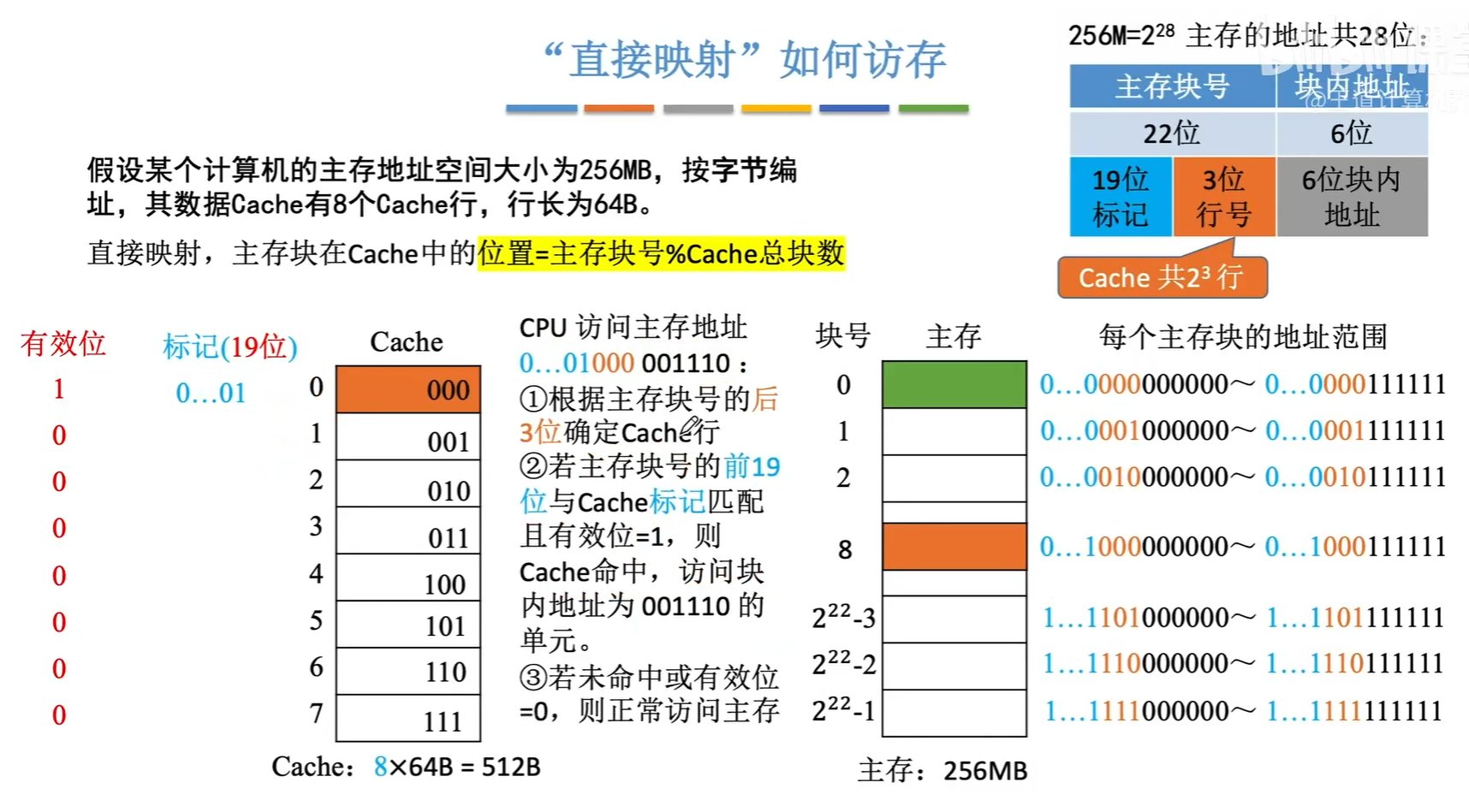

2.Cache和主存間的映射方式

其實就是主存容量是Cache的多少倍,如果主存容量是cache的4096=212倍,那么標記位數就是 12

也就是得標記4096個位置才行

比如圖中的標記位數就是 256MB/(8*64B)=219次

有效位和標記位組成地址映射表,其大小就是(有效位數+標記位數)* cache塊數

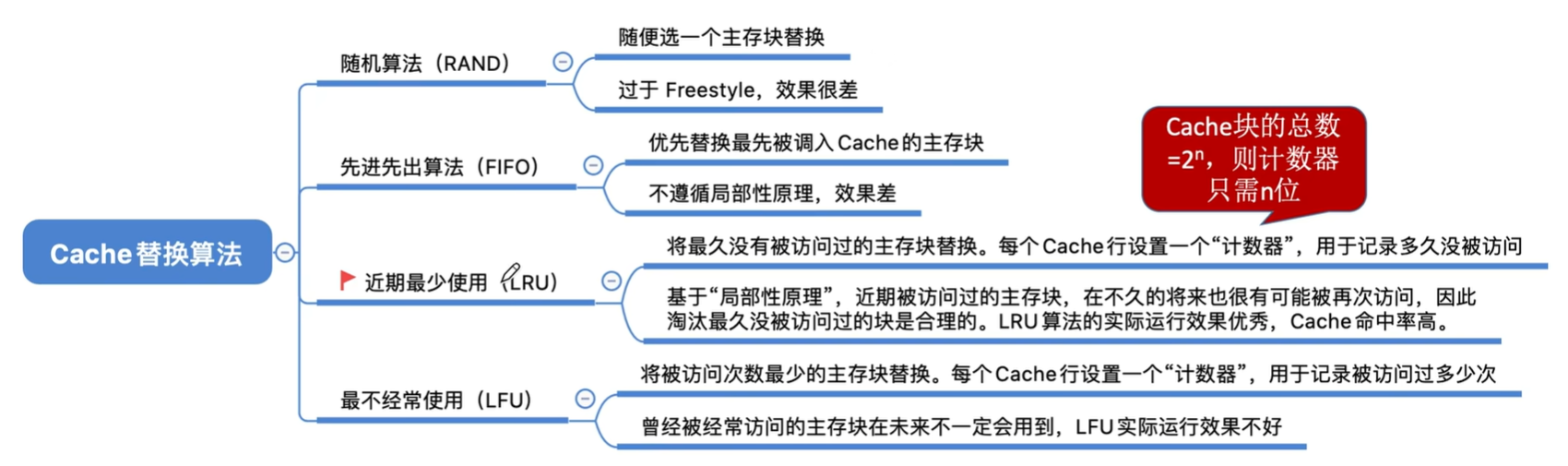

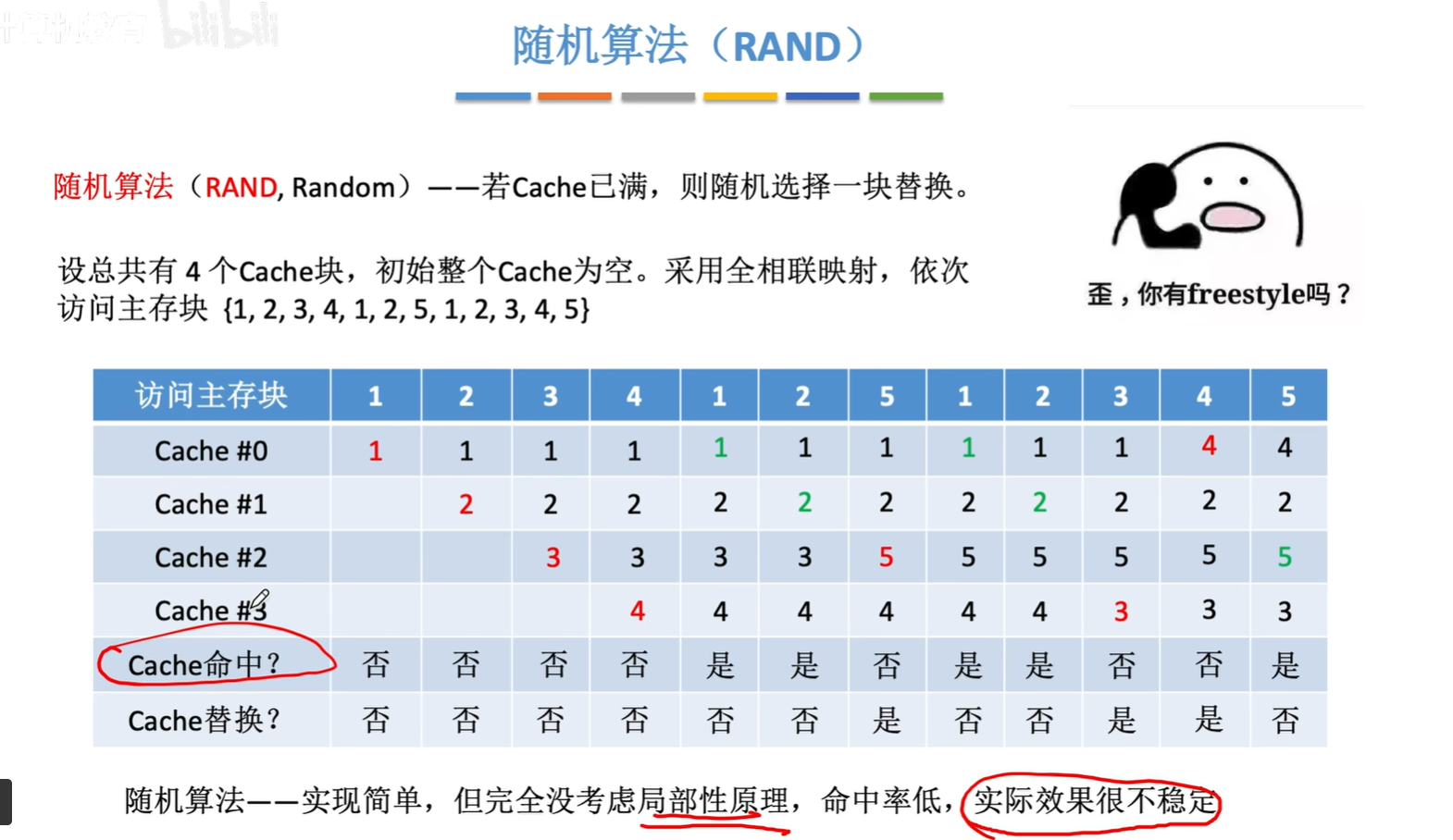

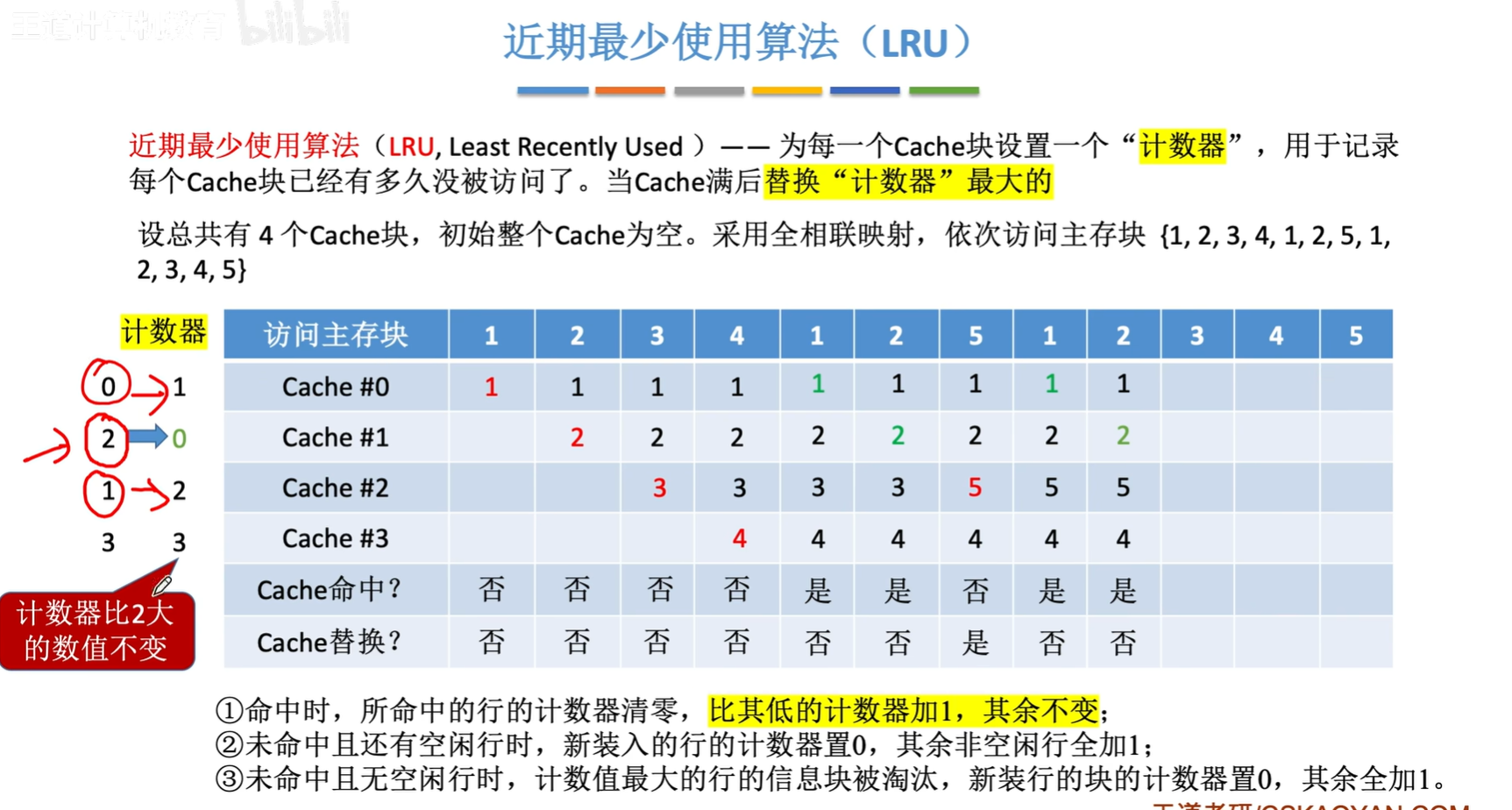

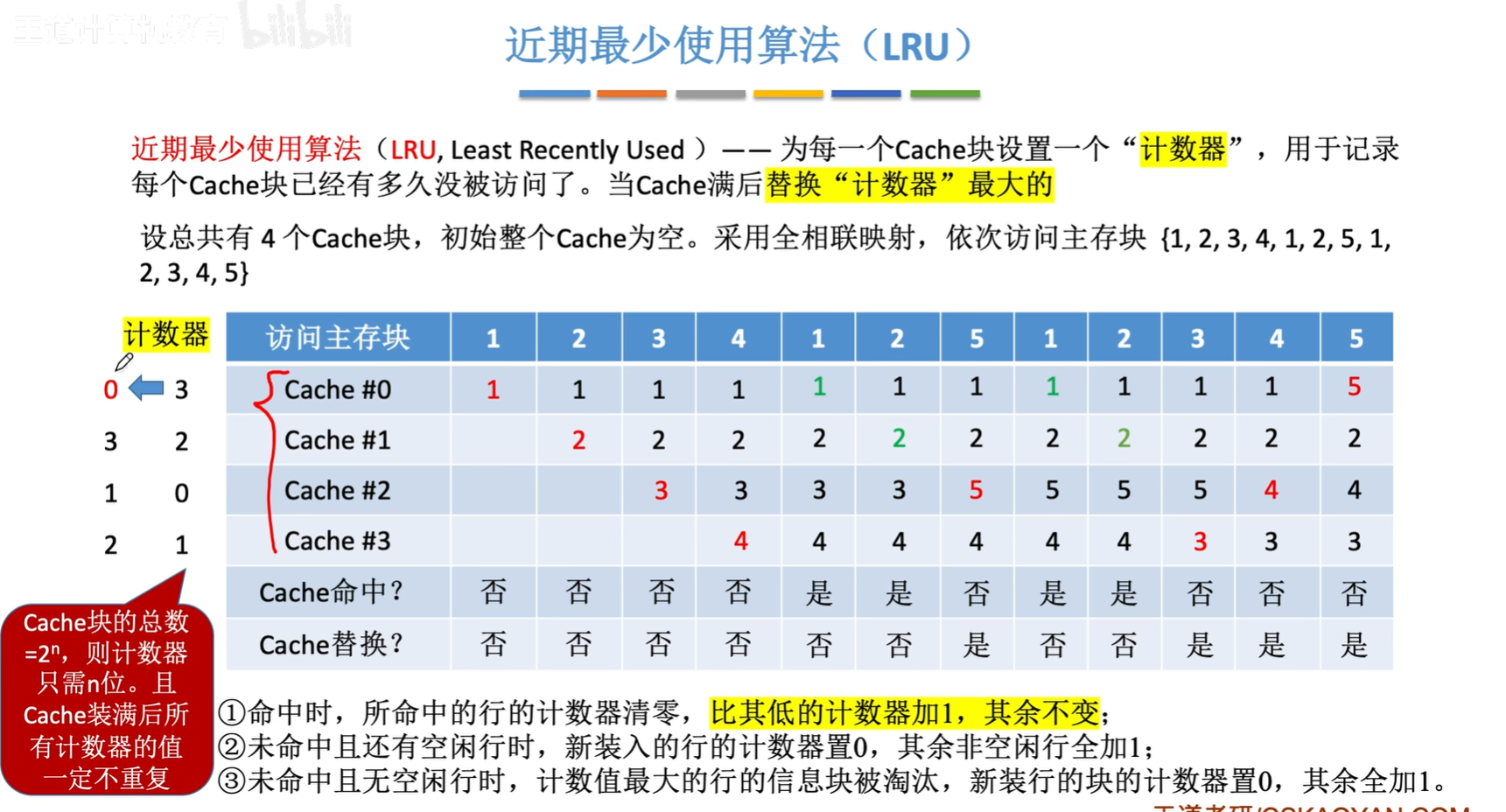

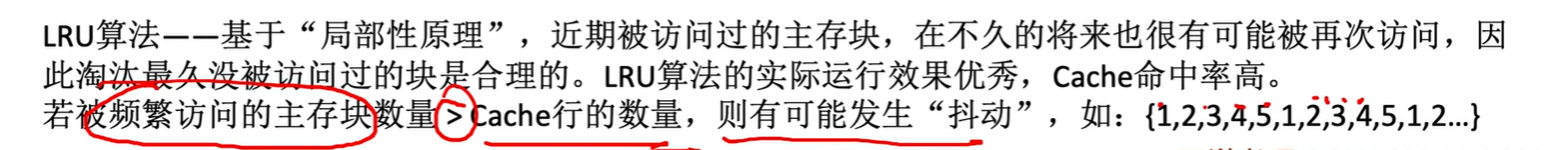

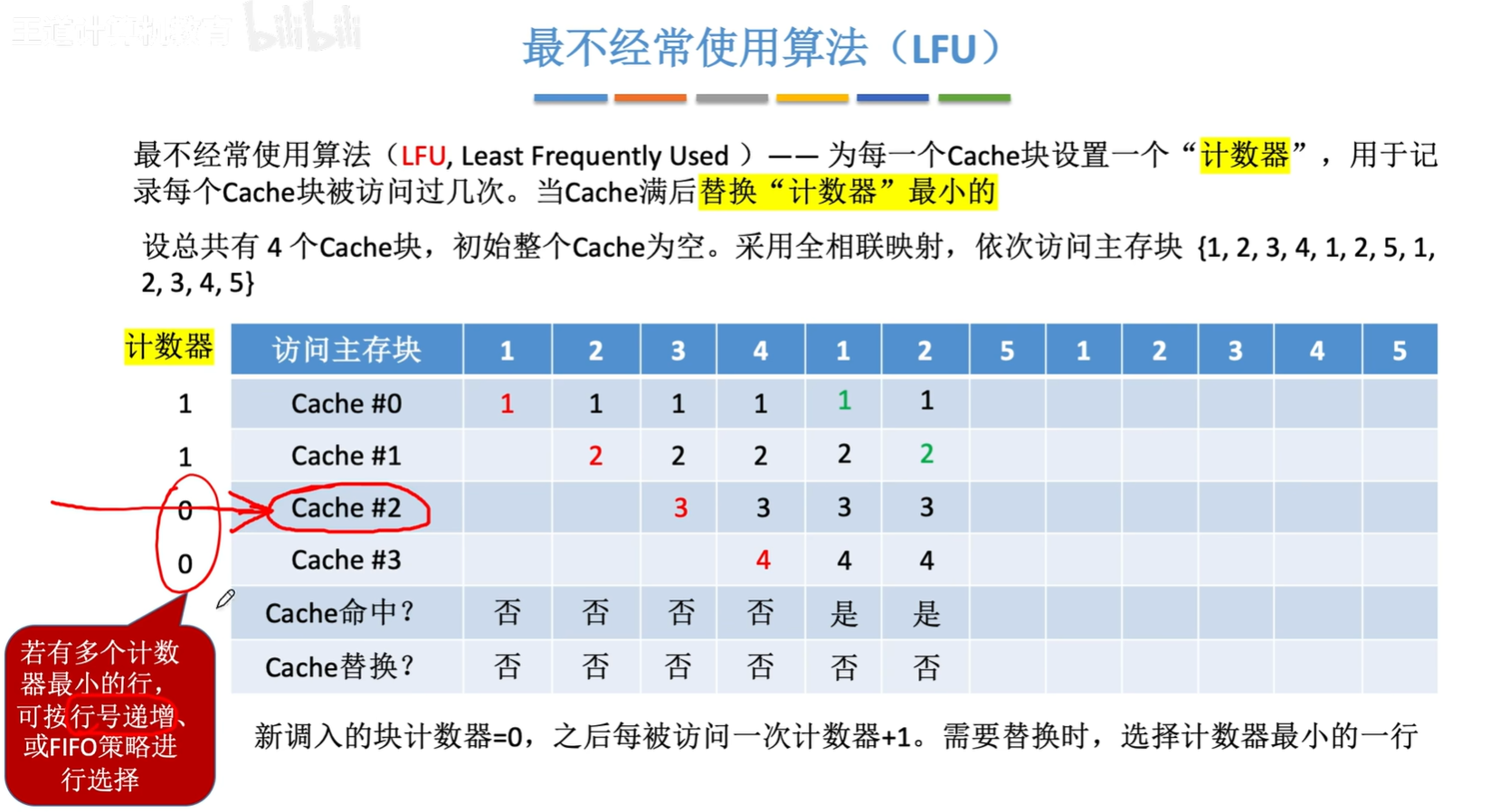

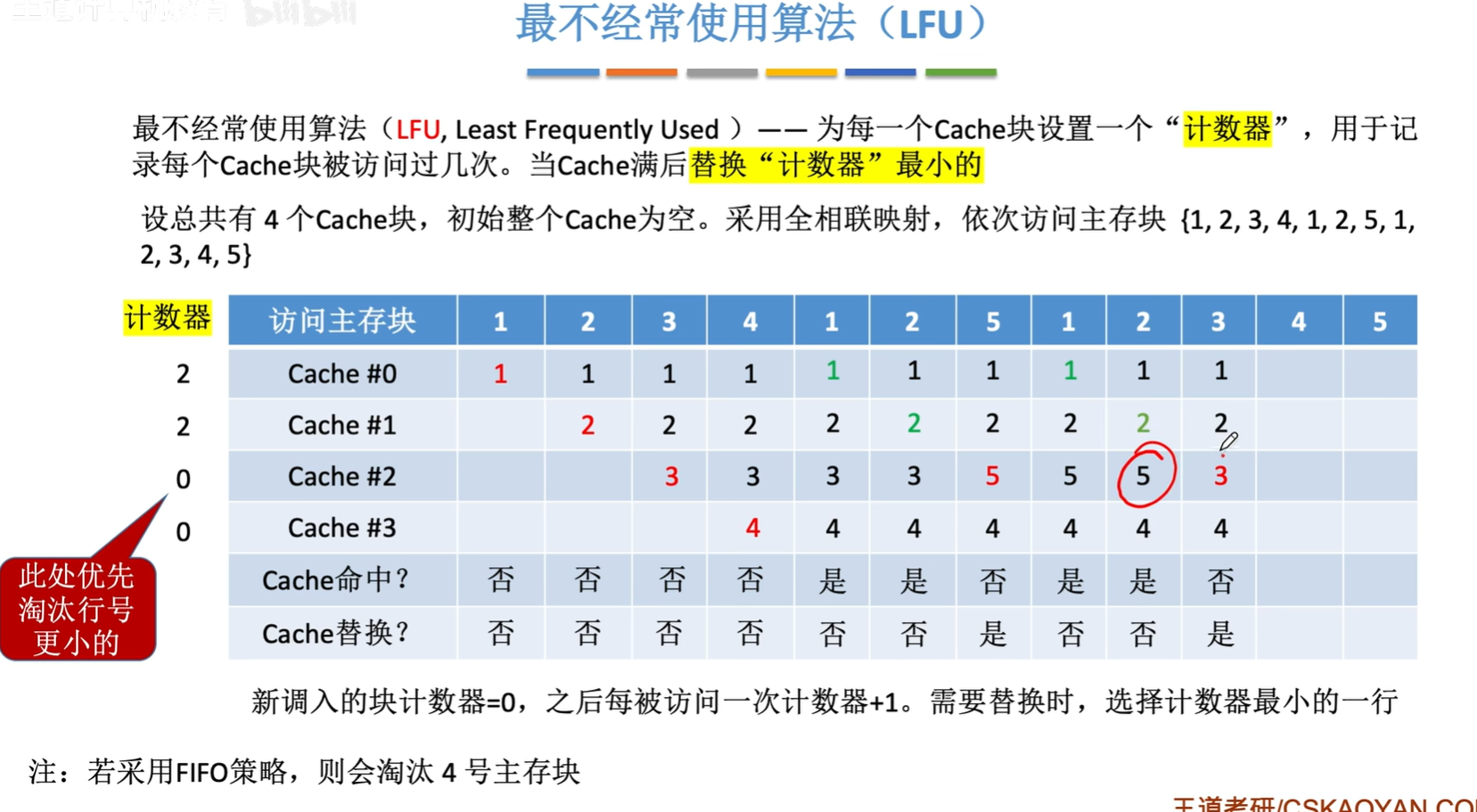

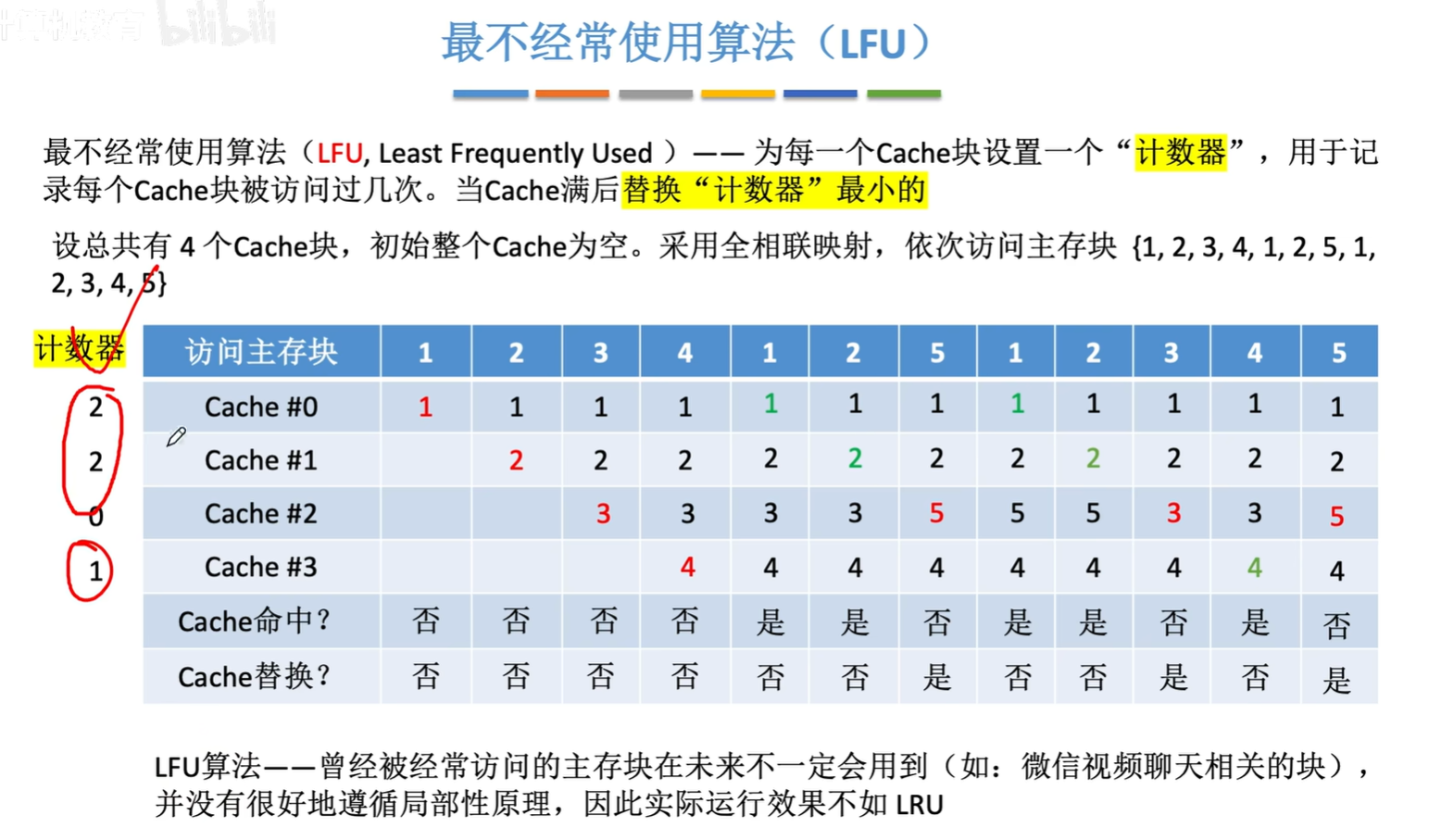

3. Cache的替換算法

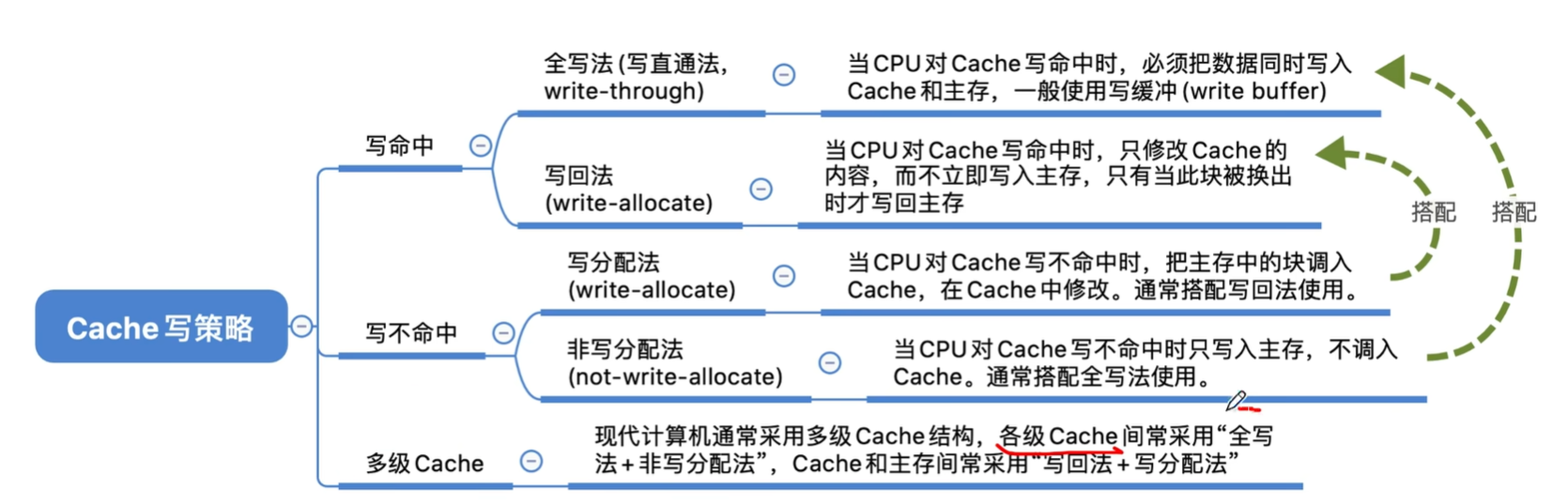

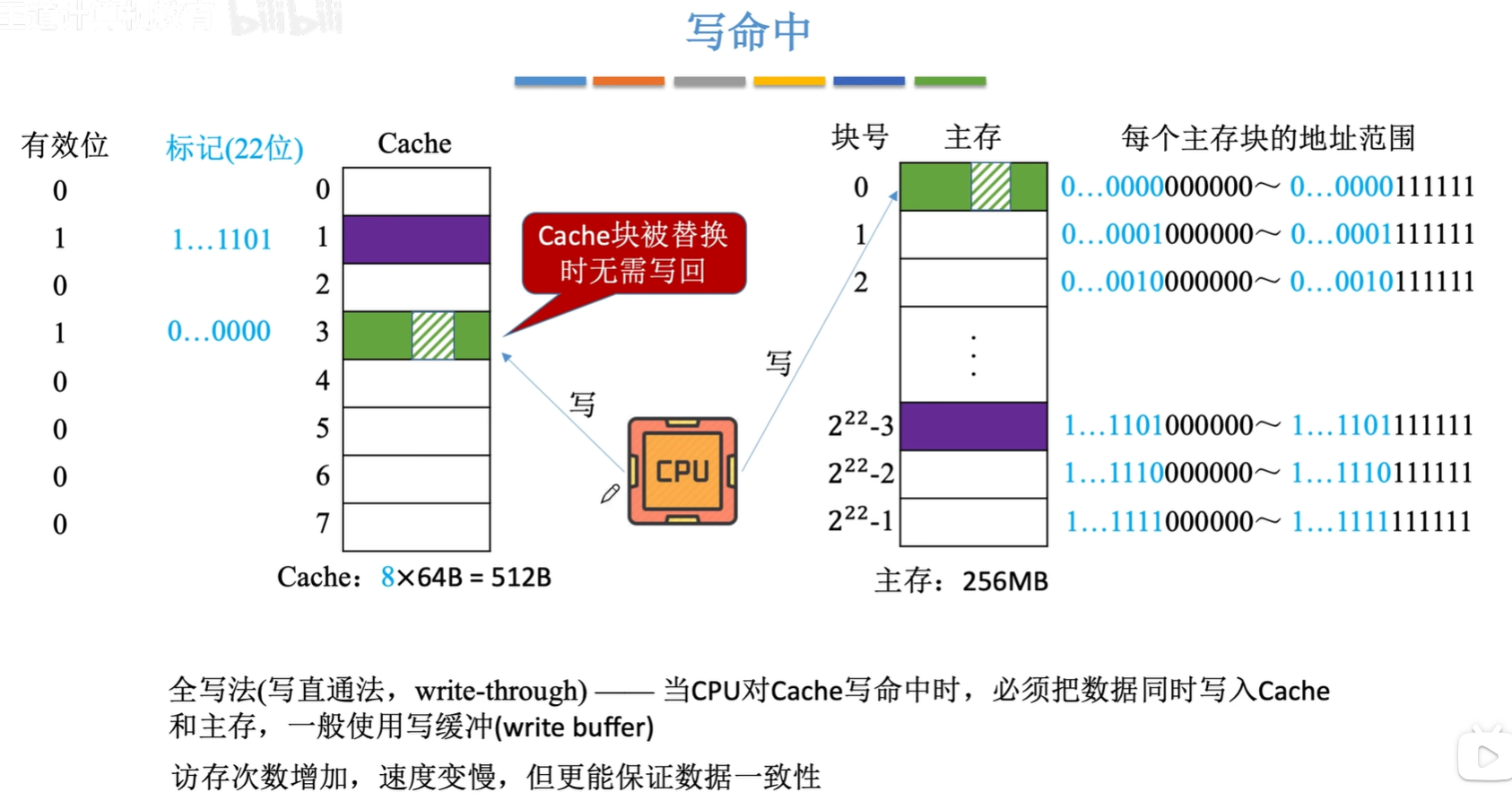

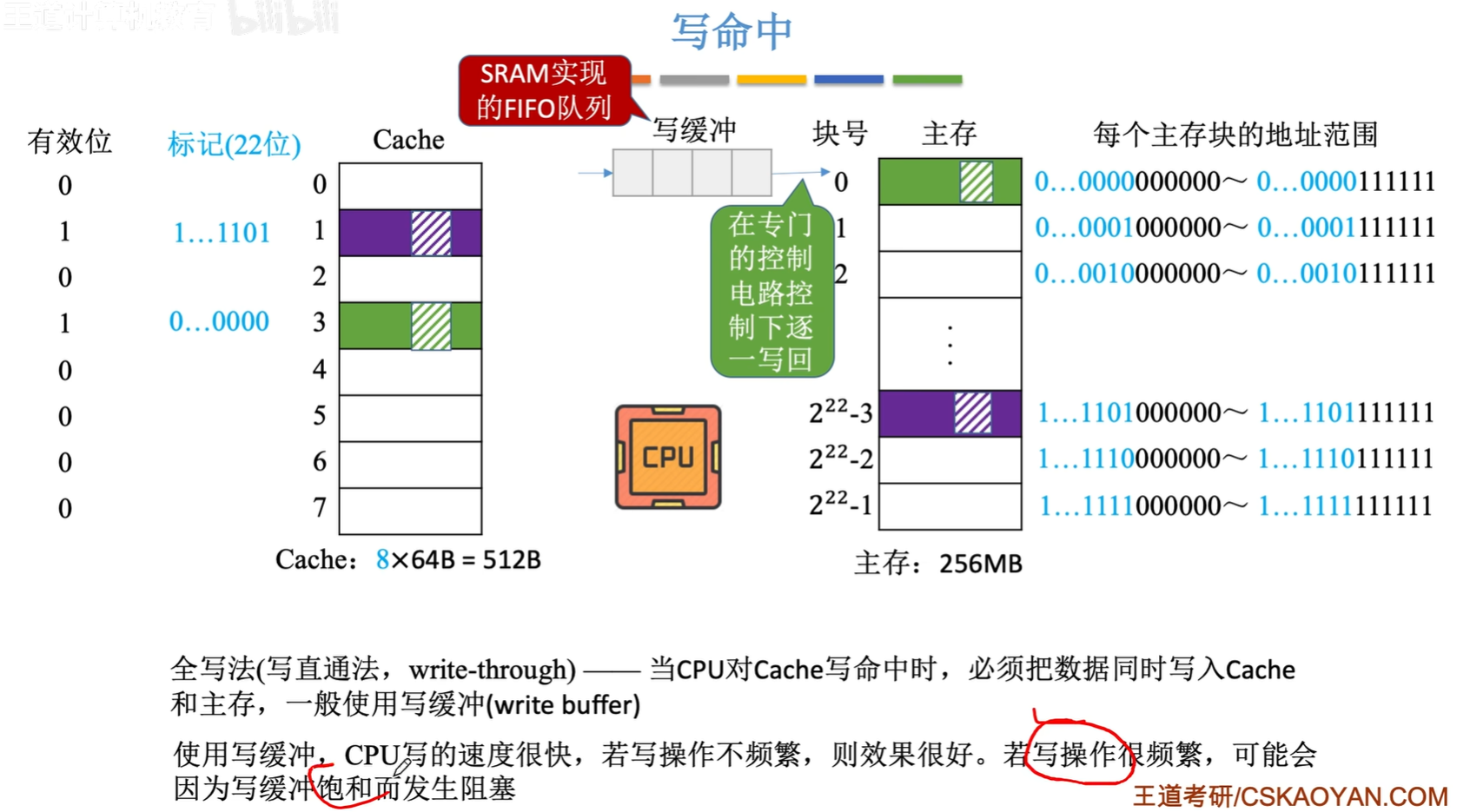

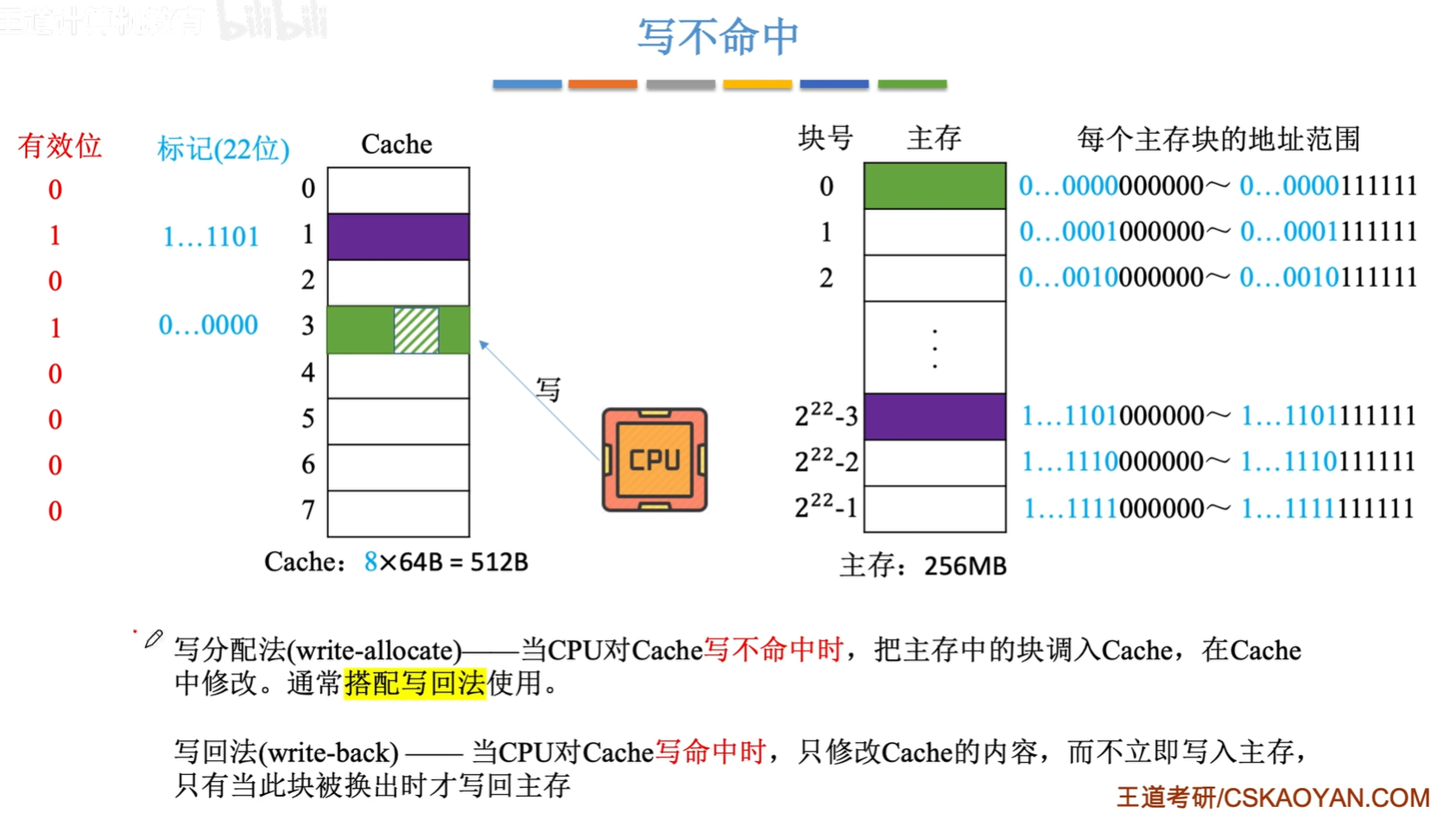

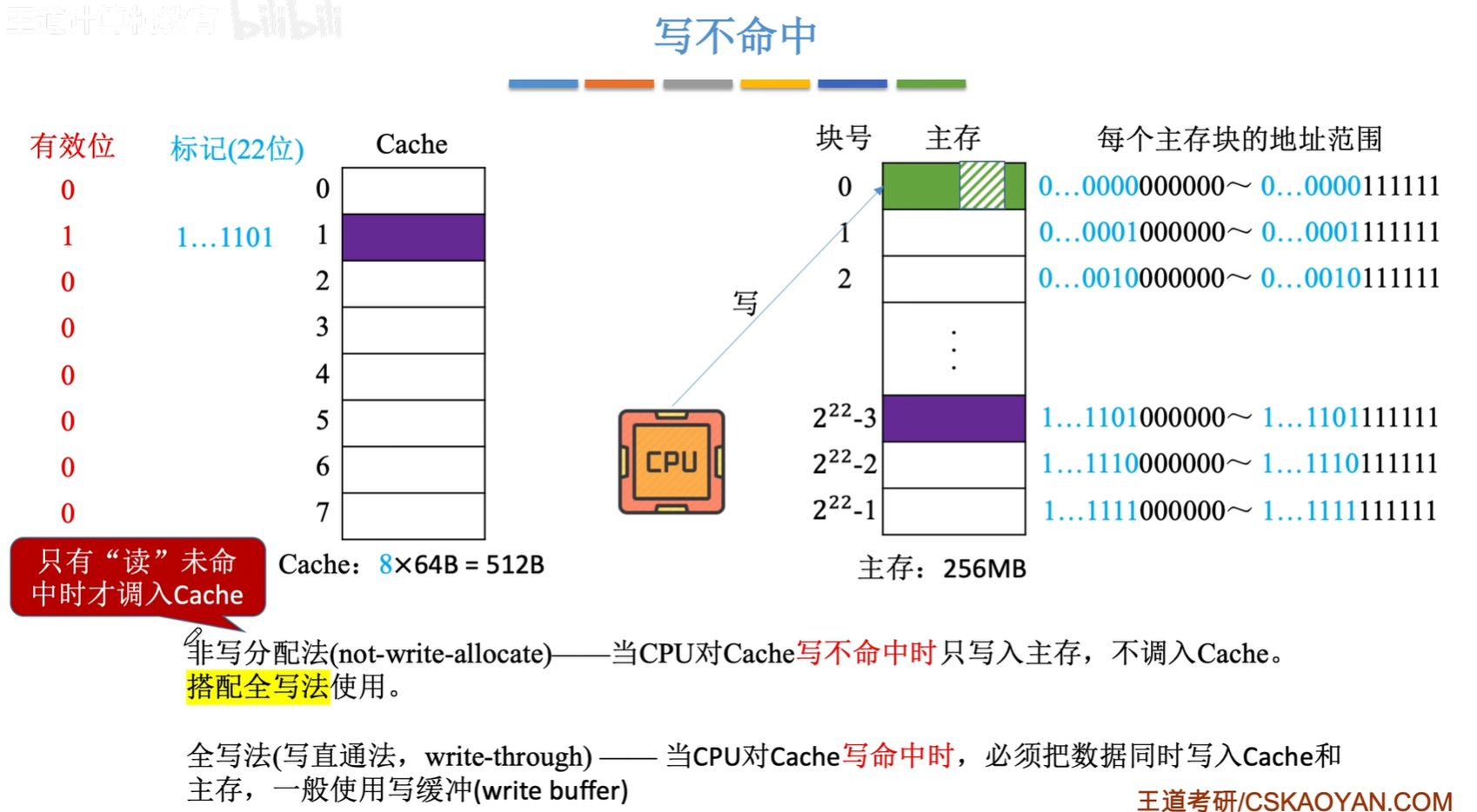

4. Cache寫策略

阻塞的意思是cpu必須阻塞等待

)

)