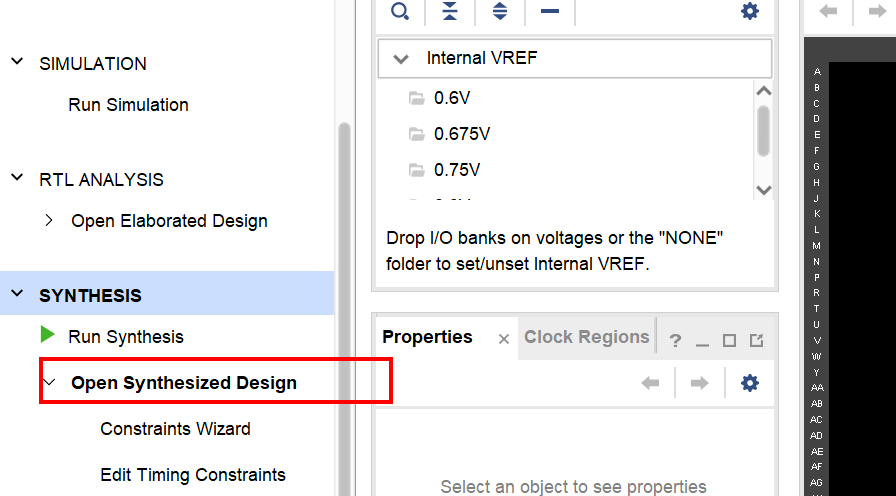

在工程綜合完成或者implement完成后,打開綜合設計或者實現設計。

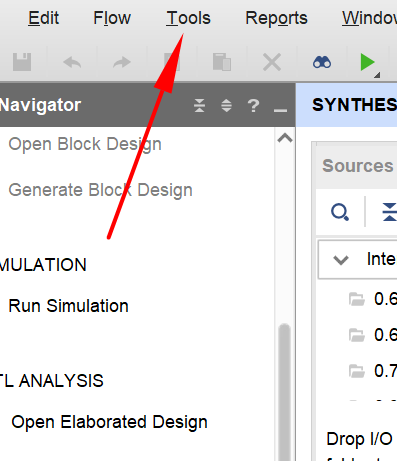

toots--->Edit Device Properties--->打開比特流設置

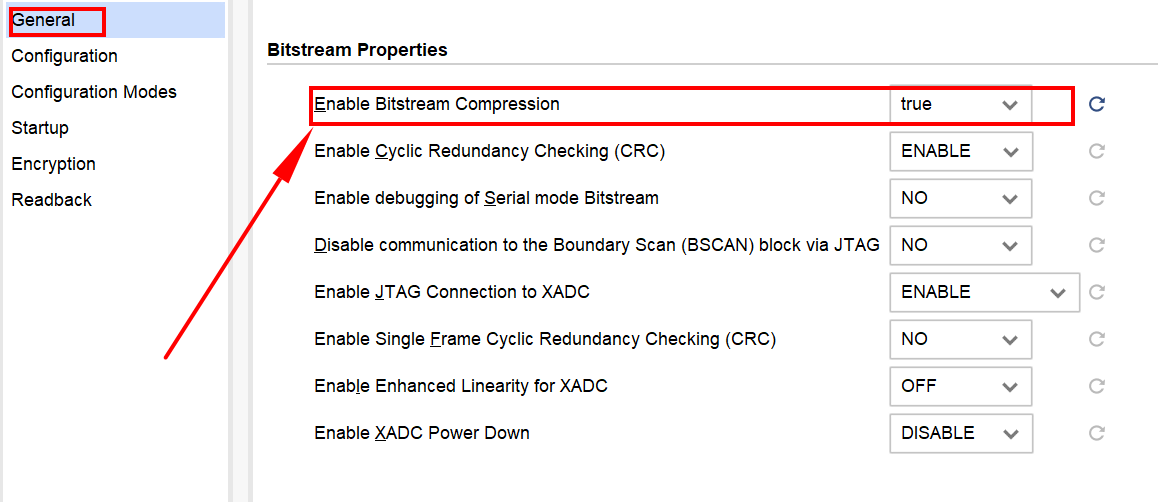

將bitstream進行壓縮

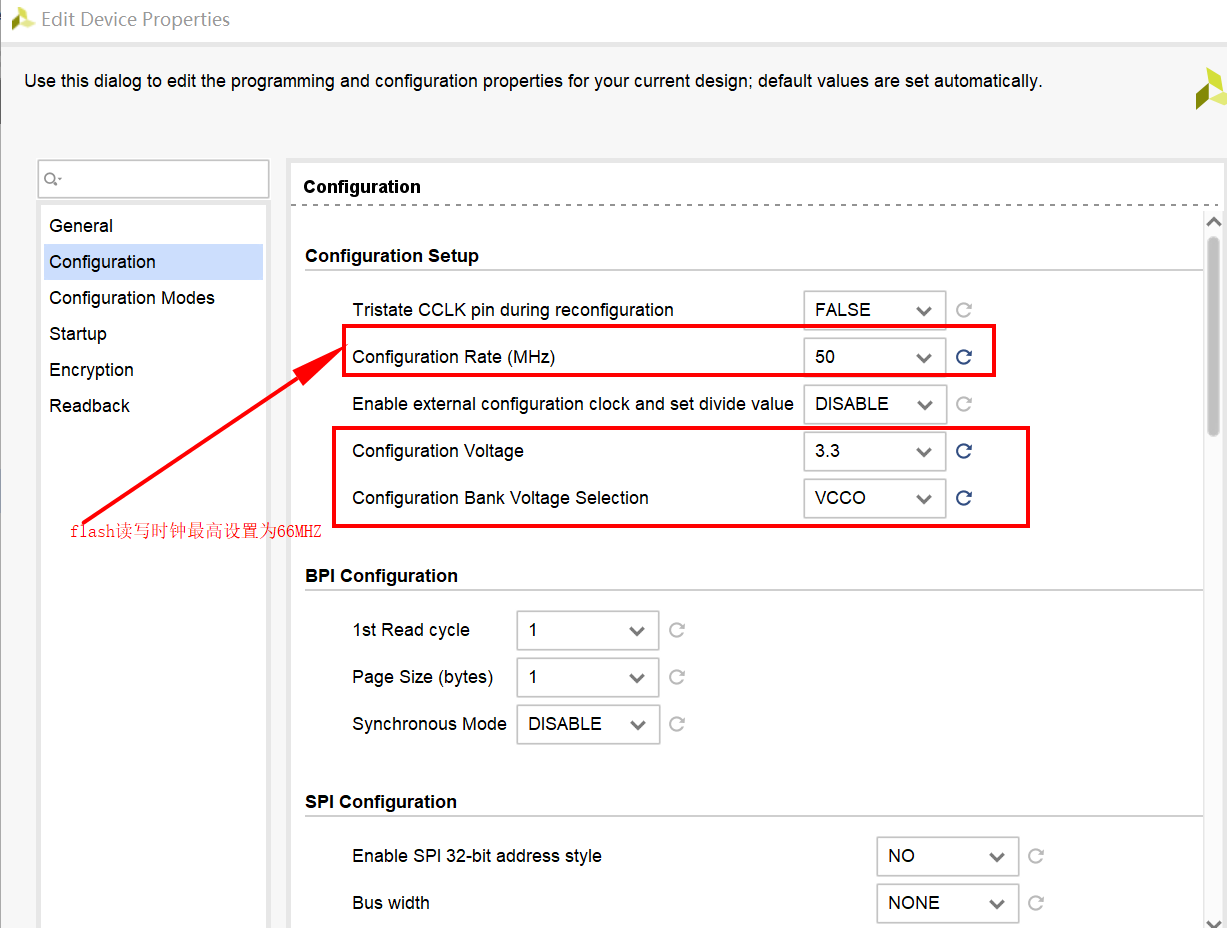

上圖中,時鐘頻率選擇的檔位有限,最大為66MHZ

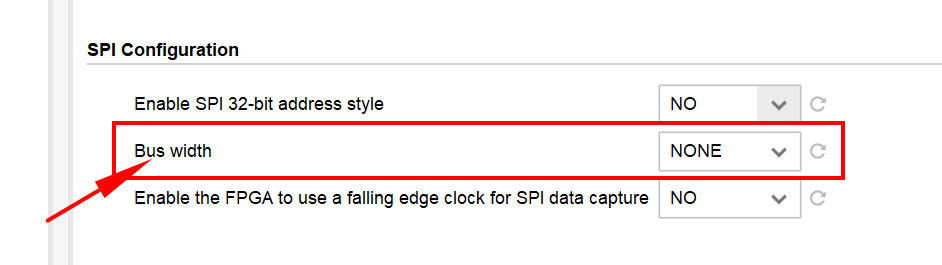

io的bus width可以設置為x1,x2,x4

- vivado在設計過程中生成的bitstream需要通過FPGA特定的配置管腳引腳導入到FPGA中。FPGA這些專用的配置管腳在不同的電壓級別下決定了其工作在不同的配置模式。

- 純FPGA的bitstream加載和ZYNQ的加載不同,其中純FPGA加載是直接通過外部Flash進行加載的,而ZYNQ的Flash不是通過FPGA加載的,而是通過ARM進行加載,所以QSPI的x1和x4是對單純的FPGA是可配的,ZYNQ一般是只能進行文件的壓縮配置和電壓配置。

- 燒錄需要注意:FPGA如果選擇生成bit文件是QSPI X4的,如果在批量燒寫完FLASH之后再貼裝的情況下,需要工廠燒錄器設置為x4的燒寫模式。要不,貼裝之后FPGA很有可能起不來。

- 參考:Xilinx FPGA——Vivado生成bit文件時需要添加的約束_edit device properties vivado-CSDN博客

- 參考:https://zhuanlan.zhihu.com/p/457990312

- 參考:xilinx fpga 啟動速度加快_專欄_易百納技術社區

- 注意:不同型號的FPGA對外部QSPI Flash支持的最高頻率是不一樣的。XC6SLX45支持的最高頻率僅為26MHz, 而XC7K325T支持的最高頻率高達66MHz

- 參考:Xilinx FPGA下如何加快QSPI Flash加載速度_如何提高spi flash訪問速度-CSDN博客

- 關于燒錄文件:固化文件bin文件最小,hex文件最大,mcs大小居中

- 參考:關于XDC 約束固化flash流程_xdc約束為x4-CSDN博客

- 參考:FPGA:生成固化文件(將代碼固化到板子上面)_fpga怎么將代碼固定-CSDN博客

- 參考:FPGA——VIVADO生成固化文件,掉電不丟失_vivado固化bin文件-CSDN博客

)

的XOR異或pyTorch版250501)

![[pdf、epub]300道《軟件方法》強化自測題業務建模需求分析共257頁(202505更新)](http://pic.xiahunao.cn/[pdf、epub]300道《軟件方法》強化自測題業務建模需求分析共257頁(202505更新))