第五篇:多主仲裁與錯誤恢復

副標題 :從總線沖突到故障自愈——構建高可靠I2C系統的終極指南

1. 多主仲裁機制

1.1 仲裁原理與硬件實現

-

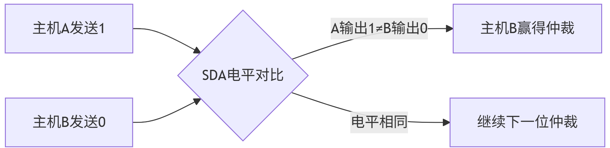

仲裁流程圖解 :

-

仲裁失敗處理 :

立即切換為從機模式

監測總線空閑后重試(隨機退避算法)

1.2 仲裁波形深度解析

- 典型沖突場景 :

關鍵節點:- t?: 主機A發送高電平,主機B發送低電平

- t?: 主機A檢測到SDA被拉低,釋放總線

- t?: 主機B繼續完成傳輸

1.3 Verilog仲裁邏輯實現

verilog

// 仲裁檢測模塊

always @(negedge scl) begin if (sda_out_reg != sda_in && master_mode) begin arbitration_lost <= 1'b1; master_mode <= 1'b0; // 切換為從機 retry_counter <= 8'd0; end

end // 隨機退避重試

always @(posedge clk) begin if (arbitration_lost) begin if (bus_free && retry_counter == backoff_time) master_mode <= 1'b1; else retry_counter <= retry_counter + 1; end

end

2. 錯誤檢測與恢復

2.1 錯誤分類與應對策略

| 錯誤類型 | 檢測方法 | 恢復策略 |

|---|---|---|

| 從機無應答 | ACK位檢測 | 重發數據包(最多3次) |

| 總線死鎖 | 超時計數器(>50ms) | 發送STOP條件強制復位 |

| 時鐘拉伸超時 | SCL低電平持續時間監控 | 主控復位并重新初始化 |

2.2 硬件CRC校驗加速

- CRC8算法實現 :

verilog

// 多項式: x^8 + x^2 + x + 1 function [7:0] crc8; input [7:0] data; input [7:0] crc; begin crc8[0] = data[7] ^ crc[6]; crc8[1] = data[6] ^ crc[7] ^ crc[0] ^ crc[6]; // ... 完整CRC邏輯 end endfunction

- 性能對比 :

| 實現方式 | 時鐘周期數 | 資源消耗(LUT) |

|---|---|---|

| 軟件計算 | 72 | 0 |

| 硬件加速 | 8 | 42 |

3. 高級診斷功能

3.1 錯誤注入測試平臺

- 可注入錯誤類型 :

python

error_types = [ "NACK Injection", "Clock Stretch", "Glitch on SDA", "Arbitration Loss" ]

- 自動化測試框架 :

測試流程: 1. 發送正常數據包 2. 注入指定錯誤 3. 監測控制器響應 4. 生成測試報告

3.2 JTAG調試接口設計

- 寄存器映射 :

| 地址 | 名稱 | 功能 |

|---|---|---|

| 0x00 | ERR_STATUS | 錯誤類型編碼 |

| 0x04 | RETRY_COUNTER | 重試次數統計 |

| 0x08 | DEBUG_CONTROL | 錯誤注入使能 |

- Vivado ILA配置 :

tcl

create_debug_core u_ila ila set_property C_DATA_DEPTH 1024 [get_debug_cores u_ila] connect_debug_port u_ila/clk [get_nets clk]

4. 設計注意事項

4.1 總線負載管理 :

總線上主設備不宜過多(建議≤3個),避免頻繁仲裁降低效率。

增加 上拉電阻 優化信號邊沿(典型值:4.7kΩ@3.3V)。

4.2 錯誤恢復機制 :

仲裁失敗的主設備應 等待隨機時間 后重試,避免重復沖突。

添加 總線監控邏輯 (如I2C協議分析儀),記錄沖突事件。

4.3 時序參數驗證 :

使用示波器檢查 建立時間(t_SU;DAT) 和 保持時間(t_HD;DAT) ,確保仲裁期間時序滿足規范。

)