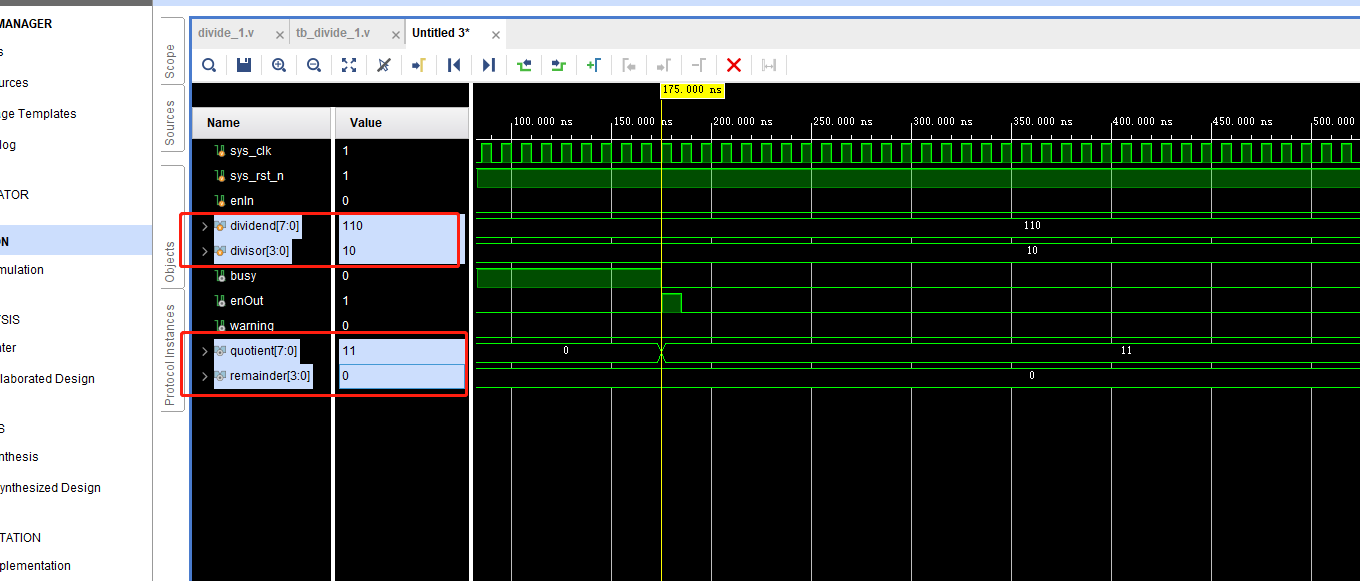

1、可變系數除法實現----利用除法的本質

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/04/15 13:45:39

// Design Name:

// Module Name: divide_1

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module divide_1(// clk and rst_ninput wire sys_clk ,input wire sys_rst_n ,// dividend and divisor input wire enIn ,input wire [7:0] dividend ,input wire [3:0] divisor ,output wire busy ,output wire enOut ,output wire warning ,output wire [7:0] quotient ,output wire [3:0] remainder);localparam IDLE = 1'b0 ;localparam S_CALC = 1'b1 ;reg current_state ;reg next_state ;reg lockDivs ;reg [7:0] DivA ;reg [3:0] DivB ;reg counting , ending ;reg [7:0] counter ;reg out_busy ;reg out_enOut ;reg out_warning ;reg [7:0] out_quotient ;reg [3:0] out_remainder ;wire [7:0] extDivB = { 4'b0,DivB } ;always@( posedge sys_clk )beginif( sys_rst_n == 1'b0 )begincurrent_state <= IDLE ;DivA <= 8'b0 ;DivB <= 4'b0 ; counter <= 8'b0 ;out_enOut <= 1'b0 ;out_warning <= 1'b0 ;out_quotient <= 8'b0 ;out_remainder <= 4'd0 ;endelsebegincurrent_state <= next_state ;// DivA DivB counterif( lockDivs == 1'b1 )beginDivA <= dividend ;DivB <= divisor ;counter <= 8'b0 ;endelse if( counting == 1'b1 )beginDivA <= DivA - extDivB ;counter <= counter + 1'b1 ;end//out_enOutout_enOut <= ending ;// out_warningif( ending == 1'b1 )beginif( DivB == 4'b0 )beginout_warning <= 1'b1 ;endelsebeginout_warning <= 1'b0 ;end// out_quotientout_quotient <= counter ;// our_remainderout_remainder <= DivA[3:0] ;endendendalways@( current_state , enIn , DivA , extDivB )beginout_busy <= 1'b0 ;lockDivs <= 1'b0 ;counting <= 1'b0 ;ending <= 1'b0 ;case( current_state )IDLE :beginif( enIn == 1'b1 )beginlockDivs <= 1'b1 ;next_state <= S_CALC ;endelsebeginnext_state <= IDLE ;endendS_CALC :beginout_busy <= 1'b1 ;if( DivA < extDivB || extDivB == 8'b0 )beginending <= 1'b1 ;next_state <= IDLE ; endelsebegincounting <= 1'b1 ;next_state <= S_CALC ;endenddefault :beginnext_state <= IDLE ;endendcaseendassign busy = out_busy ;assign enOut = out_enOut ;assign warning = out_warning ;assign quotient = out_quotient ;assign remainder = out_remainder ;endmodule

tb

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2025/04/15 15:24:32

// Design Name:

// Module Name: tb_divide_1

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tb_divide_1();reg sys_clk ;reg sys_rst_n ; reg enIn ;reg [7:0] dividend ;reg [3:0] divisor ;wire busy ;wire enOut ;wire warning ;wire [7:0] quotient ;wire [3:0] remainder ;initialbeginsys_clk = 1'b0 ;sys_rst_n = 1'b0 ;enIn = 1'b0 ;dividend = 8'b0 ;divisor = 4'b0 ;#50enIn = 1'b1 ;dividend = 8'd110 ;divisor = 4'd10 ; sys_rst_n = 1'b1 ; #20enIn = 1'b0 ;#200$finish ; endalways #5beginsys_clk = ~sys_clk ;enddivide_1 divide_1_inst(.sys_clk (sys_clk),.sys_rst_n (sys_rst_n), .enIn (enIn),.dividend (dividend),.divisor (divisor),.busy (busy),.enOut (enOut),.warning (warning),.quotient (quotient),.remainder (remainder));endmodule

?

? ? ? ? ?但是這種做法運算一次最多需要256的clk,所以需要減小消耗的實現

2、可變系數除法實現----利用除法的豎式求解

3、可變系數除法實現----利用乘法實現除法

搭建環境和點燈)

)