今天是個陽光明媚,萬里烏云的好日子。小編我一如既往地到家打開電腦準備看騰訊視頻的五十公里桃花塢的第四季,在看到汪蘇瀧汪臺說650電臺要解散的時候小編我差點也哭了。650電臺之于桃花塢就像樂隊的鼓手一樣,都是一個團隊的靈感啊,而且650電臺已經成立四年了,現在說解散就解散是有點太可惜了。

好了,咱們不能感慨太多了,不然就有黑粉說你老是說這些廢話,不能直接進入每期文章的主題嗎?更有一些性質惡劣的粉絲說你寫這些玩意沒有人看,狗都不看的,還堅持寫這個干嘛呢?

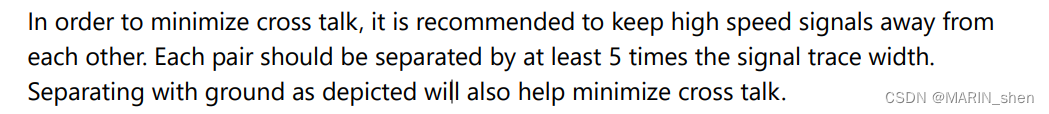

但是小編我就是一個杠精,黑子們不喜歡這個我就繼續寫,每個人的創作風格不同,不能因為別人一句話就改變了自己的原則了,用董宇輝老師之前就說的話就是一個人強大就是可以做到不以物喜,不以己悲,保持好的心態。當我正在認真看視頻時候,手機微信提醒有消息了,我打開一看原來是之前一個老伙計來自某大廠的著名PCB設計攻城獅師陳總,他說有個板子上面的信號速率很高,他們公司的硬件要求他把高速線上平行走線的長度規則加上,他說自己很多年沒有搞這個了都忘記了,問我還知道怎么設置不?你還別說我也是忘記的差不多了,我立馬打開百度那是一頓哐哐搜索啊,但是都沒有關于這個的在allegro中把高速線上平行走線的長度規則加上這個解釋和操作。其實我們在做板子的時候經常會遇到有些芯片手冊會提供這組BUS信號的間距要求,如下所示:

是不是我們按照這個手冊上重要信號線間距要求來做就一定是萬事大吉了呢?結果是否定的,我們不僅僅要考慮這個間距的問題,還要考慮同層布線的平行走線的長度耦合問題。因為大家都知道相同間距下,相鄰層間耦合帶來影響比同層間耦合更嚴重,所以說大家往往是只考慮了相鄰上下層面的串擾問題,忽略了同層走線的平行走線長度過長帶來的串擾問題,雖然說相鄰層間耦合帶來影響比同層間耦合更嚴重,但是也不是說同層的走線耦合問題就不用看了。

正當我感慨度娘也不是啥都可以查到的時候,我突然想起來之前的烏克蘭仿真同事的一句話,你要是對軟件中哪個命令不熟悉就打開這個軟件的Help命令,這個上面會有詳細的解釋的,我靈機一動果然按照這個想法成功地找到了這個在allegro中把高速線上平行走線的長度規則設置的解釋和操作了,接下來小編我就給大家分享一下這個操作命令了。

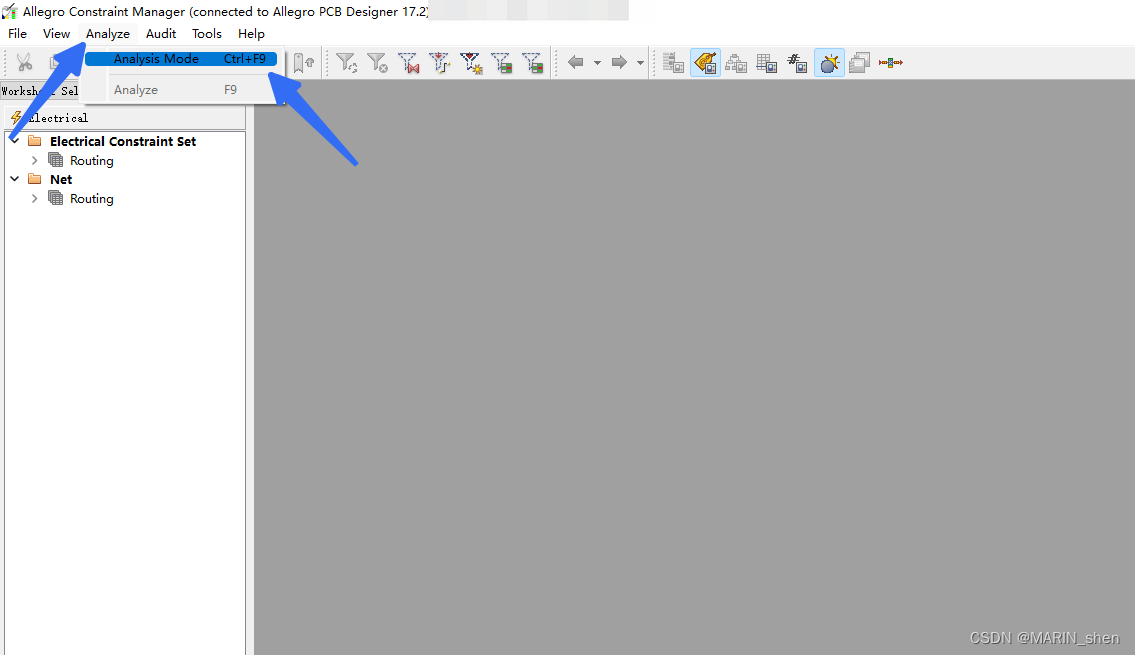

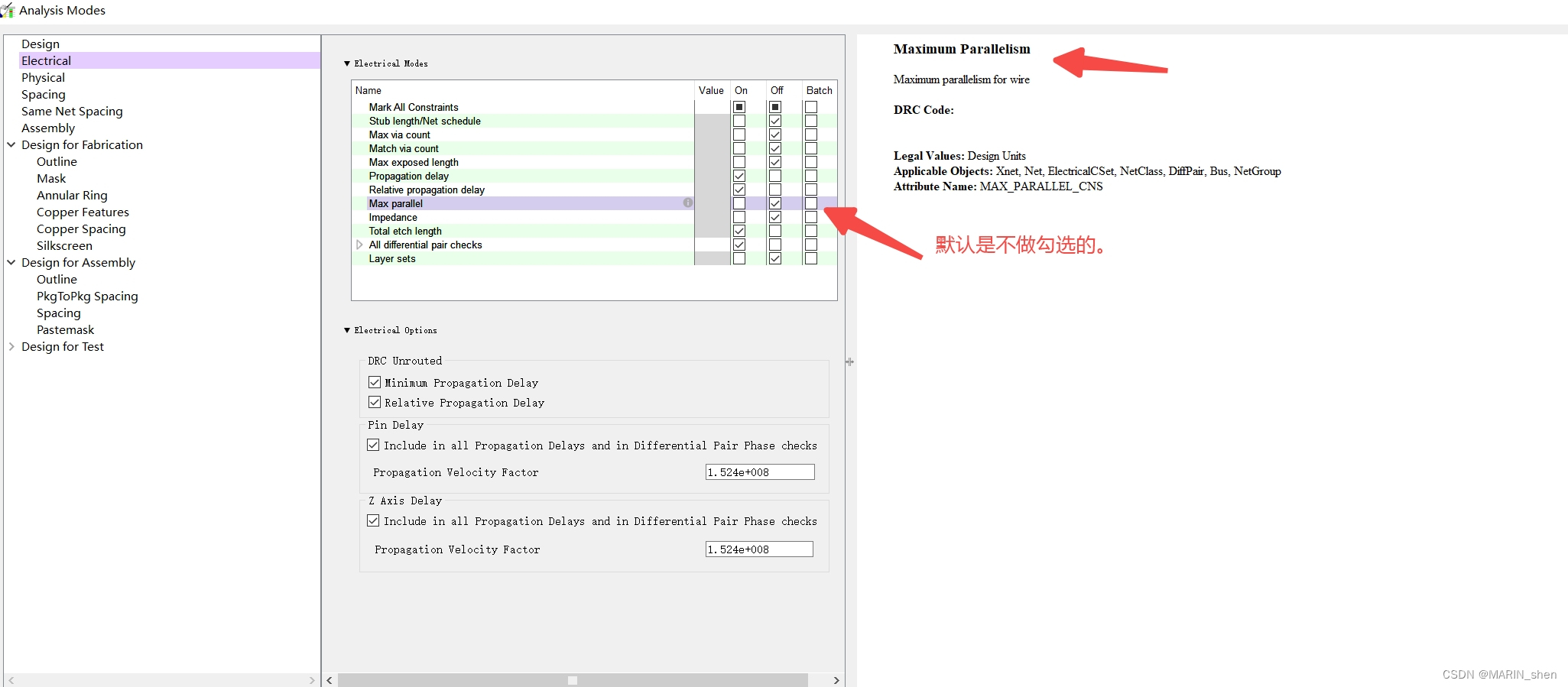

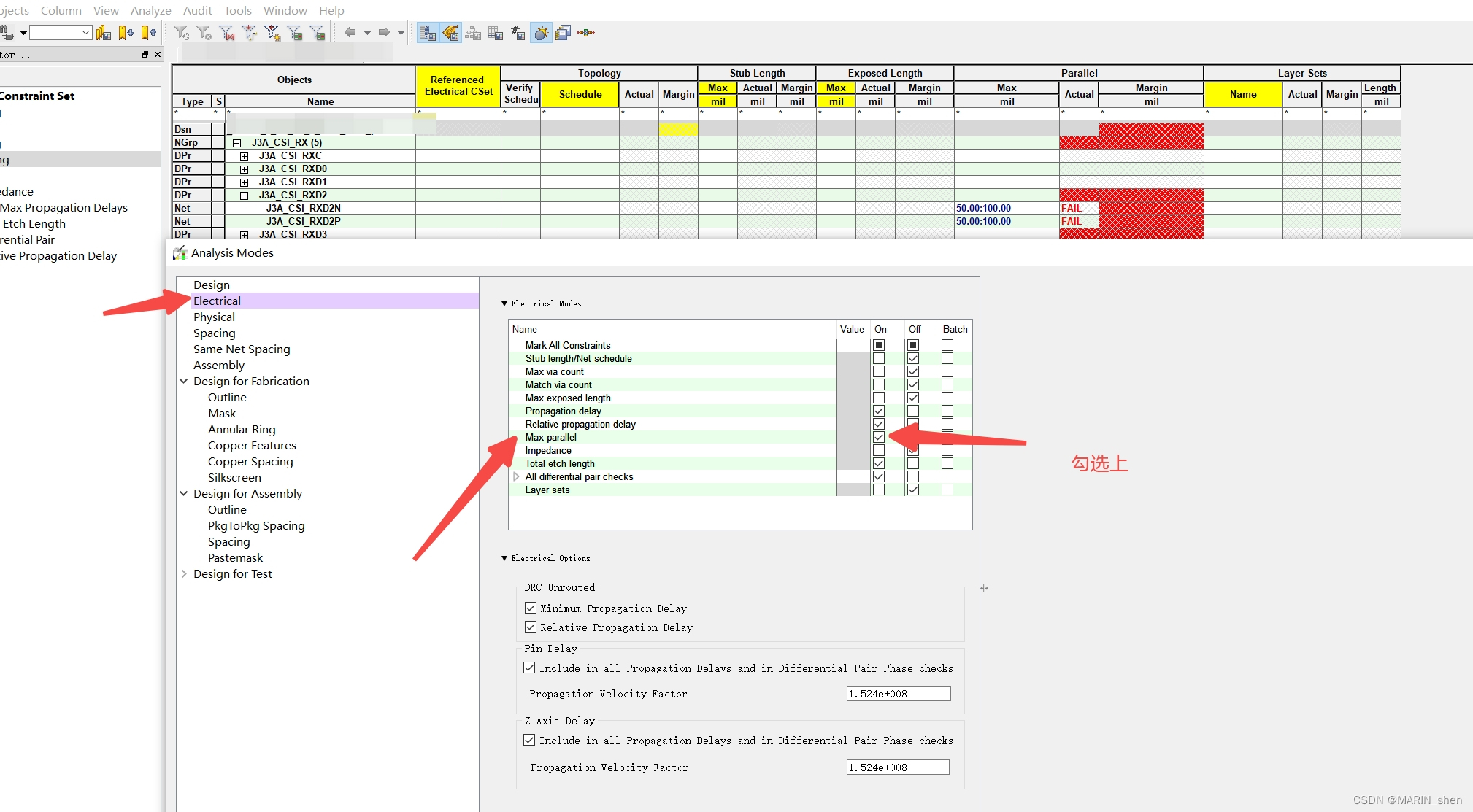

1,首先打開規則管理器界面,操作如下所示:

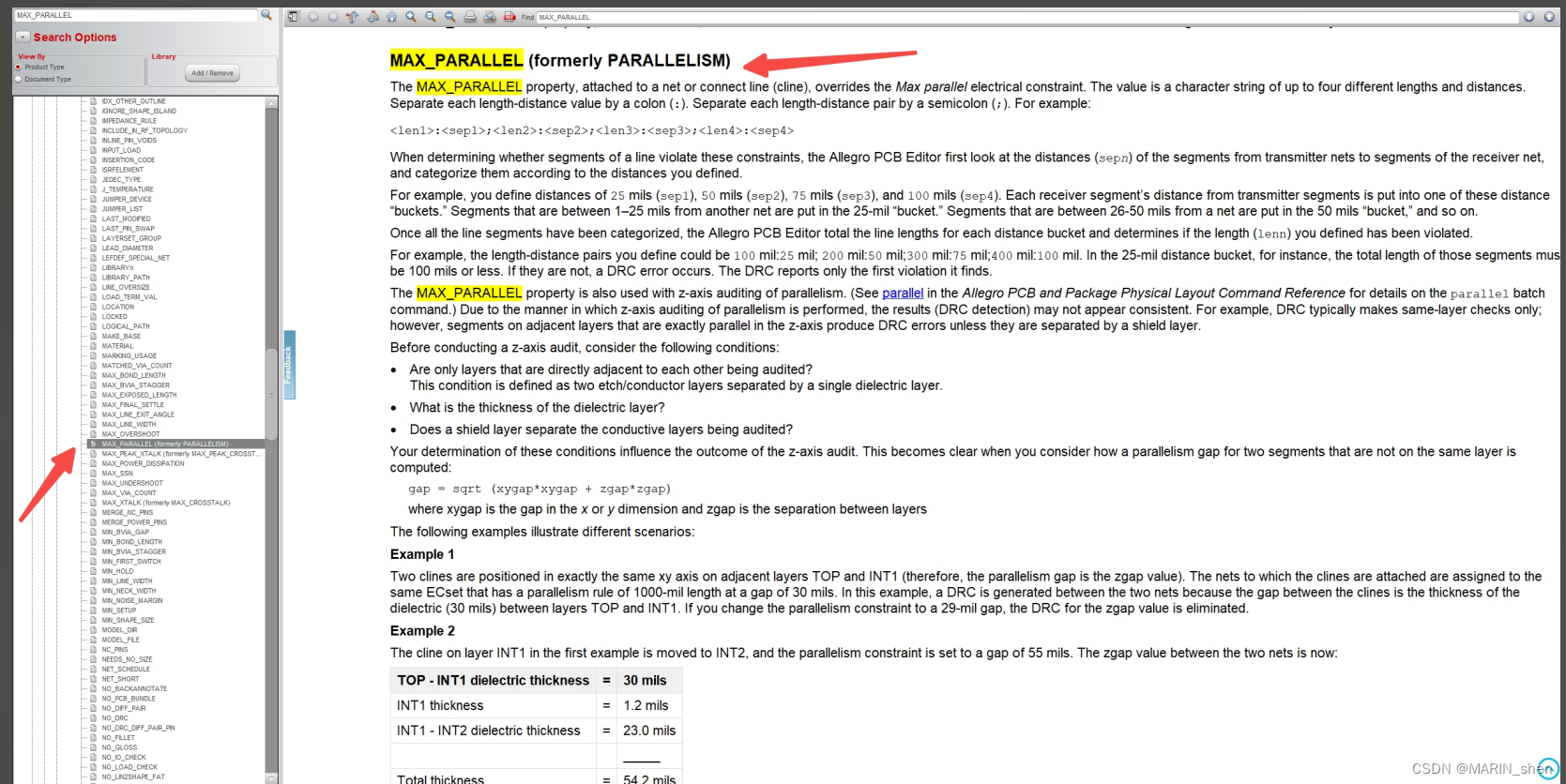

在上面的界面中把max parallel這個記得勾選上。

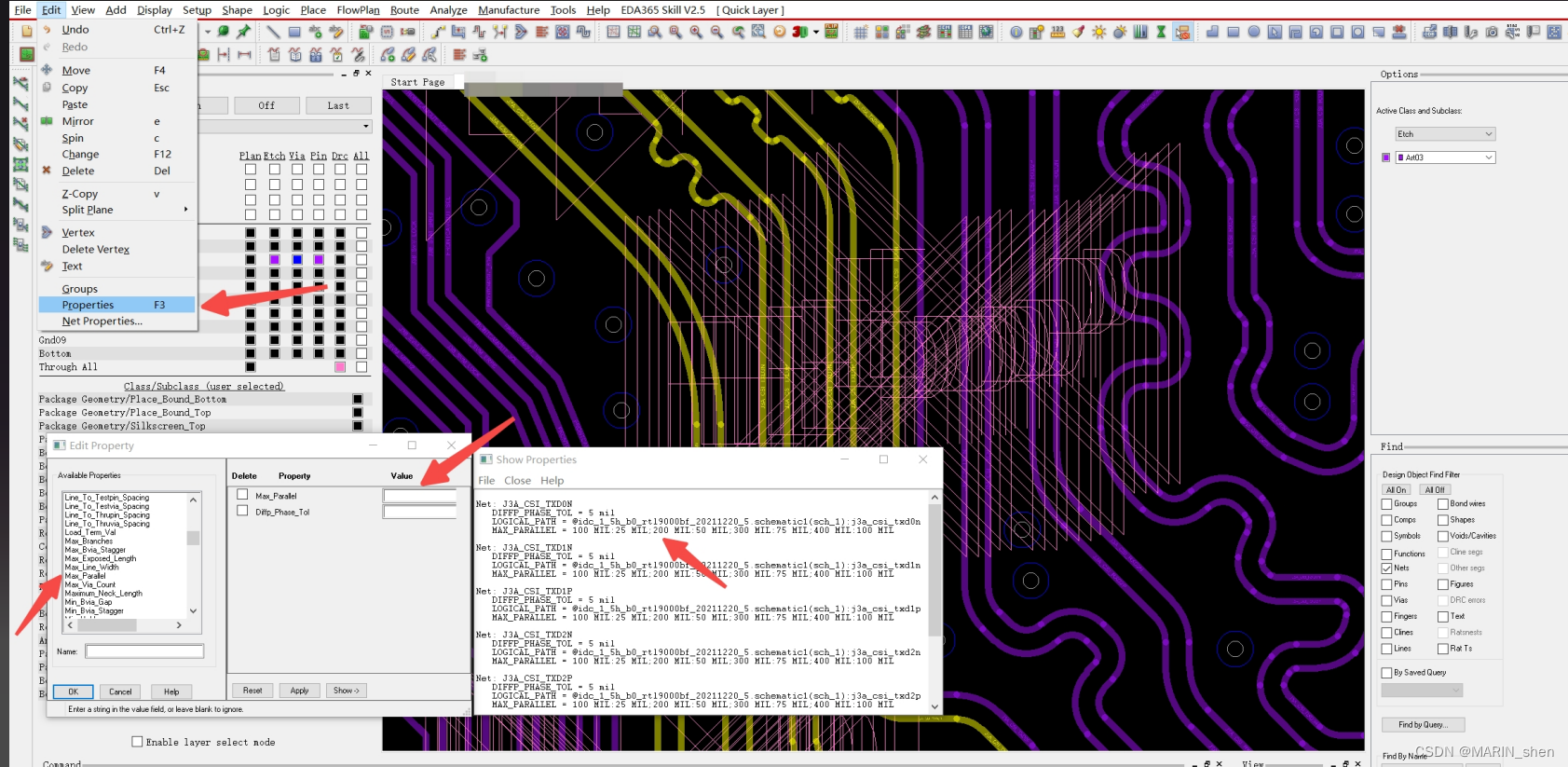

2,在PCB界面中,首先選擇Edit---properties(快捷鍵F3)?,在右邊的find欄中勾上NET,接著鼠標左鍵框選中你所需要設置的網絡,?在彈出的屬性對話欄中找到---max parallel(平行走線的最大長度)這個設置,按照仿真同事提供的數據把對應的數值填上即可。

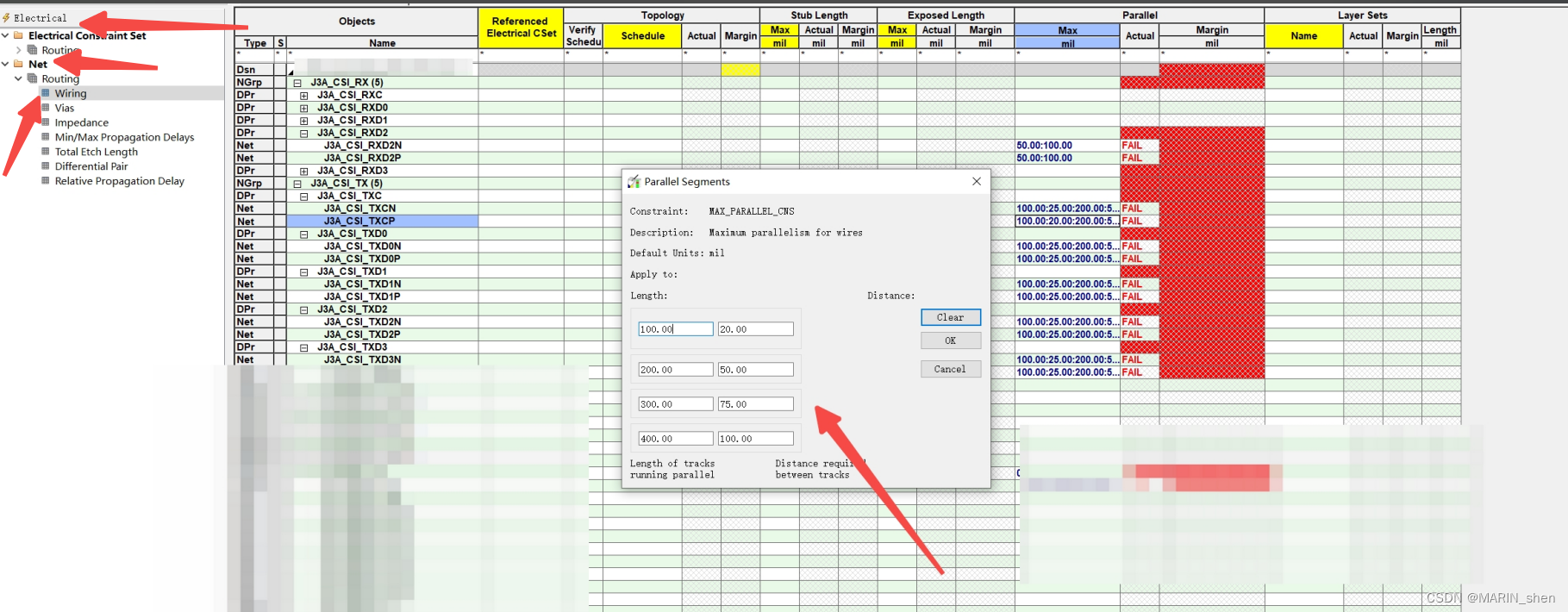

3,或者你也可以在規則管理器中也可以去設置這個屬性的,如下所示:

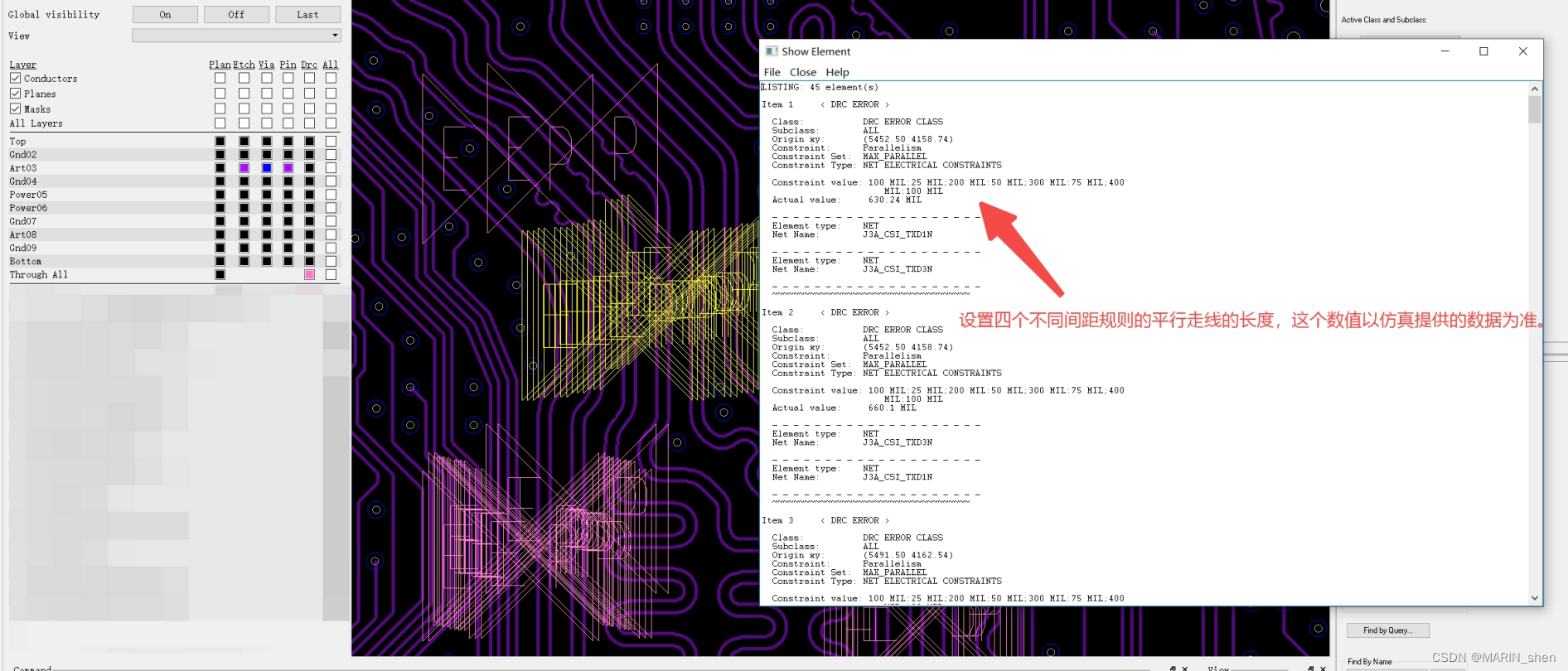

4,以上兩種方式設置完成后就可以打開DRC報錯去看下單板上高速線平行走線的規則是否滿足這要求了,記得要把DRC的ALL打開,不然你就看不到這個報錯了。

5,關于這個max parallel平行走線的最大長度)這個設置中數值是什么意思,我再這邊給大家說下,例如上面的網絡就是設置了max parallel=(100mil:25mil;200:50mil;300mil:75mil;400mil:100mil)意思就是說這個線段被分為四個部分了,第一段走線需要兩個行滿足間距在25MIL以內,走線長度小于100mil,超過這個設置就會有EP的DRC報錯了。當然也有Z方向設置的一些問題,關于這個解釋若是帖子們感興趣的話可以打開規則管理器中的Help文件去搜索一下這個,會有詳細的解釋的。

大家也都知道走線上的串擾是不可能完全消除的,只能去想辦法降低它。通常我們降低單板上信號間的串擾的做法有如下幾種設計:

1,使用平面作為返回路徑。

2,增加信號路徑之間的間距。(一些芯片手冊對重要信號的要求,例如3W,5W,5H,7H等)

3,使走線的耦合長度盡量短。(這個就是我們本期主要講的內容了)

4,在帶狀線層布線。

5,減少信號走線的阻抗。

6,使用介電常數較低的疊層(這個造成設計的成本也是會增加的,我們在一些降本的方案中謹慎使用)

7,在封裝和連接器中不采用公共返回引腳。

8,當兩條信號線之間的高度隔離度很重要的時候,可以把它們布線在具有不返回平面的不同層面上。

9,防護布線對于微帶線的作用不是很大,對于帶狀線而言,最好的做法就是在兩端和沿線上都使用有短路過孔的防護布線。(走線包GND,包地線上加GND孔)

以上就是本期的所有內容了,我們下期文章不見不散。

)

)