FPGA的LUT理解

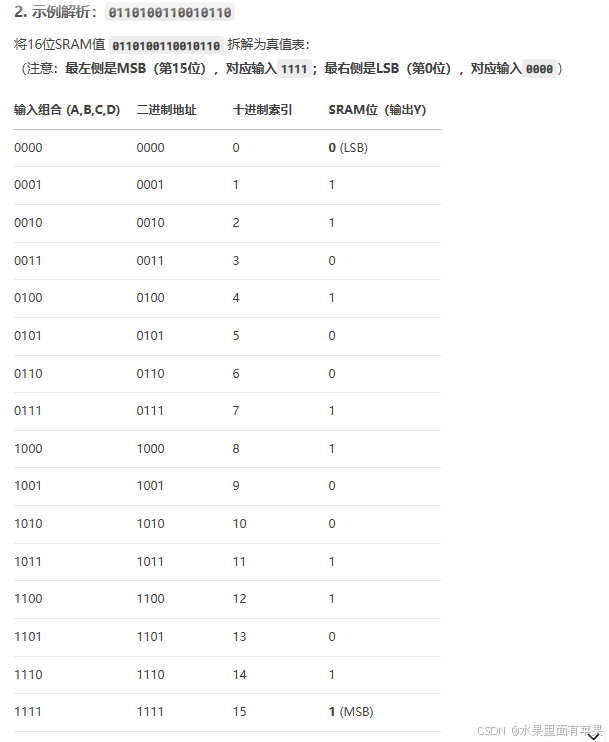

FPGA的4輸入LUT中,SRAM存儲的16位二進制數(如 0110100110010110)直接對應真值表的輸出值。下面通過具體例子詳細解釋其含義:

1. 4輸入LUT

4輸入LUT的本質是一個16×1的SRAM,它通過存儲真值表的方式實現任意4輸入1輸出的組合邏輯功能。

2. SRAM存儲的真值表映射關系

4個輸入(A,B,C,D) 組成16種可能的組合(0000到1111)。

SRAM的16位 按固定順序存儲每種輸入組合對應的輸出(0或1)。

地址映射規則(以Xilinx FPGA為例):

輸入 A,B,C,D 被視為4位二進制數,最低位是D,最高位是A。

例如:A,B,C,D = 0101 → 二進制 0101 = 十進制 5 → 選擇SRAM的第5位(從0開始計數)。

3. 實例解析

3. 對應的邏輯函數

觀察真值表:輸出Y在特定輸入組合時為1,其余為0。

實際功能:這個SRAM配置實現的是一個 自定義組合邏輯函數,例如:

當輸入滿足以下條件時,Y=1:

A,B,C,D = 0001(Y=1)

A,B,C,D = 0010(Y=1)

A,B,C,D = 0100(Y=1)

…(其他Y=1的情況)

4. 為什么這樣設計?

靈活性:通過修改SRAM的值,無需改動電路即可改變邏輯功能。

例如:將 0110100110010110 改為 1111000011110000,LUT立即變為另一個函數。

硬件效率:SRAM的讀寫速度快,適合FPGA的動態配置需求。

標準化:所有4輸入組合邏輯均可用同一LUT結構實現,簡化FPGA架構設計。

5. 實際FPGA中的應用

綜合工具:將Verilog代碼轉換為真值表并生成SRAM配置位。

處理流程(簡化版))

技能系統 投劍技能(中)技能變種實現)

)