一、概述

(一)QSPI 簡介

QSPI(Quad Serial Peripheral Interface)是一種高速串行通信接口,在標準 SPI(Serial Peripheral Interface)的基礎上擴展至 4 條數據線(Quad Mode),顯著提升數據傳輸速率。它廣泛應用于 Flash 存儲器、傳感器和微控制器之間的通信。

(二)主要特性

多種模式支持 :兼容 Standard SPI(1 - bit 模式)、Dual SPI(2 - bit 模式)以及 Quad SPI(4 - bit 模式,最高吞吐量)。

高時鐘頻率 :通常支持 50MHz - 133MHz(取決于芯片),為數據傳輸提供高速時鐘保障。

低引腳占用 :僅需 6 個引腳(CLK, CS, IO0 - IO3)即可實現全雙工通信,有效節省硬件資源。

內存映射模式(XIP, Execute - In - Place) :允許 CPU 直接訪問 QSPI Flash,無需額外緩存,提升系統運行效率。

(三)應用場景

在嵌入式系統中,QSPI 常用于連接微控制器與外部 Flash 存儲器,實現程序代碼和數據的高速讀寫操作;還可與各類傳感器配合,快速傳輸傳感器采集到的數據,滿足工業控制、汽車電子、物聯網等諸多領域的實時性與大數據量傳輸需求。

二、AS32A601 QSPI 硬件設計

| 引腳名稱 | 功能 | 說明 |

| CLK | 時鐘信號 | 主設備輸出,從設備同步數據 |

| CS | 片選信號(低電平有效) | 使能從設備通信 |

| IO0 (DQ0) | 數據線0(MOSI in SPI模式) | 單線模式:單向數據輸入/輸出 |

| IO1 (DQ1) | 數據線1(MISO in SPI模式) | 單線模式:單向數據輸入/輸出 |

| IO2 (DQ2) | 數據線2(WP# in SPI模式) | Quad模式:雙向數據傳輸 |

| IO3 (DQ3) | 數據線3(HOLD# in SPI模式) | Quad模式:雙向數據傳輸 |

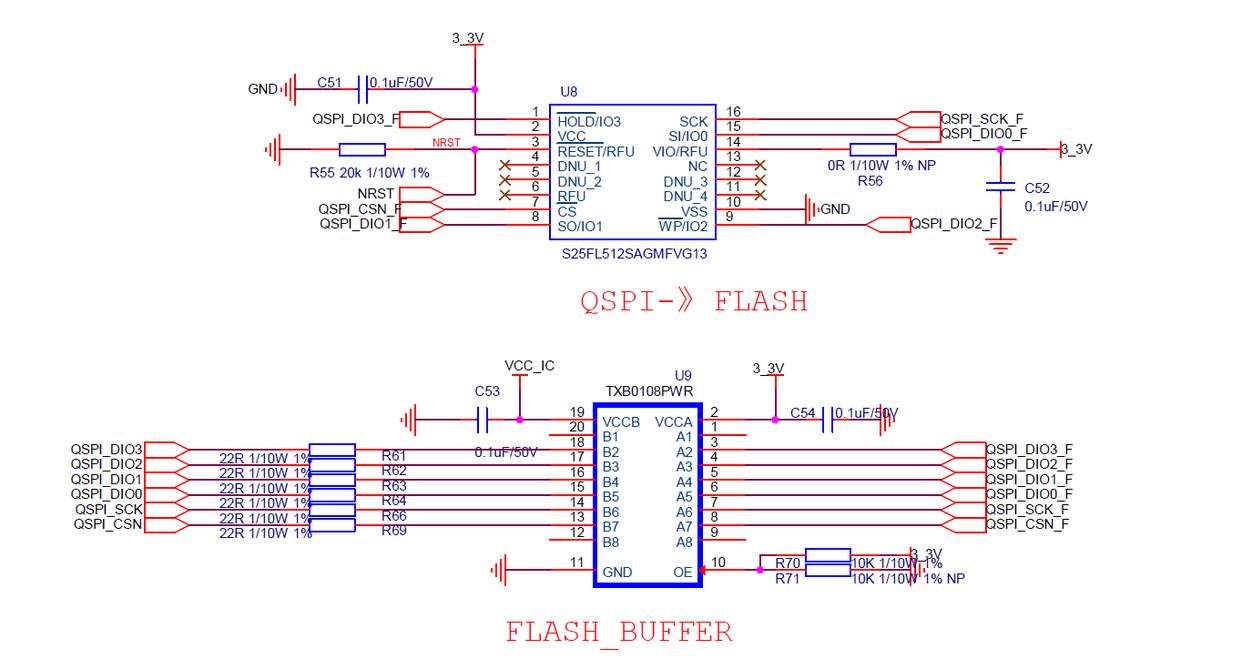

(二)開發板配置

在 AS32A601 開發板上,QSPI 經過一個 BUFFER 芯片接入 QSPI_FLASH,所選 FLASH 型號為 S25FL512SAGMFVG13,該型號 QSPI 支持最大速率可達 45MHz,為系統穩定運行提供可靠存儲支持。

三、QSPI 時序解析

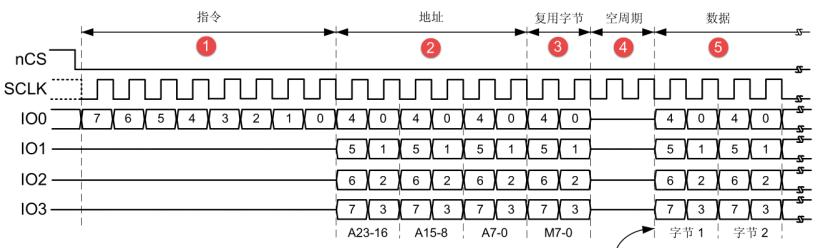

(一)指令階段

這一階段,將在QSPI_CCR[7:0]寄存器的instruction字段中配置的一條8位指令發送到Flash,指定待執行操作的類型。

盡管大多數Flash從IO0/SO信號(單線SPI模式)只能以一次1位的方式接收指令,但指令階段可選擇一次發送2位(在雙線SPI模式中通過IO0/IO1)或一次發送4位(在四線SPI模式中通過IO0/IO1/IO2/IO3)。這可通過QSPI_CCR[9:8]寄存器中的IMODE[1:0]字段進行配置。若IMODE = 00,則跳過指令階段,命令序列從地址階段(如果存在)開始。

(二)地址階段

在地址階段,將1-4字節發送到Flash,指示操作地址。待發送的地址字節數在QSPI_CCR[13:12]寄存器的ADSIZE[1:0]字段中進行配置。在間接模式和自動輪詢模式下,待發送的地址字節在QSPI_AR寄存器的ADDRESS[31:0]中指定;在內存映射模式下,則通過AHB(來自于內核或DMA)直接給出地址。地址階段可一次發送1位(單線SPI模式通過SO)、2位(雙線SPI模式中通過IO0/IO1)或4位(在四線SPI模式中通過IO0/IO1/IO2/IO3)。這可通過QUADSPI_CCR[11:10]寄存器中的ADMODE[1:0]字段進行配置。若ADMODE = 00,則跳過地址階段,命令序列直接進入下一階段(如果存在)。

(三)交替字節階段

在交替字節階段,將1-4字節發送到Flash,一般用于控制操作模式。待發送的交替字節數在QSPI_CCR[17:16]寄存器的ABSIZE[1:0]字段中進行配置。待發送的字節在QSPI_ABR寄存器中指定。

交替字節階段可一次發送1位(在單線SPI模式中通過SO)、2位(在雙線SPI模式中通過IO0/IO1)或4位(在四線SPI模式中通過IO0/IO1/IO2/IO3)。這可通過QSPI_CCR[15:14]寄存器中的ABMODE[1:0]字段進行配置。若ABMODE = 00,則跳過交替字節階段,命令序列直接進入下一階段(如果存在)。

交替字節階段存在僅需發送單個半字節而不是一個全字節的情況,比如采用雙線模式并且僅使用兩個周期發送交替字節時。在這種情況下,固件可采用四線模式(ABMODE = 11)并發送一個字節,方法是ALTERNATE的位7和3置“1”(IO3保持高電平)且位6和2置“0”(IO2線保持低電平)。此時,半字節的高2位存放在ALTERNATE的位4:3,低2位存放在位1和0中。例如,如果半字節2 (0010)通過IO0/IO1發送,則ALTERNATE應設置為0x8A (1000_1010)。

(四)空指令周期階段

在空指令周期階段,給定的1-31個周期內不發送或接收任何數據,目的是當采用更高的時鐘頻率時,給Flash留出準備數據階段的時間。這一階段中給定的周期數在QSPI_CCR[22:18]寄存器的DCYC[4:0]字段中指定。在SDR和DDR模式下,持續時間被指定為一定個數的全時鐘周期。若DCYC為零,則跳過空指令周期階段,命令序列直接進入數據階段(如果存在)。空指令周期階段的操作模式由DMODE確定。為確保數據信號從輸出模式轉變為輸入模式有足夠的“周轉”時間,使用雙線和四線模式從Flash接收數據時,至少需要指定一個空指令周期。

(五)數據階段

在數據階段,可從Flash接收或向其發送任意數量的字節。在間接模式和自動輪詢模式下,待發送/接收的字節數在QSPI_DLR寄存器中指定。在間接寫入模式下,發送到Flash的數據必須寫入QSPI_DR寄存器。在間接讀取模式下,通過讀取QSPI_DR寄存器獲得從Flash接收的數據。在內存映射模式下,讀取的數據通過AHB直接發送回Cortex或DMA。數據階段可一次發送/接收1位(在單線SPI模式中通過SO)、2位(在雙線SPI模式中通過IO0/IO1)或4位(在四線SPI模式中通過IO0/IO1/IO2/IO3)。這可通過QUADSPI_CCR[15:14]寄存器中的ABMODE[1:0] 字段進行配置。若DMODE = 00,則跳過數據階段,命令序列在拉高nCS時立即完成。這一配置僅可用于僅間接寫入模式。

四、QSPI 與 SPI 異同比較

QSPI(Quad SPI)和SPI(Serial Peripheral Interface)是兩種串行通信協議,用于在主設備和從設備之間進行數據傳輸。它們有一些相似之處,但也有一些重要的區別。

(一)相似之處

串行通信本質 :二者均為串行通信協議,通過少量引腳實現數據傳輸,在硬件資源有限的場景下具有顯著優勢。

主從架構 :均基于主從結構,主設備主導通信發起與時序控制,從設備依主設備指令響應并完成數據交互,便于系統級的設備管理和任務調度。

(二)不同之處

傳輸速率差異 :QSPI 憑借四條數據線(Quad 模式)可同時傳輸四個數據位,支持更高傳輸速率;SPI 通常僅使用一條數據線,每次僅能傳輸一個數據位,傳輸速率相對較低。

總線模式多樣性 :QSPI 支持單線、雙線、四線等多種總線模式,可根據應用場景靈活選擇;SPI 一般僅支持單線模式,難以滿足對高帶寬有需求的復雜應用。

時鐘頻率范圍 :QSPI 為匹配高速數據傳輸,通常支持更高時鐘頻率;SPI 的時鐘頻率設計相對較低,適用于對實時性要求不苛刻的場景。

引腳占用情況 :QSPI 為實現四線模式高速數據傳輸,需更多引腳;SPI 僅需少量引腳即可完成基本通信功能,在簡單應用中硬件連接更為簡便。

片選信號運用 :QSPI 與 SPI 均使用片選信號(Chip Select)選擇通信從設備,但在復雜多設備系統中,QSPI 的多線模式可減少總線切換次數,提升整體通信效率。

總之,需要根據具體的應用需求和設備支持來選擇使用QSPI還是SPI。QSPI適用于需要更高傳輸速率和更大帶寬的應用,而SPI適用于傳輸速率要求不高的應用。

)

)