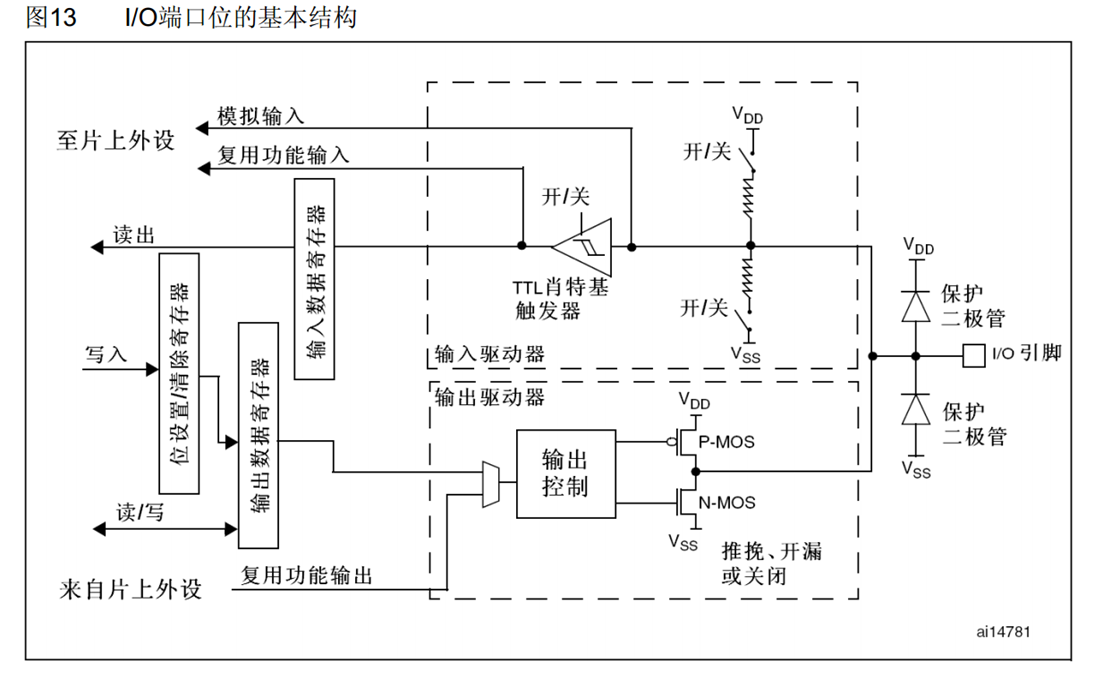

一、GPIO總體結構

?總體構成

1.APB2(外設總線)

APB2總線是微控制器內部連接CPU與外設(如GPIO)的總線,負責CPU對GPIO寄存器的讀寫訪問,支持低速外設通信

2.寄存器

控制GPIO的配置(輸入/輸出模式、上拉/下拉等)和狀態讀取(輸入電平、輸出電平等)

3.驅動器

GPIO驅動器負責將寄存器中設置的電平信號轉換為實際的電壓輸出,驅動外部負載。同時,驅動器也對輸入信號進行緩沖和整形,確保信號穩定傳輸到輸入寄存器,有著數據預處理作用

二、內部構造

某一個端口內部的結構??

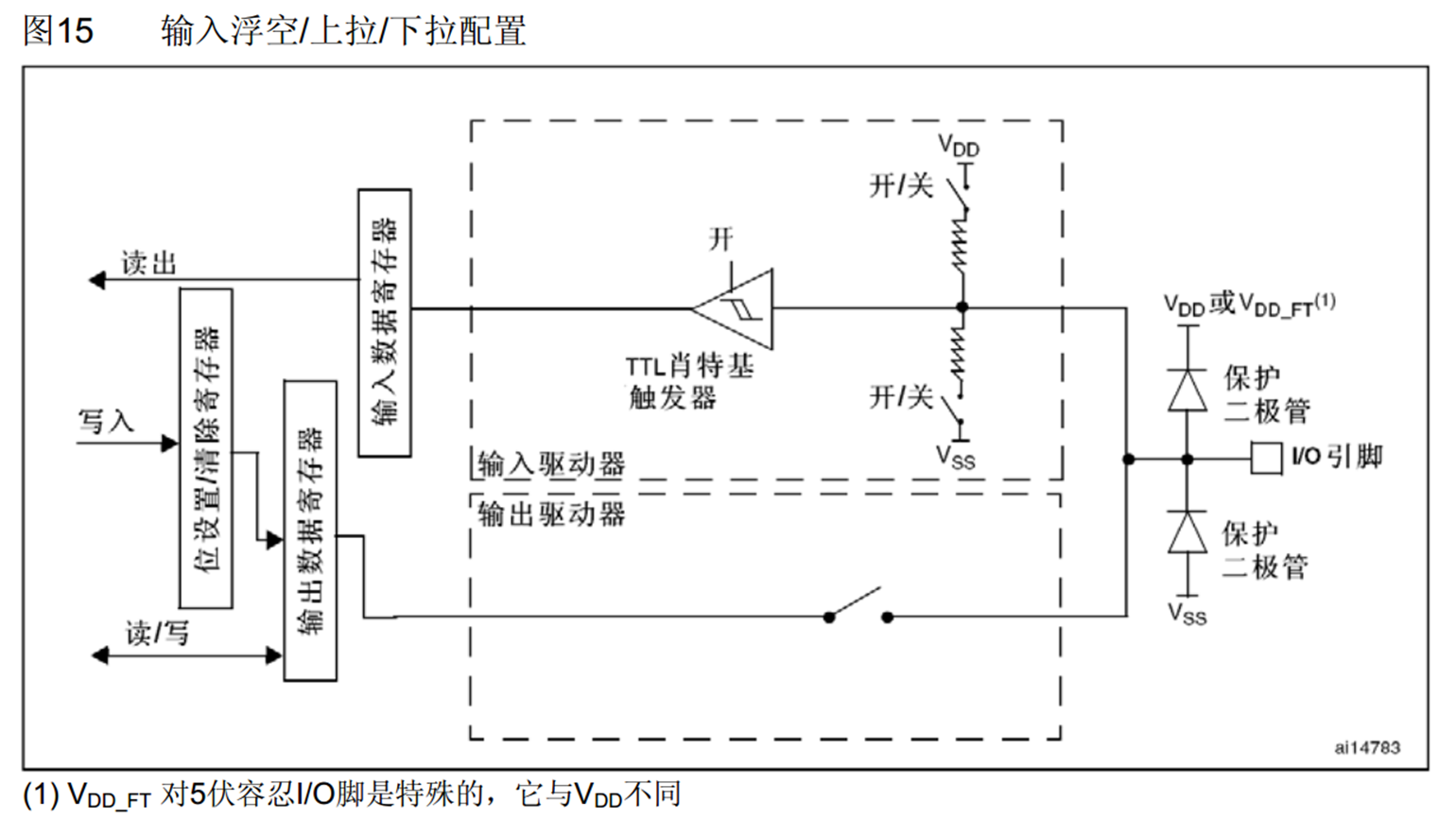

1.保護二級管

二極管具有單項導通性,在輸入情況下,當引腳電平低于Vss,Vss與引腳之間二極管導通,防止從GPIO內部汲取電流,同理,當引腳電平高于Vdd,引腳與Vdd之間二極管導通,防止GPIO內部電流過載。

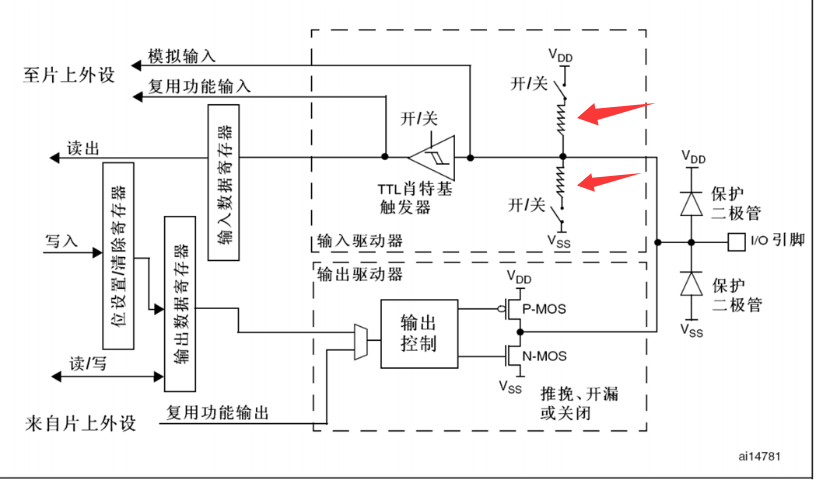

2.上拉電阻和下拉電阻

為了解決引腳懸空導致輸入電平不確定的狀態,以接上拉電阻為例,可以保證默認輸入電壓為高電平,為什么呢,因為GPIO內部的等效電阻非常大,與上拉電阻串聯,根據串聯分壓可以知道電阻的壓降很小,所以輸入等價于固定在高電平。那么為什么需要接上拉電阻呢,直接去掉不行嗎?我的理解是:如果去掉上拉電阻,那么當輸入引腳為0,那么輸入驅動器內部的Vdd與輸入引腳之間就短路,進而可能會導致元器件損壞。

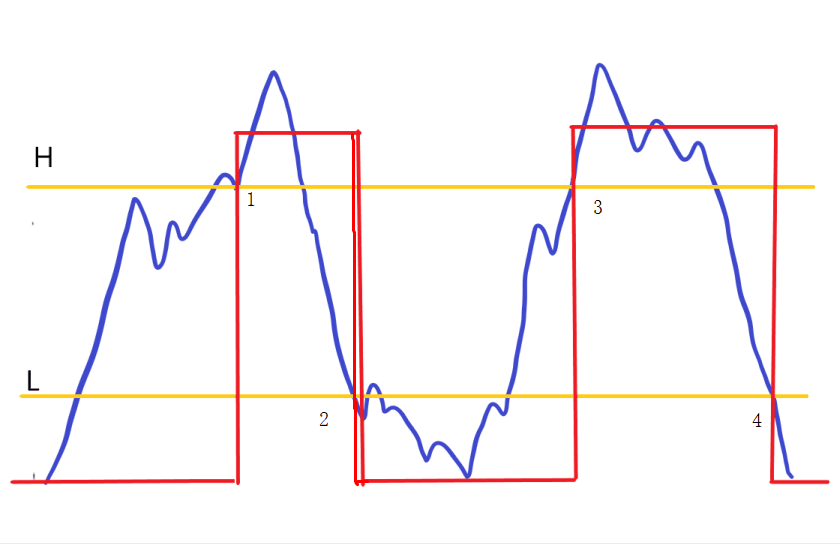

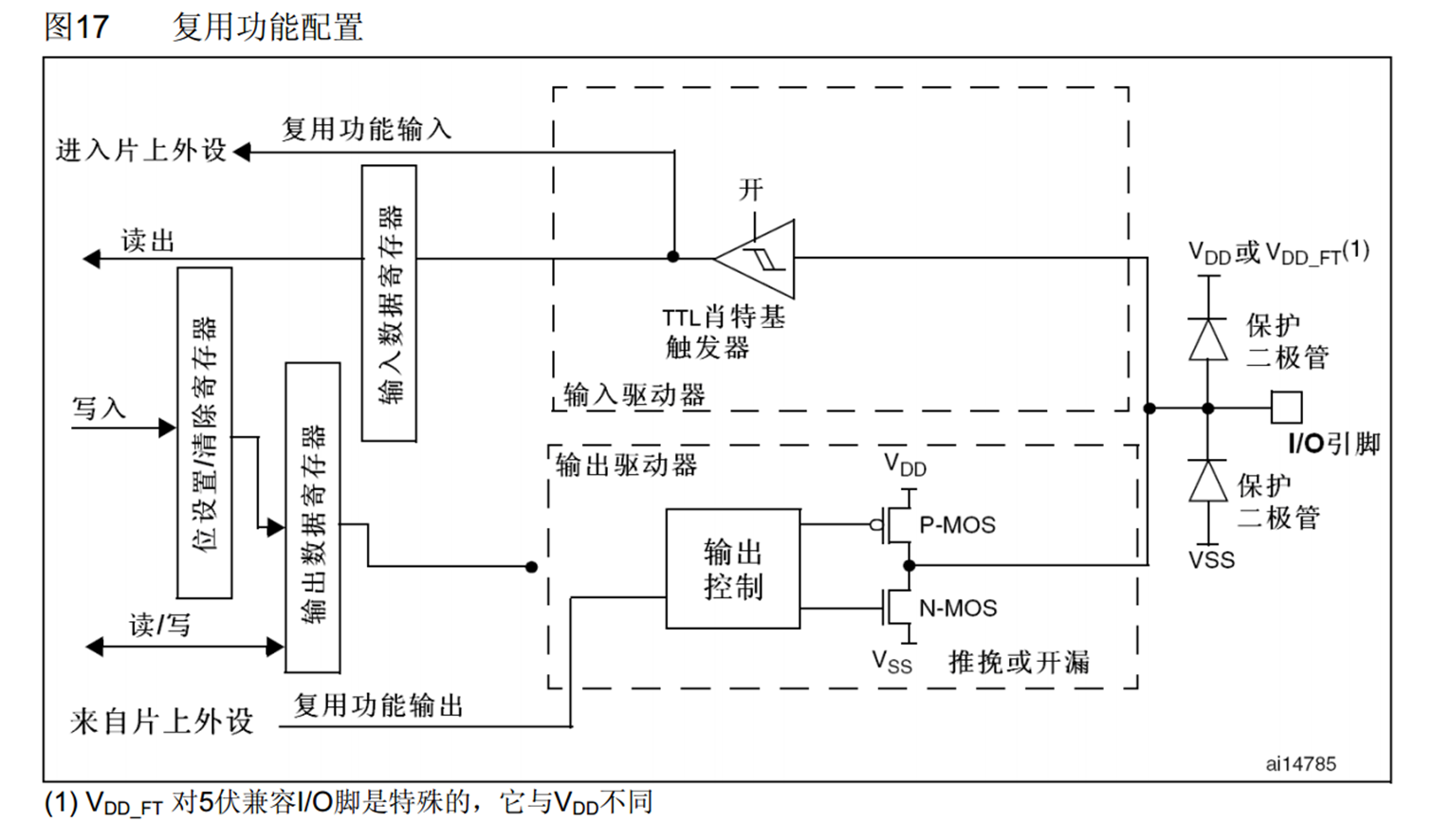

3.施密特觸發器(如圖中肖特基觸發器,翻譯錯誤)

用于對輸入電壓進行整型,提高輸入的穩定性,圖中輸入到輸入寄存器中的某一位,如下圖所示,只有電壓低于下線low或者高于上線low才會變化。同時由于片上外設ADC需要接受模擬量,因此可以在施密特觸發器整型之前獲取輸入的模擬量。

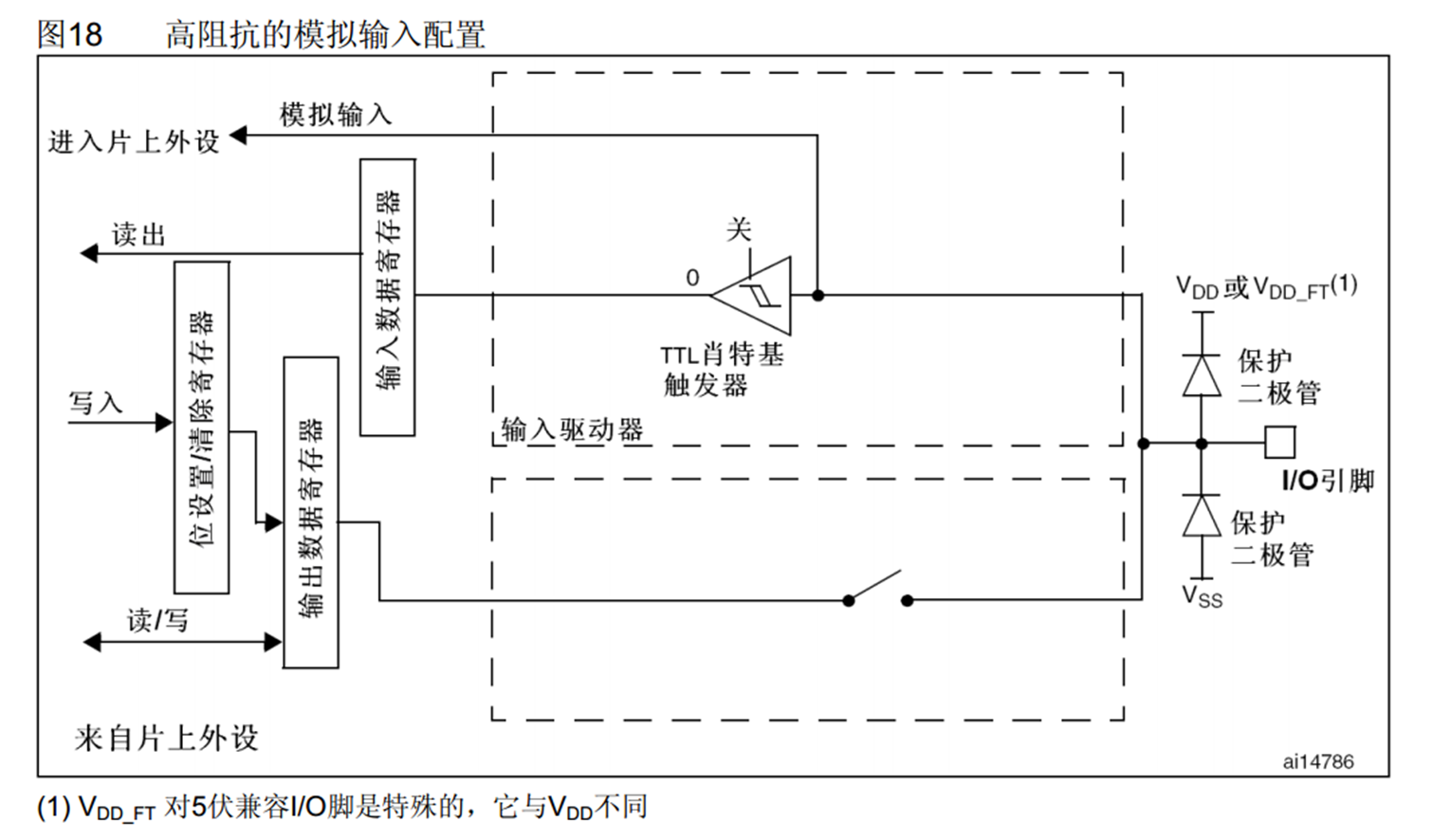

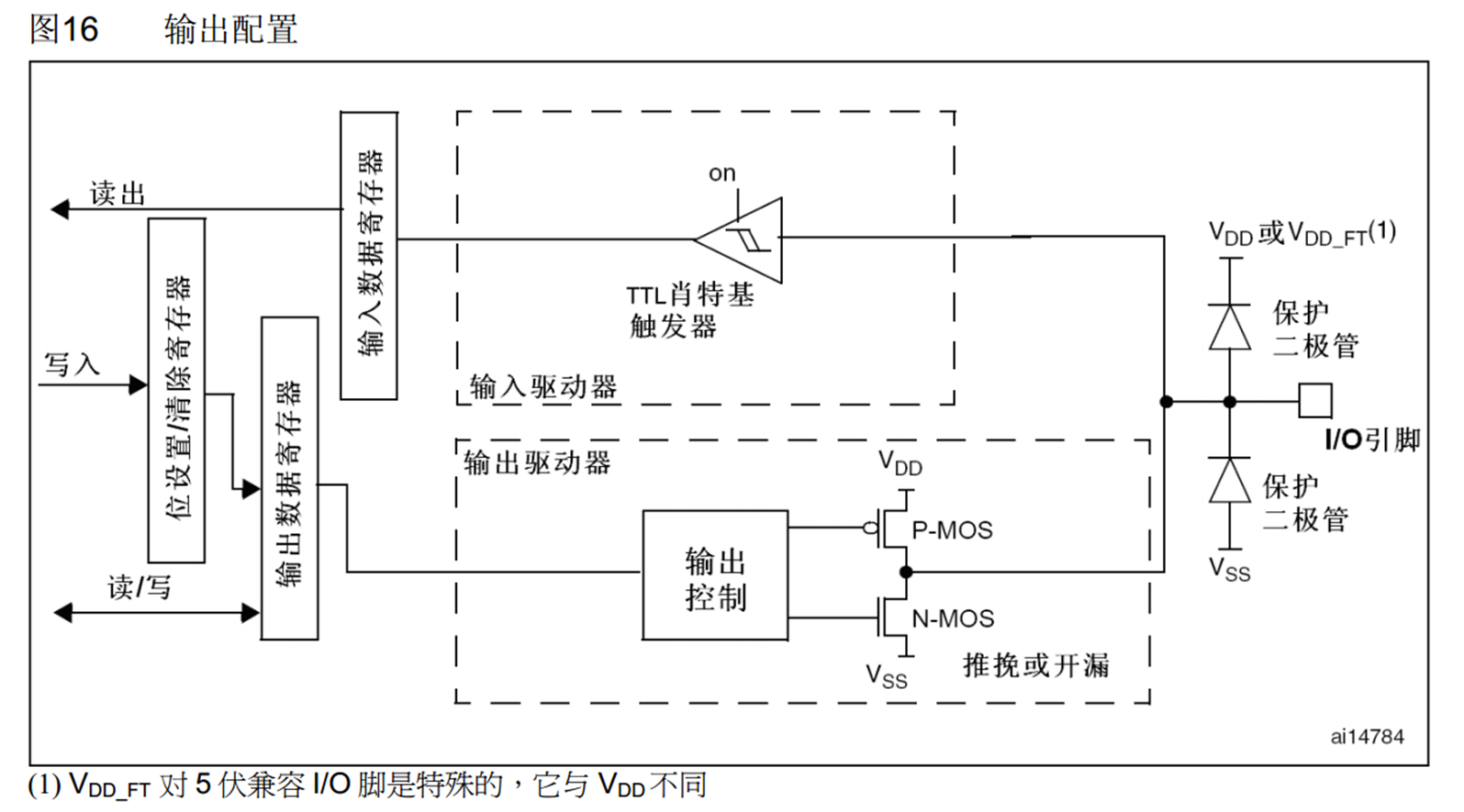

?4.端口輸出

?輸入設置如下,經過二路選擇器來選擇輸出的是GPIOx寄存器的指定比特位or復用功能信號。位設置/清楚寄存器可以用來操作寄存器中的某一位,而不影響其他位(輸出數據寄存器只能整體讀寫)。輸出控制,根據輸出寄存器的位信息,當輸出低電平,P-MOS導通,N-MOS截止,輸出高電平,反之輸出低電平。

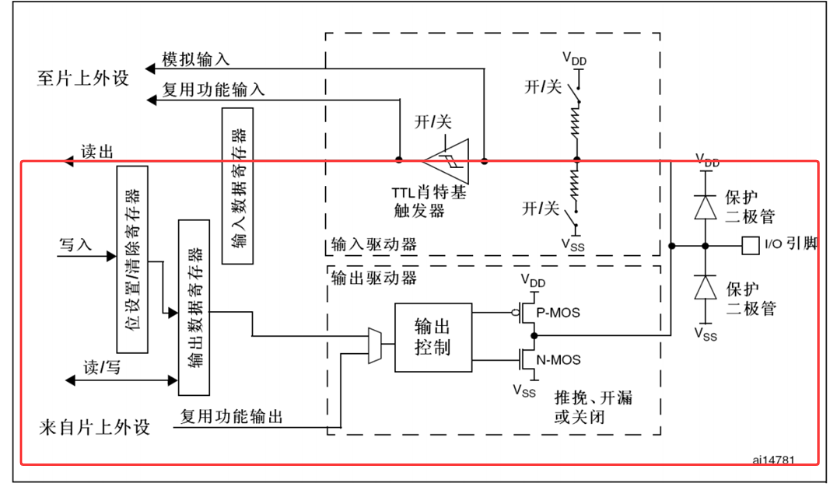

GPIO的八種工作模式?

1.浮空輸入、上拉輸入、下拉輸入

三種輸入方式在于是否連接上拉電阻和下拉電阻,這種模式下輸出控制斷開,只進行輸入。當引腳懸空時,浮空輸入電平不確定,上拉輸入電平默認高電平,下拉輸入電平默認低電平。

?2.模擬輸入

模擬輸入時,不連接上拉電阻和下拉電阻。

3.開漏/推挽輸出

當P-MOS無效,N-MOS有效,就是開漏輸出,這時候高電平為高阻態,這可以兼容不同的部件的高電平電壓值,把高電平值交給連接的部件決定(上拉輸入)。同時輸出情況下,可以保持正常讀的功能,感知輸出值,但是輸入情況下不能輸出,可能因為防止輸出高電平,輸入低電平導致短路。

?4.復用開漏/推挽輸出

只不過復用的輸出,引腳的電平是由片上外設所決定的。

)

)

)

)