仿真

鏈接:https://pan.baidu.com/s/1z9KFQANyNF5PvUPPYFQ9Ow?

提取碼:e3md

一、實驗目的

1、通過實驗,理解觸發的概念,理解JK、D等常見觸發器的功能;

2、通過實驗,加深集成計數器功能的理解,掌握利用集成計算器設計任意進制的計算器,并能在multisim中完成對設計計算器相關的仿真驗證;

二、實驗原理

1、JK、D觸發器的功能表見教材相關章節;

2、二進制和十進制計數器的功能見教材對應章節;

3、利用清零法或置數法使用集成計算器設計任意進制計數器,并在multisim中實現該電路的功能仿真和驗證;

三、實驗設備和器材

電腦、multisim電路仿真軟件(版本不限)

四、實驗內容和步驟

4.1 觸發器

在multisim器件庫選擇相應功能的芯片,完成下面實驗內容;

1.在multisim中選擇一JK觸發器芯片,簡述芯片功能,并完成其功能仿真驗證;

2.在multisim中選擇一JK觸發器芯片,簡述芯片功能,并完成其功能仿真驗證;

4.2 譯碼器

1.在multisim中選擇任一四位二進制集成計數器和一十進制集成計數器,簡述芯片功能;?

2.使用所選定十進制集成計數器芯片,設計一個模為二十四的計數器,要求技術范圍為“0~23”,并完成其功能仿真驗證;

3.使用所選定四位二進制集成計數器芯片,設計一個模為六十的計數器,要求技術范圍為“0~59”,并完成其功能仿真驗證;

五、實驗記錄和實驗結果

5.1 觸發器

-

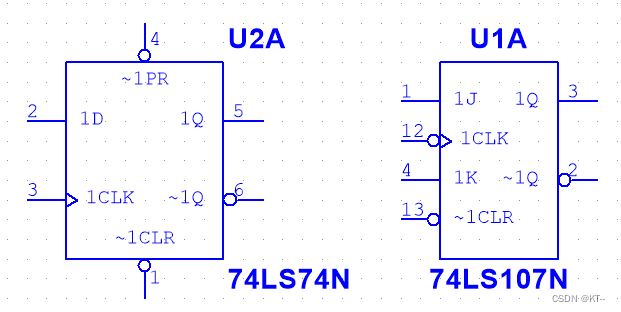

- 給出所選定的JK觸發器和D觸發器的型號、引腳圖,給出其功能表,并對功能做簡要描述(請預習時完成)

??

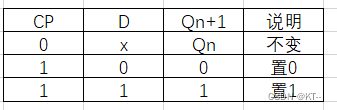

在clk上升沿到來之前,D輸入端無論輸入任何值觸發器狀態不會改變,次態等于現態。當時鐘上升沿到來時,與時鐘信號連接的非門產生的短暫延遲,使得觸發器狀態置成D輸入端的狀態。

在有效時鐘的脈沖邊沿沒到達時,即clk=0,或者clk=1,或者clk由高電平跳轉到低電平,,觸發器狀態不受輸入信號的影響,維持不變。

在時鐘上升沿信號到來時,觸發器的狀態將會隨著J與K的輸入產生相應的變化。

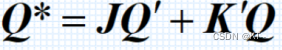

由JK觸發器特征方程

當J=0,K=0時,觸發器的狀態維持不變,Qn+1=Qn;

當J=1,K=1時,觸發器的狀態翻轉,Qn+1=?~Qn;

當J=1,K=0時,觸發器被置成1狀態;

當J=0,K=1時,觸發器被置成0狀態。

-

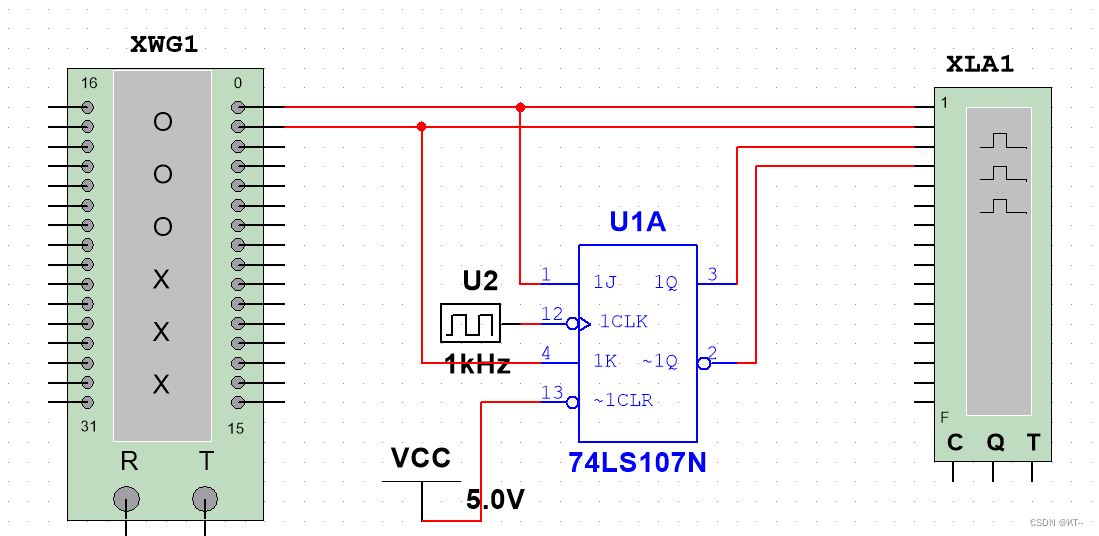

- 構造JK觸發器和D觸發器的功能仿真驗證電路和相關輸入信號,記錄仿真波形,并作簡要描述

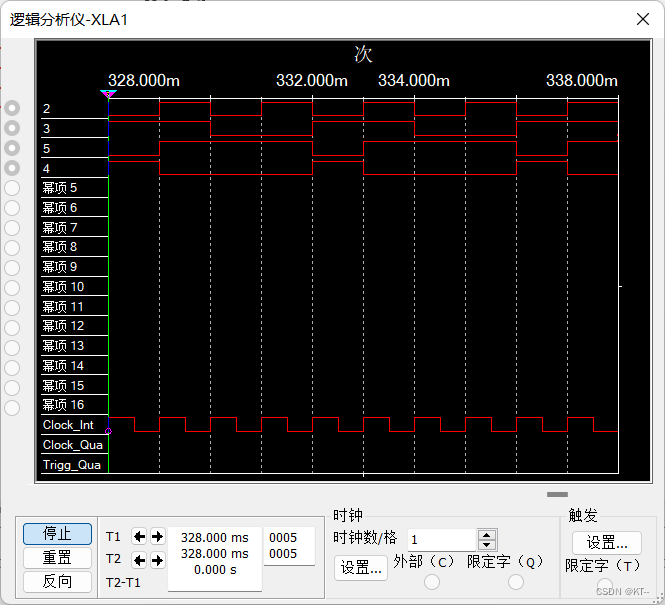

在時鐘上升沿信號到來時,J=1,K=1,觸發器的狀態翻轉,Qn由低電平變為高電平,-Qn由高電平變為低電平;當下一個上升沿到來時,J=0,K=0,觸發器狀態保持不變;再下一個上升沿到來時,J=1,K=0,觸發器置1,Qn為高電平,-Qn為低電平;再下一個上升沿信號到來時,J=0,K=1,此時,觸發器置0,Qn變為低電平,-Qn為高電平,然后觸發器以以上順序進行四個一組的周期循環。

在時鐘信號上升沿到來之前,D輸入端無論輸入任何值觸發器狀態不會改變。時鐘信號到來時,觸發器的狀態為D輸入的狀態。所以仿真成功。

5.2 集成計數器

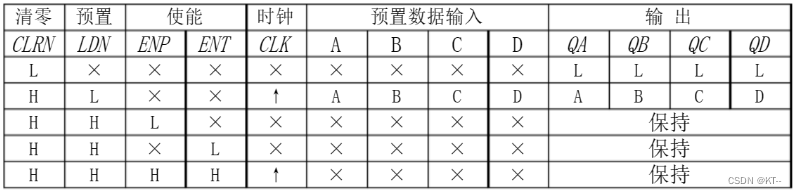

1.給出所選定的二進制和十進制集成計數器的型號、引腳圖,給出其功能表,并對功能做簡要描述(請預習時完成)

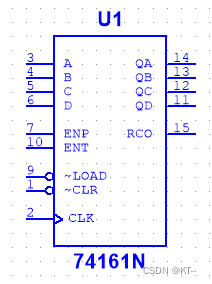

74161N是常見的四位二進制加法計數器,A B C D為置數的數字輸入端(其中D為最高位,A為最低位),在實現置數功能時會將ABCD的數值傳遞到QA QB QC QD。

ENP和ENT為使能端,這兩個端口都為1時才能讓芯片實現正常工作實現計數功能,其中只要有一個為0那么這款161就會保持狀態不進行計數。

~Load為置數端,如果該端口接收到0信號,那么進行置數功能,將ABCD傳遞給Q(ABCD)。

~CLR為清零端,如果該端口接收到0信號,那么此刻不管處于什么狀態,Q(ABCD)都會輸出0000,即實現了復位功能。

CLK為時鐘脈沖的輸入端,在上升沿到來時會計數一次。

RCO為進位端,當Q(DCBA)為1111時,該端口會輸出1信號,其余狀態皆輸出0信號。

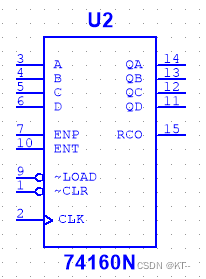

74160N是常用的十進制計數器,它具有異步清除端與同步清除端不同的是,它不受時鐘脈沖控制,只要來有效電平,就立即清零,無需再等下一個計數脈沖的有效沿到來。

1.異步清零功能

只要(CR的非)有效電平到來,無論有無CP脈沖,輸出為“0”。在圖形符號中,CR的非的信號為CT=0。其實,很容易解釋,由于異步清零端信號一旦出現就立即生效,如剛出現0111,就立即送到(CR的非)端,使狀態變為0000。所以,清零信號是非常短暫的,僅是過度狀態,不能成為計數的一個狀態。清零端是低電平有效。

2.同步置數功能

?當(LD的非)為有效電平時,計數功能被禁止,在CP脈沖上升沿作用下D0~D3的數據被置入計數器并呈現在Q0~Q3端。如在D0~D3置入0000,則在Q0~Q3端呈現的數據就是0110。

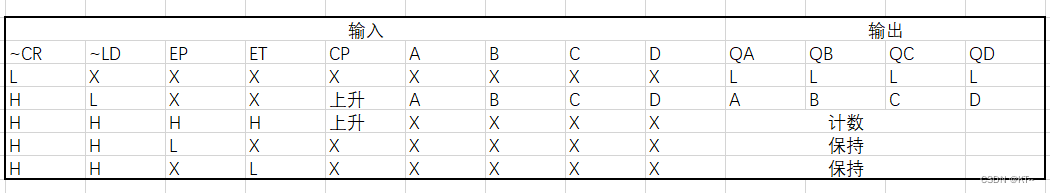

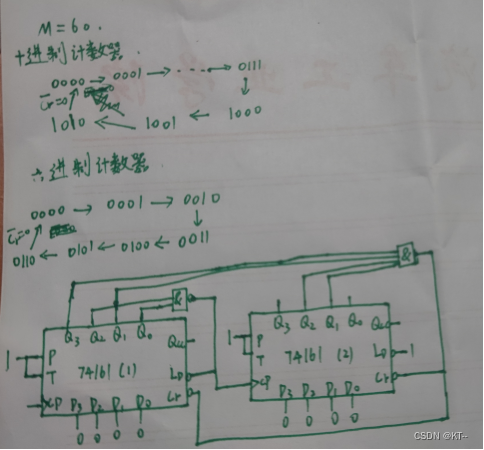

- 計數器設計(模為二十四);

1)畫出狀態轉換圖和所設計電路,并作簡要說明(請預習時完成)

第一個是二進制的計數器74161,使用置數法構成的模為二十四的計數器。

第二個是十進制的計數器74160,使用清零法構成的模為二十四的計數器。

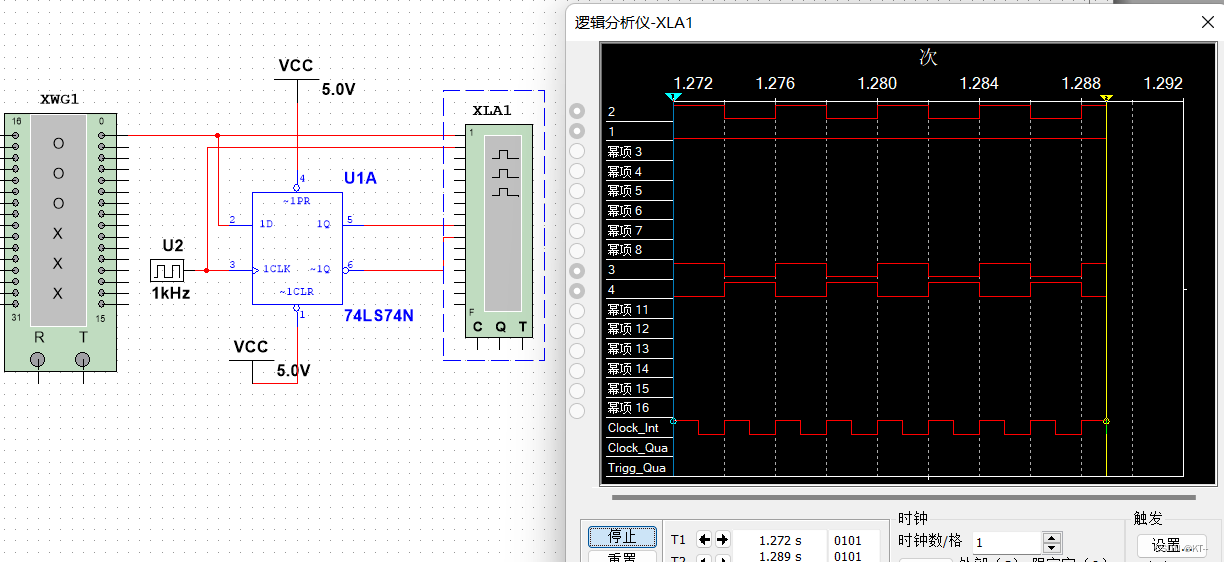

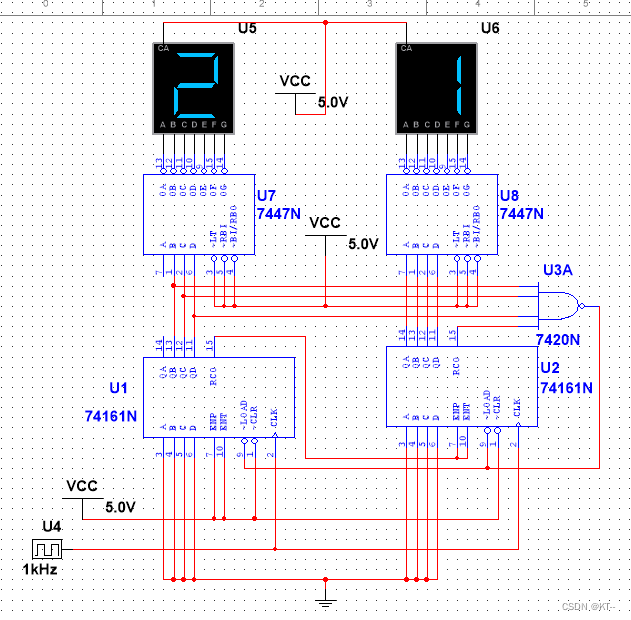

2)利用相關工具構造相關輸入信號,完成對電路功能的仿真驗證,并記錄仿真波形,并做簡要說明。

上面計數器為同步二進制置數加法計數器,U2為高位,U1為低位。當時鐘上升沿或復位下降沿到來時,如果有效,則計數器置數(0000 0000)。計數器的計數過程為,當輸出信號的低4位從0(0000)計數到15(1111)后,高4位計數加1,當計數到23(0001?0111)時,計數器重新清零,然后重新開始計數。

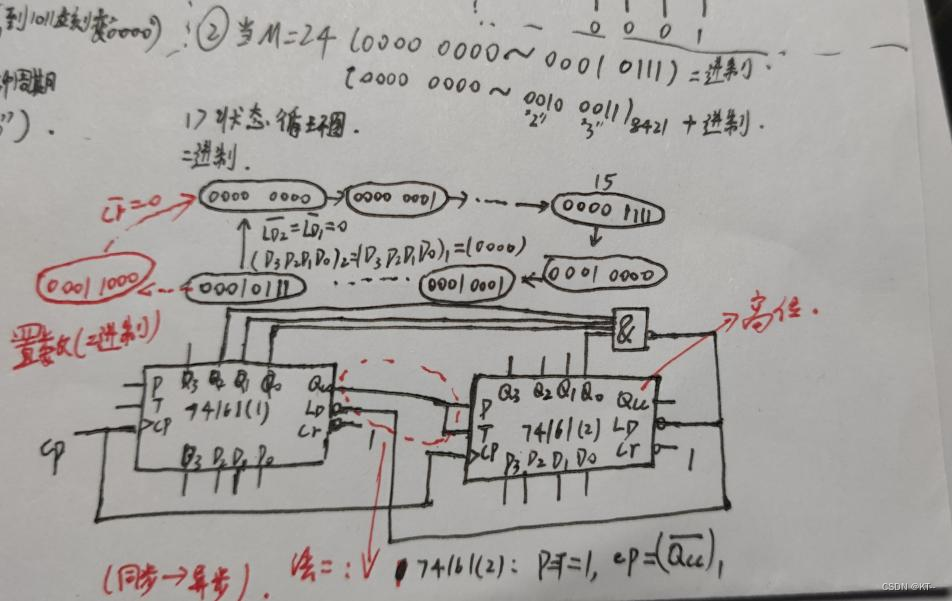

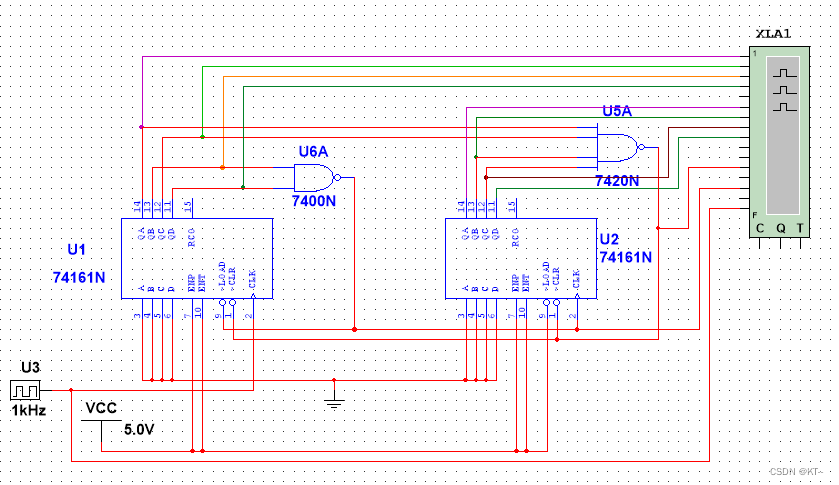

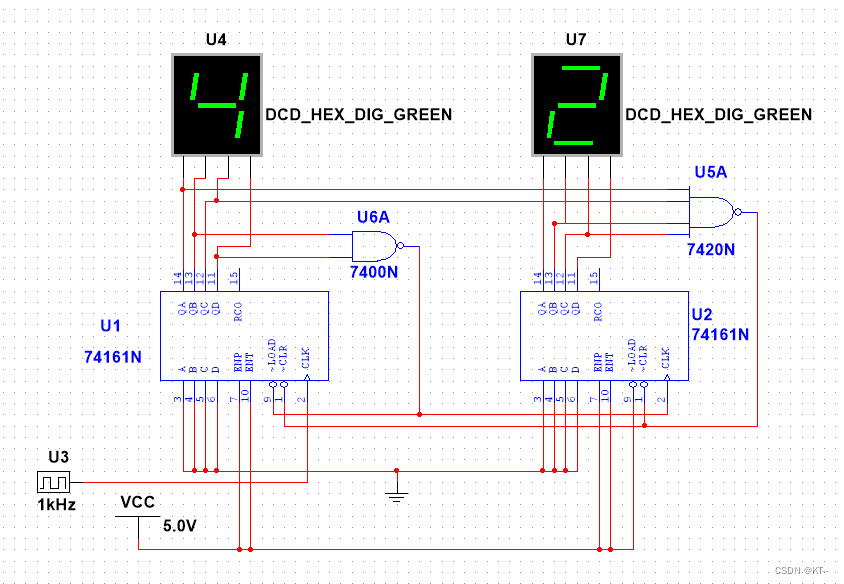

- 計數器設計(模為六十);

1)畫出所設計電路,并作簡要說明(請預習時完成)

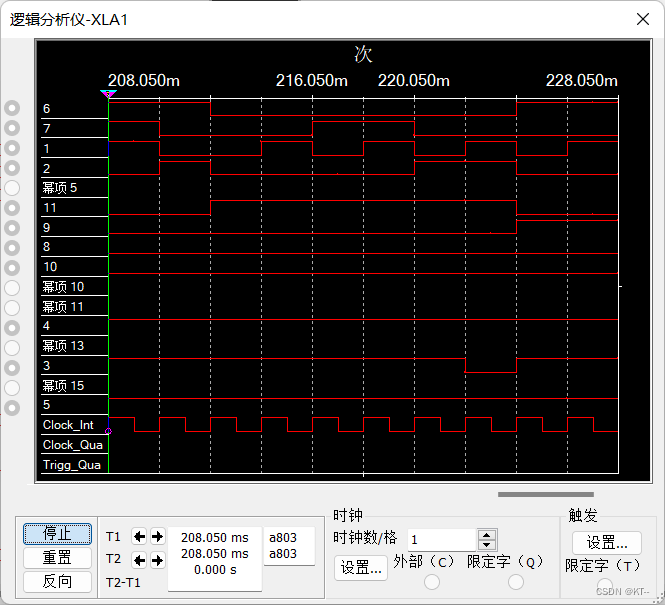

六十進制計數器由一個模6的計數器和一個模10的計數器組成,模10的計數器完成一個周期時輸出信號給模6計數器,當模10計數器計數到達10時則清零,同時給模6計數器一個信號,開始計一個數,模6計數器達到6時則清零。模6計數器選擇QB,QC端做反饋端,經過與非門輸出控制清零端CLR,形成6進制計數形式。

2)利用相關工具構造相關輸入信號,完成對電路功能的仿真驗證,并記錄仿真波形,并做簡要說明。

當出現數字五十九時,就開始清零,可以驗證電路功能正常。

六、實驗預習要求

- 實驗前認真閱讀本實驗指導;

- 熟悉multisim中相關操作及相關器件。

- 完成四和五中要求預習時完成的內容。

七、思考題。

1、完成對時序邏輯電路設計、功能仿真及驗證的步驟有哪些,與組合邏輯電路有何異同?

時序邏輯電路的設計、功能仿真和驗證步驟如下:

1、確定設計要求和規格書,包括輸入信號、輸出信號、時序參數等。

2、進行電路結構設計,包括選擇基本邏輯門、寄存器等,確定電路的輸入、輸出和時鐘信號等。對于計數器的實現,先寫計數循環圖,再根據循環圖以及所選用的計數器,確定該計數器采用置數法或清零法來設計電路圖。

3、進行功能仿真,使用仿真工具對設計的電路進行邏輯仿真,檢驗電路是否符合設計要求和規格書。

4、進行時序仿真,使用仿真工具對設計的電路進行時序仿真,檢驗電路的時序性能是否符合要求。

5、進行物理設計,包括布局和布線等,生成物理電路圖。

6、進行驗證,使用驗證工具對設計的電路進行驗證,檢驗電路是否符合設計要求和規格書。

時序邏輯電路和組合邏輯電路都是數字電路的兩種基本類型,它們有以下相同點:

1、都由邏輯門和觸發器等基本元件組成。

2、都可以使用布爾代數進行分析和設計。

3、都能實現邏輯運算和控制功能。

然而,時序邏輯電路與組合邏輯電路也存在一些區別:

1、組合邏輯電路的輸出僅取決于輸入,而時序邏輯電路的輸出還與過去的輸入和狀態有關。

2、時序邏輯電路引入了時鐘信號,需要考慮時序關系,而組合邏輯電路不需要。

3、時序邏輯電路的延遲和時序問題需要特別處理,而組合邏輯電路不需要考慮這些問題。

因此,時序邏輯電路的設計和驗證需要特別注意時序問題,并進行時序仿真和驗證。

)

)

)