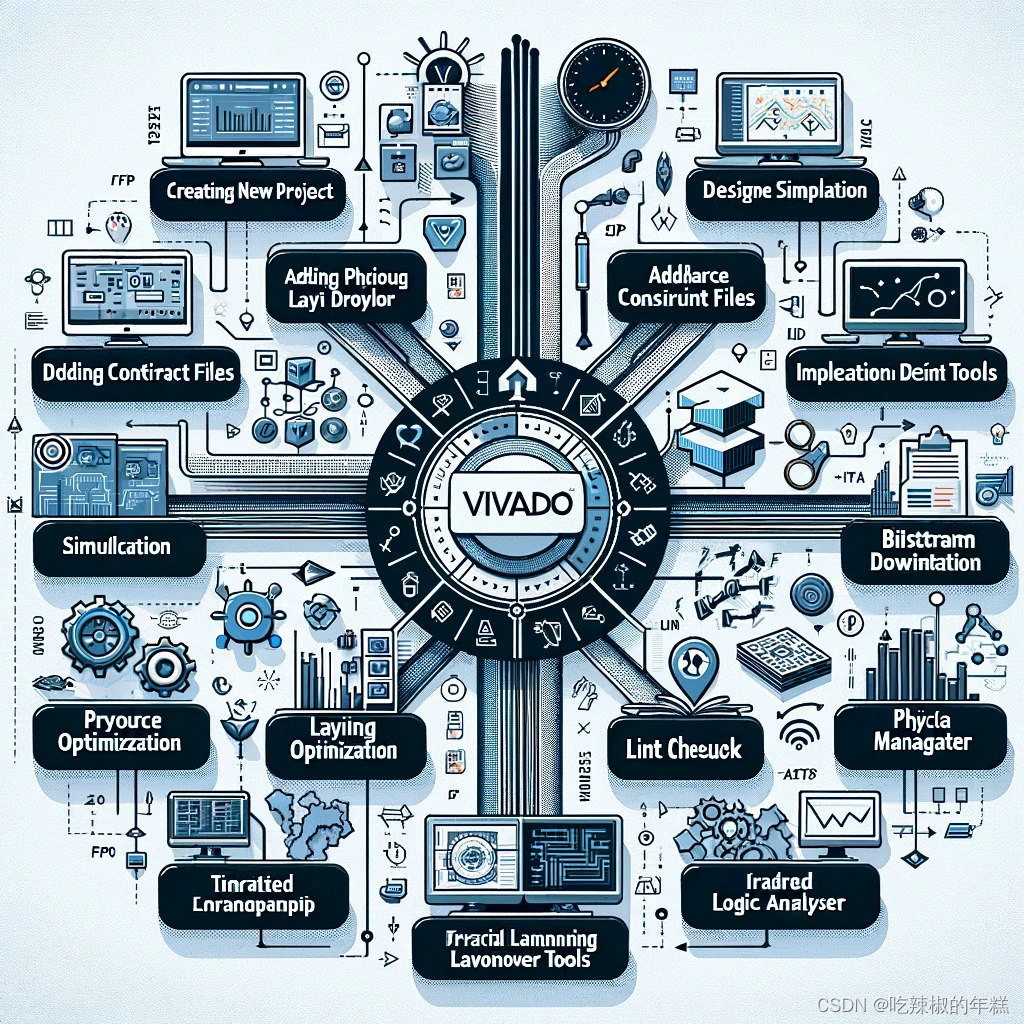

Vivado 是 Xilinx 公司推出的一款用于 FPGA 設計的集成開發環境 (IDE),提供了從設計輸入到實現、驗證、調試和下載的完整流程。本文將詳細介紹 Vivado 的使用方法,包括項目創建、設計輸入、約束文件、綜合與實現、仿真、調試、下載配置等步驟。

一、創建新項目

1.1 啟動 Vivado

打開 Vivado 應用程序,進入歡迎界面。

1.2 創建新項目

- 在歡迎界面選擇“Create New Project”。

- 輸入項目名稱和路徑。

- 選擇“RTL Project”,并勾選“Do not specify sources at this time”。

- 選擇目標器件(如 XC7Z020-1CLG484)。

- 點擊“Finish”完成項目創建。

二、設計輸入

2.1 添加設計源文件

- 在 Flow Navigator 面板中,選擇“Add Sources”。

- 選擇“Add or Create Design Sources”并點擊“Next”。

- 點擊“Create File”以創建新的 Verilog 或 VHDL 文件。

- 輸入文件名并選擇文件類型(Verilog/VHDL)。

- 點擊“Finish”完成文件創建。

2.2 編輯設計源文件

- 在 Sources 面板中,雙擊新創建的源文件以打開編輯器。

- 編寫設計代碼。例如,以下是一個簡單的 Verilog 模塊:

module led_blink (input wire clk,input wire rst,output reg led

);reg [23:0] counter;always @(posedge clk or posedge rst) beginif (rst) begincounter <= 24'd0;led <= 1'b0;end else begincounter <= counter + 1;if (counter == 24'd9999999) begincounter <= 24'd0;led <= ~led;endend

endendmodule

三、添加約束文件

3.1 添加約束文件

- 在 Flow Navigator 面板中,選擇“Add Constraints”。

- 選擇“Create File”并命名文件(如“constraints.xdc”)。

- 點擊“Finish”完成文件創建。

- 在 Sources 面板中,雙擊新創建的約束文件以打開編輯器。

- 添加引腳約束。例如:

set_property PACKAGE_PIN W5 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]set_property PACKAGE_PIN U16 [get_ports rst]

set_property IOSTANDARD LVCMOS33 [get_ports rst]set_property PACKAGE_PIN V17 [get_ports led]

set_property IOSTANDARD LVCMOS33 [get_ports led]

3.2 約束文件細節

引腳約束:指定 FPGA 器件的引腳連接。

時序約束:定義時鐘周期、輸入和輸出延遲、時鐘偏移等時序要求。例如:

create_clock -period 10.000 -name clk [get_ports clk]

set_input_delay -max 5.000 -clock clk [get_ports rst]

set_output_delay -max 5.000 -clock clk [get_ports led]

布線約束:定義特定信號的布線要求,避免電源噪聲和串擾。例如:

set_property PULLUP true [get_ports rst]

set_property DRIVE 12 [get_ports led]

3.3 約束文件的優化

- 確保時序約束的準確性,避免過于寬松或嚴格。

- 針對關鍵路徑設置合理的時序約束,保證時序收斂。

- 使用分層約束文件,便于管理和維護。

四、綜合與實現

4.1 運行綜合(Synthesis)

- 在 Flow Navigator 面板中,選擇“Run Synthesis”。

- Vivado 將開始綜合設計。完成后,查看綜合報告以確認無錯誤。

4.2 查看綜合報告

- 在 Flow Navigator 面板中,選擇“Open Synthesized Design”。

- 打開“Reports”選項卡,查看綜合報告中的時序、資源利用情況等信息。

時序報告:檢查所有路徑是否滿足時序要求。

資源利用報告:查看邏輯單元、寄存器、內存塊、DSP 等資源的使用情況。

4.3 運行實現(Implementation)

- 在 Flow Navigator 面板中,選擇“Run Implementation”。

- Vivado 將開始實現設計。完成后,查看實現報告以確認無錯誤。

4.4 查看實現報告

- 在 Flow Navigator 面板中,選擇“Open Implemented Design”。

- 打開“Reports”選項卡,查看實現報告中的布線、時序等信息。

布線報告:檢查布線是否合理,是否存在長路徑或高擁堵區域。

時序報告:再次檢查時序收斂情況,確保所有路徑滿足時序要求。

4.5 優化布線

- 調整約束:檢查和優化約束文件,確保時序約束和布線約束合理。

- 重復綜合和實現:多次運行綜合和實現過程,逐步優化設計。

- 使用物理布局工具:在 Vivado 中使用物理布局工具查看和調整關鍵路徑的布線。

4.6 布局和資源優化示例

資源優化示例

假設我們有一個簡單的計數器設計:

module counter(input wire clk,input wire rst,output reg [3:0] count

);always @(posedge clk or posedge rst) beginif (rst)count <= 4'b0000;elsecount <= count + 1;end

endmodule

資源利用報告:

- 在綜合完成后,查看綜合報告中的“Utilization Report”,檢查 LUT、FF、BRAM 和 DSP 的使用情況。

- 如果發現某些資源使用過多,可以嘗試以下優化:

- 重寫代碼以減少不必要的邏輯。

- 使用更高效的數據結構(如將組合邏輯轉換為查找表或存儲器)。

布局優化示例

- 在綜合和實現完成后,查看實現報告中的“Placement Report”和“Routing Report”。

- 檢查是否有信號的延遲過長或擁堵區域。

- 使用 Vivado 的“Floorplanning”工具進行手動布局優化:

- 將相關模塊放置在相鄰區域內,減少布線長度。

- 確保關鍵信號的路徑盡可能短,減少延遲。

- 示例:將計數器和 LED 驅動邏輯放置在相鄰的邏輯塊中。

五、仿真

5.1 添加仿真源文件

- 在 Flow Navigator 面板中,選擇“Add Sources”。

- 選擇“Add or Create Simulation Sources”并點擊“Next”。

- 點擊“Create File”以創建新的仿真文件(如“testbench.v”)。

- 輸入文件名并選擇文件類型(Verilog/VHDL)。

- 點擊“Finish”完成文件創建。

5.2 編寫測試平臺

- 在 Sources 面板中,雙擊新創建的仿真文件以打開編輯器。

- 編寫測試平臺代碼。例如:

module counter(input wire clk,input wire rst,output reg [3:0] count

);always @(posedge clk or posedge rst) beginif (rst)count <= 4'b0000;elsecount <= count + 1;end

endmodule

5.3 運行仿真

- 在 Flow Navigator 面板中,選擇“Run Simulation”。

- 選擇“Run Behavioral Simulation”。

- 仿真完成后,查看波形窗口以驗證設計行為。

5.4 波形查看和分析

- 在仿真過程中,可以使用 Vivado 仿真器查看波形圖。

- 在波形窗口中,選擇感興趣的信號,點擊“Add to Wave”以添加到波形視圖中。

- 使用“Zoom In”和“Zoom Out”工具調整波形視圖。

- 在波形視圖中,檢查信號的時序關系和邏輯行為,驗證設計的正確性。

5.5 仿真報告

查看仿真日志,確認所有測試用例通過,并且沒有錯誤和警告。

六、調試

6.1 設置調試探針

- 在設計源文件中插入 ILA (Integrated Logic Analyzer) 核。

- 例如,將以下代碼添加到 Verilog 模塊中:

ila_0 ila_inst (.clk(clk),.probe0(count)

);

6.2 配置調試核

- 在 Flow Navigator 面板中,選擇“Open IP Integrator”。

- 在 IP Integrator 中添加 ILA 核,并將其連接到設計中相應的信號。

6.3 運行調試

- 在 Flow Navigator 面板中,選擇“Run Implementation”。

- 生成比特流文件并下載到 FPGA。

- 打開硬件管理器,配置 ILA 并運行調試。

七、下載配置

7.1 下載比特流文件

- 連接 FPGA 開發板與計算機。

- 在 Flow Navigator 面板中,選擇“Open Hardware Manager”。

- 選擇“Open Target”,然后選擇“Auto Connect”。

- 選擇“Program Device”,并選擇生成的比特流文件進行下載。

7.2 驗證設計

- 確認 FPGA 已正確配置。

- 驗證設計功能是否符合預期。

八、綜合和實現的優化技巧

8.1 Lint 檢查

Lint 檢查用于在代碼綜合之前查找和修復代碼中的潛在錯誤和不規范寫法。

- 在 Flow Navigator 面板中,選擇“Open Synthesized Design”。

- 選擇“Report”->“Report DRC”進行設計規則檢查。

- 選擇“Report”->“Report CDC”進行時鐘域交叉檢查。

- 查看報告中的警告和錯誤信息,修改代碼以修復這些問題。

8.2 時序優化

- 在綜合和實現過程中,檢查時序報告,確保所有路徑滿足時序要求。

- 使用多重約束(Multi-Constraint)文件,根據不同的工作條件設置不同的時序約束。

- 調整代碼結構,優化關鍵路徑,減少路徑延遲。

8.3 資源優化

- 檢查資源利用報告,確保設計在目標 FPGA 上的資源利用率合理。

- 使用高效的數據結構和算法,減少資源消耗。

- 使用分層設計,將復雜模塊分解為多個子模塊,提高設計的可維護性和可擴展性。

8.4 物理布局優化

- 在物理布局階段,使用 Vivado 提供的布局工具,手動調整關鍵路徑的布局。

- 確保關鍵信號布線盡量短,減少布線延遲。

- 使用區域約束(Area Constraints),將相關模塊放置在相鄰的區域內,減少信號延遲。

8.5 布局和資源優化示例

假設我們有一個簡單的計數器設計:

module counter(input wire clk,input wire rst,output reg [3:0] count

);always @(posedge clk or posedge rst) beginif (rst)count <= 4'b0000;elsecount <= count + 1;end

endmodule

資源優化示例:

- 在綜合完成后,查看綜合報告中的“Utilization Report”,檢查 LUT、FF、BRAM 和 DSP 的使用情況。

- 如果發現某些資源使用過多,可以嘗試以下優化:

- 重寫代碼以減少不必要的邏輯。

- 使用更高效的數據結構(如將組合邏輯轉換為查找表或存儲器)。

布局優化示例:

- 在綜合和實現完成后,查看實現報告中的“Placement Report”和“Routing Report”。

- 檢查是否有信號的延遲過長或擁堵區域。

- 使用 Vivado 的“Floorplanning”工具進行手動布局優化:

- 將相關模塊放置在相鄰區域內,減少布線長度。

- 確保關鍵信號的路徑盡可能短,減少延遲。

- 示例:將計數器和 LED 驅動邏輯放置在相鄰的邏輯塊中。

九、實機條件下的調試

9.1 設置和配置調試核

- 在設計中添加 ILA 核,捕獲實際工作條件下的信號。

- 配置 ILA 核,選擇要捕獲的信號和觸發條件。例如:

ila_0 ila_inst (.clk(clk),.probe0(count)

);

9.2 運行實機調試

- 生成比特流文件并下載到 FPGA。

- 連接調試設備(如 JTAG 調試器)與 FPGA 開發板。

- 在 Vivado 中打開硬件管理器,選擇“Open Hardware Manager”。

- 選擇“Open Target”,然后選擇“Auto Connect”。

- 在硬件管理器中配置 ILA,設置觸發條件并捕獲信號數據。

- 分析捕獲到的波形數據,檢查信號時序和邏輯行為。

9.3 調試步驟示例

- 在硬件管理器中,選擇“Add Probes”添加需要監控的信號。

- 設置觸發條件,例如設置計數器達到特定值時觸發捕獲。

- 開始捕獲數據,運行 FPGA 設計,觸發器觸發時自動捕獲信號。

- 分析波形圖,檢查信號是否按照預期工作。

- 根據需要調整設計,重新生成比特流文件,并再次下載和驗證。

十、總結

Vivado 是一個功能強大的 FPGA 開發工具,提供了從設計輸入到實現、驗證、調試和下載的完整流程。本文詳細介紹了 Vivado 的使用方法,包括項目創建、設計輸入、約束文件、綜合與實現、仿真、調試、下載配置、優化技巧等步驟。通過這些內容的學習和實踐,可以有效提高 FPGA 設計的性能和可靠性。

:.NET Core 有什么優勢?)

)

: 現代IT管理的革命)

)