AXI Interconnect IP核內部包含一個 Crossbar IP核,用于在 Slave Interfaces(SI)和 Master Interfaces(MI)之間路由傳輸。在連接 SI 或 MI 到 Crossbar 的每條路徑上,可以選擇性地添加一系列 AXI Infrastructure cores(耦合器),以執行各種轉換和緩沖功能。這些耦合器包括 Register Slice、Data FIFO、Clock Converter、Data Width Converter 和 Protocol Converter。

這些耦合器的功能如下:

- Register Slice:通常用于在數據路徑中插入一個或多個寄存器級延遲,以便滿足時序要求或進行數據緩沖。

- Data FIFO:用于在數據傳輸過程中提供緩沖,以確保數據流的連續性和穩定性。當主設備和從設備之間的數據傳輸速率不匹配時,Data FIFO 可以起到平衡作用。

- Clock Converter:當主設備和從設備在不同的時鐘域中運行時,Clock Converter 負責將數據從一個時鐘域轉換到另一個時鐘域,以確保數據的正確同步和傳輸。

- Data Width Converter:當主設備和從設備的數據寬度不同時,Data Width Converter 負責將數據從一個數據寬度轉換到另一個數據寬度,以便在它們之間進行數據傳輸。

- Protocol Converter:當主設備和從設備使用不同的 AXI 子協議(如 AXI4、AXI3 或 AXI4-Lite)時,Protocol Converter 負責在它們之間進行協議轉換,以確保數據的正確傳輸。

AXI Interconnect IP核可以根據需要進行配置,以支持最多16個Slave Interfaces (SI) 和最多16個Master Interfaces (MI)。每個SI連接到一個AXI主設備,用于接收寫和讀事務請求。每個MI則連接到一個AXI從設備,并向從設備發出事務。

在AXI Interconnect IP核的中心是交叉開關(crossbar)IP核,它負責在SI和MI之間的所有AXI通道上路由傳輸。在SI和交叉開關之間或交叉開關和MI之間的每條路徑上,可以有一個或多個基礎核(infrastructure cores),它們執行各種轉換和存儲功能。

交叉開關有效地將AXI Interconnect IP核在SI相關功能單元(SI半球)和MI相關單元(MI半球)之間進行了分隔。

AXI Interconnect IP核的使用模型非常靈活,它可以將一個或多個AXI內存映射主設備連接到一個或多個內存映射從設備。每個連接的主設備可能是發起AXI事務的IP核(端點主設備),或者是上游AXI Interconnect IP核的級聯主接口。每個連接的從設備可能是AXI事務的最終目標(端點從設備),或者是下游AXI Interconnect IP核的級聯從接口。此外,連接的主設備或從設備也可以是AXI基礎轉換/存儲 IP核之一,盡管這些功能通常在AXI Interconnect IP核內部執行,以避免頂層設計的混亂。

每個AXI Interconnect IP核都可以配置為執行以下一般連接模式之一:

- N-to-1 互聯

- 1-to-N 互聯

- N-to-M 互聯(交叉開關模式)

- N-to-M 互聯(共享訪問模式)

互聯也可以配置為連接一個主設備到一個從設備,在這種情況下,IP集成器將自動實例化并配置路徑上所需的任何耦合器。

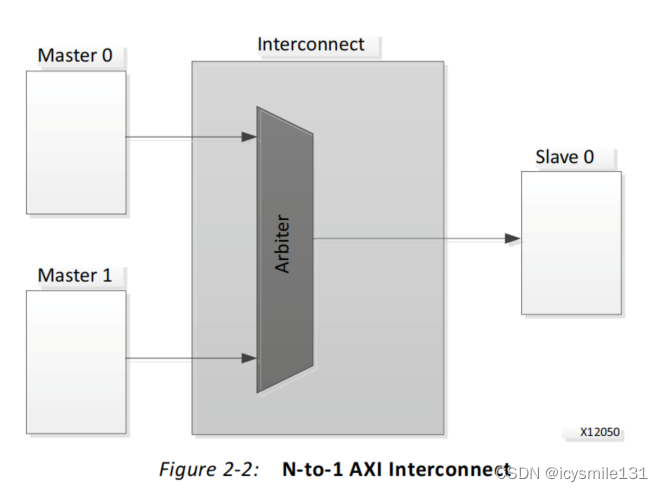

1 N-to-1 互聯

當多個主設備需要訪問單個從設備(如內存控制器)時,應使用N-to-1配置的AXI Interconnect IP核。

在這種配置中,還可以執行任何可選的轉換功能,如數據寬度和時鐘速率轉換,如圖2-2所示。通過AXI Interconnect IP核,多個主設備可以按照預定的優先級或仲裁機制訪問共享的從設備,同時保持數據傳輸的效率和正確性。

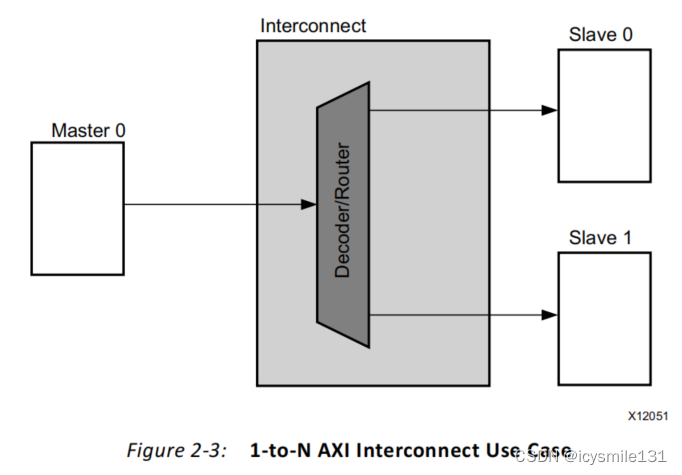

2 1-to-N 互聯

當單個主設備(通常是處理器)需要訪問多個內存映射的從設備(外設)時,應使用1-to-N配置的AXI Interconnect IP核。在這種情況下,不需要進行仲裁(在地址和寫數據路徑上),因為只有一個主設備在發送請求。

在1-to-N配置中,AXI Interconnect IP核將單個主設備的AXI事務路由到多個從設備。每個從設備通常代表一個不同的內存映射外設,如GPIO、UART、SPI等。由于沒有多個主設備競爭訪問,因此不需要進行仲裁。

圖2-3展示了這種配置的簡化示例,其中單個主設備通過AXI Interconnect IP核連接到多個從設備。AXI Interconnect IP核確保主設備的事務被正確地路由到目標從設備,同時可能還執行一些轉換或緩沖功能(如果需要)。

這種配置適用于需要處理器訪問多個外設的嵌入式系統,其中處理器作為主設備,而各個外設作為從設備。通過使用AXI Interconnect核心,可以簡化系統設計,提高性能和可靠性。

3?N-to-M互聯

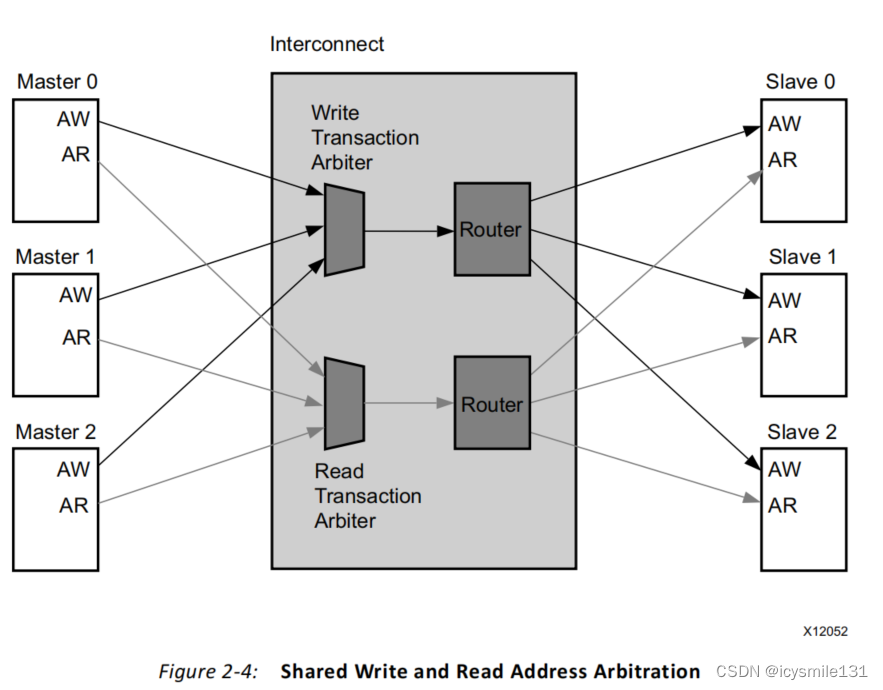

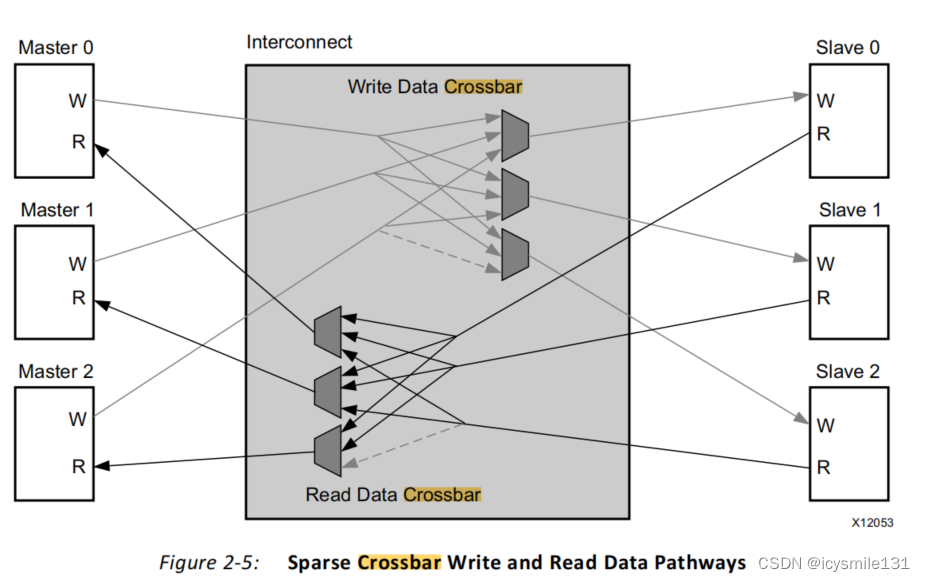

N-to-M互聯(交叉開關模式)是AXI Interconnect IP核的一種應用場景,它采用共享地址多數據(SAMD)拓撲結構,通過稀疏數據交叉開關連接,使用單一的共享寫和讀地址仲裁。

在這種模式下,AXI Interconnect IP核可以同時處理來自多個主設備(N個)的事務請求,并將它們路由到多個從設備(M個)。交叉開關的設計使得任何主設備都可以與任何從設備進行通信,從而實現了高度靈活的連接性。

圖2-4和圖2-5可能展示了這種配置的示意圖,其中可以看到主設備和從設備通過交叉開關進行連接,共享地址仲裁模塊負責處理所有設備的地址請求,確保數據能夠正確、高效地傳輸。

這些圖并非直接提供,但可以根據描述自行繪制或查找相關資料以獲取更詳細的信息。

在AXI Interconnect IP核的N-to-M互聯(交叉開關模式)中,根據配置的稀疏連接映射,每個SI(Slave Interface)槽位通過并行的寫和讀數據路徑連接到它可以訪問的所有MI(Master Interface)槽位。當多個源需要向不同的目標發送數據時,只要滿足AXI順序規則,數據傳輸就可以獨立且并發地進行。

通過禁用未使用的路徑,可以減少數據路徑復用邏輯和地址解碼邏輯,從而降低FPGA資源的利用率并加快時序路徑。

所有SI槽位的寫地址通道都輸入到中央地址仲裁器中,該仲裁器一次只允許一個SI槽位訪問。讀地址通道也采用相同的處理方式。每個仲裁周期的獲勝者將其地址信息傳輸到目標MI槽位,并將條目推入適當的命令隊列中,這些命令隊列使各種數據路徑能夠將數據路由到正確的目的地,同時強制執行AXI順序規則。

交叉開關模式僅在AXI Crossbar被配置為AXI4或AXI3協議時可用。這種模式允許在復雜的系統中實現高效且靈活的數據傳輸。

)

)

![[初學rust] 05_ rust struct](http://pic.xiahunao.cn/[初學rust] 05_ rust struct)