Verlog-流水燈-FPGA

引言:

? 隨著電子技術的飛速發展,現場可編程門陣列(FPGA)已成為電子設計自動化(EDA)領域中不可或缺的組件。FPGA以其高度的靈活性和可定制性,廣泛應用于通信、圖像處理、工業控制等多個領域。為了更好地理解和掌握FPGA的設計和應用,本實驗將通過一個簡單而經典的項目——流水燈設計——來引入Verilog硬件描述語言的使用。

希望你在本次學習過后,能夠有一定的收獲!!!

? 沖啊!!!! ?(?????)? ?(?????)? ?(?????)?

文章目錄

- Verlog-流水燈-FPGA

- 一、任務介紹

- 二、知識基礎

- 1、FPGA知識

- 2、Verilog知識

- 三、實驗內容

- 1、實驗代碼

- 2、實驗原理

- 3、實驗器材

- 4、引腳配置圖

- 四、實驗效果

- 五、總結

一、任務介紹

- 熟悉FPGA的開發流程

- 練習并且鞏固有關于verilog代碼的相關內容

- 使用Verilog語言編寫程序實現FPGA的流水燈效果

二、知識基礎

1、FPGA知識

FPGA概述: 現場可編程門陣列(Field Programmable Gate Array,簡稱FPGA)是一種集成了大量可配置邏輯塊(CLBs)的半導體設備。這些邏輯塊可以通過加載不同的配置文件(通常稱為位流文件)來重新定義其功能,從而實現不同的數字電路設計。FPGA的這種可重構特性使其在快速原型開發、復雜數字系統設計和驗證等領域非常受歡迎。

FPGA特點:

- 靈活性: FPGA的設計可以隨時更改,這使得它們非常適合于原型設計和快速迭代開發。

- 并行性: 由于FPGA內部的邏輯塊可以獨立編程和并行運行,因此它們可以同時執行多個操作。

- 低功耗: FPGA通常比專用集成電路(ASIC)更加節能。

- 成本效益: 對于小批量生產或需要定制化功能的產品,FPGA提供了一種成本效益高的解決方案。

FPGA設計流程:

- 概念設計: 確定項目需求和FPGA將執行的功能。

- 邏輯設計: 使用硬件描述語言(如Verilog或VHDL)編寫代碼,描述所需的邏輯功能。

- 仿真測試: 在計算機上模擬設計的邏輯,確保其按預期工作。

- 綜合: 將HDL代碼轉換成FPGA可以理解的門級表示。

- 布局與布線: 將邏輯映射到FPGA的具體物理位置,并連接各個邏輯塊。

- 位流生成: 生成配置文件,用于初始化FPGA。

- 下載與測試: 將位流文件下載到FPGA上,并進行實際測試。

FPGA在電子設計中的應用:

- 通信系統: FPGA被用于實現復雜的通信協議和信號處理。

- 視頻處理: 在視頻監控、圖像壓縮和顯示技術中,FPGA能夠處理高速數據流。

- 工業控制: FPGA用于實現定制化的控制算法和接口。

- 醫療設備: 在醫療成像和診斷設備中,FPGA可以提供必要的處理能力。

- 航空航天: 在航空航天領域,FPGA用于導航、遙感和飛行控制系統。

通過掌握FPGA的基礎知識,將能夠更好地理解流水燈實驗的硬件背景,并為后續的實驗步驟打下堅實的基礎。

2、Verilog知識

Verilog概述: Verilog是一種用于電子系統設計的硬件描述語言(HDL),它允許設計師以文本形式描述復雜的數字邏輯。Verilog語言由Gateway Design Automation公司于1983年開發,并于1989年成為IEEE標準(IEEE 1364-1989),隨后經過多次修訂,以適應不斷變化的設計需求。

Verilog特點:

- 結構化設計: Verilog支持模塊化和層次化的設計方法,使得大型設計可以被分解為更小、更易于管理的部分。

- 并發性: Verilog使用并發語句來描述系統中同時發生的事件,這與數字電路的工作原理相吻合。

- 可讀性: Verilog的語法類似于C語言,使得有編程背景的工程師更容易上手。

- 仿真能力: Verilog提供了強大的仿真工具,可以在實際硬件實現之前對設計進行測試和驗證。

Verilog語言基礎:

- 模塊(Module): Verilog設計的基本單位,每個模塊可以包含輸入、輸出和內部邏輯。

- 數據類型: 包括線網(wire)、寄存器(reg)、參數(parameter)等,用于定義信號和存儲數據。

- 操作符: 提供了位操作符、算術操作符、邏輯操作符等,用于構建邏輯表達式。

- 控制流: 使用

if-else、case、for、while等語句來描述條件和循環邏輯。

Verilog在FPGA設計中的應用:

- 行為描述: 用于描述模塊的功能,不涉及具體的邏輯門或電路實現。

- 數據流描述: 側重于信號之間的數學關系,常用于描述組合邏輯。

- 結構描述: 描述電路的物理實現,包括邏輯門、觸發器等的連接方式。

Verilog設計流程:

- 需求分析: 明確設計目標和性能要求。

- 設計編寫: 使用Verilog語言編寫模塊的代碼。

- 功能仿真: 對設計進行仿真,驗證其邏輯功能是否正確。

- 綜合: 將Verilog代碼轉換成適用于FPGA的門級描述。

- 時序仿真: 檢查設計的時序特性,確保滿足FPGA的時鐘要求。

- 布局布線: 在FPGA上安排邏輯和互連,優化性能和面積。

- 下載測試: 將設計下載到FPGA開發板上,進行實際測試和驗證。

三、實驗內容

1、實驗代碼

module led (input clk,input rst_n,output reg[7:0] led

);parameter TIME_1s = 25_000_000;reg [30-1:0] cnt_1s ; wire add_cnt_1s , end_cnt_1s ; always @(posedge clk or negedge rst_n) if (!rst_n)cnt_1s <= 30'b0;else if (add_cnt_1s )if (end_cnt_1s )cnt_1s <=30'b0;else cnt_1s <= cnt_1s +1'd1;else cnt_1s <= cnt_1s ;assign add_cnt_1s = 1'b1;assign end_cnt_1s = add_cnt_1s && (TIME_1s-1 == cnt_1s );always @(posedge clk or negedge rst_n)if(!rst_n)led <= 8'b0000_0001;else if(end_cnt_1s)led <= {led[6:0],led[7]};elseled <= led;endmodule

2、實驗原理

設計目標: 本實驗的目標是創建一個簡單的流水燈效果,即通過FPGA控制一組LED燈依次點亮,從而產生動態的視覺效果。

設計思路:

- 時鐘信號(clk): 提供整個設計的脈沖源,所有的邏輯變化都依賴于時鐘信號的上升沿。

- 復位信號(rst_n): 用于初始化和同步系統狀態,當復位信號為低時,系統將重置到初始狀態。

- LED輸出(led): 表示8個LED燈的狀態,每一位對應一個LED燈,1表示點亮,0表示熄滅。

核心邏輯:

- 1秒計數器: 使用一個30位的寄存器

cnt_1s來實現1秒的計數。由于FPGA的時鐘頻率通常遠高于1秒的倒數,因此需要通過計數來實現1秒的延遲。 - 計數控制信號:

add_cnt_1s和end_cnt_1s是控制cnt_1s寄存器的關鍵信號。add_cnt_1s始終為1,表示始終在時鐘上升沿增加計數;end_cnt_1s在計數達到TIME_1s - 1時為1,表示1秒時間已到。

實現步驟:

- 初始化: 當復位信號

rst_n為低時,cnt_1s寄存器清零,所有LED燈熄滅。 - 計數: 在每個時鐘上升沿,如果復位信號為高,則

cnt_1s寄存器增加1。 - 1秒判斷: 當

cnt_1s寄存器的值在時鐘上升沿達到TIME_1s - 1時,表示1秒時間已到,此時end_cnt_1s為1。 - LED狀態更新: 每當1秒時間到,將最左邊的LED狀態(

led[7])移動到最右邊(led[0]),其余LED狀態向左移動一位,從而實現流水燈效果。

代碼解析:

- 使用

always塊來描述在時鐘上升沿或復位信號下降沿時的行為。 if (!rst_n)判斷復位信號,如果是復位狀態,則重置cnt_1s和led。if (add_cnt_1s)和if (end_cnt_1s)用于控制計數器和LED狀態的更新。assign語句用于生成控制信號,add_cnt_1s直接賦值為1,而end_cnt_1s在計數達到預設的1秒時間時為1。

通過上述原理和實現步驟,可以清晰地理解流水燈FPGA設計的核心邏輯和工作流程。

3、實驗器材

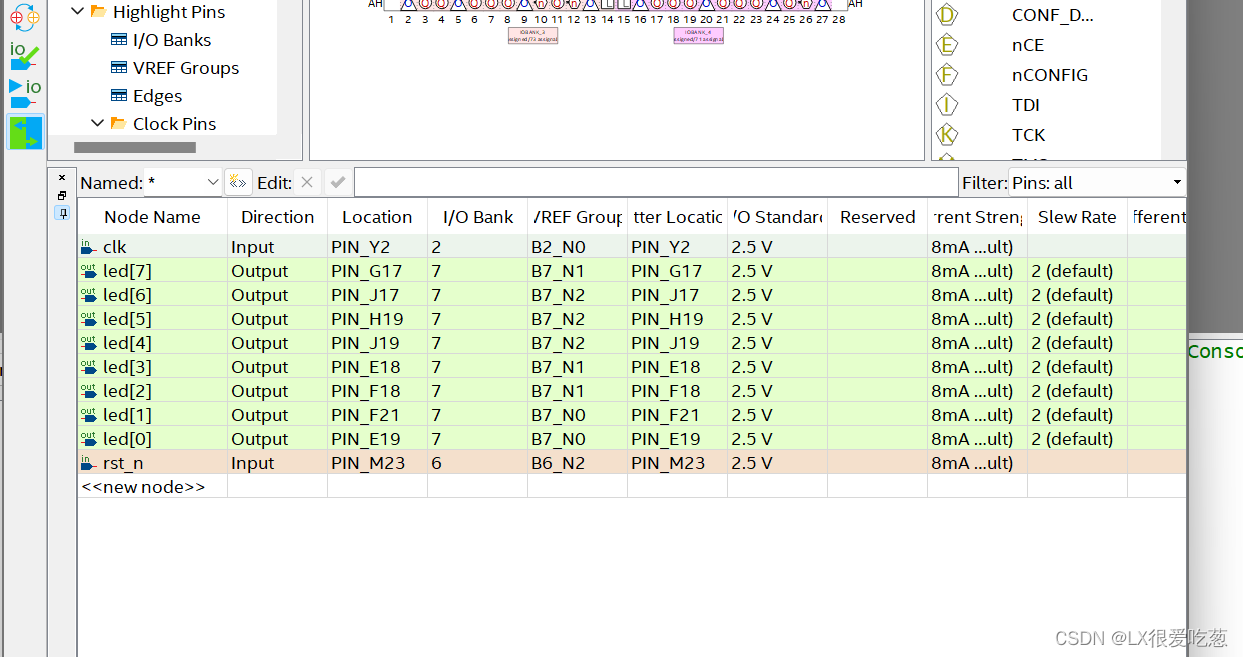

4、引腳配置圖

四、實驗效果

v-lsd

五、總結

實驗目的回顧: 本次實驗的核心目的在于通過實踐操作,熟悉FPGA的開發流程,并通過編寫Verilog代碼來實現FPGA的流水燈效果,以此來練習和鞏固Verilog編程的相關知識。

實驗過程概述:

- 理論學習: 首先需要了解FPGA的基本概念、特點以及設計流程,同時掌握Verilog語言的基礎語法和編程技巧。

- 環境搭建: 配置FPGA開發環境,包括安裝相應的軟件工具和硬件設備。

- 設計實現: 根據實驗原理,使用Verilog語言編寫流水燈模塊的代碼,并在開發環境中進行功能仿真。

- 硬件測試: 將編譯后的位流文件下載到FPGA開發板上,進行實際的硬件測試,觀察LED燈的流水效果。

實驗關鍵點:

- 時鐘和復位信號的處理: 理解時鐘信號在數字設計中的重要性,以及如何使用復位信號來初始化和同步系統狀態。

- 計數器的設計: 學習如何利用計數器產生定時信號,以實現LED燈的順序點亮。

- 狀態寄存器的更新: 掌握如何在Verilog中通過狀態寄存器來控制LED燈的狀態變化,實現流水燈效果。

實驗成果: 通過本次實驗,應能夠:

- 熟練掌握FPGA的設計流程和開發環境的搭建。

- 深入理解Verilog語言的編程方法,包括模塊定義、數據類型、操作符和控制流語句。

- 學會使用Verilog進行基本的數字邏輯設計,如計數器和移位寄存器。

- 能夠獨立完成從設計、仿真到硬件測試的整個FPGA設計過程。

實驗成果: 通過本次實驗,應能夠:

- 熟練掌握FPGA的設計流程和開發環境的搭建。

- 深入理解Verilog語言的編程方法,包括模塊定義、數據類型、操作符和控制流語句。

- 學會使用Verilog進行基本的數字邏輯設計,如計數器和移位寄存器。

- 能夠獨立完成從設計、仿真到硬件測試的整個FPGA設計過程。

未來展望: 流水燈實驗是FPGA設計的一個基礎入門項目。未來,可以在此基礎上探索更復雜的設計,如加入傳感器輸入、實現更復雜的邏輯控制、或者設計具有特定功能的數字系統。

)

函數和stoll函數)

-百變屏幕無壓力,這才是Android屏幕適配的終極解決方案)

----單級放大器(共源極))