1:能不復位盡量不要復位,減少邏輯扇出數:比如打拍信號。

2:xilinx的FPGA推薦高復位,ATERAL的FPGA推薦低復位。

3:盡量使用異步復位:大多數廠商目標庫內的觸發器都只有異步復位端口,采用同步復位需消耗較多邏輯資源。

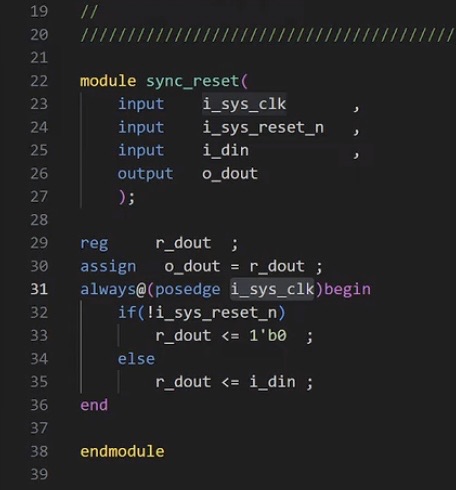

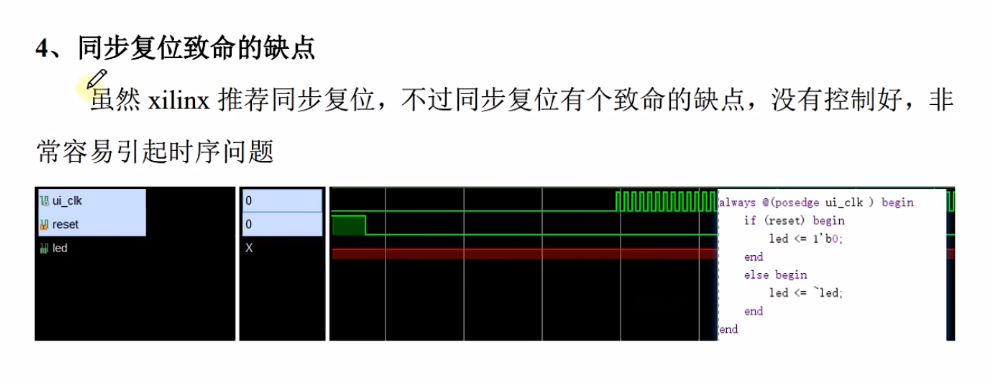

一:同步復位

1優點?:比較容易滿足時序,都在時鐘上升沿才觸發。

2缺點:

2.1復位有延遲,有可能復位開始了由于要在時鐘沿才有效所以并未及時響應。

2.2異步復位更加消耗邏輯資源。

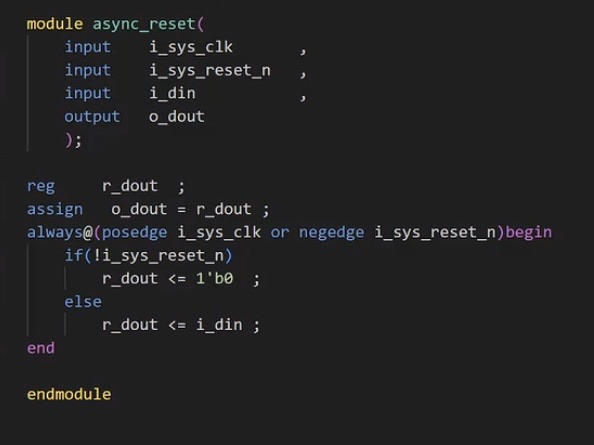

二異步復位:

1優點:復位響應及時,因為不需要在時鐘沿才響應

2缺點:

2.1:因為是異步信號,容易導致亞穩態 。

2.2:復位信號只要有點干擾,就會導致復位響應。

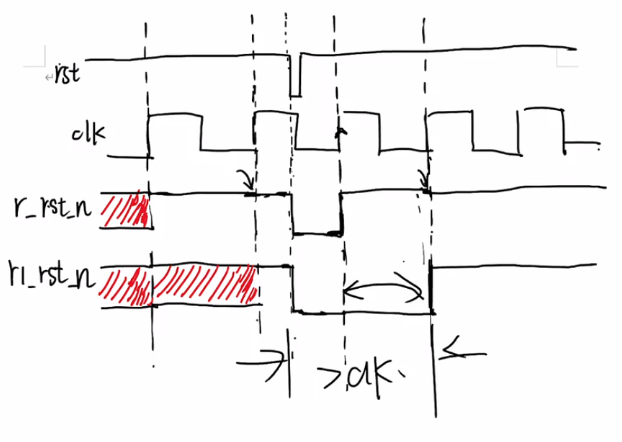

三:異步復位同步釋放——推薦實戰就用這個方式復位

module rst(input sys_clk ,input sys_rst_n ,input data_in ,output reg data_out

);reg sys_rst_n_reg0;

reg sys_rst_n_reg1;//對復位信號打兩拍

always @(posedge sys_clk or negedge sys_rst_n)beginif(!sys_rst_n)beginsys_rst_n_reg0 <= 1'b0;sys_rst_n_reg1 <= 1'b0;end else beginsys_rst_n_reg0 <= sys_rst_n;sys_rst_n_reg1 <= sys_rst_n_reg0;end

end //使用同步后的復位信號對數據進行復位

always @(posedge sys_clk or negedge sys_rst_n_reg1)beginif(!sys_rst_n_reg1)data_out <= 1'b0;else data_out <= data_in;

end endmodule

優點:

只要異步復位信號出現一點毛刺復位都能使系統復位。有人會說這算啥優點和異步復位電路一樣缺點太神經質了,萬一人家根本不想復位呢。——

1.1系統不希望出現X態,異步復位電路由于未作同步釋放,有可能出現一個及其窄的復位電平,導致有的慢時鐘域處于未復位狀態,有點快時鐘域處于復位狀態,有的臨界時鐘域剛好采集到沿上處于亞穩態(X)。而同步釋放如圖進行在本時鐘域打拍延拓了復位周期,本時鐘域都能采集到穩定復位信號。

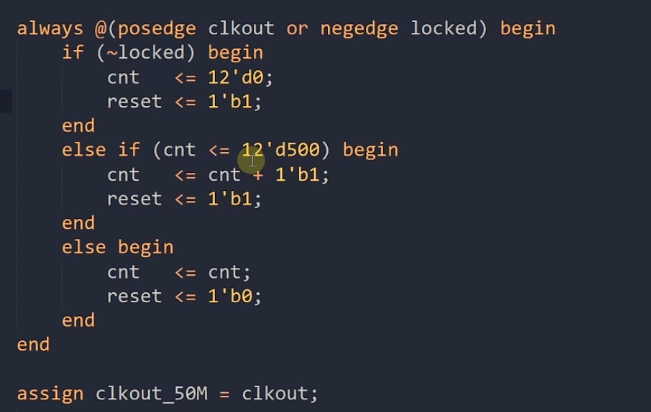

四:復位信號的來源——由于實際運用不太可能用按鍵復位,一般就用pll的locked信號

優點1:因為是Xilinx平臺,所以產生的reset信號是高復位。

優點2:時鐘lock后并未馬上釋放復位,而是等時鐘完全穩定后在釋放復位信號。

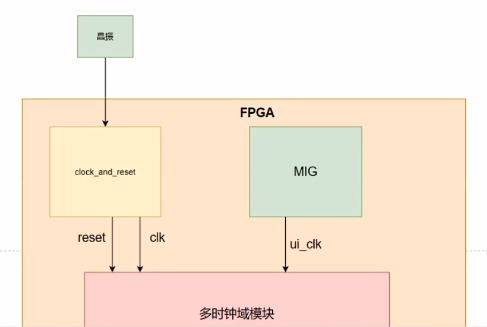

五案例:遇到mig的ui_clk,需要我們lock制造的異步復位信號,來復位整個系統。

此時我們就需要使用異步復位同步釋放+加上一段時間的時鐘穩定計數器操作即可。

?

?

?

?

)

】 需求工程之:面向對象需求分析方法:統一建模語言(UML)(下))

)

圖表--儀表盤)