目錄

一、任務

二、分析

三、代碼

四、實驗現象

五、更新

一、任務

使用VGA實現彩條顯示,模式是640x480@60。

二、分析

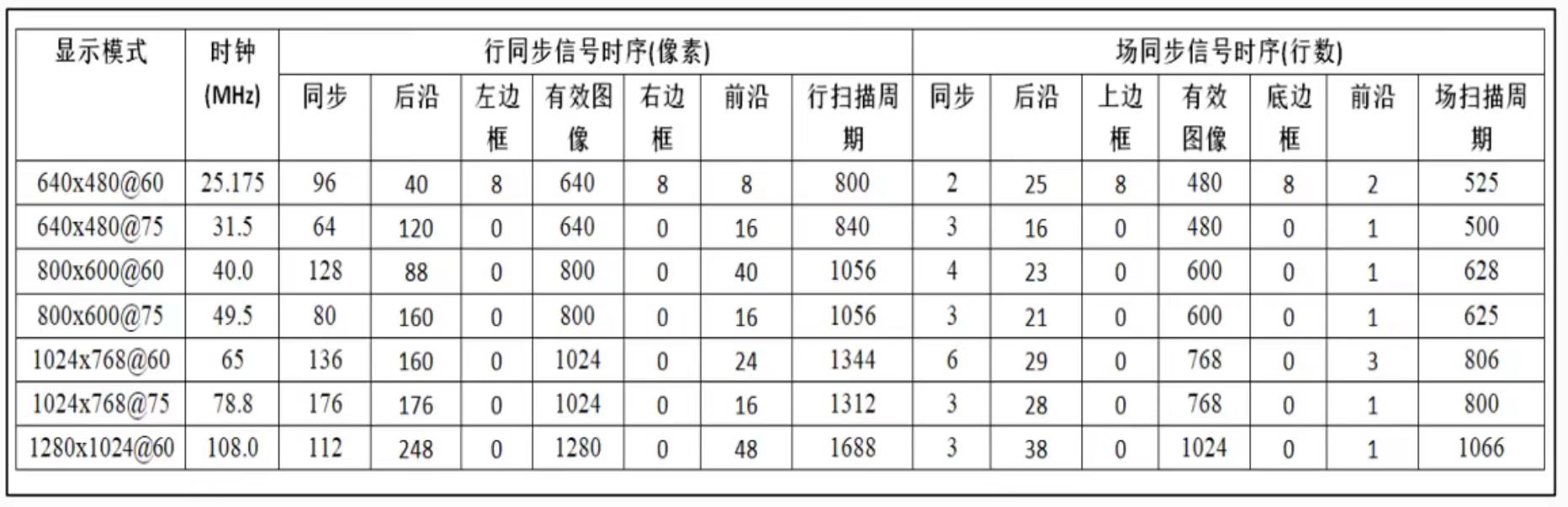

????????首先,模式是640x480@60,那么對照以下圖標,知道其它信息,不清楚時序和VGA掃描方式的可以看看這個FPGA學習筆記——VGA簡介-CSDN博客,那么對行同步信號,在有效圖像里面對640進行分塊(我這里是分成10塊)。

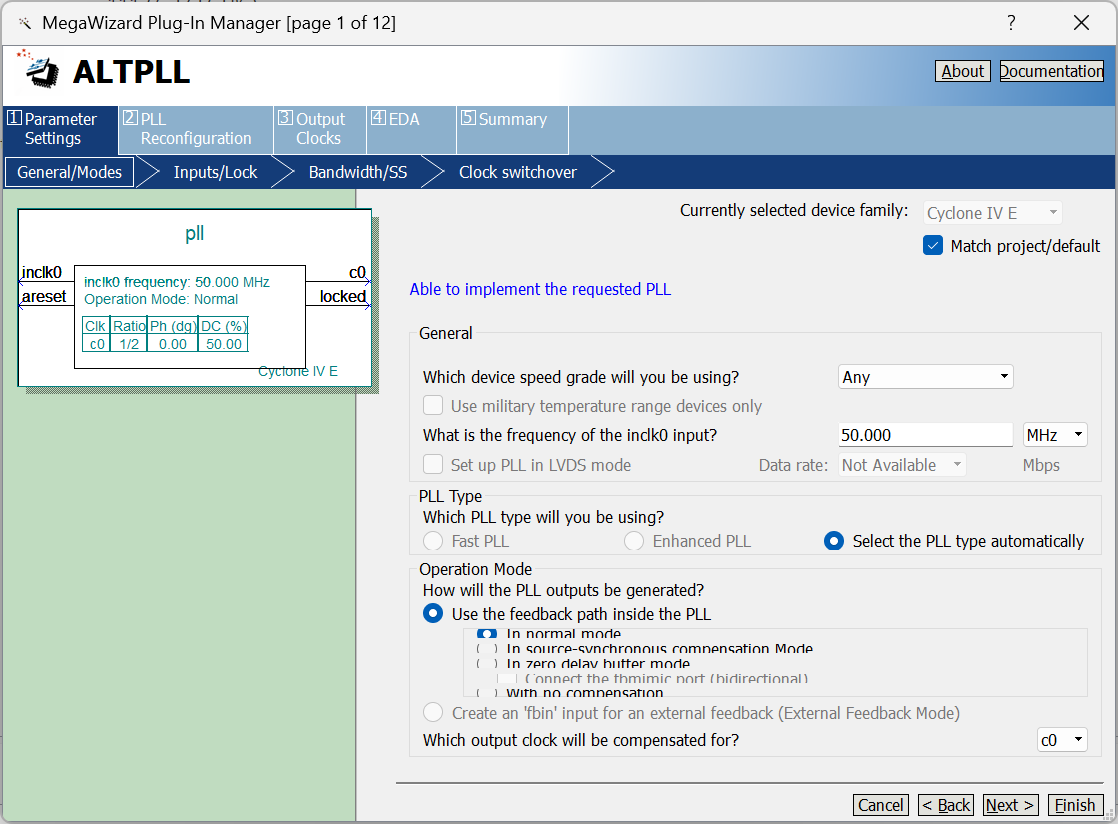

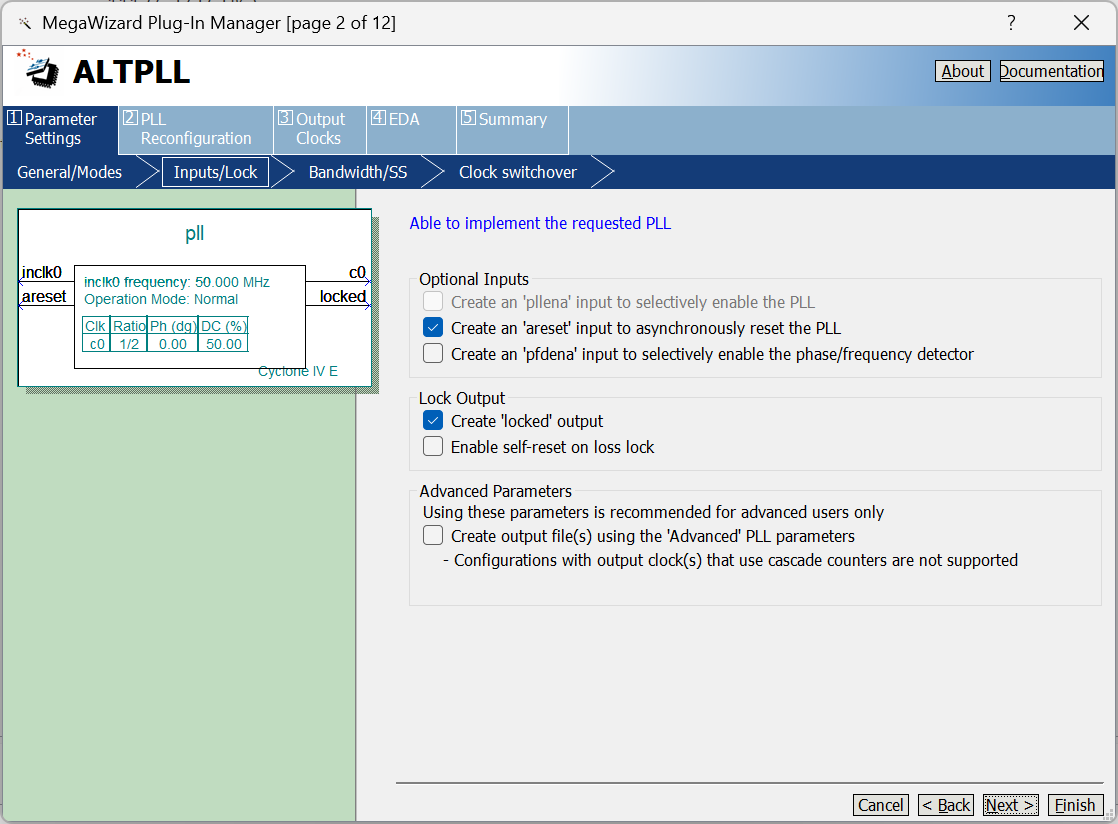

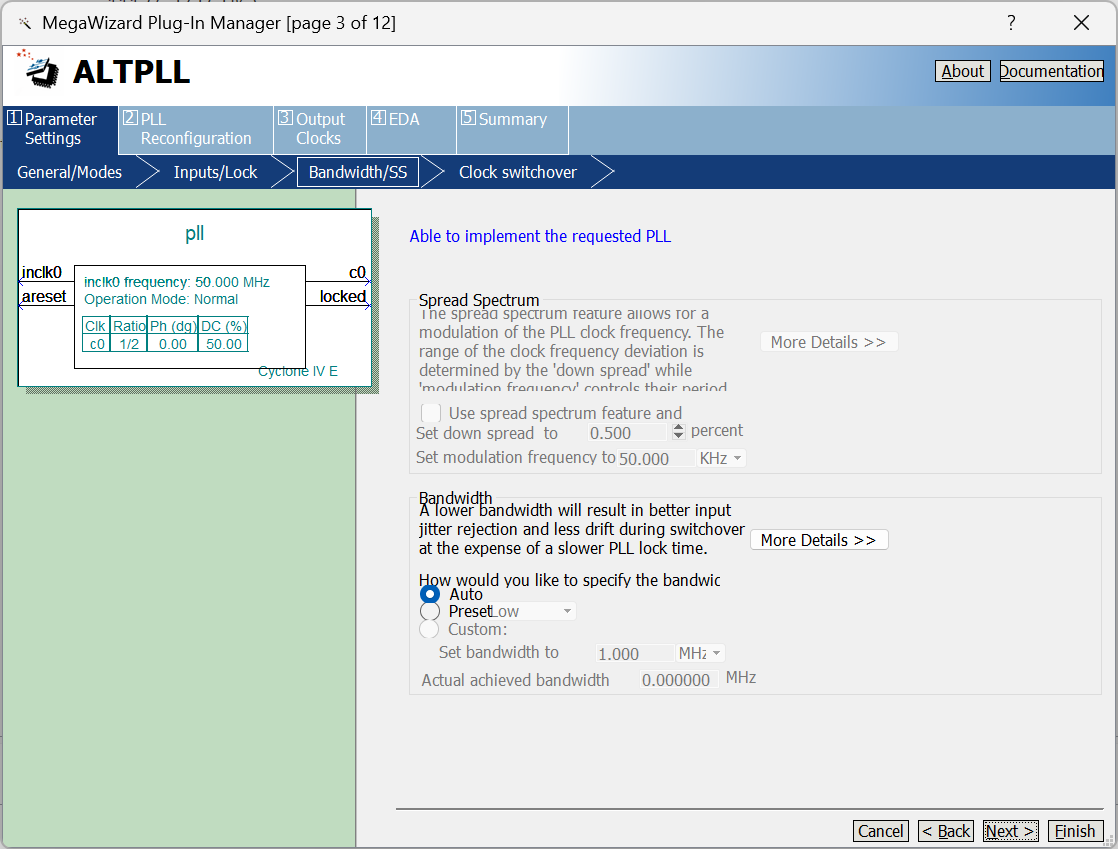

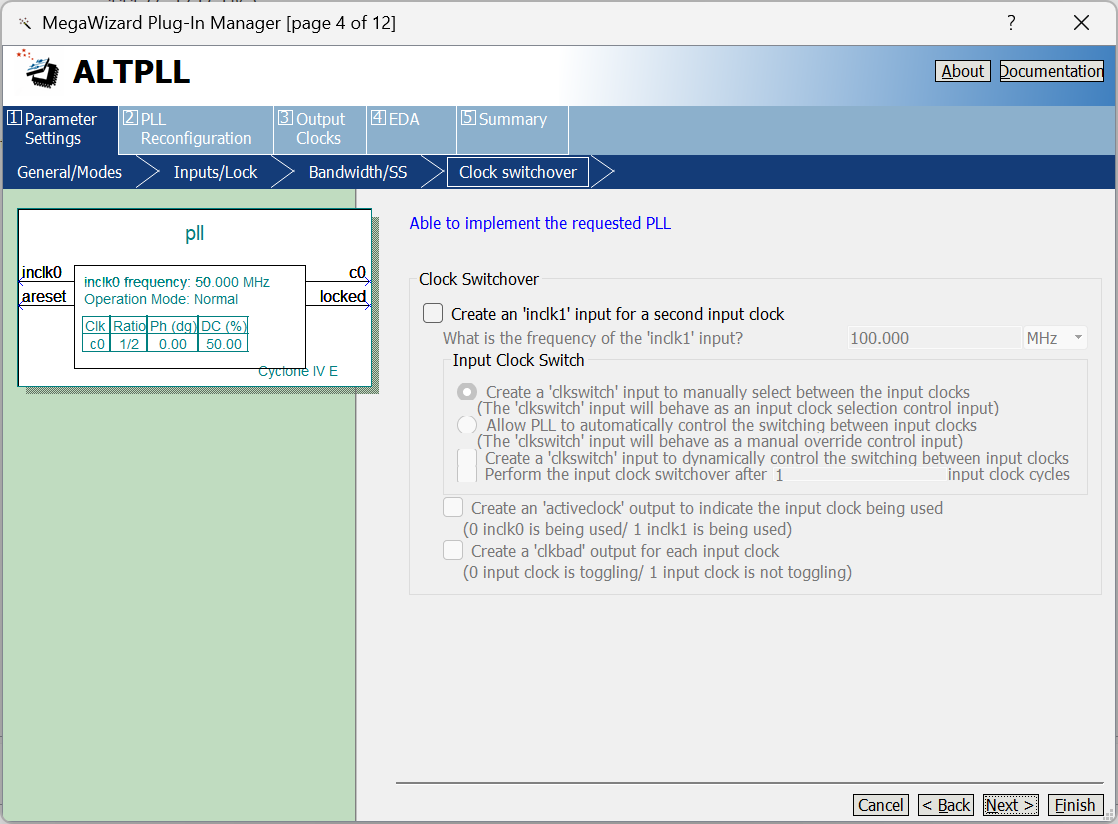

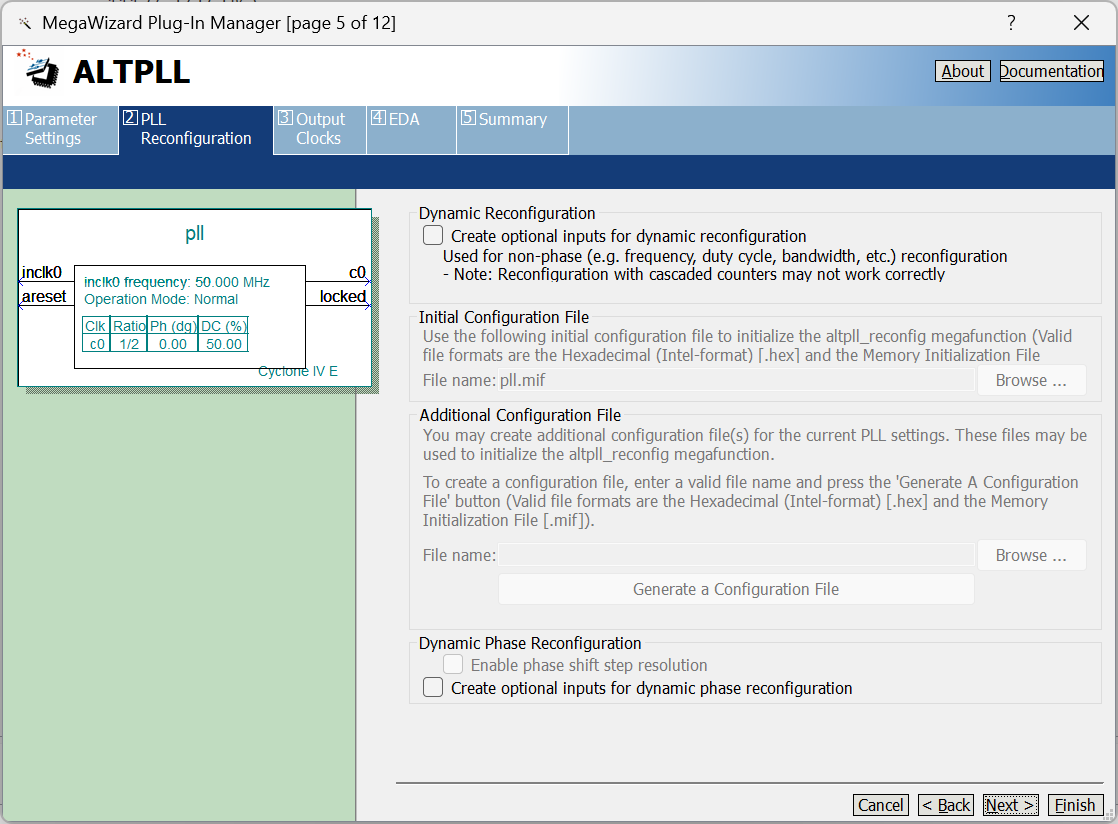

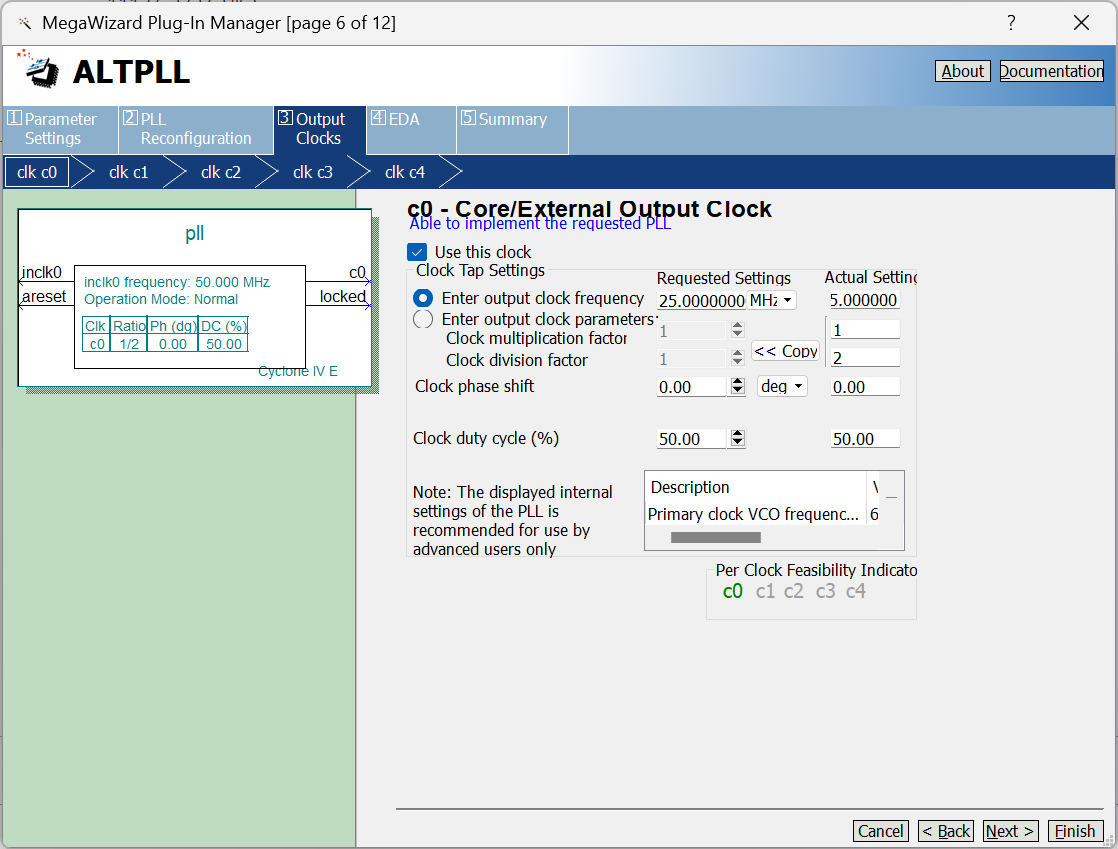

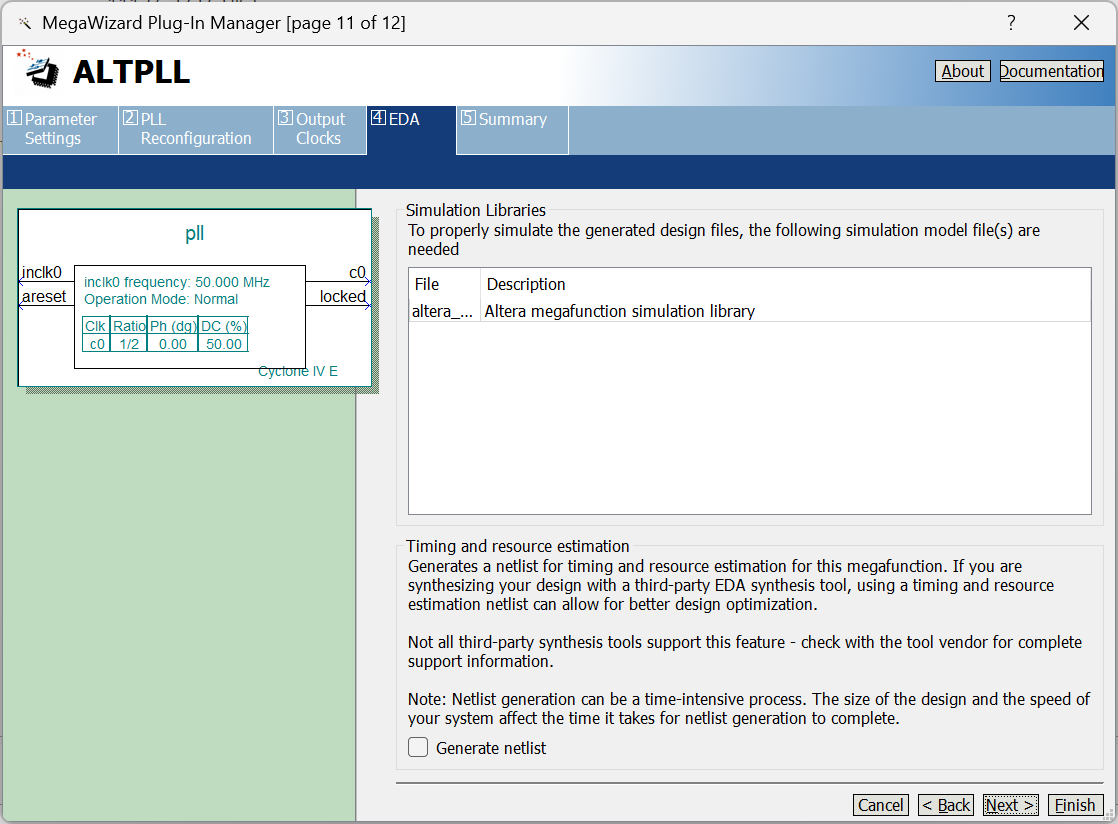

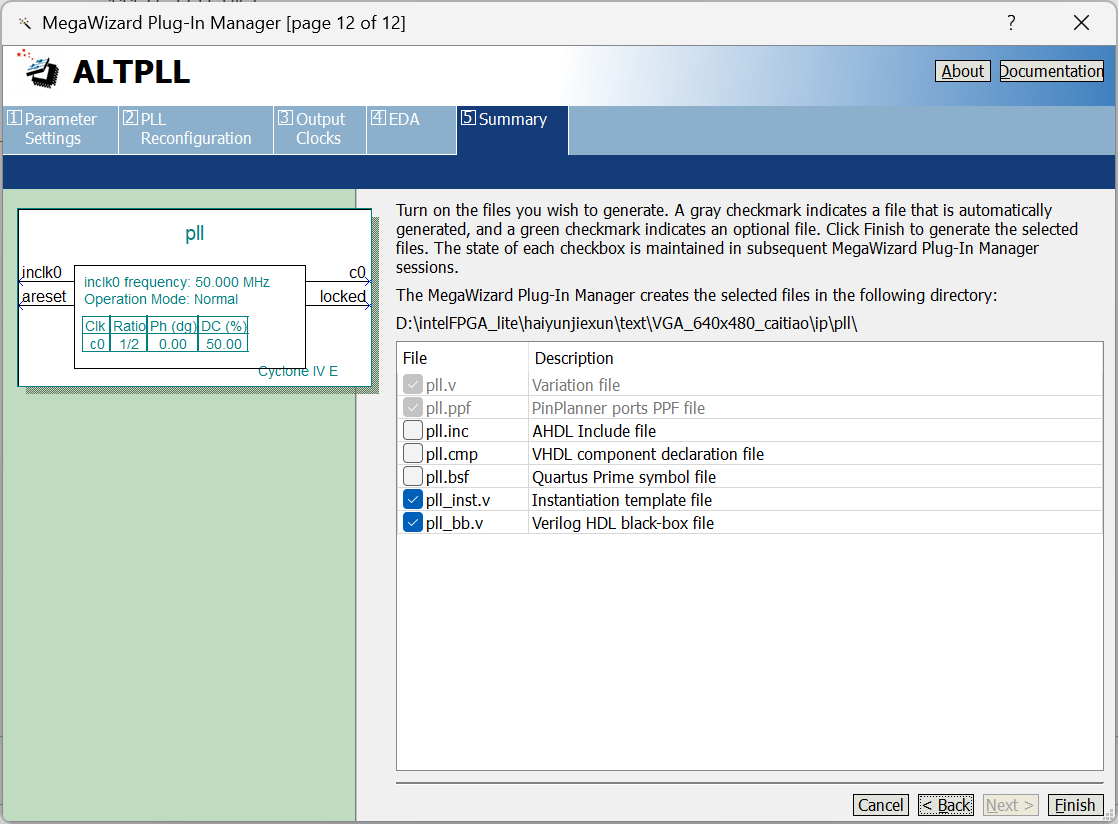

????????那么,在寫代碼的時候應該先配置好PLL IP核,模式的時鐘頻率是25.175MHz,我這里使用的時鐘是50MHz,所以我對它二分頻得到25MHz的時鐘,然后,對常量進行定義,再對應的有效圖像里面對顏色進行賦值。

PLL IP核配置

三、代碼

top.v

module top (

input wire clk ,

input wire rst_n ,

output wire [15:0] data_rgb ,

output wire Hsync ,

output wire Vsync

);//vga

wire De;

wire [9:0] X;vga vga_u(

. pclk (pclk ) ,

. rst_n (locked) ,

. De (De ) , //數據有效信號

. X (X ) ,

. Hsync (Hsync ) , //行同步信號

. Vsync (Vsync ) //場同步信號

);data data_u(

. clk (pclk ) ,

. rst_n (locked ) ,

. X (X ) ,

. De (De ) ,

. data_rgb (data_rgb )

);wire pclk;

wire locked;pll pll_inst (.areset ( !rst_n ),.inclk0 ( clk ),.c0 ( pclk ),.locked ( locked ));endmodule

vga.v

module vga (

input wire pclk ,

input wire rst_n ,

output wire [9:0] X ,

output wire De , //數據有效信號

output wire Hsync , //行同步信號

output wire Vsync //場同步信號

);localparam H_Total = 800 ,//行總像素點H_Addr = 640 ,//有效像素點H_Right = 8 ,//右邊框H_Front = 8 ,//前沿H_Sync = 96 , //同步H_Back = 40 , //后沿H_Left = 8 ;//左邊框localparam V_Total = 525 ,//場總像素點V_Addr = 480 ,//有效像素點V_Bottom = 8 ,//底邊框V_Front = 2 ,//前沿V_Sync = 2 , //同步V_Back = 25 , //后沿V_Top = 8 ; //上邊框reg [9:0] cnt_h,cnt_v;//行周期計數

always @(posedge pclk) beginif(!rst_n)cnt_h <= 0;else if( cnt_h == H_Total - 1 )cnt_h <= 0;elsecnt_h <= cnt_h + 1;

end//場周期計數

always @(posedge pclk) beginif(!rst_n)cnt_v <= 0;else if( cnt_h == H_Total - 1 ) beginif( cnt_v == V_Total - 1 )cnt_v <= 0;elsecnt_v <= cnt_v + 1; endelsecnt_v <= cnt_v;

end//行場同步信號

assign Hsync = (cnt_h < H_Sync ) ? 1 : 0;

assign Vsync = (cnt_v < V_Sync ) ? 1 : 0;

assign De = ((cnt_h > H_Sync + H_Back + H_Left - 1) &&(cnt_h < H_Sync + H_Back + H_Left + H_Addr) &&(cnt_v >= V_Sync + V_Back + V_Top ) &&(cnt_v < V_Sync + V_Back + V_Top + V_Addr) ) ? 1 : 0;assign X = (De == 1) ? (cnt_h - H_Sync - H_Back - H_Left) : 0 ;endmoduledata.v

module data (

input wire clk ,

input wire rst_n ,

input wire De ,

input wire [9:0] X ,

output wire [15:0] data_rgb

);reg [15:0] data_reg ;always @(posedge clk) beginif(!rst_n)data_reg <= 0;else if (X < 64 && De == 1)data_reg <= 16'hF800;else if (X < 128 && De == 1)data_reg <= 16'h07E0;else if (X < 192 && De == 1)data_reg <= 16'h001F;else if (X < 256 && De == 1)data_reg <= 16'hD700;else if (X < 320 && De == 1)data_reg <= 16'h07AF;else if (X < 384 && De == 1)data_reg <= 16'hF00F;else if (X < 448 && De == 1)data_reg <= 16'hA0F8;else if (X < 512 && De == 1)data_reg <= 16'hBCDA;else if (X < 576 && De == 1)data_reg <= 16'hCD69;else if (X < 640 && De == 1)data_reg <= 16'hFFFF;elsedata_reg <= 0;

endassign data_rgb = data_reg;endmodule四、實驗現象

五、更新

針對vga.v代碼,想要顯示更多的顏色可以使用case語句更好

module data (

input wire clk ,

input wire rst_n ,

input wire De ,

input wire [9:0] X ,

output wire [15:0] data_rgb

);reg [15:0] data_reg ;localparam H_Addr = 640 ;//有效像素點//always @(posedge clk) begin

// if(!rst_n)

// data_reg <= 0;

// else if (X < 64 && De == 1)

// data_reg <= 16'hF800;

// else if (X < 128 && De == 1)

// data_reg <= 16'h07E0;

// else if (X < 192 && De == 1)

// data_reg <= 16'h001F;

// else if (X < 256 && De == 1)

// data_reg <= 16'hD700;

// else if (X < 320 && De == 1)

// data_reg <= 16'h07AF;

// else if (X < 384 && De == 1)

// data_reg <= 16'hF00F;

// else if (X < 448 && De == 1)

// data_reg <= 16'hA0F8;

// else if (X < 512 && De == 1)

// data_reg <= 16'hBCDA;

// else if (X < 576 && De == 1)

// data_reg <= 16'hCD69;

// else if (X < 640 && De == 1)

// data_reg <= 16'hFFFF;

// else

// data_reg <= 0;

//end//n 份數

//H_Addr/n 顏色寬度always @(posedge clk) beginif(!rst_n)data_reg <= 0;else if(De) begincase( X/(H_Addr/5) )0:data_reg <= 16'hF800;1:data_reg <= 16'h07E0;2:data_reg <= 16'hFFFF;3:data_reg <= 16'hCD69;4:data_reg <= 16'h07AF;default:data_reg <= 0;endcaseendelsedata_reg <= 0;

endassign data_rgb = data_reg;endmodule以上就是VGA彩條顯示。(個人想法)

)

)

)