目錄

3.1存儲器概述

3.1.1存儲器的分類

1.按在計算機中的作用(層次)分類

2.按存儲介質分類

3.按存取方式分類

4.按信息的可保存性分類

3.1.2存儲器的性能指標

3.2主存儲器

3.2.1SRAM芯片和DRAM芯片

1.SRAM的工作原理

2.DRAM的工作原理

3.SRAM和DRAM的比較

4.存儲器芯片的內部結構

3.2.2只讀存儲器

1.只讀存儲器(ROM)的特點

2.ROM的類型

3.2.3主存儲器的基本組成

3.2.4多模塊存儲器

1.單體多字存儲器

2.多體并行存儲器

(1)高位交叉編址(順序方式)

(2)低位交叉編址(交叉方式)

3.3主存儲器與CPU的連接

3.3.1連接原理

3.3.2主存容量的擴展

1.位擴展法

2.字擴展法

3.字位同時擴展法

3.3.3存儲芯片的地址分配和片選

1.線選法

2.譯碼片選法

3.3.4存儲器與CPU的連接

1.合理選擇存儲芯片

2.地址線的連接

3數據線的連接

4.讀/寫控制線的連接

5.片選控制線的連接

3.4外部存儲器

3.4.1磁盤存儲器

1.磁盤存儲器

(1)磁盤設備的組成

(2)磁記錄原理

(3)磁盤的性能指標

(4)磁盤地址

(5)磁盤的工作過程

2.磁盤陣列

3.4.2固態硬盤

1.固態硬盤的特性

2.磨損均衡(WearLeveling)

3.5高速緩沖存儲器

3.5.1程序訪問的局部性原理

3.5.2 Cache的基本工作原理

3.5.3Cache和主存的映射方式

1.直接映射

2.全相聯映射

3.組相聯映射

3.5.4Cache中主存塊的替換算法

3.5.5Cache的一致性問題

3.6虛擬存儲器

3.6.1虛擬存儲器的基本概念

3.6.2頁式虛擬存儲器

1.頁表

2.地址轉換

3.快表(TLB)

4.具有TLB和Cache的多級存儲系統

3.6.3段式虛擬存儲器

3.6.4段頁式虛擬存儲器

3.6.5虛擬存儲器與Cache的比較

1.相同之處

2.不同之處

3.7本章小結

3.1存儲器概述

3.1.1存儲器的分類

1.按在計算機中的作用(層次)分類

1)主存儲器。簡稱主存,也稱內存儲器(內存),用來存放計算機運行期間所需的程序和數據,CPU可以直接隨機地對其進行訪問,也可以和高速緩沖存儲器(Cache)及輔助存儲器交換數據。其特點是容量較小、存取速度較快、單位成本較高。

2)輔助存儲器。簡稱輔存,也稱外存儲器或外存,用來存放當前暫時不用的程序和數據,以及一些需要永久性保存的信息。輔存的內容需要調入主存后才能被CPU訪問。其特點是容量大、存取速度較慢、單位成本低。

3)高速緩沖存儲器。簡稱Cache,位于主存和CPU之間,用來存放當前CPU經常使用的指令和數據,以便CPU能高速地訪問它們。Cache的存取速度可與CPU的速度相匹配,但存儲容量小、價格高。現代計算機通常將它們制作在CPU中。

2.按存儲介質分類

按存儲介質,存儲器可分為磁表面存儲器(磁盤、磁帶)、磁芯存儲器、半導體存儲器(MOS型存儲器、雙極型存儲器)和光存儲器(光盤)。

3.按存取方式分類

1)隨機存儲器(RAM)。存儲器的任何一個存儲單元都可以隨機存取,而且存取時間與存儲單元的物理位置無關。其優點是讀/寫方便、使用靈活,主要用作主存或高速緩沖存儲器。RAM又分為靜態RAM和動態RAM。

2)只讀存儲器(ROM)。存儲器的內容只能隨機讀出而不能寫入。信息一旦寫入存儲器就固定不變,即使斷電,內容也不會丟失。因此,通常用它存放固定不變的程序、常數和漢字字庫等。它與隨機存儲器可共同作為主存的一部分,統一構成主存的地址域。由ROM派生出的存儲器也包含可反復重寫的類型,ROM和RAM的存取方式均為隨機存取。廣義上的只讀存儲器已可通過電擦除等方式進行寫入,其“只讀”的概念沒有保留,但仍保留了斷電內容保留、隨機讀取特性,但其寫入速度比讀取速度慢得多。

3)串行訪問存儲器。對存儲單元進行讀/寫操作時,需按其物理位置的先后順序尋址,包括順序存取存儲器(如磁帶)和直接存取存儲器(如磁盤、光盤)。順序存取存儲器的內容只能按某種順序存取,存取時間的長短與信息在存儲體上的物理位置有關,其特點是存取速度慢。直接存取存儲器既不像RAM那樣隨機地訪問任何一個存儲單元,又不像順序存取存儲器那樣完全按順序存取,而是介于兩者之間。存取信息時通常先尋找整個存儲器中的某個小區域(如磁盤上的磁道),再在小區域內順序查找。

4.按信息的可保存性分類

斷電后,存儲信息即消失的存儲器,稱為易失性存儲器,如RAM。斷電后信息仍然保持的存儲器,稱為非易失性存儲器,如ROM、磁表面存儲器和光存儲器。若某個存儲單元所存儲的信息被讀出時,原存儲信息被破壞,則稱為破壞性讀出;若讀出時,被讀單元原存儲信息不被破壞,則稱為非破壞性讀出。具有破壞性讀出性能的存儲器,每次讀出操作后,必須緊接一個再生的操作,以便恢復被破壞的信息。

3.1.2存儲器的性能指標

存儲器有三個主要性能指標,即存儲容量、單位成本和存儲速度。這三個指標相互制約,設計存儲器系統所追求的目標就是大容量、低成本和高速度。

1)存儲容量=存儲字數×字長(如1M×8位)。單位換算:1B(Byte,字節)=8b(bit,位)。

存儲字數表示存儲器的地址空間大小,字長表示一次存取操作的數據量。

2)單位成本:位價=總成本/總容量。

3)存儲速度:數據傳輸速率(每秒傳送信息的位數)=數據的寬度/存取周期。

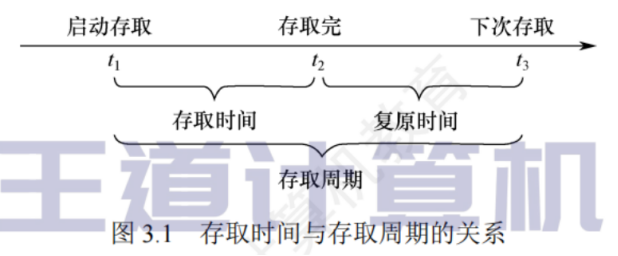

①存取時間(Ta):存取時間是指從啟動一次存儲器操作到完成該操作所經歷的時間,分為讀出時間和寫入時間。

②存取周期(Tm):存取周期是指存儲器進行一次完整的讀/寫操作所需的全部時間,即連續兩次獨立訪問存儲器操作(讀或寫操作)之間所需的最小時間間隔。

③主存帶寬(Bm):也稱數據傳輸速率,表示每秒從主存進出信息的最大數量,單位為字/秒、字節/秒(B/s)或位/秒(b/s)。

存取時間不等于存取周期,通常存取周期大于存取時間。這是因為對任何一種存儲器,在讀/寫操作之后,總要有一段恢復內部狀態的復原時間。對于破壞性讀出的存儲器,存取周期往往比存取時間大得多,甚至可達Tm=2T,因為存儲器中的信息讀出后需要馬上進行再生。存取時間與存取周期的關系如圖3.1所示。

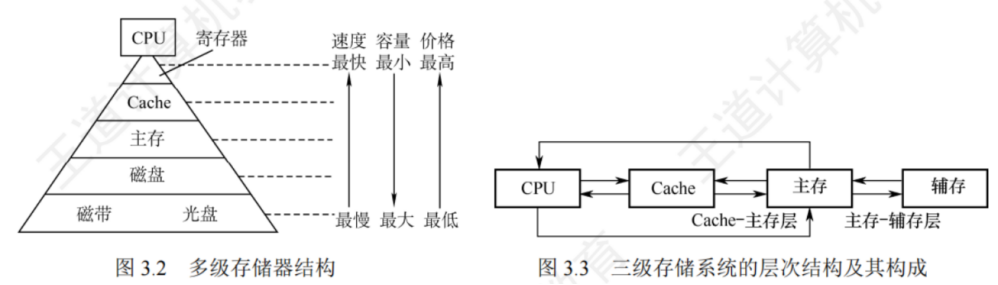

多級層次的存儲系統

為了解決存儲系統大容量、高速度和低成本這三個相互制約的矛盾,在計算機系統中,通常采用多級存儲器結構,如圖3.2所示。在圖中由上至下,位價越來越低,速度越來越慢,容量越來越大,CPU訪問的頻度也越來越低。實際上,存儲系統層次結構主要體現在Cache-主存層和主存-輔存層。在存儲體系中,Cache、主存能與CPU直接交換信息,輔存則要通過主存與CPU交換信息;主存與CPU、Cache、輔存都能交換信息,如圖3.3所示。

存儲器層次結構的主要思想是上一層的存儲器作為低一層存儲器的高速緩存。當CPU要從存儲器中存取數據時,先訪問Cache,若不在Cache中,則訪問主存,若不在主存中,則訪問磁盤,此時,操作數從磁盤讀出送到主存,然后從主存送到Cache。從CPU的角度看,Cache-主存層的速度接近于Cache,容量和位價卻接近于主存。從主存-輔存層分析,其速度接近于主存,容量和位價卻接近于輔存。這就解決了速度、容量、成本這三者之間的矛盾。

Cache-主存層主要解決CPU和主存速度不匹配的問題,主存和Cache之間的數據調動是由硬件自動完成的,對所有程序員均是透明的。主存-輔存層主要解決存儲系統的容量問題,主存和輔存之間的數據調動是由硬件和操作系統共同完成的,對應用程序員是透明的。在主存-輔存層的不斷發展中,逐漸形成了虛擬存儲系統,在這個系統中程序員編程的地址范圍與虛擬存儲器的地址空間相對應,編程時可用的地址空間遠大于主存空間。

注意:在Cache-主存層和主存-輔存層中,上一層中的內容都只是下一層中的內容的副本,也即Cache(或

主存)中的內容只是主存(或輔存)中的內容的一部分。

3.2主存儲器

3.2.1SRAM芯片和DRAM芯片

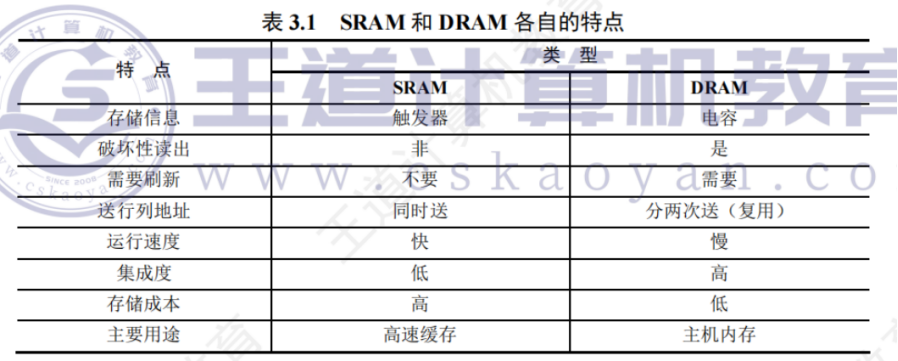

半導體存儲器分為隨機存儲器(RAM)和只讀存儲器(ROM)。RAM又分為靜態隨機存儲器(SRAM)和動態隨機存儲器(DRAM),主存儲器主要由DRAM實現,靠近處理器的那一層(Cache)則由SRAM實現,它們都是易失性存儲器。ROM是非易失性存儲器。

1.SRAM的工作原理

通常把存放一個二進制位的物理器件稱為存儲元,它是存儲器的最基本的構件。地址碼相同的多個存儲元構成一個存儲單元。若干存儲單元的集合構成存儲體。靜態隨機存儲器(SRAM)的存儲元是用雙穩態觸發器(六晶體管MOS)來記憶信息的,靜態是指即使信息被讀出后,它仍保持其原狀態而不需要再生(非破壞性讀出)。SRAM的存取速度快,但集成度低,功耗較大,價格昂貴,一般用于高速緩沖存儲器。

2.DRAM的工作原理

與SRAM的存儲原理不同,動態隨機存儲器(DRAM)是利用存儲元電路中柵極電容上的電荷來存儲信息的,DRAM的基本存儲元通常只使用一個晶體管,所以它比SRAM的密度要高很多。相對于SRAM來說,DRAM具有集成度高、位價低和功耗小等優點,但DRAM的存取速度比SRAM慢,且必須定時刷新和讀后再生,一般用于大容量的主存系統。

●需要刷新的存儲芯片:SDRAM

DRAM電容上的電荷一般只能維持1~2ms,因此即使電源不斷電,信息也會自動消失。此外,讀操作會使其狀態發生改變(破壞性讀出),需讀后再生,這也是稱其為動態存儲器的原因。刷新可以采用讀出的方法進行,根據讀出內容對相應單元進行重寫,即讀后再生。對同一行進行相鄰兩次刷新的時間間隔稱為刷新周期,通常取2ms。常用的刷新方式有以下3種:

1)集中刷新:在一個刷新周期內,利用一段固定的時間,依次對存儲器的所有行進行逐一再生,在此期間停止對存儲器的讀/寫操作,稱為死時間,也稱訪存死區。優點是讀/寫操作期間不受刷新操作的影響;缺點是在集中刷新期間(死區)不能訪問存儲器。

2)分散刷新:將一個存儲器系統的工作周期分為兩部分:前半部分用于正常的讀/寫操作;后半部分用于刷新。這種刷新方式增加了系統的存取周期,如存儲芯片的存取周期為0.5μs,則系統的存取周期為lμs。優點是沒有死區;缺點是加長了系統的存取周期。

3)異步刷新:結合了前兩種方法,使得在一個刷新周期內每一行僅刷新一次。具體做法是將刷新周期除以行數,得到相鄰兩行之間刷新的時間間隔t,每隔時間t產生一次刷新請求。這樣就使“死時間”的分布更加分散,避免讓CPU連續等待過長的時間。

DRAM的刷新需要注意以下問題:①刷新對CPU是透明的,即刷新不依賴于外部的訪問;②DRAM的刷新單位是行,由芯片內部自行生成行地址;③刷新操作類似于讀操作,但又有所不同。另外,刷新時不需要選片,即整個存儲器中的所有芯片同時被刷新。

●DRAM芯片的地址引腳復用技術

DRAM芯片容量較大,地址位數較多,為了減少芯片的地址引腳數,通常采用地址引腳復用技術,行地址和列地址通過相同的引腳分先后兩次輸入,這樣地址引腳數可減少一半。

3.SRAM和DRAM的比較

4.存儲器芯片的內部結構

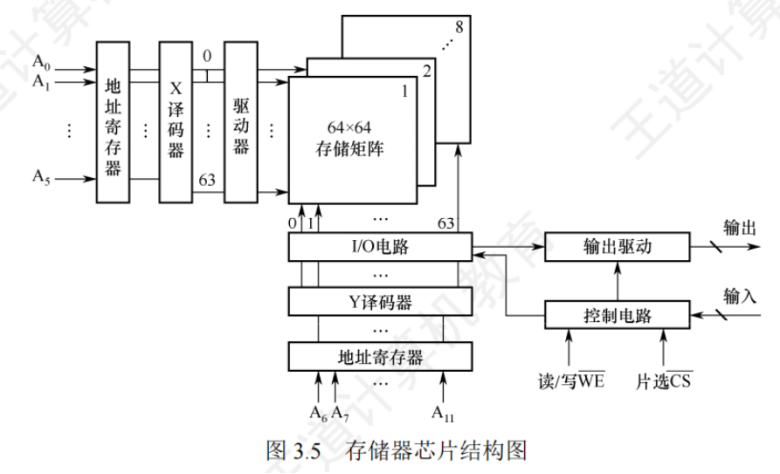

如圖3.5所示,存儲器芯片由存儲體、I/O寫電路、地址譯碼器和控制電路等部分組成。

1)存儲體(存儲矩陣)。存儲體是存儲單元的集合,它由行選擇線(X)和列選擇線(Y)來選擇所訪問單元,存儲體的相同行、列上的多位(位平面數)同時被讀出或寫入。

2)地址譯碼器。用來將地址轉換為譯碼輸出線上的高電平,以便驅動相應的讀/寫電路。地址譯碼有單譯碼法(一維譯碼)和雙譯碼法(二維譯碼)兩種方式。

●單譯碼法。只有一個行譯碼器,同一行中所有存儲單元的字線連在一起,同一行中的各單元構成一個字,被同時讀出或寫入。缺點是地址譯碼器的輸出線數過多。

●雙譯碼法。如圖3.5所示,地址譯碼器分為X和Y兩個譯碼器,在選中的行和列交叉

點上能確定一個存儲單元,這是DRAM芯片目前普遍采用的譯碼結構。

3)I/O電路。用以控制被選中的單元的讀出或寫入,具有放大信號的作用。

4)片選控制線。單個芯片容量太小,往往滿足不了計算機對存儲器容量的要求,因此需用一定數量的芯片進行存儲器的擴展。在訪問某個字時,必須“選中”該存儲字所在的芯片,而其他芯片不被“選中”,因此需要有片選控制信號(經片選控制線傳輸)。

5)讀/寫控制線。根據CPU給出的讀命令或寫命令,經讀/寫控制線控制被選中單元進行讀或寫。

3.2.2只讀存儲器

1.只讀存儲器(ROM)的特點

ROM和RAM都是支持隨機訪問的存儲器,其中SRAM和DRAM均為易失性半導體存儲器。而ROM中一旦有了信息,就不能輕易改變,即使掉電也不會丟失。ROM具有兩個顯著的優點:

①結構簡單,所以位密度比可讀/寫存儲器的高。②具有非易失性,所以可靠性高。

2.ROM的類型

根據制造工藝的不同,ROM可分為掩模式只讀存儲器(MROM)、一次可編程只讀存儲器(PROM)、可擦除可編程只讀存儲器(EPROM)、Flash存儲器和固態硬盤(SSD)。

(1)掩模式只讀存儲器

MROM的內容由半導體制造廠商按用戶提出的要求在芯片的生產過程中直接寫入,寫入以后任何人都無法改變其內容。優點是可靠性高、集成度高、價格便宜;缺點是靈活性差。

(2)一次可編程只讀存儲器

PROM是可以實現一次性編程的只讀存儲器,允許用戶利用專門的設備(編程器)寫入自己的程序,一旦寫入,內容就無法改變。

(3)可擦除可編程只讀存儲器

EPROM不僅可以由用戶利用編程器寫入信息,而且可以對其內容進行多次改寫。EPROM雖然既可讀又可寫,但它不能取代RAM,因為EPROM的編程次數有限,且寫入時間過長。

(4)Flash存儲器

Flash存儲器是在EPROM的基礎上發展起來的,它兼有ROM和RAM的優點,可在不加電的情況下長期保存信息,又能在線進行快速擦除與重寫。Flash存儲器既有EPROM價格便宜、集成度高的優點,又有E2PROM電可擦除重寫的特點,且擦除重寫的速度快。

(5)固態硬盤(SolidStateDrive,SSD)

基于閃存的固態硬盤是用固態電子存儲芯片陣列制成的硬盤,由控制單元和存儲單元(Flash芯片)組成。保留了Flash存儲器長期保存信息、快速擦除與重寫的特性。對比傳統硬盤也具有讀/寫速度快、低功耗的特性,缺點是價格較高。

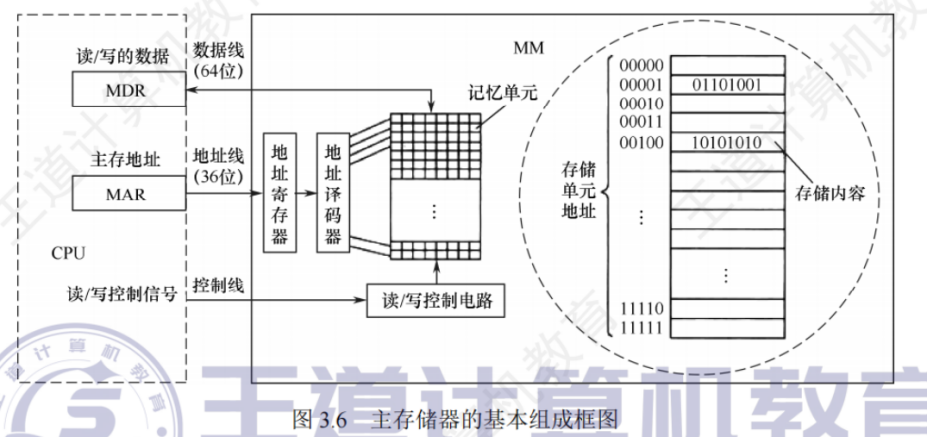

3.2.3主存儲器的基本組成

圖3.6是主存儲器(MainMemory,MM)的基本框圖,其中由一個個存儲0或1的記憶單元(也稱存儲元件、存儲單元)構成的存儲矩陣(也稱存儲體、存儲陣列)是存儲器的核心部件。存儲元件是具有兩種穩態的能表示二進制0和1的物理器件。為了存取存儲體中的信息,必須對存儲單元編號(也稱編址)。編址單位是指具有相同地址的那些存儲元件構成的一個單位,可以按字節編址,也可以按字編址。現代計算機通常采用字節編址方式,此時存儲體內的一個地址中有1字節。

指令執行過程中需要訪問主存時,CPU首先把被訪問單元的地址送到MAR中,然后通過地址線將主存地址送到主存中的地址寄存器,以便地址譯碼器進行譯碼,選中相應單元,同時CPU將讀/寫控制信號通過控制線送到主存的讀/寫控制電路。若是寫操作,則CPU同時將要寫的信息送到MDR中,在讀/寫控制電路的控制下,經數據線將信號寫入選中的單元;若是讀操作,則主存讀出選中單元的內容送至數據線,然后被送到MDR中。MDR的位數與數據線的位數相同,MAR的位數與地址線的位數相同。圖3.6采用64位數據線,所以在按字節編址方式下,每次最多可以存取8個單元的內容。地址線的位數決定了主存地址空間的最大可尋址范圍。例如,36位地址的最大尋址范圍為0~23?-1,即地址從0開始編號。

注意:數據線的位數通常等于存儲字長,因此MDR的位數通常等于存儲字長;若數據線的位數不等于存儲字長,則MDR的位數由數據線的位數決定。

3.2.4多模塊存儲器

多模塊存儲器是一種空間并行技術,利用多個結構完全相同的存儲模塊的并行工作來提高存儲器的吞吐率。常用的有單體多字存儲器和多體低位交叉存儲器。(注意:CPU的速度比存儲器快得多,若同時從存儲器中取出n條指令,就可以充分利用CPU資源,提高運行速度。多體交叉存儲器就是基于這種思想提出的。)

1.單體多字存儲器

在單體多字系統中,每個存儲單元存儲m個字,總線寬度也為m個字,一次并行讀出m個字。在一個存取周期內,從同一地址取出m條指令,然后將指令逐條送至CPU執行,即每隔1/m存取周期,CPU向主存取一條指令。這顯然提高了單體存儲器的工作速度。

缺點:只有指令和數據在主存中連續存放時,這種方法才能有效提升存取速度。一旦遇到轉移指令,或操作數不能連續存放時,這種方法的提升效果就不明顯。

2.多體并行存儲器

多體并行存儲器由多體模塊組成。每個模塊都有相同的容量和存取速度,各模塊都有獨立的讀/寫控制電路、地址寄存器和數據寄存器。它們既能并行工作,又能交叉工作。多體并行存儲器分為高位交叉編址和低位交叉編址兩種。

(1)高位交叉編址(順序方式)

高位地址表示模塊號(或體號),低位地址為模塊內地址(或體內地址)。如圖3.7所示,存儲器共有4個模塊M?~M?,每個模塊有n個單

——第22天:面向對象之繼承與多繼承)

)