如果你對 FPGA 有些了解,大概知道它的意思是“可編程邏輯器件”,可以把寫好的邏輯電路(通常是 Verilog/VHDL)通過工具綜合、布局布線、燒寫進去,讓一塊芯片變成“你想要的電路”。

但如果我告訴你,現在有個開源項目,能讓你:

🧩 在一個 FPGA 里“模擬出”另一個 FPGA

🔧 自己設計一整套 FPGA 架構:LUT、開關矩陣、配置鏈、IO 結構,全由你說了算

💡 最后甚至還能用自己的工具鏈,生成 bitstream 文件,像真的 FPGA 一樣配置運行

你會不會覺得這太“套娃”了點?

這不是虛構,也不是概念,而是一個真正存在的開源項目——OpenFPGA。

OpenFPGA 是什么?

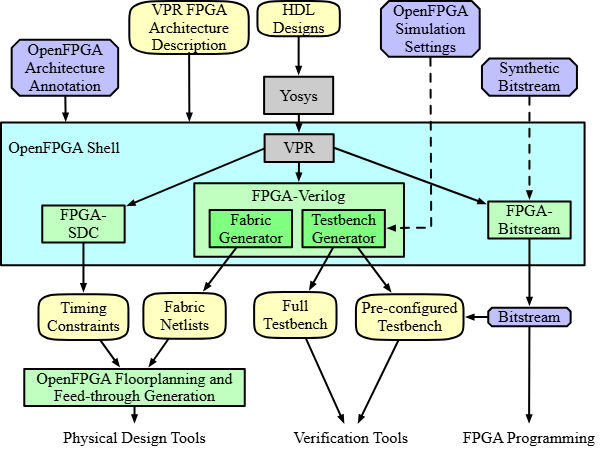

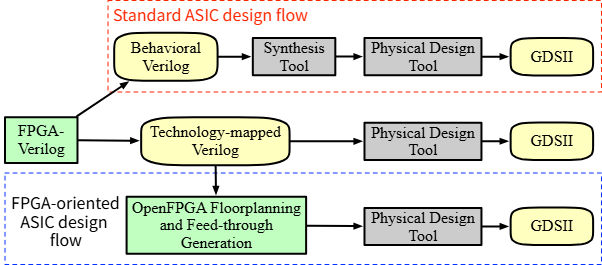

OpenFPGA 是一個由美國猶他大學(University of Utah)開發的開源平臺,用于:

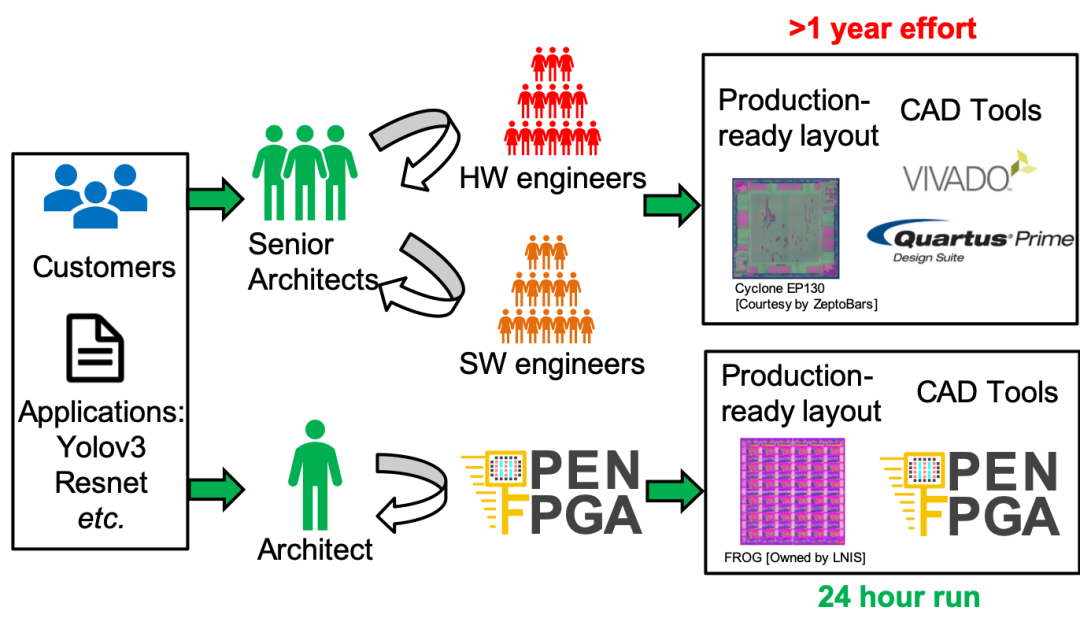

快速構建、驗證、測試和優化可定制的 FPGA 架構。

說白了,它提供了一整套工具鏈,讓你可以像拼樂高積木一樣,去“搭”出你自己想象中的 FPGA 架構,并且:

自動幫你生成 Verilog 實現

生成 bitstream 加載配置

集成仿真、綜合、布局布線流程

支持在真實 FPGA 或仿真器中運行驗證

更重要的是,OpenFPGA 本身就是開源的,你可以把它用于教學、研究、探索架構、甚至 tape-out 前的原型驗證。

它能做什么?

用一句話總結:

讓你從“用 FPGA 寫邏輯”→“自己設計一顆 FPGA”。

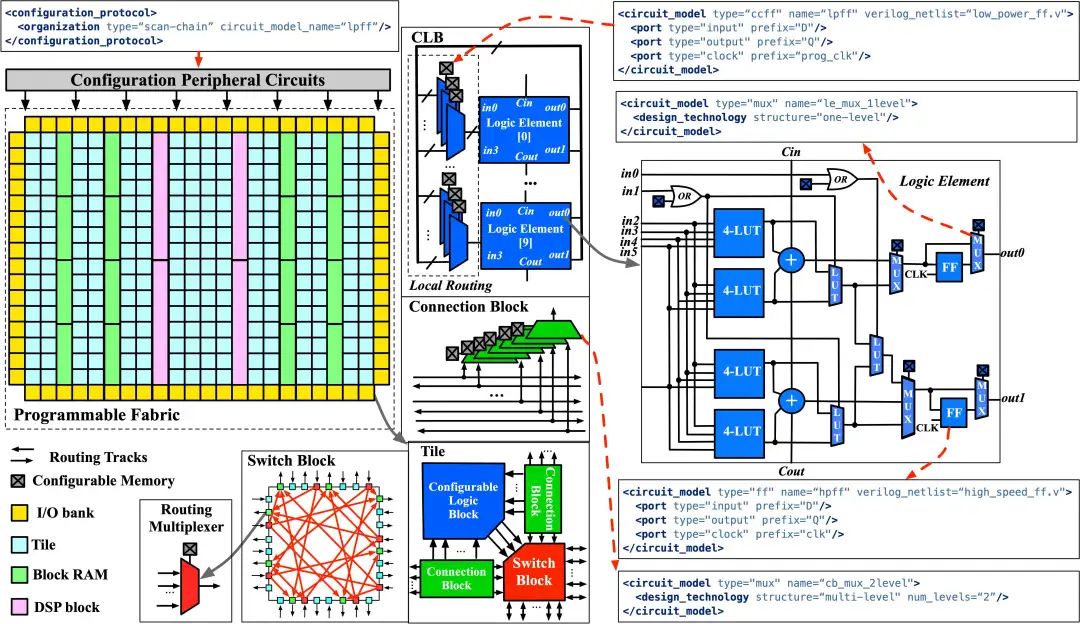

更具體地說,它支持你:

能力 | 描述 |

|---|---|

🎛? 架構定義 | 自己定義 LUT、MUX、交叉開關、布線資源 |

📐 自動生成 RTL | 從架構描述出發生成 Verilog 模塊 |

🛠? 搭建配置鏈 | 包括 SRAM 控制、bitstream 加載邏輯 |

📦 編譯用戶電路 | 用 VTR 工具鏈將用戶模塊映射到你的軟 FPGA 架構上 |

💡 Bitstream 控制 | 輸出配置數據,加載到 FPGA 架構中驅動運行 |

🔄 驗證工具 | 提供仿真、資源分析、可視化接口等 |

最終你會得到一個在真實 FPGA 上運行的 “可配置邏輯網絡”,也就是你自己的“軟核 FPGA”。

🤔 它和我們平時用的 FPGA 有什么區別?

項目 | 普通 FPGA(如 Vivado + Zynq) | OpenFPGA |

|---|---|---|

架構 | 固定(由芯片廠預定義) | 你說了算 |

工具鏈 | 專有(Xilinx/Intel) | 開源(Yosys + VTR + OpenFPGA Flow) |

使用方式 | 寫 Verilog 實現功能 | 先設計架構、再燒進“功能” |

適用范圍 | 產品開發 | 教學、研究、架構探索、原型驗證 |

Bitstream 格式 | 加密、私有 | 自定義、開源可分析 |

你可以把 OpenFPGA 理解為“FPGA 架構設計的實驗室”: 不再是用別人造好的芯片,而是自己動手定義一套“芯片的內核”,并用代碼親自搭出來。

為什么要做這樣的項目?

這個項目的核心目標其實很清晰:

探索更多樣的 FPGA 架構設計(比如不同尺寸的 LUT、異構邏輯塊)

做科研/芯片前驗證:不確定某種布線方式是否高效?先在 OpenFPGA 上驗證一下

教學用具:讓學生“看見并理解”一個 FPGA 的完整內部結構和工作機制

構建自定義 FPGA Overlay:比如把這套軟核嵌進更大的 SoC 中當作自定義協處理器

所以它的定位不是要替代 Xilinx/Intel 的 FPGA,而是:

“給你一張白紙和一套畫筆,讓你畫出自己理解的 FPGA 架構。”

你不僅能跑 HDL,還能造 HDL 運行的平臺,真正從“使用者”進化為“創造者”。

傳送門

項目地址:https://github.com/lnis-uofu/OpenFPGA

配套架構設計手冊:https://docs.openfpga.org/

推薦結合 VTR 項目一起食用:https://github.com/verilog-to-routing/vtr-verilog-to-routing

如果你也想:

搭建自己的軟核 FPGA?

理解 FPGA 背后的世界?

或者在下次答辯/講座/面試時秀一波底層知識?

OpenFPGA 不適合高性能產品,但絕對是探索 FPGA 架構的神器!

)