目錄

1、 概述

2 、硬件電路

3、 新建 VIVADO 工程

4、 添加工程文件

6、編寫流水燈功能的Verilog代碼

7 、添加管腳約束文件

8、 RTL 仿真

8.1 添加仿真測試源碼

8.2 仿真結果

9、 編譯并且產生 bit 文件

10、 下載程序

11、實驗結果

?編輯12、總結

1、 概述

本章課程以大家熟悉的流水燈為例子,詳細講解了 VIVADO 軟件的使用,包括創建 FPGA 工程,編寫 Verilog代碼,添加管腳約束,最后編譯,下載 bit 文件到開發板測試。對于初學 XILINX FPGA 的讀者請注意,bit 文件斷電后就丟失了。如果實現上電能夠啟動程序,需要把 BIT 文件打包成 bin 或者 MCS 文件才可以。如果打包,固化到FLASH。由于是基礎課程,讀者一定不要停留在實現了功能的目的,而是要真正掌握代代碼的編寫能力,寫出優秀的代碼。即便是功能實現了,但是不同的代碼也代表了不同的水平,作為編程者一定要時刻要求自己寫出高水平的代碼。

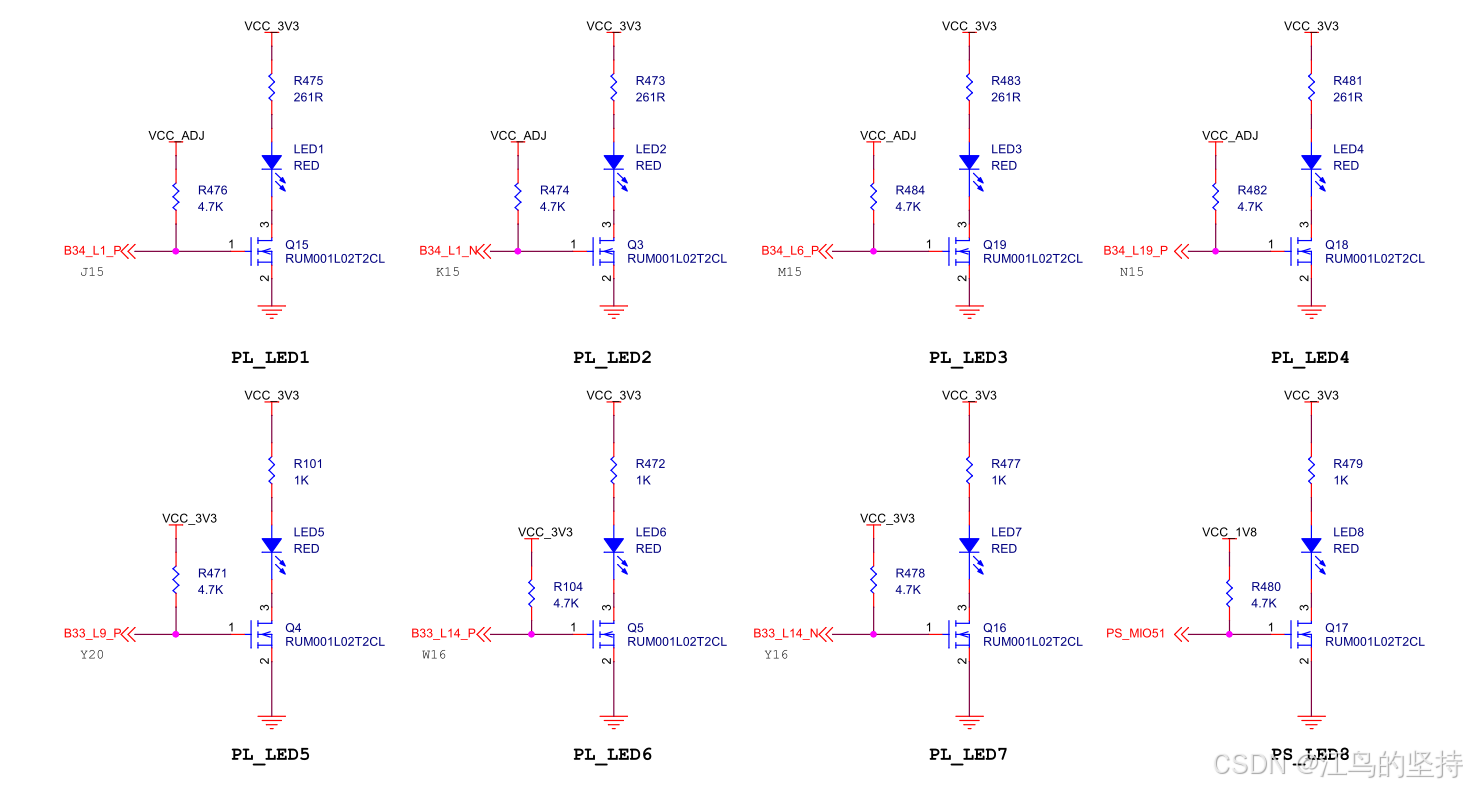

2 、硬件電路

上一節有提到,開發板使用的是米聯客的Zynq 7020,開發板是由核心板和底板(擴展板)組成,LED是在底板上,中間由連接器把兩個板子連接起來,所以引腳不是直接引到FPGA的引腳上。下面鏈接給出了完整的原理圖,自行下載參考。

米聯客Zynq7020核心板和底板原理圖。

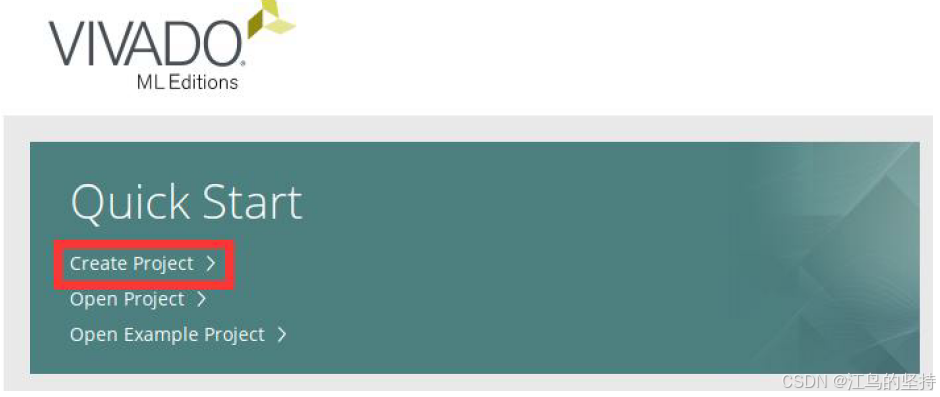

3、 新建 VIVADO 工程

Step1:啟動 VIVADO,單擊 Create Project

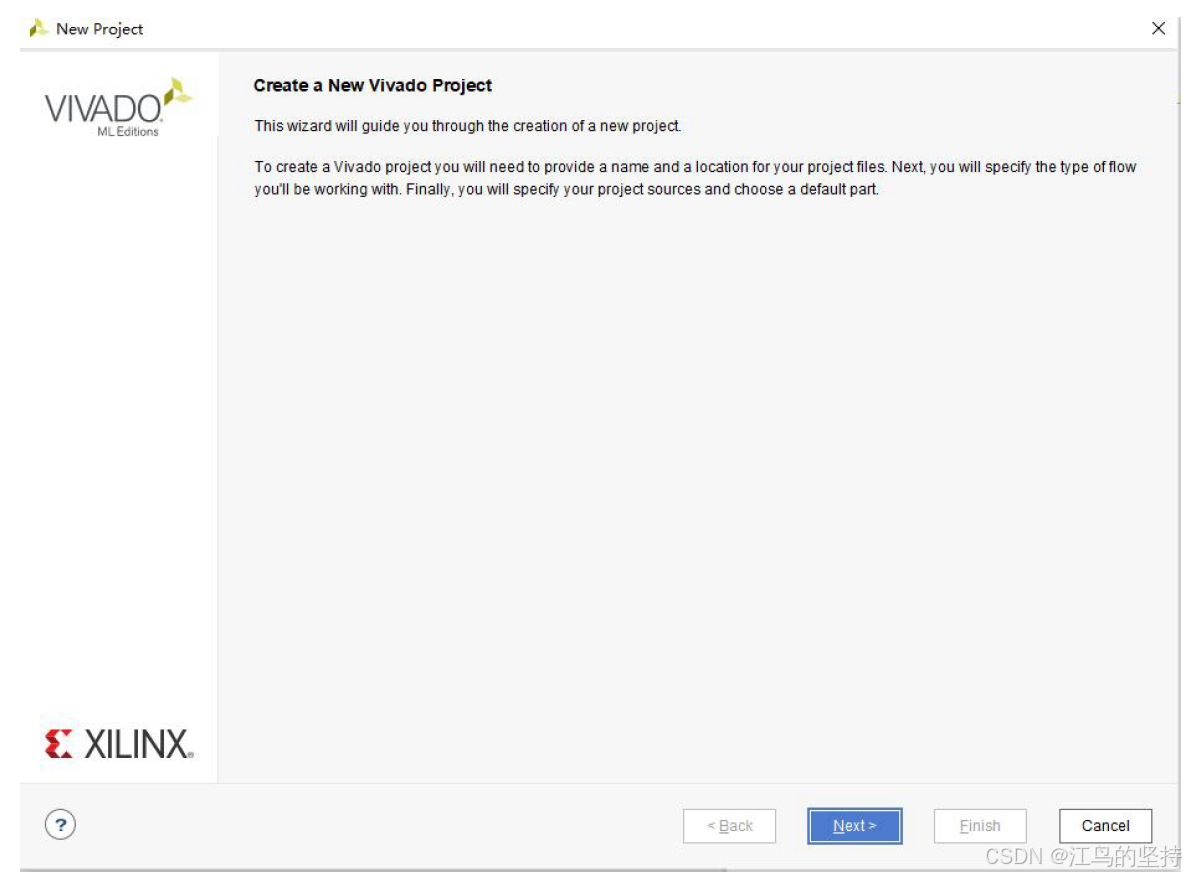

Step2:單擊 NEXT

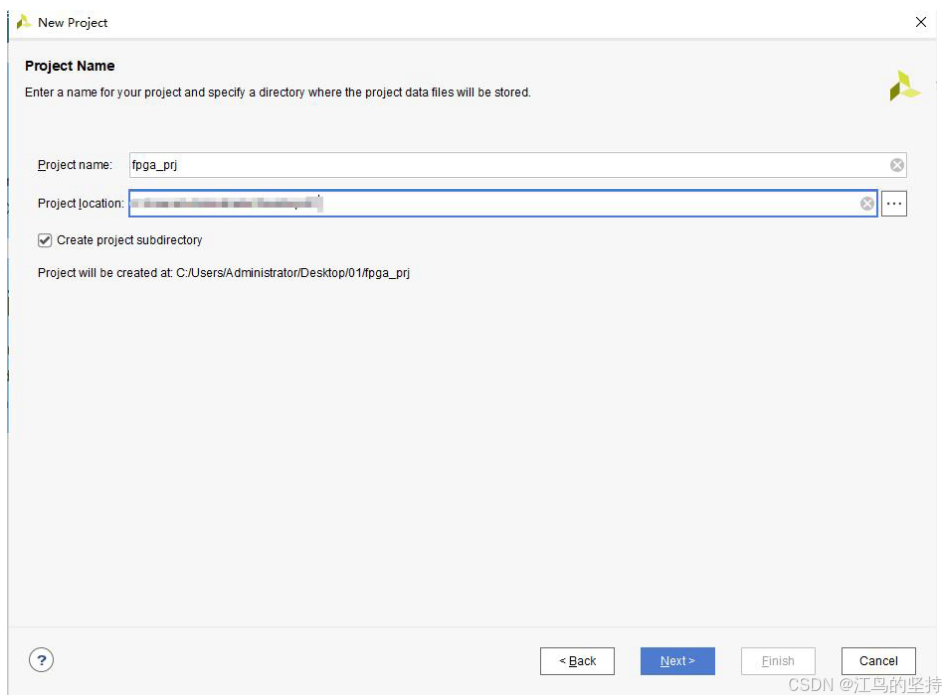

Step3:創建名為 fpga_prj 的工程

到對應的文件目錄,文件路徑自定義,不能有中文或非法字符,之后單擊 NEXT

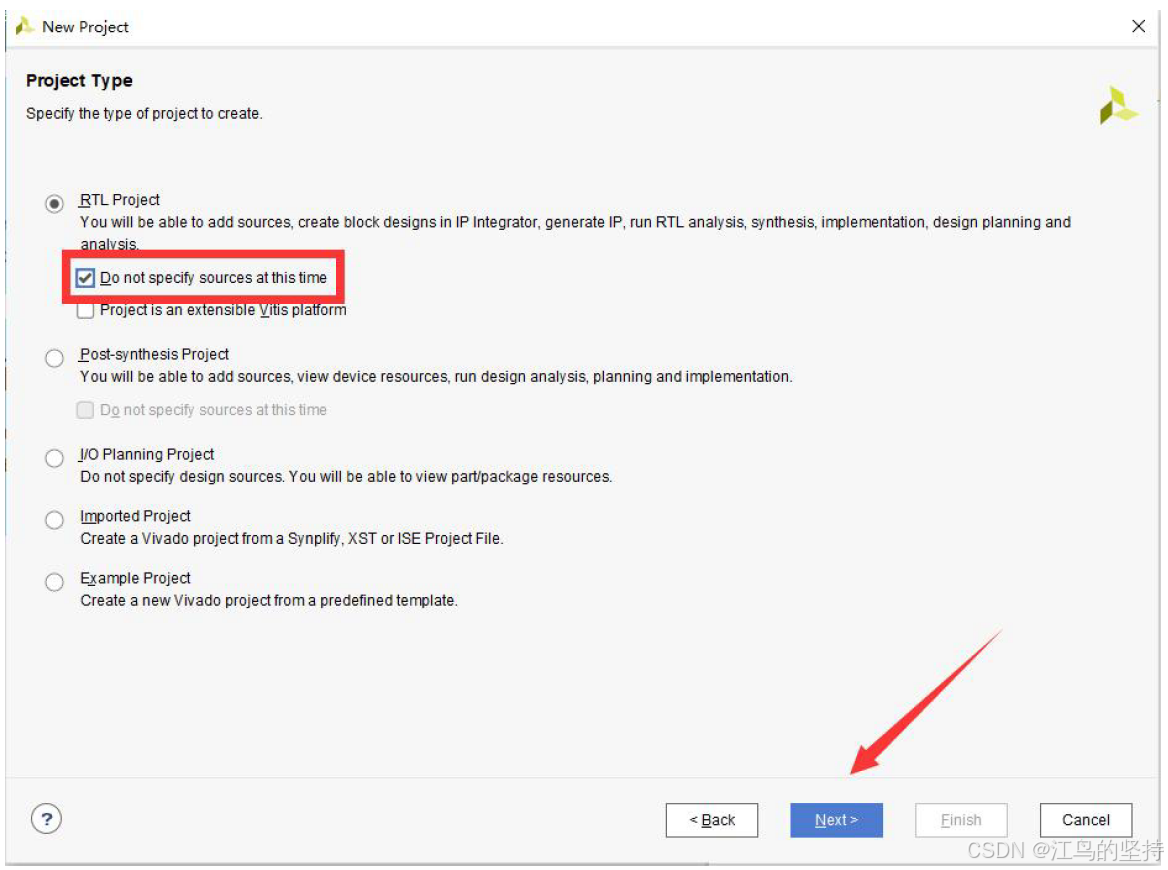

Step4:選擇 RTL Project 并且勾選復選框,之后單擊 NEXT

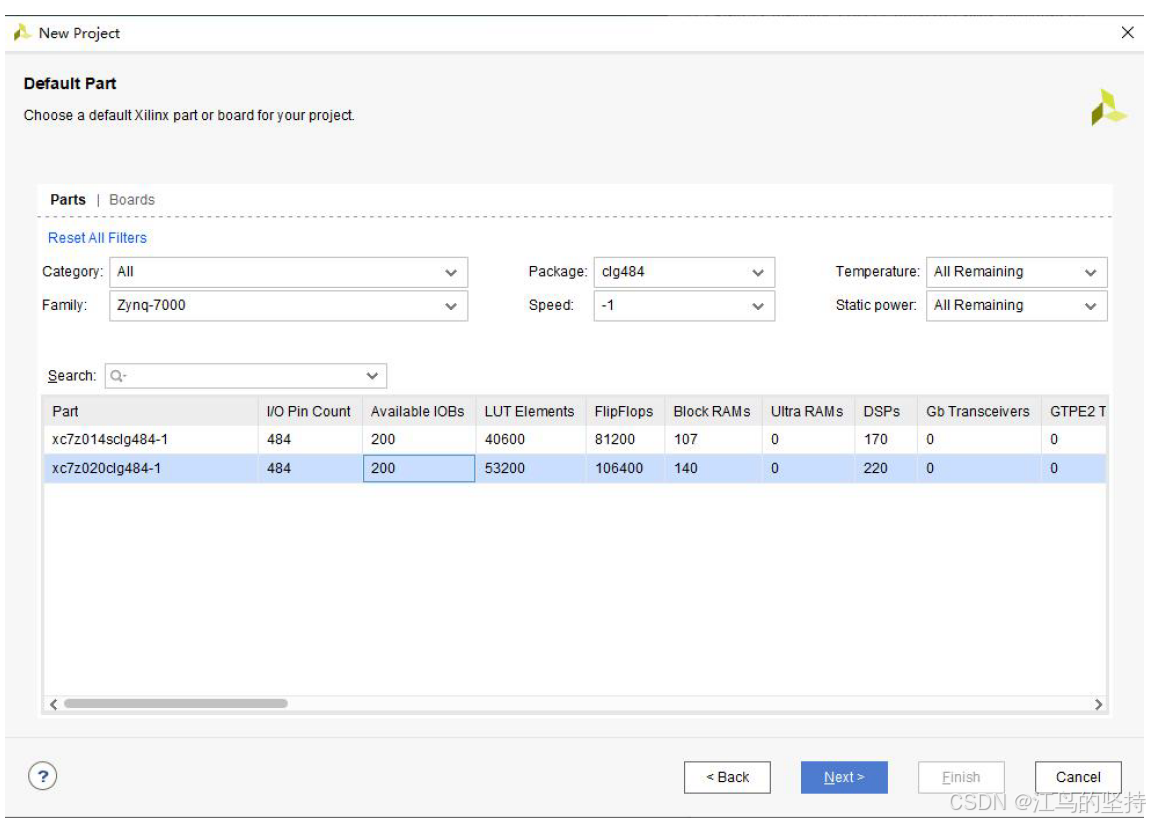

Step5:選擇芯片的型號和封裝速度等級:

核心板使用的芯片型號為 Zynq xc7z020clg484-1,clg484代表封裝,-1為速率等級(-x,x數越大,速度越快)

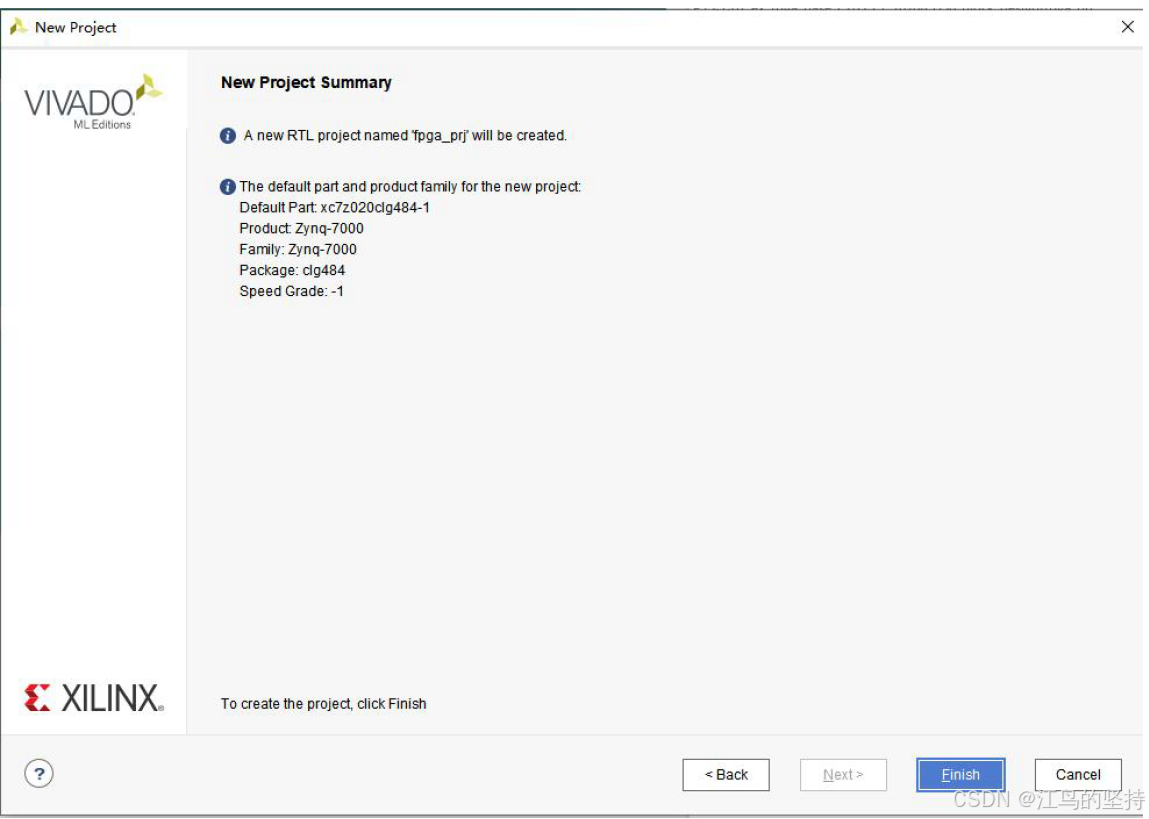

Step:6 單擊 Finish 完成工程創建。

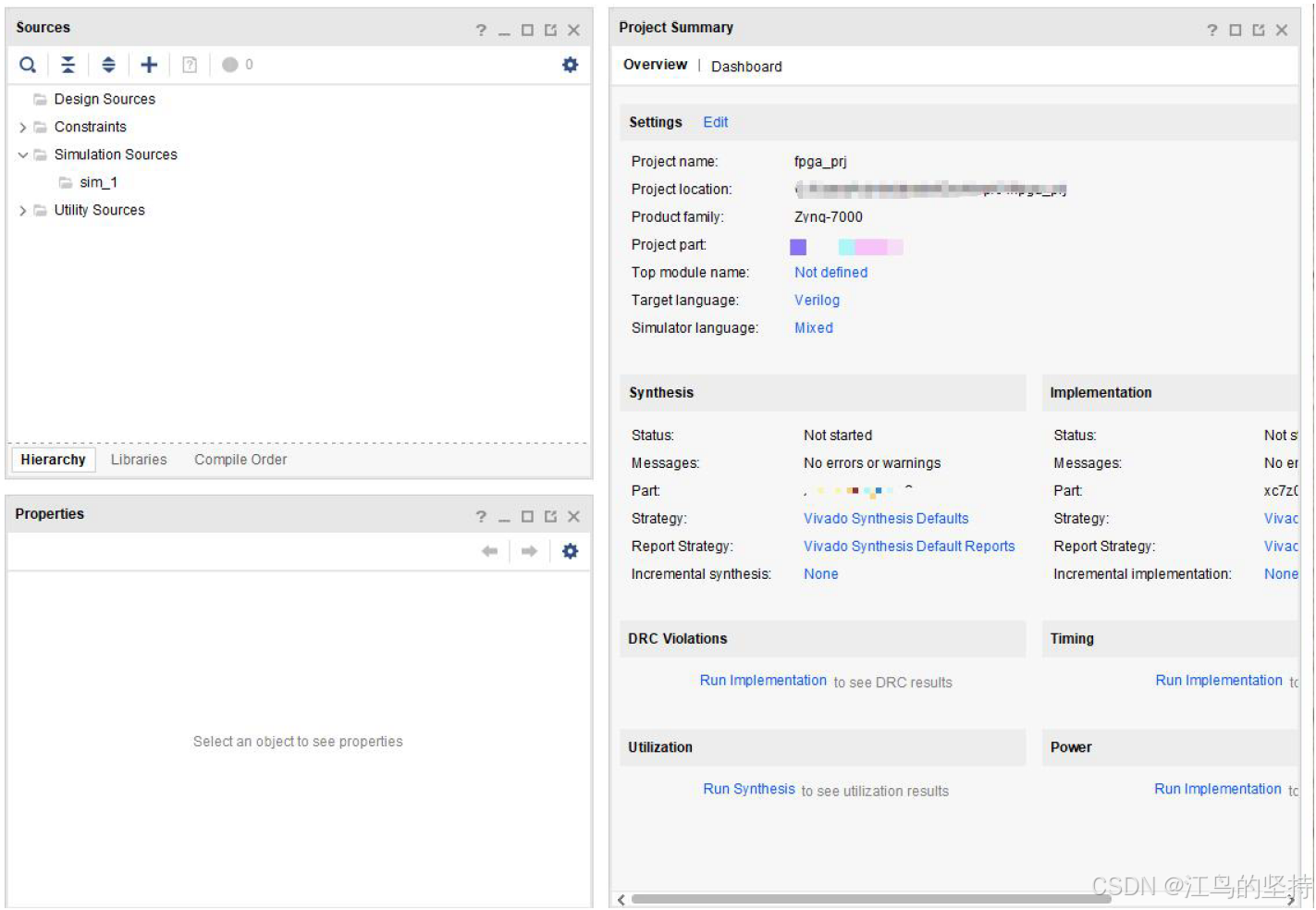

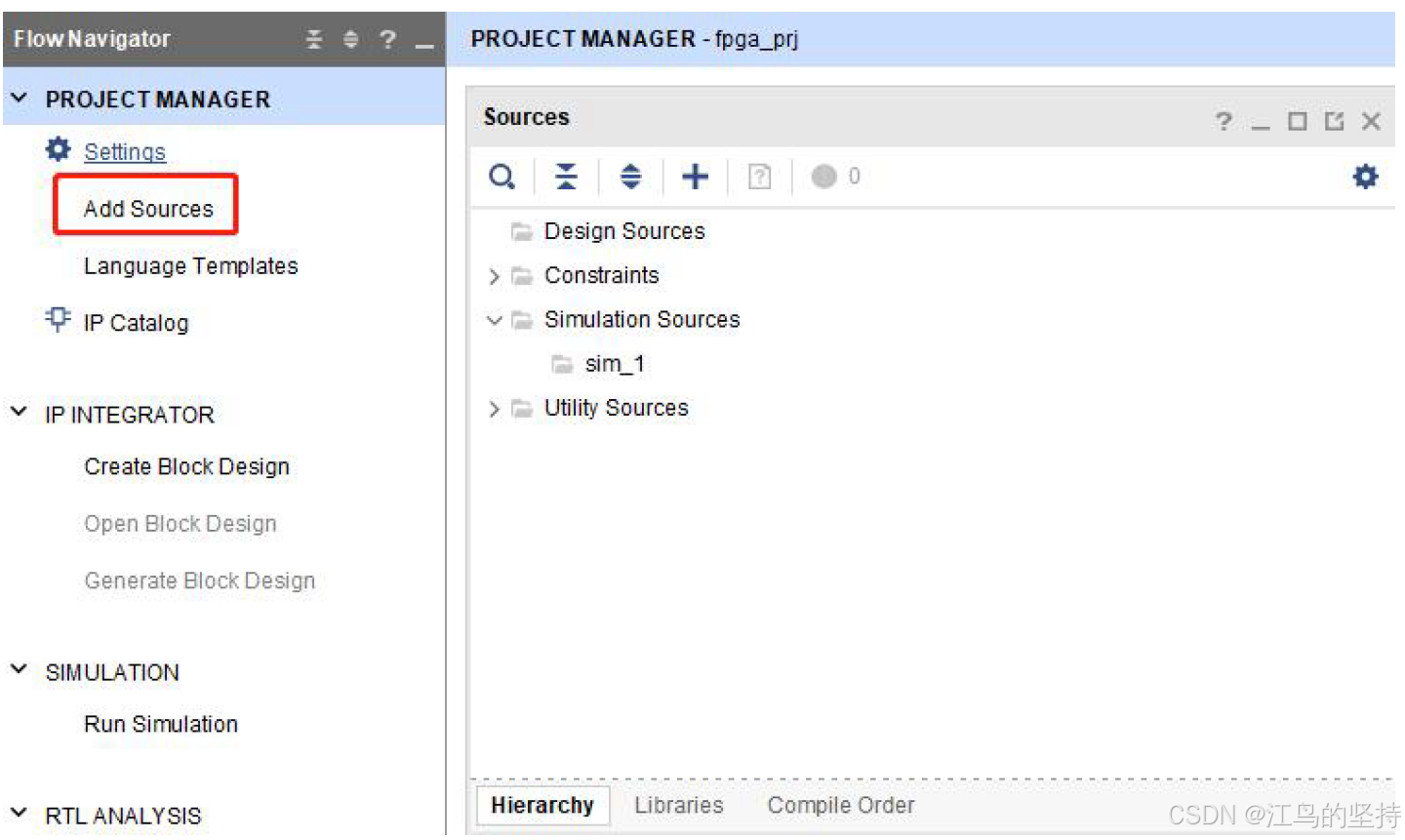

4、 添加工程文件

Step1:打開 VIVADO 軟件

Step2:單擊 Add Sources

Step3

![【STM32的通用定時器CR1的CKD[1:0]: 時鐘分頻因子 (Clock division)】](http://pic.xiahunao.cn/【STM32的通用定時器CR1的CKD[1:0]: 時鐘分頻因子 (Clock division)】)

)

山東大學軟件學院項目實訓-基于大模型的模擬面試系統-面試對話標題自動總結)

)

知識點及案例代碼(13))

和對齊點(AlignmentPoint)詳解——CAD c#二次開發)