標準單元庫中幾種時序單元介紹

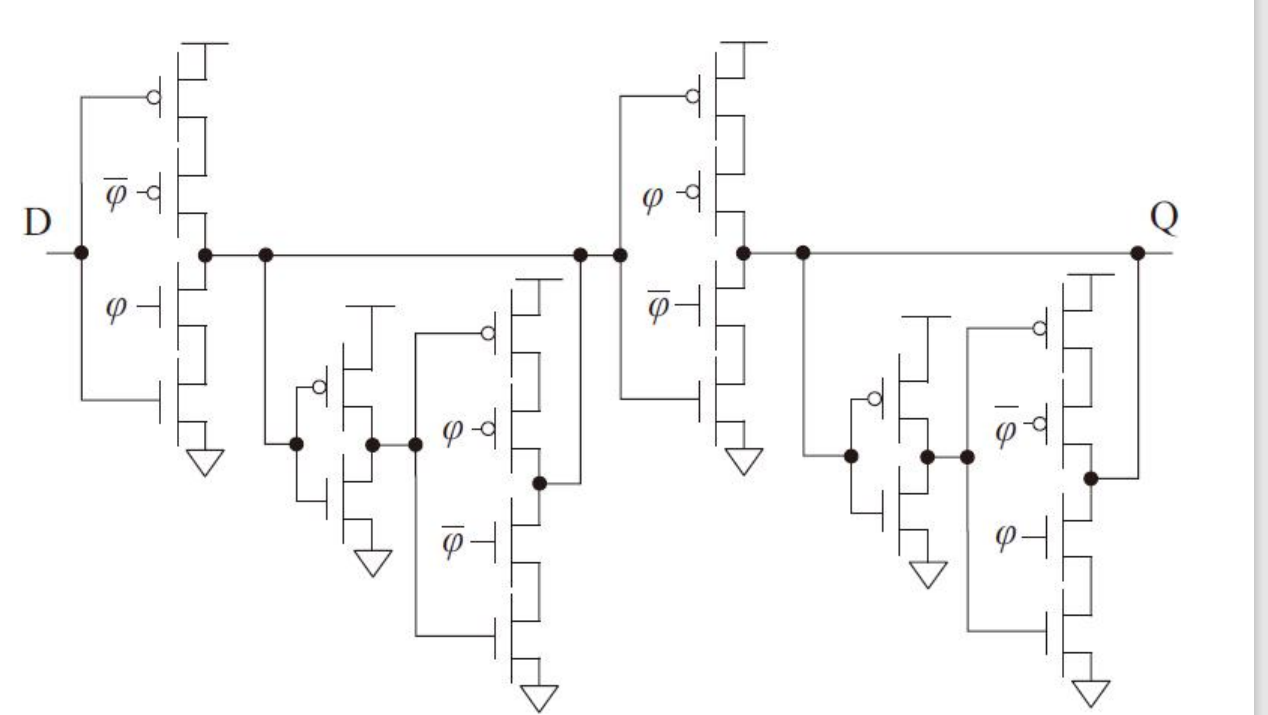

C2MOS觸發器

C2MOS觸發器的工作分為兩個階段:

1)φ=0(φ=1)時,第一個三態驅動器導通(三態門主要體現在,此時主級處于求值模式。同時從級處在高阻抗模式,即維持模式。

2)φ=1時,恰好相反:主級部分處在維持模式,而從級進行求值。

從上述工作過程可以看出,只要時鐘邊沿的上升和下降時間足夠小,具有φ和φ時鐘控制的C2MOS觸發器對時鐘重疊是不敏感的。由于C2MOS觸發器具有對時鐘重疊不敏感的優點,主要標準單元庫中采用了類似該結構的觸發器(一般標準單元中用傳輸門來取代三態門)。

要理解為什么從上述文字可以得出 C2MOS 觸發器對時鐘上升沿交疊(clock overlap)不敏感,我們需要從其工作原理和結構特點入手。

一、C2MOS 觸發器的工作原理回顧

C2MOS 觸發器是一種典型的邊沿觸發結構,由兩個級聯的鎖存器(主級和從級)組成,分別受互補時鐘信號 φ 和 φ? 控制:

-

φ = 0(φ? = 1)時:

- 主級三態驅動器導通,主級處于求值模式(evaluating),接收輸入數據。

- 從級三態驅動器關斷,從級處于維持模式(holding),保持上一次的輸出狀態。

-

φ = 1(φ? = 0)時:

- 主級三態驅動器關斷,主級進入維持模式。

- 從級三態驅動器導通,從級進入求值模式,將主級鎖存的數據傳送到輸出端。

二、什么是時鐘交疊(Clock Overlap)?

時鐘交疊指的是在一對互補時鐘信號(φ 和 φ?)中,兩個信號同時為高電平或低電平的時間段。理想情況下,φ 和 φ? 是完全互補的,即一個為高時另一個為低。但在實際電路中,由于時鐘緩沖器延遲、工藝偏差、溫度變化等因素,可能導致兩個時鐘信號在邊沿轉換時出現短暫的交疊。

時鐘交疊可能導致以下問題:

- 主級和從級同時導通,導致數據路徑直通(data path through);

- 造成數據競爭,觸發器可能輸出錯誤值;

- 引起功耗尖峰或邏輯錯誤。

三、為什么 C2MOS 觸發器對時鐘交疊不敏感?

從工作過程的描述中可以看出:

“只要時鐘邊沿的上升和下降時間足夠小,具有 φ 和 φ? 時鐘控制的 C2MOS 觸發器對時鐘重疊是不敏感的。”

這句話的關鍵在于:

? 1. 互補時鐘控制的非重疊工作模式

- 主級和從級分別由 φ 和 φ? 控制,且它們在正常工作時不會同時處于求值狀態。

- 即使在時鐘邊沿轉換過程中存在短暫的交疊,只要邊沿轉換時間(上升/下降時間)足夠快,就能避免主級和從級同時導通。

? 2. 邊沿轉換速度快,交疊時間極短

- 文中指出“只要時鐘邊沿的上升和下降時間足夠小”,說明設計者可以通過優化時鐘驅動電路,使得 φ 和 φ? 的轉換非常迅速。

- 這樣即使存在交疊,其持續時間也極短,不足以讓主級和從級同時完全導通,從而不會導致數據直通或錯誤傳遞。

? 3. 結構上具有隔離性

- 三態門或傳輸門結構在非導通狀態下具有高阻態,能夠有效隔離主級與從級之間的信號路徑。

- 這種結構天然具備一定的容忍交疊的能力,即使時鐘有輕微重疊,也不會導致數據錯誤。

四、總結

從文中描述可以得出 C2MOS 觸發器對時鐘交疊不敏感的原因是:

- 主級和從級由互補時鐘控制,正常工作時不會同時導通;

- 邊沿轉換時間足夠快,避免了長時間的時鐘交疊;

- 三態門/傳輸門結構在非導通狀態下提供高阻隔離;

- 因此即使存在輕微的時鐘交疊,也不會導致數據錯誤或電路異常。

這種特性使得 C2MOS 觸發器在標準單元庫中被廣泛采用,尤其是在對時鐘抖動和工藝變化較為敏感的先進工藝節點中。

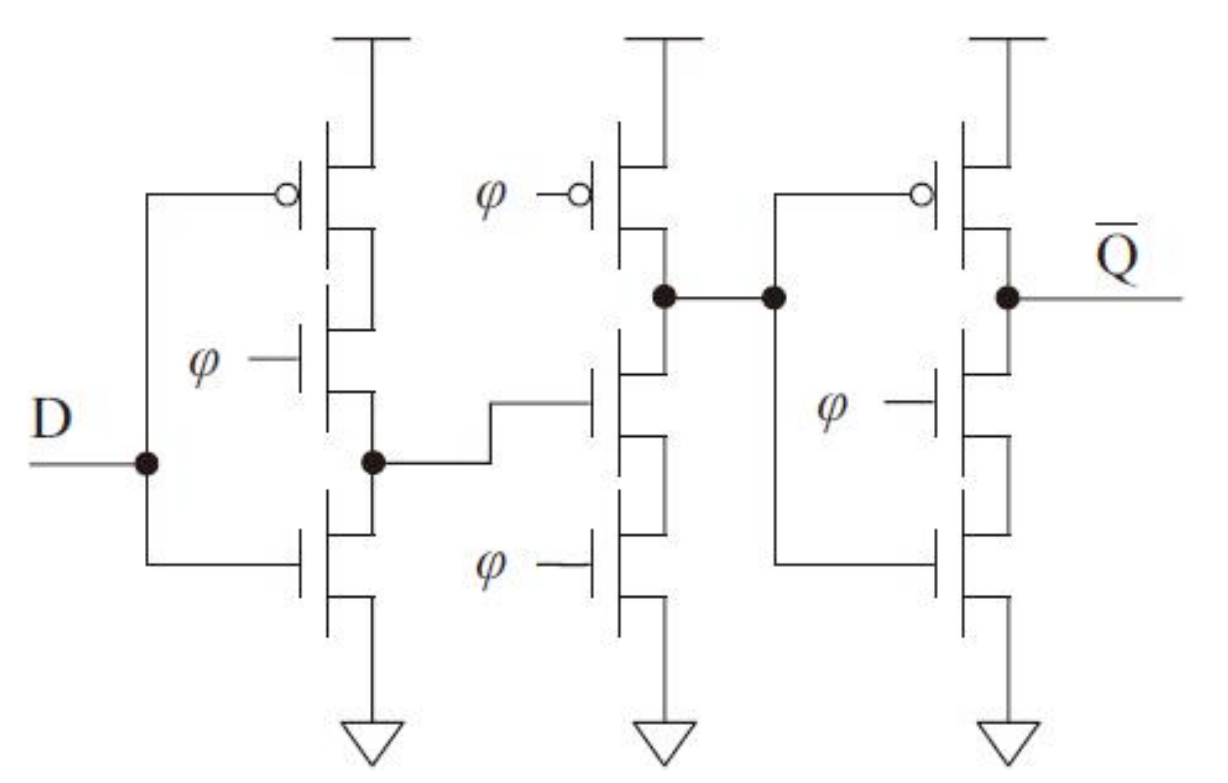

真單相觸發器

在高性能和復雜的設計中,為了克服多個時鐘信號分布的問題和避免因時鐘偏差引起的各種問題,我們通過使用單相位時鐘并結合主從拓撲結構電路實現的觸發器來避免競爭問題,該種觸發器就是真單相觸發器。

TSPC觸發器利用一個負沿鎖存器(通過PMOS管鐘控)作為主級鎖存器,驅動一個鐘控反相器。

從級鎖存器包括由NMOS管鐘控的一個正沿鎖存器。

當φ=0時,輸入反相器采樣反相的輸入信號,第二個(動態)反相器處于預充電狀態,第三個反相器處于維持狀態。因此在時鐘的低電平階段,最后一個(靜態)反相器的輸入保持它原來的值,從而輸出結果。

TSPC觸發器只使用單相位的時鐘并融入動態結構,晶體管數目比傳輸門形式的觸發器略有增加,但是時鐘負載小,它可以將邏輯功能嵌入到鎖存器中,這種嵌入邏輯的觸發器已經廣泛應用于DEC公司的微處理器中。

合理地設計TSPC觸發器的晶體管尺寸是實現正確功能的關鍵,TSPC結構的鎖存器典型脈沖觸發器的組成部分,只要提供短暫的單向脈沖即可工作,有效地提高了抗毛刺能力。

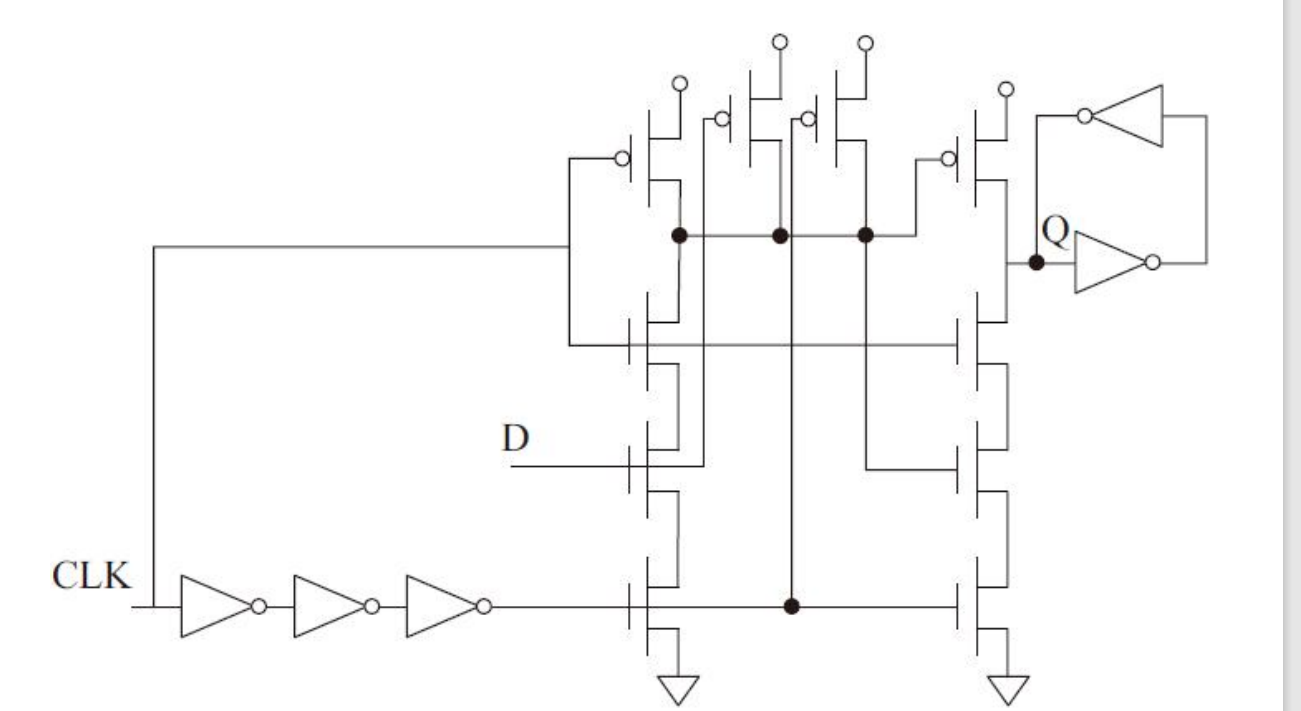

脈沖觸發器

觸發器設計一般采用主從結構來構成邊沿觸發器,但是根據工程的具體需求,需要設計實現原理不同的觸發器。其中一種就是采用脈沖信號來實現的觸發器——脈沖觸發器。

通過在時鐘上升(下降)沿附近生成一個短脈沖,這一脈沖的作用類似于鎖存器的時鐘輸入,它只在一個很短的窗口采樣輸入,利用鎖存器的透明時間非常短來避免競爭情況。

因此,脈沖觸發器是將毛刺產生電路和鎖存器組合成的一個邊沿觸發器。脈沖觸發器比主從結構的兩級減少了1級,通過在時鐘上升(下降)沿附近生成一個短脈沖并與一級鎖存器結合構成了邊沿觸發器。脈沖觸發器通過對邏輯結構和級數的優化,有效減少觸發器的輸入到輸出的延時。更重要的是,脈沖觸發器的建立時間是0甚至是負數,這意味著數據可以在時鐘有效沿以后到達。由于脈沖觸發器的這些優勢,它能比主從觸發器提供更多的性能提升。脈沖觸發器根據應用脈沖電路的形式分顯式和隱式兩種。顯式脈沖觸發器的脈沖產生電路在觸發器外部,因此它可以與多個觸發器單元共用脈沖產生電路,隱式脈沖觸發器的脈沖產生電路集成在觸發器內部。

HLFF在AMD公司的K6芯片中有實際的應用,該單元為脈沖形式的觸發器。通過分析發現,它與一般的脈沖觸發器不同,區別是它取值脈沖,而不是產生脈沖波形并在短時間有效期中求值。而且它具有隱式的結構,不適合多個單元集成一起共用一個脈沖信號的顯式結構。脈沖觸發器與一般的觸發器是有區別的,它的建立時間是負的,因而可以給上一級電路提供多余的時間。脈沖觸發器是針對具體應用的而不是針對所有電路的。

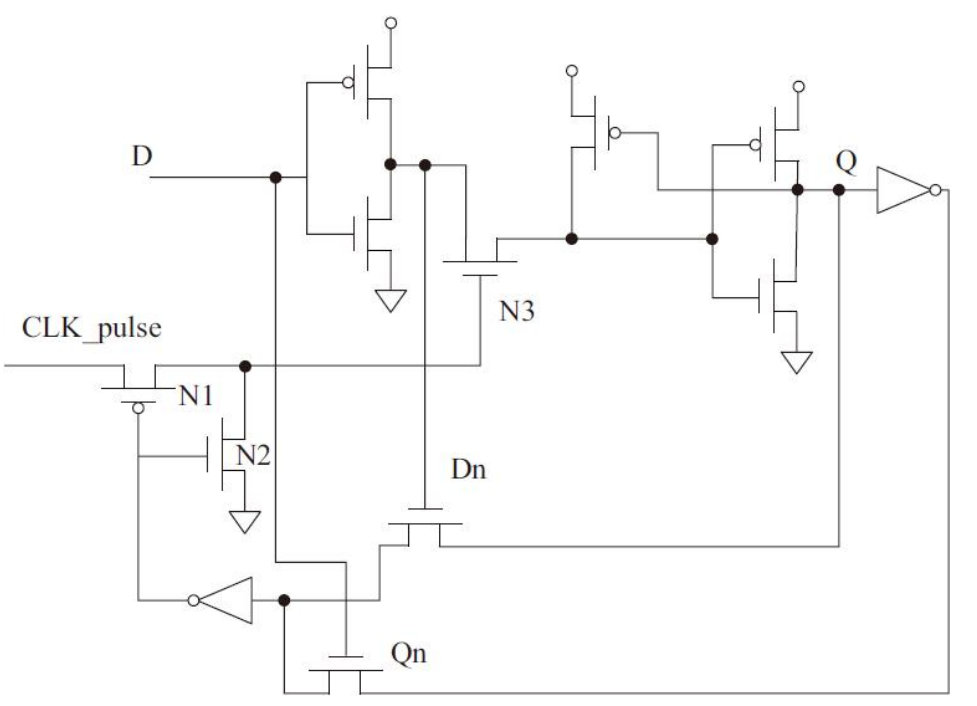

數據流觸發器

在數字VLSI中,減少能量消耗是低功耗設計的直接目的,其中高頻率的0和1之間的轉換是能量消耗的主要原因。

根據電路的不同特性,其他能量的消耗形式分為動態和靜態電路。動態電路通過對電路節點電容進行預充消耗能量,靜態電路主要是以亞域漏流的形式消耗能量。由時序單元(觸發器和鎖存器)組成的時鐘網絡是大規模集成電路系統中主要的能量消耗源。在典型的IC設計中,大約30%~60%的能量消耗在時鐘網絡中。通過減少觸發器的能量消耗將直接減少整個系統的能量消耗量,同時觸發器的性能提升直接緩解時鐘網絡的分布約束并提高整個系統的性能。

數據流觸發器(SJLFF)通過判斷輸入數據的變化來有條件地進行求值操作,減少多余的功耗損失;通過結構上的改進,減少了時鐘的負載并提高了性能。

SJLFF工作原理如下:通過融入數據預先判斷的思想,互補形式的輸入D(Dn)和輸出Q(Qn),通過偽NMOS結構構成一個同或結構,再通過反相器控制N1和N2,只要D=Q,N1斷開,脈沖信號不能到達N3,則觸發器不做求值運算,從而減少多余的求值操作以降低功耗。

通過把時鐘脈沖使能的求值管用N3實現又有效地提高了觸發器的性能。

當時鐘脈沖有效時,D的傳播延時只有一個N管和一個反相器的時間。

不用異或結構來控制N1和N2是因為傳輸管閾值損失導致信號減弱而不能很好地驅動負載,使用同或加反相器結構來實現異或邏輯對觸發器本身的傳播延時沒有明顯的影響又能提高觸發器的穩定性。

以HLFF為例講解電路設計流程

1)電路設計需求定義。電路設計之前需要對功能應用、工作性能和設計周期等需求因素進行評估和定義,為后續電路設計提供參考依據。

2)電路設計實現。基于功能需求定義,通過合理的電路結構進行電路設計實現。

3)電路符號產生。電路設計完成后,需要產生該電路對應的電路符號,供后期電路設計過程中的其他電路模塊調用。

4)電路功能仿真。電路設計完成后需要通過功能仿真來驗證電路的正確性及是否達到性能要求。

5)電路spice網表輸出。電路功能驗證通過并達到設計要求以后,就可以以spice網表的形式輸出電路結果給版圖設計人員進行版圖實現。

Virtuoso Schematic Composer操作流程

1.建立庫及電路設計環境

建庫時可以根據自己的需要設置項目庫的屬性,選擇不加工藝庫或者直接連接現有的工藝庫或者重新編譯一個新庫。在Name框里設置庫的名稱,這里設置為Icdream,同時在Technolog File中有3個選項可以選擇:

1)Compile a new techfile,新建的庫基于某個工藝進行,而這個是通過讀取流片廠家提供的工藝文件(techfile)實現的,所以一般選擇該設置。

2)Attach to an existing techfile,如果新建的庫可以和其他已經存在的庫共享同樣的工藝設置,可以選擇該選項。

3)Don’t need a techfile,不設置對應的工藝數據庫。

2.該設計HLFF單元電路原理圖

3.時序單元HLFF電路元件的產生

4.時序單元HLFF電路網表輸出

電路仿真

5.設置帶激勵輸入的仿真電路圖

HLFF電路仿真需要使用的輸入激勵器件。

1)電源地電位(gnd):在電路中表示0電位,和它相連的線名為gnd或者Vss。

2)電源電位(Vdd):和它相連的線名為Vdd。這個器件一般用來標識電源電位值。

3)電壓源(vdc):用于為電路提供對應的電壓。

4)時變電壓源(vpluse):在瞬態分析中可以生成不同占空比的方波、三角波、梯形波、鋸齒波。

5)電容(cap):用于在數字電路仿真中作為輸出負載。

6.進行電路仿真Virtuoso Analog Design Environment(ADE)

1)選擇要仿真的電路。

如果是從CIW窗口中打開的仿真環境,則需要設置仿真的電路。在ADE界面中,選擇Setup→Design或者點擊右上角的圖標 ,彈出Choosing Design對話框。

選擇需要仿真的電路,比如HLFF_sim,并點擊OK按鈕。

2)選擇仿真的模擬軟件。

在ADE界面里,選擇Setup→Simulator/Directory/Host選擇Simulator為spectre。

3)設置模型文件地址。

在ADE界面中,選擇Setup→Model Libraries設置模型文件地址,模型文件是仿真時仿真器需要提取器件參數的最基本數據。一般仿真模型包括五種基本的工藝模型:TT、FF、SS、FS、SF。

SF和FS

FS (Fast-Slow): 這個工藝角表示NMOS晶體管制造得比典型情況要快(具有更高的載流子遷移率或更低的閾值電壓),而PMOS晶體管則制造得比典型情況要慢(具有更低的載流子遷移率或更高的閾值電壓)。這種情況下,NMOS的速度會比正常快,而PMOS的速度會比正常慢,可能會導致電路的開關速度不平衡。

SF (Slow-Fast): 與FS相反,這個工藝角表示NMOS晶體管制造得比典型情況要慢,而PMOS晶體管制造得比典型情況要快。這意味著NMOS的速度會比正常慢,而PMOS的速度會比正常快,同樣可能導致電路的開關速度不平衡。

4)設置仿真的環境溫度。

5)設置仿真分析類型。

常用的有DC分析、AC分析、瞬態(Transient)分析、噪聲分析、零極點分析。

6)設置需要結果輸出的電路節點。

·直接選擇連線會在輸出中添加該到線的電壓;

·直接選擇一個器件的端口則會把這個端口的電流添加到輸出中;

·直接選擇一個器件則會把該器件的所有端口電流都添加到輸出中。

7)進行仿真。根據設計需要,選擇需要分析的最合適的電路節點

8)結果分析。

仿真完成后進行結果分析,在ADE界面中,選擇Result→Plot Outputs→Transient或者點擊右下角的圖標 顯示仿真結果波形圖。

9)保存和導入仿真結果。

仿真完成后,所有的相關結果都可以保存,用于以后的再次分析。

)

降低版本,涉及兼容性問題)

生成!)

OmniGen2:通向先進多模態生成的探索)