在以往的電子產品設計中,我們經常會選型 DCDC 芯片,在選型過程中經常遇到有些DC-DC電路中需要用到自舉電容,本文主要分析自舉電容在DC-DC電路中的原理。

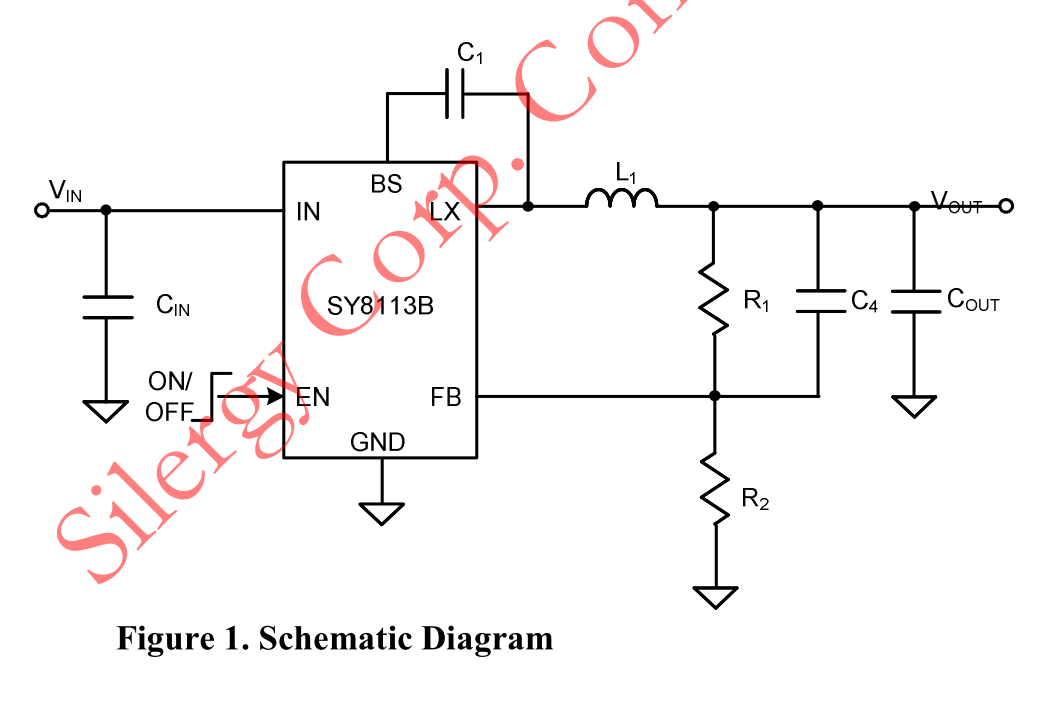

無論同步或者異步整流,經常會看到一個自舉電容,常并聯在DC-DC的LX和BS PIN腳之間,但是有也有無需自舉電容的DC-DC。

這里以矽力杰的SY8113BADC和 SM8082A為例說明;

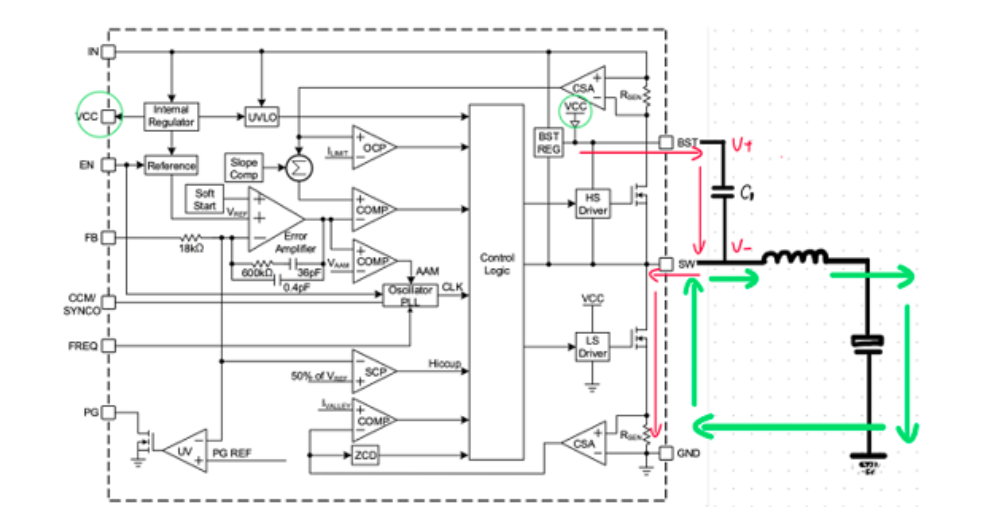

以SY8113BADC為基礎的BUCK電路,需要自舉電容,在BS和LX兩個PIN腳之間并聯的C1就是這個BUCK電路的自舉電容

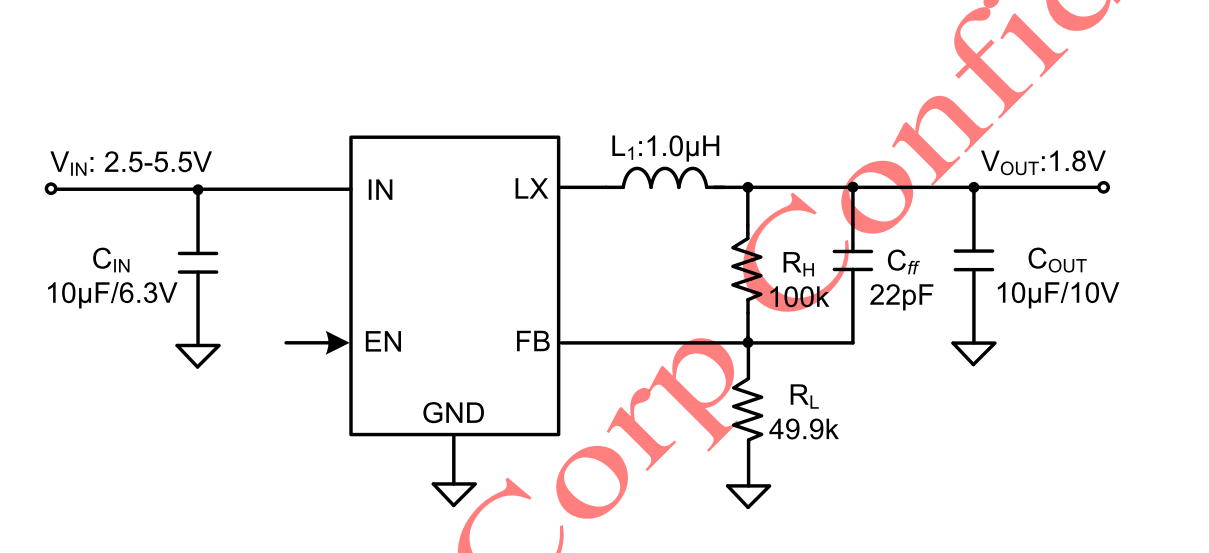

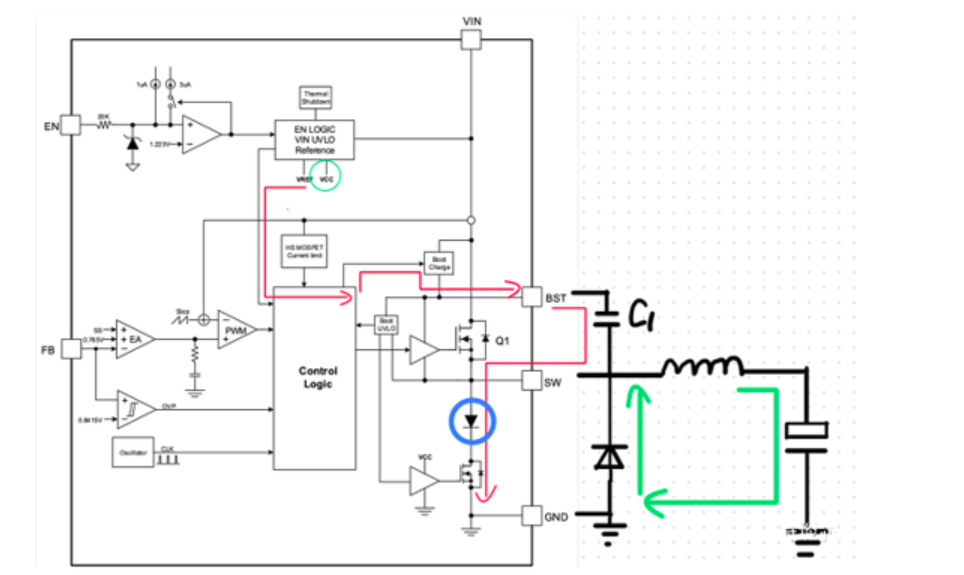

而SM8082A的BUCK電路中則沒有用到自舉電容;

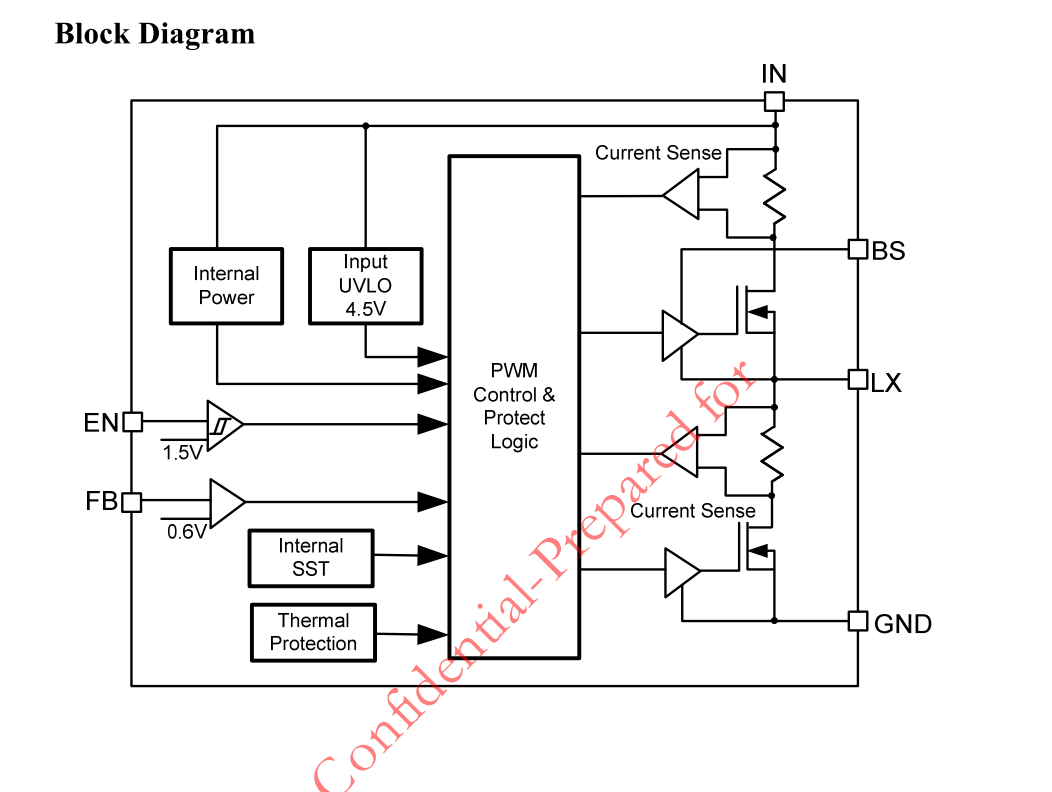

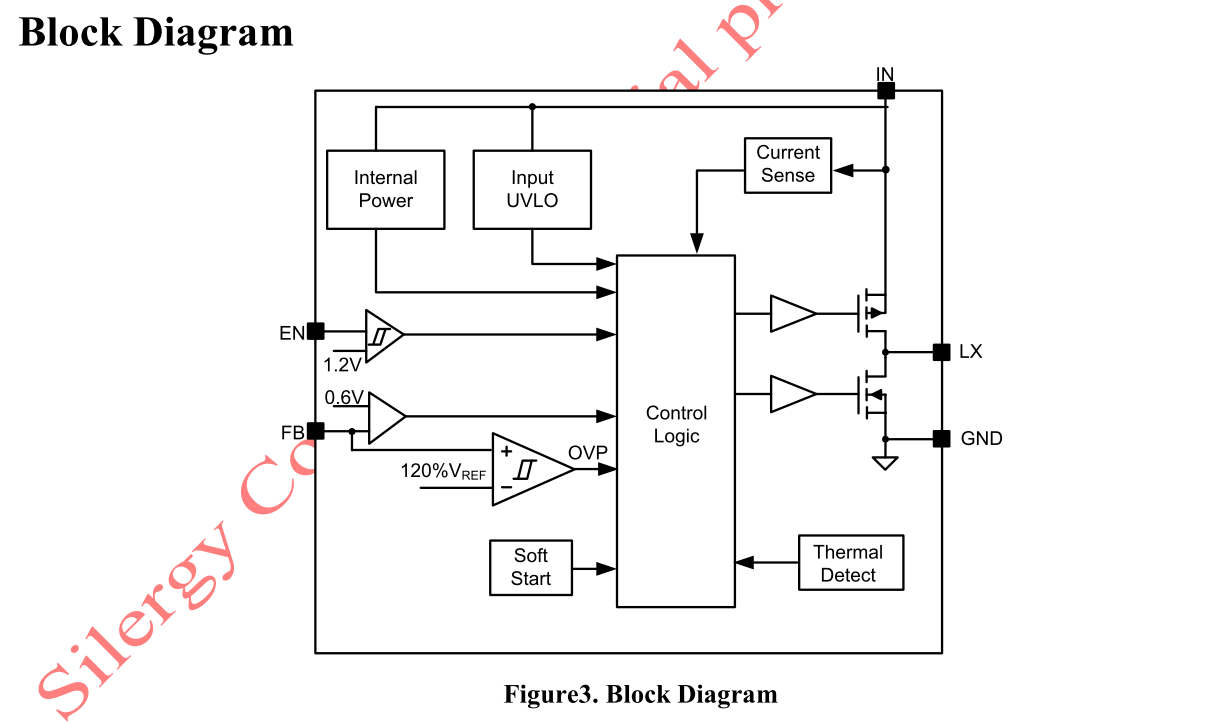

再比對一下二者的芯片內部框圖:

SY8113內部的高邊和低邊MOS均是N溝通MOS管;

而SM8082A的內部高邊MOS用的是P溝道MOS,低邊用的是N溝通MOS;

相較發現:SY8113 內部高邊MOS 為 NMOS,而 SM8082A的高邊 MOS 為 PMOS

結論:自舉電容的有無取決于芯片設計時采用的 MOS 管類型。

為什么有些用PMOS,有些用NMOS?

PMOS和NMOS由于其產品特性不同,各自的應用領域和使用方式也有所不同。

從器件本身來看:

PMOS的外延層是P型材料,多數載流子是空穴,

NMOS的外延層是N型材料,多數載流子是電子,

而電子的遷移率大概比空穴高2到3倍。因此在晶片面積相同的情況下,PMOS的導通電阻比NMOS高兩到三倍。

具有相同導通電阻的PMOS晶片面積是NMOS的2到3倍,

這樣PMOS的寄生參數如Qg等會比NMOS大,但是器件熱阻比NMOS小。

此外,PMOS的跨導也比NMOS小,所以響應速度會更慢。

從 上述MOS 管的生產工藝我們知道,PMOS 的導通電流往往不會很大,而在同樣的成本下,NMOS 的導通電流可以大很多,這意味著 Rdson 可以比較低。

因此很多DCDC的high-side mosfet都由PMOS換成了NMOS

同步DC-DC芯片內部的自舉電路原理:

以下圖的的同步DC-DC內部框圖看一下自舉電路;

框圖中,兩個綠色圓圈的 VCC 是 DC-DC 芯片內部穩壓出來的一個既可以驅動 MOS 管開通的電壓,同時也可以為芯片內部的其他邏輯電路供電。

Step1:

當低邊 MOS 管被 LS Driver 導通后(這里因為是低邊 NMOS,所以可以直接用 VCC 來驅動),VCC通過紅色箭頭所示的電路對自舉電容進行充電,

并將自舉電容兩端的 V+、V-電壓之間充電到 VCC 的電壓。此時C1的上端V+是VCC,下端V-是GND,(忽略低邊NMOS的內阻產生的壓降)。

此時降壓電路處于續流狀態,因此綠色箭頭表示電源輸出與負載電路之間的續流回路。

Step2:

當導通完成后,低邊 NMOS 將關閉,而高邊 NMOS 將由 HS 驅動器打開,給后級電感充電;

此時高邊MOS的S極是接在SW上,此時低邊MOS也關斷,這樣就沒了回路,

我們可以認為高邊MOS的S極是懸浮在半空中。只是單純的讓G極輸出高電平,并不能讓高邊MOS導通;

正是Cboot,將原本懸浮的HS Driver的兩個電源端V+/V-(這里可以認為是NMOS的G極和S極)之間建立了(電位差)聯系。這個電位差剛好是VCC

這里強調下:C1是并聯在HS Driver的電源兩端(V+/V-),并不是直接并聯在高邊MOS管的G和S兩端。但HS Driver和MOS是共"參考點"。

此時可以認為高邊MOS的Vgs=VCC。當Vgs>Vth此時,高邊MOS導通。

高邊MOS導通后,V-點電位突變為VCC,如果V+依舊保持VCC的電位,那Q1恐怕要被迫關閉了!

正是由于自舉電容C1的存在,C1電容兩端電壓差不能突變V+點電位變為2VCC。

這樣對C1而言,電壓差依然是VCC。對HS Drvier而言,以SW點電位為參考,輸出高電平時,Vgs依然是VCC,大于Vth,可以讓高邊MOS持續導通。

如果將 DC-DC 中的高邊 NMOS 換成 PMOS,就不需要經過電容充電的麻煩,直接給出一個低于系統輸入電壓 VIN 的電壓就可以使高端 PMOS 導通。

異步DC-DC的自舉電路和同步相似,不同的是:由于異步 DCDC 沒有低邊 MOS 管,所以都是依靠外部設計一個肖特基二極管來續流所以芯片的內部設計還是有區別的。

我們可以看到異步 DC-DC 芯片在橋下側設計了一個小 MOS 管,并且串聯了一個二極管(藍色圈出),之所以說這是一個小 MOS 管,是因為里面串聯了一個二極管,在電流續流的過程中,大電流回路只會流過外部的肖特基二極管,而不會影響自舉電容的充電回路。

紅色箭頭指向的電路是自舉電容充電電路,這次我們了解一下,在異步 DC-DC 芯片中,工程師都是預置一個小 MOS 管來控制自舉電容充電電路的。

因此在高端 MOS 采用 NMOS 的 DC-DC 芯片設計中,需要一個電路來起自舉的作用,即產生一個高于系統輸入電壓的電壓來導通高端 NMOS,而由于該電容尺寸較大,很難集成在 IC 中,所以大部分的 DC-DC 芯片都要求用戶將自舉電容放置在芯片的外部。

了解了自舉電容的原理,其實對于自舉電容的選擇也能得心應手,手冊上一般都會標注出來,對于內置功率MOS的DC-DC,它就是理論額定電壓也就是 DCDC 芯片 VCC 的電壓。

Reference list:

1.https://electronicspost.com/why-is-there-a-bootstrap-capacitor-in-all-dcdc-chip-designs/

2.https://blog.csdn.net/qq_21794157/article/details/123477257

3.https://blog.csdn.net/impossible1224/article/details/126606986

,支持經緯度定位與查找)

)

)

:)

基礎自定義分區器)