第一篇:I2C總線協議深度解剖

副標題 : 兩根線如何征服千億設備?詳解硬件工程師必須掌握的通信奧義

1. 為什么I2C仍是嵌入式經典?

1.1 總線拓撲的哲學

拓撲對比圖

SPI需4線+N片選 vs I2C僅2線級聯

UART點對點 vs I2C多主從架構

成本控制實例 :某智能手表傳感器模組布線成本節省37%

1.2 技術演進時間線

- 1982~2023關鍵節點 :

| 年份 | 事件 | 速率提升 |

|---|---|---|

| 1982 | Philips發布初版標準 | 100kHz |

| 1998 | 專利開放引發生態爆發 | 400kHz |

| 2007 | 加入高速模式(HS-mode) | 3.4MHz |

| 2014 | 最新版UM10204規范 | 5MHz |

1.3 當代應用場景

- 工業領域 :PLC模塊中的板載溫度傳感器鏈

- 消費電子 :手機攝像頭模組的控制總線

2. 物理層核心機制

2.1 電氣特性深度解析

-

開漏輸出原理 :

電路中僅使用一個N溝道晶體管。晶體管的漏極直接輸出,沒有連接到電源電壓。工作原理:當晶體管導通(開啟)時,輸出端接近地線;當晶體管關閉時,輸出端是懸空的,需要外部上拉電阻連接到高電平,以確保輸出端能夠達到高電平狀態。

優點:簡化了驅動電路,方便與不同電壓的電路接口,常用于I2C等總線通信協議中。

缺點:輸出高電平時依賴外部上拉電阻,對電路的設計提出了額外要求;輸出電流能力較弱。 -

為何需要上拉電阻?避免總線"鎖死"的數學證明

-

上拉電阻計算黃金公式 :

Rp(min) = (VDD - VOL(max)) / IOL Rp(max) = tr / (0.8473 × Cb) 其中: tr = 上升時間(規范要求<1μs@100kHz) Cb = 總線總電容(包括線路+器件引腳)

- 實例計算:當VDD=3.3V, Cb=200pF時,Rp取值區間

2.2 地址擴展的演進

- 7位 vs 10位尋址對比表 :

| 特性 | 7位地址 | 10位地址 |

|---|---|---|

| 設備數量 | 112個 | 1008個 |

| 首字節格式 | 0bAAA AAAA R/W | 0b1111 0AX R/W |

| 典型應用 | 傳感器 | 大型存儲陣列 |

3. 協議層關鍵時序

3.1 起止信號的時間密碼

- 時序參數規范表 :

| 參數 | 標準模式 | 快速模式 | 單位 |

|---|---|---|---|

| tSU:STA | 4.7 | 0.6 | μs |

| tHD:STA | 4.0 | 0.6 | μs |

| tSU:STO | 4.0 | 0.6 | μs |

- 常見設計錯誤 :

案例1:FPGA主頻過高導致tSU:STA不滿足

案例2:未考慮線延遲引發的建立時間違例

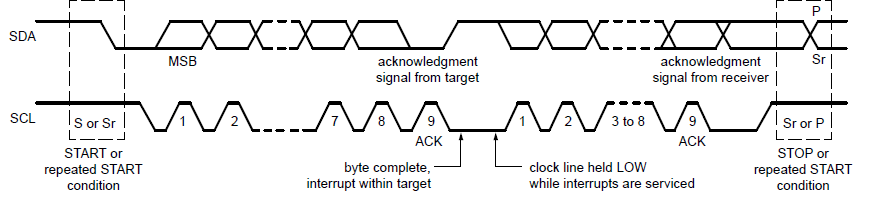

3.2 ACK/NACK應答機制

- 從機響應流程圖 :

Master發送字節 → 釋放SDA → 從機在第9時鐘拉低SDA → Master檢測ACK

- NACK的三種含義 :

- 從機地址不匹配

- 寫入時從機寄存器不可寫

- 讀取時主機應終止傳輸

3.3 時鐘拉伸(Clock Stretching)

- 典型應用場景 :

低速從機(如EEPROM)的數據準備期

安全芯片的加密計算耗時階段 - Verilog處理代碼片段 :

always @(posedge scl) begin if (slave_busy) scl_out <= 1'bz; // 釋放SCL線 else scl_out <= scl_gen; end

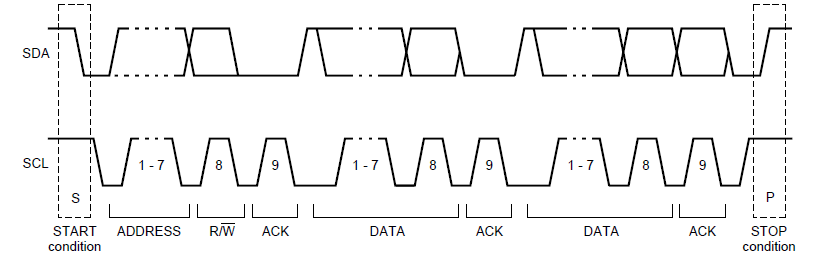

4. I2C 協議時序要求

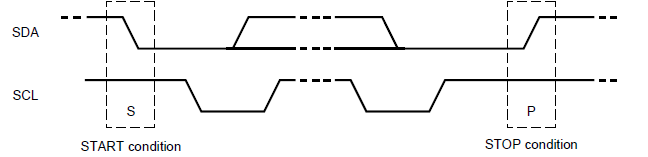

4.1 I2C傳輸開始結束時序

SCL: 高電平

SDA: 高電平 -> 低電平 傳輸開始

低電平 -> 高電平 傳輸結束

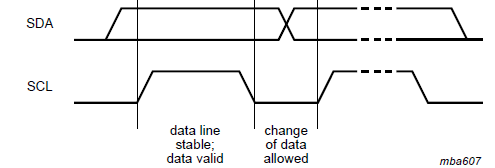

4.2 I2C有效數據時序

SCL:高電平時,SDA保持不練

SDA: SCL低電平時,SDA允許變化

4.3 I2C數據傳輸時序

Byte format: MSB first

配套資源

- I2C協議檢查表 (PDF下載):包含22個關鍵參數速查表

- I2C 協議 2021版本 :62頁完整I2C協議

![[Linux] vim及gcc工具](http://pic.xiahunao.cn/[Linux] vim及gcc工具)

WiFi 抓包環境配置教程)

——物聯網體系結構分層)