電流測試

我們可以通過電流來判斷芯片的工作狀態時,首先先了解下芯片的電流是如何產生的。

靜態電流

理論上,CMOS結構的芯片靜態時幾乎不耗電

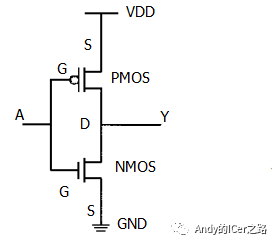

- CMOS基本結構:Pmos + Nmos 串聯

- 當邏輯電平穩定時:

? 要么Pmos導通,Nmos斷開

? 要么Nmos導通,Pmos斷開

? 整體不會形成直流通路 ? 所以靜態電流接近0

如下,利用經典的反相器來解釋這一原理:

| 輸入 | 動作 | 輸出 | 結論 |

|---|---|---|---|

| 高電平 | PMOS關,NMOS開,**VDD (斷了) ? **GND (通過NMOS) | 低電平 | 只有NMOS開,但沒有VDD到GND直接導通 ? 所以沒有直流電流 |

| 低電平 | PMOS開,NMOS關,**VDD *(通過PMOS) ? **GND (斷了) | 高電平 | 只有PMOS開,但還是沒有VDD到GND直接通路 ? 靜態電流近乎0 |

結論:

-

邏輯電平穩定時(比如芯片沒動靜的時候)

-

? 要么PMOS通,NMOS斷

-

? 要么NMOS通,PMOS斷

-

? 電流不會從VDD直接流到GND ? 所以理論上****靜態功耗幾乎為0

然而,實際上由于工藝問題,芯片上總會有微小的漏電,特別是先進工藝如7nm以下的芯片制成,這個漏電會更加嚴重,漏電產生的原因如下:

(1)亞閾值電流(Subthreshold Leakage)

- NMOS/PMOS在**理論"關斷"*時,實際上還是有*微小導通 ? 因為MOS管的閾值并不是硬開硬關

(2)二極管反向漏電

- MOS管的漏極/源極和襯底之間,會形成PN結,PN結反向偏置時,也會有少量漏電流

(3)柵氧化層漏電

- 現代工藝柵氧層超薄(特別是7nm、5nm以下),電場一高 ? 電子會穿隧 ? 也有漏電流

動態電流

然而,上述是指芯片在靜態的情況下的漏電流。當芯片在工作的時候,芯片內部的電流會增大,這主要是由于芯片內部的寄生電容開始放電導致的。

在芯片中,每個mos管和連線都會物理上帶有電容,這是無法避免的。這些電容主要來自MOSFET 柵極和漏/源極之間 , 天然就有電容結構,還有金屬連線之間的電容,金屬層和層之間(M1對M2、M3…)也像電容板,而芯片工作時的電平反轉,其實就是給這些寄生電容充電/放電。

信號翻轉時(比如0 ? 1),電容要充電**(芯片內部線長有電容),翻轉瞬間 ? PMOS和NMOS都短時間同時導通,這時候就會產生瞬時電流,從VDD ? GND這就是動態功耗

動態功耗的公式:

? P=CV2f

其中P代表動態功耗,C代表電容,V代表電壓,f代表工作頻率。

電容代表芯片的電容負載,反映芯片的大小和復雜度,電壓代表芯片電壓,即電源電壓,頻率代表芯片的工作頻率,即芯片每秒處理的指令數。

從公式可以看出,如果電容和電壓增大,動態功耗也會增大:如果頻率增大,動態功耗也會增大。因此,減小芯片的電容、電壓和頻率是減小動態功耗的關鍵

芯片測試中是如何測試靜態和動態電流的?

各類電流測試

| 測試項 | 作用 | 測試時機 | 從CMOS原理解釋 |

|---|---|---|---|

| IDDQ | 靜態電流測試 (Quiescent IDD) | 芯片靜態時 | 檢查有沒有短路、漏電。CMOS靜態時電流應接近0 |

| IDD | 工作電流測試 | 芯片運行時 | 邏輯翻轉時,電容充放電 ? 電流上升 |

| IDDT | 動態電流測試 (Transient IDD) | 芯片特定激勵時 | 電流波動,檢測信號是否在切換 |

| Leakage | 漏電測試 | 電源腳或IO腳 | MOSFET柵氧穿透、電源腳短路、芯片損壞時 ? 漏電流升高 |

IDDQ —— 靜態電流測試(最經典的失效檢測法)

作用:

- 檢查芯片內部有沒有短路、泄漏路徑

- 傳統CMOS邏輯靜態時,IDDQ應為幾微安或幾十微安

- 如果測到mA級別 ? 說明有短路、漏電

從CMOS原理看:

- CMOS的靜態電流 ≈ 漏電流(次級路徑)

- 如果有某個短路缺陷,比如:

- Nmos和Pmos 都導通 ? 電源直接拉通 ? 電流暴漲

ATE設置:

| 參數 | 說明 | 典型設定 |

|---|---|---|

| VDD Supply | 供電電壓 | 0.8V ~ 1.2V(核心) |

| Force Pattern | 特定靜態邏輯Pattern | 全0或全1,或Scan鏈特殊值 |

| Measure Range | uA ~ mA級別 | |

| Limit | 設定上限 | 如 IDDQ < 100uA |

IDD —— 正常工作時的電源電流

作用:

- 測試芯片在正常運作時,總功耗是否在預期范圍

- IDD變化 ? 反映芯片內部邏輯是否在運行

從CMOS原理看:

- 芯片運行時 ? 信號翻轉 ? 電容充放電

- 功耗P = C × V2 × f ? 電流跟頻率直接相關

- 頻率升高 ? 電流增加

- 負載電容大 ? 電流也大

常用于:

- 功耗敏感芯片(手機SoC、IoT)

- 檢查芯片有沒有「鎖死」、「時鐘丟失」之類的失效

- 比如:芯片跑起來 ? IDD從10mA變成30mA ? 說明邏輯活動正常

- 如果ID不變 ? 可能芯片沒跑動

ATE設置:

| 參數 | 說明 | 典型設定 |

|---|---|---|

| VDD Supply | 供電電壓 | 0.8V ~ 1.2V |

| Run Pattern | 向芯片加載Scan Shift/邏輯Pattern | 動態Pattern,如Scan shift 1000 cycles |

| Measure Range | mA ~ 幾百mA | |

| Limit | 設定動態功耗上下限 | 如 10mA < IDD < 30mA |

IDDT —— 動態電流檢測(專門檢測「信號活動」)

作用:

- 通過觀察電流波動,檢測芯片內部信號是否有切換

- 可以間接檢測時鐘、數據鏈是否活躍

從CMOS原理看:

- 動態電流 ? CMOS電容充放電導致

- 如果某個時鐘鏈死了 ? 該部分電流下降 ? IDDT變低

常用于:

-

Scan鏈檢測:看Scan Shift時,IDDT是否如預期波動

-

時鐘鏈檢測:時鐘失效 ? IDDT波動消失

IDD 和IDDT 一般區別不大。

Leakage —— 漏電流檢測(最基礎電流檢測)

作用:

- 檢查芯片IO腳、電源腳有沒有異常漏電

- 比如:芯片Pad與地/電源短路,或者ESD損壞

從CMOS原理看:

- MOS管有亞閾值電流、隧穿電流

- ESD損傷時 ? 短路路徑形成 ? 漏電升高

ATE設置:

| 參數 | 說明 | 典型設定 |

|---|---|---|

| Force Voltage | 施加的電壓 | 0.8V ~ 1.2V(核心電壓),或2.5V、3.3V(IO電壓) |

| Measure Range | 測量電流范圍 | nA ~ uA級別 |

| Limit (Pass/Fail) | 電流門限判斷 | 比如 Leakage < 1uA 為Pass |

良品芯片:Leakage通常在幾十nA~幾百nA

壞品芯片:Leakage達到uA甚至mA ? 短路或損傷

tips:關于芯片制程和IDDQ以及IDD的關系

芯片制程越先進,動態 電流越小,靜態 電流越大

| 功耗類型 | 制程變小(例如從28 nm→7 nm→5 nm) | 原因 |

|---|---|---|

| 動態功耗 | 減小 | 電容 C 更小,工作電壓 V 也更低 → Pdynamic=C·V2·f↓ |

| 靜態功耗 | 增大 | 柵氧層超薄、閾值電壓降 → 漏電流(亞閾值、隧穿)飆升 |

)

)

)

)

)